EPSON_高精度实时时钟模块

高精度时钟芯片的测试方法介绍

高精度时钟芯片的测试方法介绍 中国电子科技集团公司第五十八研究所武新郑解维坤 摘要: 高精度时钟芯片是一种能够提供精确计时的芯片,相对于普通的时钟芯片,它的晶体和温度补偿集成在芯片中,为提高计时精度提供了保障,它同时还具备日历闹钟功能、可编程方波输出功能等。本文以DS3231芯片为例,以J750Ex测试机和相关仪表为测试环境,重点介绍以I2C总线协议为基础的内部寄存器功能和芯片各模块功能的测试。通过测试机测试保存在寄存器中秒、分、时、星期、日期、月、年和闹钟设置等信息,以及电源控制功能,通过测试机对示波器和频率计的程控实现对老化修正和输出频率的测试,同时还会重点介绍该芯片时钟精度的测试方法和测试环境。 关键词: 高精度时钟芯片;DS3231芯片;J750Ex测试机;I2C总线协议 Introduction of testing method of the extremely accurate RTC Wu Xin-zheng (China Electronic Technology Group Corporation, No.58 Research Institute , Jiangsu Wuxi 214035, China) Abstract: The extremely accurate real time clock is a piece of chip which can maintain accurate timekeeping, compared with the ordinary RTC chip, its integrated temperature compensated crystal oscillator and crystal are located in the center of the chip, which provides an assurance for promoting the exacticy, it also has two programmable time-of-day alarms and a programmable square-wave output. This paper takes DS3231 for instance, the environment with J750Ex and related instruments, introduces inner register with I2C and the testing method of every module. The ATE tests seconds, minutes, hours, day, date, month, and year information, the function of power. By means of OSC and frequency meter, it can test the output wave and register for aging trim, at the same time, also introduced the testing method and environment of accuracy. Key words:

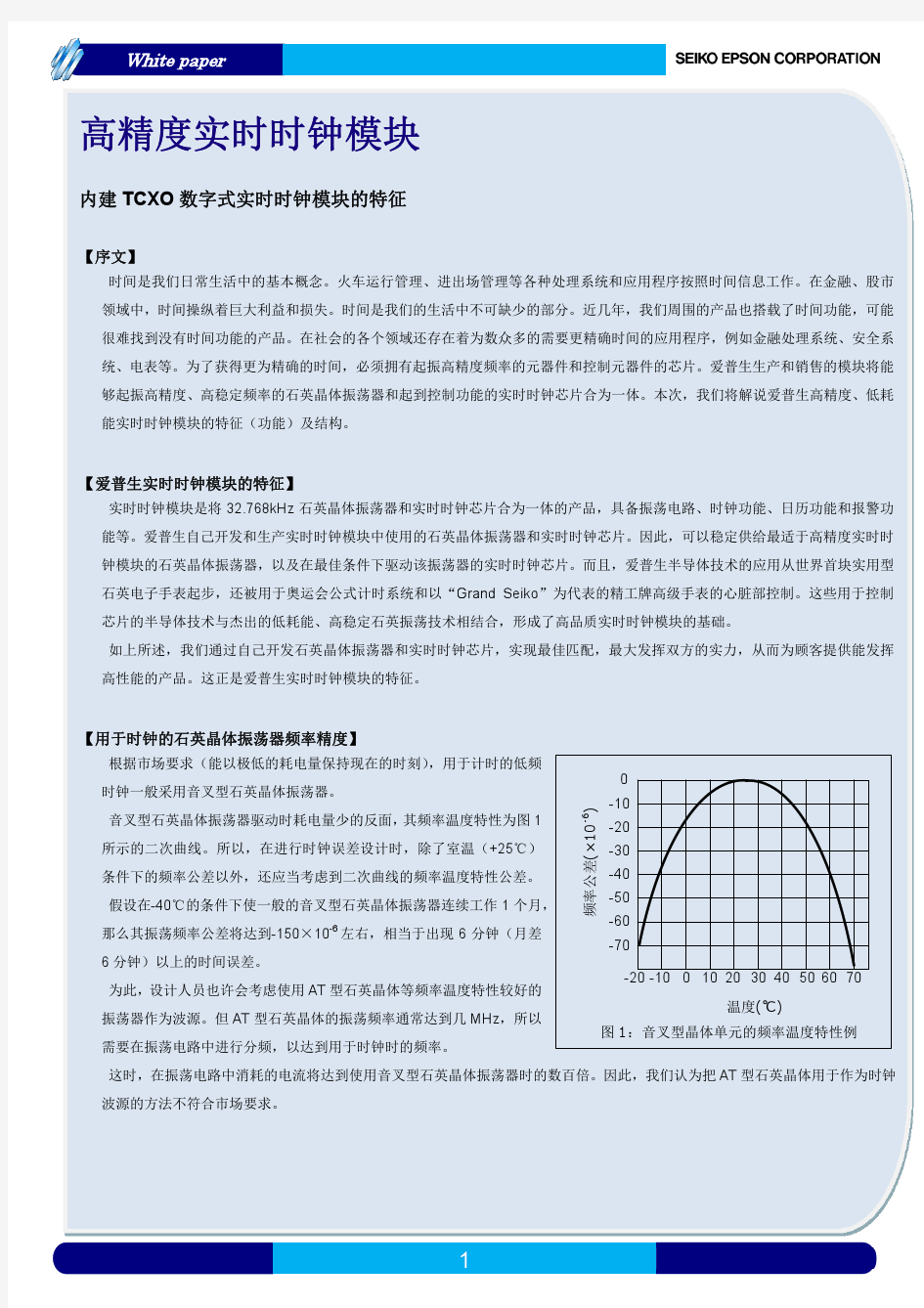

单片机原理课程设计基于AT89C52的电子时钟设计说明

单片机原理课程设计 题目: 基于AT89C52的电子时钟设计 姓名: 学院: 专业: 班级: 学号: 指导教师: 年月日 农业大学教务处制

aortiu 目录 摘要 (2) 关键词 (2) 引言 (2) 1设计要求与方案论证 (2) 1.1设计要求 (2) 1.2系统方案选择方案和论证 (2) 1.2.1单片机芯片的选择方案和论证 (2) 1.2.2 显示模块选择方案和论证 (3) 1.2.3 时钟芯片的选择方案和论证 (3) 2.系统的硬件设计与实现 (3) 2.1电路设计框图 (3) 2.2系统硬件概述 (3) 2.3主要单元电路的设计 (4) 2.3.1 单片机主控制模块的设计 (4) 2.3.2时钟电路模块的设计 (4) 2.3.3 键盘模块设计 (5) 2.3.4蜂鸣器模块的设计 (5) 2.3.5显示模块的设计 (5) 3.系统的软件设计 (6) 3.1程序流程框图 (6) 3.2程序的设计 (7) 4.系统调试 (7) 4.1软件调试 (7) 4.2硬件调试 (8) 4.3 实验箱调试结果 (8) 5.总结心得体会 (9) 附录一:系统程序 (9)

基于AT89C52的电子时钟设计 指导教师:吕成绪胡飞 摘要:单片机在电子产品中的应用越来越广泛,特别是51系列的单片机,由于其使用方便、价格低廉等优势,在市场上占有很大的份额。AT89C52就是51系列中的一个比较成熟的型号。本设计是一个多功能的实时时钟,带秒表、整点报时、闹铃、调整时间等功能。可按键直接设置闹铃时间。由AT89C51单片机、DS1302、LCD1602等模块组成。现代社会,时间就是金钱,时钟是每个人的必备品。本设计实现了所需功能,给大家带来方便,整体性好、人性化强、可靠性高,实现了时钟的多功能应用。 关键词:电子时钟;DS1302;LCD1602; 引言: 随着科技的快速发展,时间的流逝,从观太阳、摆钟到现在电子钟,人类不断研究,不断创新纪录。美国DALLAS公司推出的具有涓细电流充电能的低功耗实时时钟电路DS1302。它可以对年、月、日、周、时、分、秒进行计时,还具有闰年补偿等多种功能,而且DS1302的使用寿命长,误差小。对于数字电子时钟采用直观的数字显示,可以同时显示年、月、日、周日、时、分、秒和温度等信息,还具有时间校准等功能。该设计以AT89C51单片机作为核心,功耗小,能在3V的低压工作,电压可选用3~5V电压供电。 综上所述,此电子时钟具有读取方便、显示直观、功能多样、电路简洁、成本低廉等诸多优点,符合电子仪器仪表的发展趋势,具有广阔的市场前景。 1.设计要求与方案 1.1 设计要求: (1)启动时显示制作的年、月、日、制作者的学号等信息。 (2)24小时计时功能(精确到秒) (3)整点报时功能。 (4)秒表功能 (5)省电功能模式(未设计) 1.2 系统基本方案选择 1.2.1单片机芯片的选择方案和论证 方案一: 采用89C51芯片作为硬件核心,采用Flash ROM,部具有4KB ROM 存储空间,能于3V的超低压工作,而且与MCS-51系列单片机完全兼容,但是运用于电路设计中时由于不具备ISP在线编程技术, 当在对电路进行调试时,由于程序的错误修改或对程序的新增功能需要烧入程序时,对芯片的多次拔插会对芯片造成一定的损坏。 方案二: 采用AT89S52,片ROM全都采用Flash ROM;能以3V的超底压工作;同时也与MCS-51

高精度数模转换器

选择和使用高精度数模转换器 时间:2011-05-10 23:17:40 来源:作者:叶子 很多应用 (包括精密仪器、工业自动化、医疗设备和自动测试设备) 都需要高准确度数模转换。在 16 位分辨率时要求准确度好于约±15ppm 或±1LSB 的电路中,设计师传统上一直被迫使用大量校准,以在所有情况下保持准确度。新型高精度 DAC 使得能够采用一个单片式 DAC 来实现±4ppm 准确度或±1LSB (在 18 位分辨率条件下),而无需校准。在本文中我们将对高精度数模转换器的选择和使用过程中所涉及的问题进行研究。 DAC 的架构对于 DAC 的技术规格及其对电路板设计师的要求均有影响。为了实现最佳性能,需要谨慎地考虑 DAC 上的电源、基准和输出放大器所产生的影响。 过采样或增量累加 DAC 过采样或ΔΣ ADC 采用一个低分辨率 DAC (通常仅 1 位),在其前后分别布设一个噪声整形数字调制器和一个模拟低通滤波器。最准确的商用增量累加 DAC 实现±15ppm 的准确度,但是需要 15ms 才能稳定,并要承受相对较高的 1μV/√Hz 噪声密度。其它可购得的过采样 DAC 在 80us 内稳定,但是INL 较差,大约为 240 ppm。 合成 DAC 通过结合两个较低分辨率的单片 DAC,有可能构成一个高分辨率的合成 DAC。请注意,粗略 DAC 的分辨率和精细 DAC 的范围需要重叠,以确保所有想要的输出电压都可实现。粗略 DAC 的准确度和漂移一般将限制合成 DAC 的最终准确度,因此要提高准确度,就需要对合成 DAC 转移函数的特性和软件进行校正。也可能需要频率校准,以校正随温度、时间、湿度和机械压力产生的变化导致的漂移。 电阻串 DAC 电阻串 DAC 采用具有 2N 个分接点的一系列电阻分压器,以实现 N 位分辨率。采用电阻串架构的单片 16 位 DAC 一般含有一个较低分辨率的电阻串 DAC 和一个范围较小的 DAC,范围较小的 DAC 用于插入串器件之间,以实现 16 位分辨率。这种串+内插器方法的一个优点是,DAC 输出具有固有的单调性,无需微调或校准。 这类 DAC 的基准输入阻抗一般很高 (50KΩ~ 300kΩ),而且不受输入代码的影响,从而有可能使用一个非缓冲型基准。因为电阻串的输出阻抗随输入代码变化,所以大多数电阻串 DAC 含有集成的输出缓冲器放大器,以驱动电阻性负载。 尽管电阻串 DAC 的 DNL 本身非常好,但是 INL 由串联电阻器件的匹配决定,而且可能由于含有大量的独立器件而难以控制。直到最近,这类 DAC 的准确度一直限制在约±180ppm。最近的进步已经使得准确度提高到了±60ppm。例如,LTC2656 在 4mm x 5mm 封装中集成了 8 个 DAC 通道,在 16 位分辨率时具有±4LSB 的最大 INL。 阻性梯形或 R-2R 型 DAC 阻性梯形或 R-2R DAC 采用一种类似于图 2 所示的三端子结构,电阻器在 A 端和 B 端之间切换。请注意,A 端和 B 端上的阻抗与代码的相关性很高,而 C 端则具有一个固定阻抗。电阻器与开关的匹配情况将会影响这种结构的单调性和准确度。此类 DAC 一般经过修整或在出厂时经过校准,而且,具±1LSB INL 和 DNL 的单调 16 位阻性梯形电路 DAC 上市已有很长时间了。 电压输出 R-2R DAC 一种常见类型的 R-2R DAC 将C 端用作 DAC 输出电压,而 A 端连接到基准,B 端连接到地。输出阻抗相对于输入代码是恒定的,从而有可能以非缓冲方式驱动电阻负载。例如,LTC2641 16 位 DAC 能以非缓冲方式驱动 60kΩ负载,同时保持±1LSB 的 INL 和 DNL,并消耗不到 200μA 的电源电流。 这种方法的一个缺点是,基准阻抗随着输入代码大幅变化。由于 R-2R 梯形电路的本质,甚至DAC 输出电压中很小的变化也可能在基准电流中引起 1mA 或更大的阶跃变化。为此,必须由一个高性能放

PCF8563实时时钟高精度调整方法

广州周立功单片机发展有限公司 Tel: (020)38730976 38730977 Fax: 38730925 https://www.360docs.net/doc/731546693.html, PCF8563实时时钟高精度调整方法 一、概述 PCF8563是PHILIPS公司设计生产的经典工业级实时时钟芯片(RTC),I2C总线接口,具有功耗低、精度高等特点,广泛应用于电表、水表、气表、电话等产品。本文将介绍如何调整PCF8563时钟精度的方法。 二、电路原理 图1 PCF8563高精度调整 三、相关说明 如图1所示,R3、R4为I2C总线上拉电阻,若总线速度高于100KHz,电阻阻值要更小。由于PCF8563的中断输出及时钟输出均为开漏输出,所以要外接上拉电阻(如图1的R1、R2),若不使用这两个信号,对应的上拉电阻可以不用。 对于PCF8563芯片,需外接时钟晶振32768Hz(如图1的X1),推荐使用5ppm或更稳定的晶振。PCF8563典型应用电路推荐使用15pF的晶振匹配电容,实际应用时可以作相应的调整,以使RTC获得更高精度的时钟源。一般晶振匹配电容在15pF~21pF之间调整(相对于5ppm精度的32768Hz晶振),15pF电容时时钟频率略偏高,21pF电容时时钟频率略偏低。 四、操作方法 1. 设置PCF8563时钟输出有效(CLKOUT),输出频率为32.768KHz。 使用高精度频率计测量CLKOUT输出的频率。 2. 根据测出的频率,对JC1、JC2、JC3作短接或断开调整。频率比32768Hz偏高时, 3. 加大电容值;频率比32768Hz偏低时,减小电容值。 说明:图1中的C1、C2、C3的值在1pF~5pF之间,根据实际情况确定组合方式,以便于快速调整。推荐使用(3pF、3pF、3pF)、(1pF、2pF、3pF)、(2pF、3pF、4pF)。 - 1 -

用普通单片机实现低成本高精度AD与DA转换

用普通单片机实现低成本高精度A/D与D/A转换(之一) 摘要:用普通单片机实现低成本的多路A/D与D/A转换,其转换结果为8bit或更高。 关键词:单片机A/D转换D/A转换PWM(脉冲宽度调制)比较器 目前单片机在电子产品中已得到广泛应用,许多类型的单片机内部已带有A/D转换电路,但此类单片机会比无A/D转换功能的单片机在价格上高几元甚至很多,本文给大家提供一种实用的用普通单片机实现的A/D转换电路,它只需要使用普通单片机的2个I/O脚与1个运算放大器即可实现,而且它可以很容易地扩展成带有4通道A/D转换功能,由于它占用资源很少,成本很低,其A/D转换精度可达到8位或更高,因此很具有实用价值。 其电路如图一所示: 500) {this.resized=true; this.width=500; this.alt='点击查看原图';}; this.style.cursor='hand'" onclick="if(!this.resized) {return true;} else {window.open('https://www.360docs.net/doc/731546693.html,/blog/u/40/1144027076.jpg');}" border="0" width="500"> 图一 其工作原理说明如下: 1、硬件说明: 图一中“RA0”和“RA1”为单片机的两个I/O脚,分别将其设置为输出与输入状态,在进行A/D 转换时,在程序中通过软件产生PWM,由RA0脚送出预设占空比的PWM波形。RA1脚用于检测比较器输出端的状态。 R1、C1构成滤波电路,对RA0脚送出的PWM波形进行平滑滤波。RA0输出的PWM波形经过R1、C1滤波并延时后,在U1点产生稳定的电压值,其电压值U1=VDD*D1/(D1+D2),若单片机的工作电压为稳定的+5V,则U1=5V*D1/(D1+D2)。 图一中的LM324作为比较器使用,其输入负端的U1电压与输入正端的模拟量电压值进行比较,当U1大于模拟量输入电压时,比较器的输出端为低电平,反之为高电平。 2、A/D转换过程: 如果使RA0输出PWM波形,其占空比由小到大逐渐变化,则U1的电压会由小到大逐渐变化,当U1电压超过被测电压时,比较器的输出端由高电平变为低电平,因此可以认为在该变化

实时时钟RTC模块和串口设计电子钟实验

实时时钟RTC模块和串口设计电子钟实验一、实验要求 对开发板上STM32处理器的RTC模块进行操作。RTC模块的当前时间通过串口 传送给PC机的超级终端显示,若RTC模块还未设置时间则通过超级终端进行设置。RTC的秒中断每发生一次,发光二极管LED1闪烁一次。 二、硬件电路设计 在开发板上STM32F103VET6处理器的VBAT引脚接+3V钮扣电池,PB6引脚接 LED1,晶振、USART等均已连接好。 该应用实例不需要额外电路设计,只需将用一根RS232串行通讯线将开发板 的COM1口与PC机的串口相连即可。 三、软件设计思路 根据设计要求,软件需实现以下任务: (1) 系统启动后检查RTC是否已设置。由于RTC在BKP区域,当Vdd掉电之后可由后备电源提供电源,当后备电源连接到针脚VBAT上时,RTC的设置不会由于外部电源的断开而丢失。在本例中先写一个值到BKP_DR1中以标示RTC是否已配置,在启动之后程序检查BKP_DR1的值,如果保持不变,则表示有后备电池;若BKP_DR1的值不是已经写入的值,则可能是BKP_DR1的值有误或者由于是第一次运行值还未写进去,则需要配置RTC,并且询问用户当前的时间作为RTC的起始值。 (2) 若BKP_DR1的值正确,则意味着RTC已配置,此时将在超级终端上按照每秒一次的频率更新时间。 (3) 在RTC秒中断发生时,连接到PB.05 的LED1灯改变一次状态,这样闪烁频率为2秒。 四、程序分析 整个工程包含3个源文件:startup_stm32f10x_hd.s、stm32f10x_it.c和main.c,其中startup_stm32f10x_hd.s为启动代码,所有中断服务子程序均在stm32f10x_it.c中,其它函数则在main.c中。下面分别介绍相关的函数,函数RTC_IRQHandler用于处理秒中断事件,每次秒中断令LED1闪烁一次,在每次遇到23:59:59时将时钟回零。 函数RTC_Configuration用于配置RTC模块。 函数USART_Scanf用于从PC超级终端中获取输入的数字值。 函数Time_Regulate则利用函数USART_Scanf从超级终端获取新的RTC时间值,并回显到终端中。 函数Time_Adjust使用函数Time_Regulate的结果设置新的RTC时间。 函数Time_Show和Time_Display用于每秒一次的时间处理和将RTC时间转换 了时分秒字符串送往USART1。 源文件其他函数,例如GPIO、RCC、NVIC、USART的配置,不再作冗述。 编译与链接:

卫星共视高精度时间比对与传递

卫星共视法高精度时间频率比对与传递系统

目录 1.概述 (3) 2.卫星共视时间比对与传递系统组成及工作原理 (4) 2.1 卫星共视时间比对与传递工作原理 (4) 2.2 时间比对和传递系统设备配置及连接 (7) 3.经费预算................................................. 错误!未定义书签。

1.概述 时间是物理学的基本参量之一。随着科学技术的发展,高精度的时间和频率在国民经济发展中的地位日趋重要,诸如通信、电力、交通、高速数字网同步等高新技术领域有着广泛的应用,特别是我国国防建设和空间技术领域,如空间目标探测与拦截(类似于美国爱国者导弹防御系统)、我国第二代战略武器试验、载人航天工程和拟建中的二代卫星导航系统对时间和频率的精度提出了更高的要求。 二十世纪末,随着空间技术的发展,GPS和北斗卫星导航系统相继问世,授时具有了全方位性(陆地、海洋、航空和航天)、全球性、全天候、连续性和实时性,并提供了高精度的授时覆盖和服务。“时间统一系统”为精密时间产生、传递、恢复和保持、科学研究、科学实验和工程技术及一切动力学系统和时序过程的测量和定量研究提供了必不可少的时间基准和依据。 就高精度时间传递与比对系统而言,可以应用于工程项目的主要包括以下几种: 1.RNSS卫星共视时间比对与传递; 2.RNSS卫星载波相位时间同步; 3.卫星双向时间比对与传递; 4.搬运钟时间比对与传递。 在以上几种方法中,卫星共视时间比对与传递是一种较为优秀的高精度时间比对与传递系统。

2.卫星共视时间比对与传递系统组成及工作原理 2.1 卫星共视时间比对与传递工作原理 所谓“共视”(Common View)就是位于两个不同位置的观测者,在同一时刻对同一颗卫星进行观测,其原理如下图所示。 图1 GPS 共视法高精度时间同步原理图 图1给出了一个单收系统示意图,在每个比对点,本地钟均按自己的速率运行。根据比对需求,利用卫星所发射的1PPS 秒信号、或其它固定速率发射的时钟脉冲信号。 在每个测站,利用本地钟的1PPS 信号打开时间间隔计数器闸门,再用从共视接收机所输出的1PPS 秒信号关闭时间间隔计数器的闸门。这样,我们可以得到以下的时间关系(图2): 在钟1处: 接收时间 1τ+=卫接收T t 计数器读数 1d T =)(11τ+-卫T T (1) GPS 卫星

高精度数模转换器AD420及其与MSP430的接口技术

高精度数模转换器AD420及其与MSP430的接口技术 1 概述 AD420是ADI公司生产的高精度、低功耗全数字电流环输出转换器。AD420的输出信号可以是电流信号,也可以是电压信号。其中电流信号的输出范围为4mA~20mA,0mA~20mA或0mA~24mA,具体可通过引脚RANGE SELECTl,RANGE SELECT2进行配置。当需要输出电压信号时,它也能从一个隔离引脚提供电压输出,这时需外接一个缓冲放大器,可输出0V~5V,0V~10V,±5V或±10V电压。 AD420具有灵活的串行数字接口(最大速率可达3.3 Mb/s),使用方便、性价比高、抑制干扰能力强,非常适合用于高精度远程控制系统。AD420与单片机的接口方式有2种:3线制和异步制。单片机系统通过AD420可实现连续的模拟量输出。其主要特点如下: ?宽泛的电源电压范围为12 V~32 V,输出电压范围为0V~-2.5 V; ?带有3线模式的SPI或Microwire接口,可采集连续的模拟输入信号,采用异步模式时仅需少量的信号线; ?数据输出引脚可将多个AD420器件连接成菊链型; ?上电初始化时,其输出最小值为0 mA,4 mA或O V; ?具有异步清零引脚,可将输出复位至最小值(0mA、4 mA或0V); ?BOOST引脚可连接一个外部晶体管来吸收回路电流,降低功耗; ?只需外接少量的外部器件,就能达到较高的精度。 AD420采用24引脚SOIC和PDIP封装,表1是其引脚功能说明。

2 工作原理 在AD420中,二阶调节器用于保持最小死区。从调节器发出的单字节流控制开关电流源,两个连续的电阻电容装置进行过滤。电容为电流输出额外增加的器件。输出电流则简单显示为4 mA~20 mA,OmA~20mA或0mA~24mA。AD420采用BiCMOS工艺,能够适合高性能的低电压数字逻辑和高电压模拟电路。

实时时钟芯片应用设计时必须要考虑的事项

实时时钟芯片应用设计时必须要考虑的事项 总述 实时时钟芯片(RTC)允许一个系统能同步或记录事件,给用户一个易理解的时间参考。由于RTC的应用越来越广泛,为了避开设计时出现的问题,设计者应熟悉RTCs。 选择接口 RTC可用的总线接口范围很宽。串行接口包括2线(I2C),3线和串行外设接口(SPI)。并行接口包含多总线(多数据和地址线)和带单独地址及字节数据输入的设计。接口的选择通常由所用的处理器类型决定,很多处理器包括2线或SPI接口。其它的,如8051处理器及其派生的处理器支持多路地址和数据总线。时间保持非易失性(NV)RAM和SRAM用相同的控制信号,许多处理器都提供这种方便的接口,也包括各种不同的用电池组支持的RAM。最后,看不见的时钟隐藏电池供电的RAM中并可用64位的软件协议去访问时钟。 备用电池的功能 在有的应用中,例如VCRS,如果去掉电源,会丢失时间和日期信息,。许多新的应用中,即使主电源去掉了,要求时间和日期信息应保持有效。为了保持时钟晶振运行,要用到一个主电源或者备用电源,或者一个大容量的电容。在这种情况下,时钟芯片必须能够在两个电源之间进行切换。 如果有一个电池,例如钮扣型锂电池用作备用电源,当在用备用电源工作时RTC应设计成尽可能少的消耗功耗。电源切换电路,一般情况下由主电源供电,会使电源切换到电池供电,并使RTC进入低功耗模式。微处理器和RTC之间的通信通常锁定(称为写保护),用来使电池供电电流最小和防止数据损坏。 许多时钟芯片都包括一个晶振控制位,通常称之为时钟中断(CH)或是晶振使能位(/EOSC)。此位通常位于秒寄存器或控制寄存器的最高位(位7),几乎在有这位的所有时钟芯片中,初始电池上的首选状态对于晶振来说是无效的。这允许系统设计者提出制造流程,在安装和测试后,用Vbat进行供电,通常用个锂电池。此时晶振处于一个停止状

用比较器进行高精度模数转换

一种高精度单斜率AD 及其单片机实现 摘要:介绍了一种利用MSP430 F1121单片机构成的采用类似于Σ-Δ技术的高精度的单斜率AD 。分析了工作原理和参数计算。提供了分辨率,精度,线性度,稳定性等性能的测试结果,并讨论了它们的影响因素和应用。 关键词:MSP430单片机 单斜率AD 一 引言 AD 转换最常用的方法是逐次逼近法(SAR ),转换时间固定且快速是其最大特点,但要明显提高分辩率有一定困难。积分型AD 有较强的抗干扰能力,但转换时间较长。而过采样Σ-ΔA/D 由于其高分辩率,高线性度及低成本的特点正得到越来越多的应用。TI 公司的MSP430F1121单片机内带有一个模拟比较器,因此,只须外接一只电阻和电容即可构成一个类似于Σ-Δ技术的高精度单斜率AD 。 二 测量电路及过程 MSP430于F1121是16位RISC 结构的FLASH 型单片机。有14个双向I/O 口并兼有中断功能。一个16位定时器,兼有计数和定时功能。一个模拟电压比较器。 测量电路如图2-1所示。 MSP430F1121工作电压为1.8-3.6V 。I/O 口输出高电平时电压接近Vcc ,低电平时接近Vss ,因此,一个I/O 口可以看作一位DAC ,具有PWM 功能。测量时P2.4引脚接被测电压。P2.0口输出一串占空比为50%,脉宽为Tp 的脉冲。当电容充电到Vout=Vin 时,比较器输出将翻转,这一过程称为预充电。此后为维持Vout=Vin ,P2.0继续输出脉冲。程序开始对总的输出脉冲数N 和输出为高的 脉冲数n 进行计数。P2.0口根据比较器的输出状态来决定是输出高还是低电平,如果比较器输出为低,表示Vout

DS1302实时时钟模块,1602显示

/******************* 说明:************************** 将实时时钟数据通过LCD1602 显示基于51 单片机 **************************************************/ #include 高精度Delta-Sigma A/D转换器的原理及其应用 本次在线座谈主要介绍TI的高精度Delta-Sigma A/D转换器的原理及其应用,Delta-Sigma转换器的特点是将绝大多数的噪声从动态转移到阻态,通常Delta-Sigma转换器被用于对成本与精度有要求的低频场合。本文首先将对TI的高精度Delta-Sigma A/D转换器进行综述性介绍,而后将介绍噪声的测量及芯片ADS1232等。 Delta-Sigma转换器综述 Delta-Sigma转换器是采用超采样的方法将模拟电压转换成数字量的1位转换器,它由1位ADC、1位DAC与一个积分器组成,见图1。Delta-Sigma转换器的优点表现在低成本与高分辨率,适合用于现在的低电压半导体工业的生产。 Delta-Sigma转换器组成 Delta-Sigma转换器由差分放大器、积分器、比较器与1位的DAC组成,输入信号减去来自1位DAC 的信号将结果作为积分器的输入,当系统得到稳定工作状态时,积分器的输出信号是全部误差电压之和,同时积分器可以看作是低通滤波器,对噪声有-6dB的抑制能力。积分器的输出用1位ADC来转换,而后比较器将输出数字1和0的位流。DAC将比较级的输出转换为数字波形,回馈给差分放大器。 Delta-Sigma转换器原理详述 积分器将量化噪声伸展到整个频带宽度,从而使噪声成型,而滤波器可以过滤掉绝大多数的成型噪声。有几个误差源会降低整个系统的效果,为了满足ADC的输入范围,很多信号要求一些放大电路和电平偏移电路,有时放大器在ADC的内部,有时使用外部放大器。无论是哪一种情况,放大器电压、电压漂移、输入偏置电流或采样噪声将引入误差信号。为了得到精确的ADC转换结果,放大器的误差应该通过调整来消除或减少。积分器对输入低频或直流信号内置一个低通滤波器,从而极大地降低了通道内的噪声。 典型的半导体放大器的噪声分为两个部分,1/F噪声和对地噪声,Delta-Sigma ADC的主要应用是在低频场合,因此1/F噪声的影响占主要地位。选择合适的放大器可以控制1/F噪声。由噪声频谱图可知(见图2),器件的噪声在高频主要是背景噪声,而在低频主要是1/F噪声,当越接近我们想要得到的直流信号时,1/F噪声越大。人们通常把1/F噪声想象成漂移,它是一个非常低频率的现象,常用的解决方法是采用窄波输入。 mcHF实用教程——支持实时时钟 作者:BI3MEK 目录 一、环境要求 (3) (一)主板要求 (3) (二)配件要求 (4) 二、实施步骤 (4) (一)增加触摸屏(非必须操作) (4) 1.原版0.4版本方案 (4) 2.原版0.5版本方案 (5) 3.使用BI3MEK0.5版本 (6) (二)屏幕改为SPI接口方式 (7) 1.原版0.4版本PCB (7) 2.原版0.5版本PCB (7) 4.使用BI3MEK 0.5版本的PCB (8) (三)改实时时钟 (8) 步骤一:接好电池 (9) 步骤二:接好晶振 (10) 步骤三:接好按键 (11) 步骤四:RTC使能 (12) 三、注意事项 (13) mcHF是由英国火腿M0NKA Chris设计的入门级别的SDR 电台。具有短波机常见的工作模式。机器小巧、廉价、操作方便、显示直观,令人生爱。目前mcHF机器硬件版本已经发展到0.6版本,具有更好的性能,但是一直未开放实时时钟功能,本文将介绍对国内常见的0.4和0.5版本升级实时时钟功能(RTC)。 一、环境要求 McHF机器如果要改为支持RTC实时时钟,需要使用STM32单片机的内置时钟模块,原设计该时钟模块的引出脚用于显示屏的并口显示模式,如果确需增加RTC功能,必须要求显示屏支持SPI模式。 另外由于修改还会对两个按键造成影响,需要重新定义按键,因此软件软件环境要求固件版本为1.58以上。具体要求如下: (一)主板要求 升级RTC功能一般要求0.4以上版本的pcb。国内PCB 的主要版本为0.4、0.5、0.6以及BI3MEK设计的0.5、0.6版本PCB。官方PCB(0.4-0.6)如要升级RTC功能,均要修改硬件。 BI3MEK设计的0.5版本与官方0.5版本修改方法相同,但是布局不同,0.6版本PCB直接集成了本文所述的时钟功能,无需任何更改。 智能电表实时时钟技术综述 智能电表实时时钟技术综述 摘要:高精度实时时钟芯片/模块作为智能电表中重要的功能模块,近年成为智 能电表领域中的研究热门。其具有低功耗、高计时精度的特点,是智能电表中伴随整个电表寿命的模块。围绕智能电表领域近年来对实时时钟性能和技术的研究,对实时时钟技术进行分析,主要包含晶体封装在芯片内部、晶体作为芯片外部分立元器件、无晶体实时时钟等方面。 关键词:智能电表;实时时钟;晶体;ADC;全温区 0引言 实时时钟(Real-Time Clock,RTC)在智能电表中具有重要的作用,其为电能表 计费、计时,以及在此基础上的智能化功能提供了精准的时间保障。通常的实时时钟芯片需要在电表的市电环境和电池环境下都可以正常可靠地工作,所以其功耗的高低、工作电压范围对电表寿命有较大影响;同时在实现智能电表的功能例如远程抄表、分时电价等方面,需要时钟有极高的精准度;由于电表的应用环境分布于我国的大江南北,气候带跨度较大,在这种环境中需要芯片具有全温区工作的能力。国网智能电表对于实时时钟芯片、模块的需求每年在六千万以上,产值约为两亿元人民币。所以对实时时钟技术的研究具有很高的价值及意义。 1实时时钟技术发展现状 实时时钟(Real-Time Clock,RTC)技术最早由32.768kHz晶体振荡器[1]模块衍生而来,很多研究致力于对BT-Cut晶体进行温度补偿,以达到高精度的实时时钟,由于BT-Cut32.768kHz晶体具有类抛物线型的温度曲线,所以很多研究围绕对晶体温度曲线的补偿展开;由于通常的RC振荡器以及其他形式的模拟自激发振荡器在频率的精度方面都有较大差异,难以将低频振荡电路调整到ppm(Point per Million)数量级的频率精度,因受半导体工艺影响较大,振荡器本身的工业生产会存在较多问题,同时需要较高的封装测试成本维持量产良品率,所以CMOS工艺RC振荡器在高精度RTC设计中一直未被广泛采用。MEMS振荡器在近些年开始发展,逐步针对RTC进行设计,但产品的成熟性还有待验证[2-3]。 智能电表中RTC主要负责提供高精准度的时钟以及基本的日历功能,目前RTC时 多通道高精度模数转换器AD7718原理与应用 解放军信息工程大学信息工程学院六系(450002)陈铖武安河 摘要:本文从外部引脚和内部可编程寄存器两方面讲解了多通道高精度模数转换器AD7718,并通过一个24bits分辨率的数据采集电路介绍了AD7718的应用。 关键词:模数转换器 AD7718 数据采集 The Principle And Application Of 10-Channel 24-Bit Resolution Σ-Δ ADCs AD7718 Institute of Information Engineering, Information Engineering University of PLA, Zhengzhou 450002,China Chen Cheng, Wu AnHe Abstract: The AD7718 is a 10-channel 24-bit resolution Σ-ΔAnalog To Digital Converter. This paper presents firstly its pin and consist, and then designs a data acquisition scheme. Key Words: ADC, AD7718, Data Acquisition 1 概述 在低频测量应用中,AD7718是一个单电源供电(+3V或+5V)的完整前端。其内部结构如图1所示。从图中可以看出片内有一个带PGA(Programmable Gain Amplifier,可编程增益放大器)的Σ-Δ型ADC(Analog to Digital Converter,模数转换器)。ADC的分辨率为24 bits ,PGA的范围为20~27,8档可编程。所以,AD7718能直接转换范围在20mV~2.56V之间的输入信号而无须信号调理电路。AD7718片内还有一个多路开关MUX,可以将模拟输入配置成4或5通道差分输入,也可以配置成8或10通道伪差分输入。AD7718需要外接32KHZ晶体,片内PLL通过它产生所需要的工作时钟。 图1 AD7718的内部功能框图 第三章 高精度逐次逼近ADC 设计分析 第二章已经简单介绍了逐次逼近ADC 的原理,尽管其工作原理比较简单,但是具体的实现结构多种多样。其中按照内部DAC 的实现方式大概可以分为电压定标、电流定标和电荷定标三种结构。电压定标DAC 是指基于开关树电阻串分压结构,这种结构在实现较高精度时总的电阻阻值很大,会占用很大面积,所以通常很少用来实现高精度的数模转换。电流定标DAC 是指在Bipolar 工艺中比较常用的R-2R 结构,这种结构避免了电阻比值范围大的缺点。但由于CMOS 工艺中电阻占用面积较大,而且电阻的阻值精确性较双极性工艺低,电阻网络还存在较大的静态功耗,所以在高精度逐次逼近ADC 中也已经很少采用R-2R 结构。电荷定标DAC 是目前最常用的一种结构,它是基于电容阵列电荷再分配实现数模转换。由于CMOS 工艺中电容之间的匹配高于电阻匹配,所以这种结构可以实现较高的精度。另外,由于这种结构是基于开关电容方式,因此不存在静态功耗,所以已经成为目前SAR ADC 的主流结构。因此,本文从电荷再分配DAC 结构讲起,也分析了电阻电容混合结构DAC 结构,并重点介绍了带失调消除技术的高精度比较器的设计以及误差自动校准算法。最后,还对其它影响A/D 转换器的因素如噪声、开关非理想效应作了分析。 3.1 SAR ADC 中的高精度DAC 模块 1975年James L. McCREARY 首次提出将电荷再分配技术[23]应用到逐次逼近ADC 的设计当中,该技术是基于二进制加权电容阵列,利用电容的电荷再分配完成二进制搜索算法,由于该结构功耗小,而且不需要额外的采样保持电路,因而成为了目前逐次逼近ADC 中最常用的一种结构。然而由于在高精度应用中,最低位电容和最高位电容之间存在很大的比值,例如对于12位精度,最大电容和最小电容的比值2048:1,这必然将占用很大的芯片面积。解决这个问题的方法主要有两种,一种是采用分段电容阵列结构,另外一种是采用电阻电容混合结构。 3.1.1 分段电容阵列结构DAC 模块 文献[24]中提出了一种分段电容DAC 结构,该结构中由MSB 电容阵列和LSB 电容阵列通过一个耦合电容s C 级联,其中耦合电容s C 与MSB 电容阵列总电容MSB C 和 Σ-Δ转换器的特点是将绝大多数的噪声从动态转移到阻态,因而Σ-Δ转换器通常被用于对成本与精度有要求的低频场合。CS1232是芯海科技公司自主设计的一款高精度模数转换器(ADC),采用先进的3阶Σ-Δ 转换技术,可用于低电平、高精度测量,尤其适用于衡器领域,软件和硬件上不需要做任何修改,即可完全兼容于TI公司的ads1232。 CS1232的有效精度达到23.5位,可以在3.3V-5.5V的电压范围内正常工作,工作电压范围宽,并且内置4.9152M晶振,无需外部提供时钟信号,如果同时运行多个芯片,还可以使用外部时钟。通过控制PDWN引脚为低电平,可以使芯片进入掉电工作模式,功耗电流仅1μA。片内有两路差分通道,可用于多通道测量。片上内置低噪声的仪用放大器,最高128倍,可以直接测量幅度较小的微小信号。输出速度可以选择10Hz或80Hz,采用10Hz的数据速率时,可拟制50Hz和60Hz的干扰信号。CS1232的增益温漂约2pp/℃,并内置温度传感器,可以监测环境温度。 关键特性及结构 CS1232包括一个高性能Σ-ΔADC、低噪声放大器(PGA)、多路复用器、时钟、校准寄存器和串行外围接口,图1为CS1232的内部结构图。 CS1232内置一路Σ-Δ ADC,ADC采用三阶Σ-Δ调制器,通过低噪声仪用放大器结构实现PGA放大,PGA=1时,有效分辨率23.5位;PGA=128时,有效分辨率可达21位,内部放大器具有低噪声、低温漂等优点。CS1232的参数配置都通过外部引脚控制,无需寄存器编程。 图1: CS1232的内部结构图。 典型应用设计 传统的精密数据转换器解决方案不能兼备低噪声和低功耗的特性,而CS1232因为具有功耗低、噪声小、温漂系数小等特点,特别适合于衡器仪表、电子天平、数字传感器等小信号测量领域。图2给出了CS1232的仪表方案典型应用电路。 图2:采用CS1232的仪表方案典型应用电路。 图2中的传感器是电阻应变式传感器。根据电阻应变式传感器的原理,四片应变片构成全桥桥路,在电桥供电端施加恒定的直流电压,则电桥输出端的电压将与其上所承受的压力成正比,由此可根据输 关于实时时钟模块DS1302的介绍 DS1302是由美国DALLAS公司推出的具有涓细电流充电能力的低功耗实时时钟芯片。它可以对年、月、日、周、时、分、秒进行计时,且具有闰年补偿等多种功能。DS1302工作原理DS1302 工作电压为2.0V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个318的用于临时性存放数据的RAM寄存器。DS1302是DS1202的升级产品,与DS1202兼容,但增加了主电源/后备电源双电源引脚,同时提供了对后备电源进行涓细电流充电的能力。DS1302主要性能指标DS1302实时时钟芯片广泛应用于电话、传真、便携式仪器等产品领域,他的主要性能指标如下: 1、DS1302是一个实时时钟芯片,可以提供秒、分、小时、日期、月、年等信息,并且还有软年自动调整的能力,可以通过配置AM/PM来决定采用24小时格式还是12小时格式。 2、拥有31字节数据存储RAM。 3、串行I/O通信方式,相对并行来说比较节省IO口的使用。 4、DS1302的工作电压比较宽,大概是2.0V~5.5V都可以正常工作。采用双电源供电,当主电源比备用电源高0.2V时,由主电源供电,否则采用备用电源,一般是一个纽扣电池。 5、DS1302这种时钟芯片功耗一般都很低,它在工作电压2.0V的时候,工作电流小于300nA。 6、DS1302共有8个引脚,有两种封装形式,一种是DIP-8封装,芯片宽度(不含引脚)是300mil,一种是SOP-8封装,有两种宽度,一种是150mil,一种是208mil。 DS1302引脚及定义这是单字节写入的时序图,可见,先拉高使能端,进行使能选择,然后在时钟上升沿写入一个字节。 DS1302在进行读写操作时最少读写两个字节,第一个是控制字节,就是一个命令,说明是读还是写操作,第二个时需要读写的数据。 对于单字节写,只有在SCLK为低电平时才能将CE 置高电平,所以刚开始将SCLK 置低,CE置高,然后把需要写入的字节送入IO口,然后跳变SCLK,在SCLK下降沿时,高精度Delta-Sigma AD转换器的原理及其应用

Mchf支持实时时钟教程

智能电表实时时钟技术综述

多通道高精度模数转换器AD7718 原理与应用

一种高精度逐次逼近模数转换器的研究与设计_(优选.)

高精度模数转换器(ADC)

关于实时时钟模块DS1302的介绍