第19章 串行外围设备接口(SPI)

第19章串行外围设备接口(SPI)

19.1 概述

串行外围设备接口(SPI serial peripheral interface)允许MPC8349E与其他PowerQUICC系列芯片、MC68360、M68HC11和M68HC05微控制器系列以及其他系列设备交换数据。可以将SPI用于与外围设备的通信,例如EEPROM、实时时钟、A/D转换器和ISDN设备等。

SPI是一个全双工、同步、面向字符的通道,支持四线接口(接收、发送、时钟和从选择)。SPI部件由发送器和接收器单元、一个独立的波特率发生器和一个控制单元组成。发送器和接收器单元使用相同的时钟。这个时钟在主模式下源自SPI波特率发生器,在从模式下由外部提供。在SPI传输过程中,同时发送和接收数据。

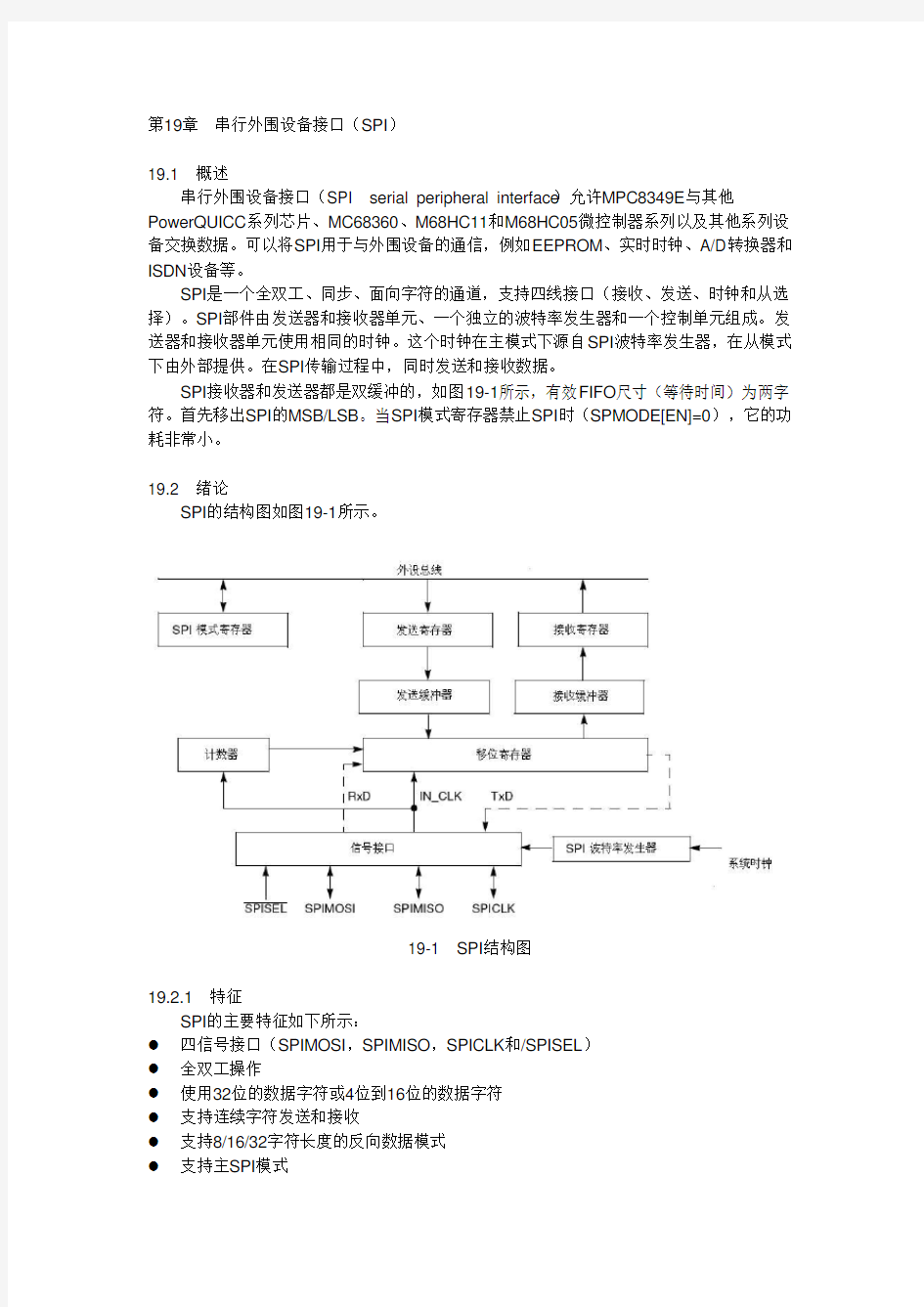

SPI接收器和发送器都是双缓冲的,如图19-1所示,有效FIFO尺寸(等待时间)为两字符。首先移出SPI的MSB/LSB。当SPI模式寄存器禁止SPI时(SPMODE[EN]=0),它的功耗非常小。

19.2 绪论

SPI的结构图如图19-1所示。

19-1 SPI结构图

19.2.1 特征

SPI的主要特征如下所示:

●四信号接口(SPIMOSI,SPIMISO,SPICLK和/SPISEL)

●全双工操作

●使用32位的数据字符或4位到16位的数据字符

●支持连续字符发送和接收

●支持8/16/32字符长度的反向数据模式

●支持主SPI模式

●支持多主环境

●最大时钟频率在主模式下为(系统时钟频率/4),在从模式下为(系统时钟频率/2)

●独立的可编程波特率发生器

●用于测试的本地回送能力

●漏极开路输出支持多主配置

19.2.2 SPI发送和接收过程

由于SPI是面向字符通信单元,因此由核负责是打包和解包接收和发送的帧。一帧包含一个完整的SPI传输会话中发送或接收的所有字符,从写入SPITD寄存器的第一个字符开始到设置SPCOM[LST]之后发送的最后一个字符为止。更多的信息参看19.4.1.4节“SPI命令寄存器(SPCOM)”。

核通过读SPI接收数据保持寄存器(SPIRD)接收数据,然后SPI清除非空的SPIE[NE]以释放SPIRD寄存器,为下一次接收操作做准备。核通过将数据写入SPI发送数据保持寄存器(SPITD)以发送数据,然后SPI清除SPI事件寄存器(SPIE)的非满位(NF),指示SPITD 寄存器包含待发送的字符。当待发送的下一个字符为当前帧中最后一个字符时,核置位SPCOM[LST],然后将最后一个字符写入SPITD。

SPI核握手协议可以通过轮询或中断来实现。当采用轮询方式时,核按照预定义的频率读SPIE,并且根据SPIE位的值进行操作。轮询频率取决于SPI串行信道的频率。当采用中断机制时,置位SPIE的非满(NF)或非空(NE)位引起到e300核的中断。然后核读SPIE,并根据SPIE位的值进行操作。三个基本的发送和接收模式为主、从和多主模式。

注意

当非满(NF)和非空(NE)位均被置位时,e300核应在发

送新数据前读取接收的数据。

SPMODE[LEN]确定硬件发送的字符的长度。核负责位处理,将数据打包或者解包成合适的字符长度。更多信息参看表19-4中SPMODE[LEN]的说明。

19.2.3 操作模式

可以把SPI设定在在单主设备或多主设备环境下工作。本节介绍单主设备配置时的SPI 主和从操作。同时也讨论了多主设备环境下SPI的操作。

下面几节总结了SPI支持的主要操作模式。

19.2.3.1 作为主设备的SPI

在主设备模式下,SPI发送消息到从外设,从外设同时发回应答。带有多个从设备的单主设备可以使用通用并行I/O信号有选择地启用从设备,如图19-2所示。为了消除单主设备

环境下的多主设备的错误,应通过外部上拉强制主设备的SPISEL输入无效。

图19-2 单主设备/多从设备的配置

为了开始交换数据。e300将待发送数据写入SPITD寄存器。然后SPI为每一个字符在SPICLK产生可编程时钟脉冲。将Tx数据在SPI主出从入(SPIMOSI)移出,同时将Rx数据在SPI主入从出(SPIMISO)移入。在发送过程中,无论何时SPI发出请求,核都负责提供数据,从而保证操作的顺畅。在最后一个数据(LST命令和紧接其后的数据)发送完毕后,写入SPITD的第一个字符作为SPI的开始命令。

SPI连续地发送和接收字符,直到SPCOM[LST]被置位或者有错误发生。

只要发送缓冲区不满,SPI就置位SPIE[NF]向中断控制器发送可屏蔽中断。在发送完最后一个字之后,SPI也置位NF。作为回应,核应读取与最后一个字相关的异常标志。只要接收缓冲区填充了数据,SPI就置位SPIE[NE],向中断控制器发送可屏蔽中断。

19.2.3.2 作为从设备的SPI

在从模式下,SPI设备接收来自SPI主设备的信息并且同时发送回答。从设备的SPISEL 必须在识别出Rx时钟之前有效。一旦SPISEL信号有效,SPICLK就成为从主设备到从设备的输入。SPICLK可以为从DC到系统时钟/2之间的任意频率。

核心将待发送数据送入SPITD寄存器,为数据传输做准备。一旦SPISEL有效,从设

备将数据从SPIMISO移出,从SPIMOSI移入。SPI置位SPI寄存器的NF位,当满缓冲完成发送和接收时或者在出现错误之后,发出可屏蔽中断。SPI连续接收,直到SPISEL信号无效。

发送连续进行,直到没有更多的数据可用或者SPISEL无效。一旦SPISEL重新有效,并且SPICLK开始翻转,就继续发送。缓冲区中的字符都发送了之后,只要SPISEL保持有

效,SPI就发送1。

19.2.3.3 多主设备环境下操作的SPI

SPI可以工作在多主设备环境中,此时所有的SPI设备都被连接到同一个总线上。在这种配置中,所有SPI设备共享SPIMOSI、SPIMISO和SPICLK信号,但是SPISEL输入是独立连接的,如图19-3所示。某一时刻仅有一个SPI设备可以作为主设备——其他所有的SPI 设备必须为从设备。当把一个SPI配置成主设备时,如果它的SPISEL输入有效,将产生多

主设备错误,因为有多个SPI设备成为总线主设备。SPI置位SPI事件寄存器中的SPIE[MME]并且向核发出可屏蔽中断。它还禁止SPI操作和SPI信号的输出驱动器。在重新使用SPI之前,核心必须清除SPMODE[EN],纠正错误,并清除SPIE[MME]。

注意:

1.所有信号都是漏极开路的。

2.对于两个以上主设备的多主设备配置,SPISEL和SPIE[MME]不能检测到所有可能的冲突。

3.由软件负责SPI总线的仲裁(例如使用如令牌传递)。

4.SELOUTx信号用软件使用通用I/O信号实现。

图19-3 多主设备配置

SPI支持的最大稳定数据速率为系统(csb)时钟/50。但是SPI可以高得多的速率传输单个字符——在主机模式下为系统时钟/4,在从机模式下为系统时钟/2。在多个字符之间应插入间隔,以保证不超过最大稳定数据速率。

19.3 外部信号说明

SPI的四线接口包括发送、接收、时钟和从选择。

19.3.1 概述

表19-1列出了信号的属性。

表19-1 信号属性

19.3.2 详细信号说明

表19-2详细说明了信号。

在单主设备或者多主设备环境模式下,可以把SPI配置成从设备或者主设备。主SPI 利用SPI波特率发生器(BRG)生成传输时钟SPICLK。SPI BRG从时钟合成器产生的系统时钟中获取输入。

SPICLK是一个门控时钟,仅在数据传输时有效。SPICLK相位和极性的四种组合可以由时钟反向(SPMODE[CI])和时钟相位(SPMODE[CP])寄存器位配置。还可以把SPI 配置为漏极开路,以支持多主设备配置,此时共享的SPI信号由SPI设备或外部SPI设备驱动。

SPI 主设备入从设备出SPIMISO信号作为主设备的输入和从设备的输出。反之,主设备出从设备入SPIMOSI信号作为主设备的输出和从设备的输入。这些信号的双重功能允许多主设备环境下的SPI之间使用相同的硬件配置进行通信。

●当SPI为主设备时,SPICLK是时钟输出信号,它从SPIMISO移入接收到的数据,

将发送的数据移出到SPIMOSI。SPI主设备必须输出一个从设备选择信号,通过

使用独立的通用I/O信号使能SPI从设备。当把SPI设备配置成主设备时,使

SPISEL有效则导致错误。

●当SPI为从设备时,SPICLK是时钟输入信号,它从SPIMOSI移入接收到的数据,

将发送的数据通过SPIMISO移出。SPISEL是到SPI从设备的使能输入信号。在

多主设备环境下,SPISEL(始终作为输入)还用来检测有多个主设备操作这样

的错误。

19.4 内存映射/寄存器定义

表19-3包含SPI的映射到内存空间的寄存器。表中所列的地址为到SPI基址的偏移量,同第二章“内存映射”中定义的那样。

19.4.1 寄存器说明

19.4.1.1 SPI模式寄存器(SPMODE)

SPMODE控制SPI操作的模式和时钟源,如图19-4所示。

图19-4 SPMODE-SPI模式寄存器表19-4说明了SPMODE的字段。

表19-4 SPMODE字段说明

图19-5显示了SPI的传输格式,其中SPICLK在传输的中间开始翻转(SPMODE[CP]=0)。

图19-5 SSPMODE[CP]=0时的SPI传输格式

图19-6显示了SPI的传输格式,其中SPICLK在传输的开始处开始翻转(SPMODE[CP]=1)。

图19-6 SPMODE[CP]=1时的SPI传输格式

19.4.1.2 SPI 事件寄存器(SPIE)

SPI事件寄存器(SPIE)产生中断并报告SPI所识别的事件。当识别了某个事件时,SPI置位对应的SPIE位。SPIE位通过写入‘1’清除,写入‘0’没有作用。置位SPI屏蔽寄存器(SPIM)中的位允许对应的中断,清除一位则屏蔽对应的中断。必须在核清除内部中断请求之前清除清除未屏蔽的SPIE位。图19-7显示了SPI事件寄存器。

图19-7 SPIE-SPI事件寄存器

表19-5说明了SPIE的字段。

表19-5 SPIE字段说明

19.4.1.3 SPI屏蔽寄存器(SPIM)

SPI屏蔽寄存器(SPIM)如图19-8所示,它允许/屏蔽被SPI识别的事件的中断。当识别了一个事件时,SPI置位对应SPI位。置位SPIM位允许对应的中断,清除SPIM位则屏蔽对应的中断。必须在核清除内部中断请求之前清除清除未屏蔽的SPIE位。

图19-8 SPIM-SPI屏蔽寄存器

表19-6说明了SPIM的字段。

19.4.1.4 SPI命令寄存器(SPCOM)

SPI命令寄存器(SPCOM)用于结束SPI操作,如图19-9所示。

图19-9 SPI命令寄存器(SPCOM)

表19-7说明了SPCOM的字段。

表19-7 SPCOM字段说明

19.4.1.5 SPI发送数据保持寄存器(SPITD)

SPITD保持待发送的数据。SPMODE[LEN]定义每个字符的位数。每次SPIE[EN]置位时,如果SPIE中不报错,核就可以向SPITD写入另一个数据字符。在帧的末尾,核应置位SPCOM[LST]并准备好数据的最后一个字符。图19-10显示了SPI发送数据保持寄存器。

图19-10 SPI发送数据保持寄存器。

表19-8给出了SPI发送数据保持寄存器的字段说明。

表19-8 SPI发送数据保持寄存器

19.4.1.6 SPI接收数据保持寄存器(SPIRD)

SPIRD用于从SPI信道接收数据字符,如图19-11所示。每次SPIE[NE]置位时,核可以读SPIRD。

图19-11 SPI接收数据保持寄存器

表19-9给出了SPI接收数据保持寄存器的字段说明。

19.4.1.6.1 反向模式SPMODE[REV]举例

在反向数据模式(SPMODE[REV]=1)和正常数据模式(SPMODE[REV]=0)中,数据在接收完毕后被送入SPIRD。下面为8位字符长度(SPMODE[LEN]=7)的实例。

图19-12 SPMODE[REV]=0 SPMODE[LEN]=7 首先发送LSB举例

图19-13 SMODE[REV]=1 SPMODE[LEN]=7 首先发送MSB举例

图19-14 SMODE[REV]=1 SPMODE[LEN]=15 首先发送MSB举例

图19-15 SPMODE[REV]=0 SPMODE[LEN]=15 首先发送LSB举例

19.5 初始化/应用信息

下面几节介绍SPI主设备和从设备编程实例。

19.5.1 SPI主设备编程实例

以下步骤将SPI初始化为高速工作的主机模式:

1.如果需要,配置并行I/O信号,作为SPI选择输出信号

2.向SPIE中写入0xFFFFFFFF清除以前的所有事件。配置SPIM允许所有期望的SPI 中断。

3.配置SPMODE允许正常操作(非回送)、主设备模式、SPI启用、字符长度和可能的最快速度。

4.向SPITD写入待发送的第一个字符。

19.5.2 SPI从设备编程实例

以下为SPI处于从模式时的初始化步骤示例。本例和SPI主设备实例很相似,不同点是采用SPISEL代替I/O信号。

1.向SPIE写入0xFFFFFFFF清除以前的所有事件。

2.配置SPIM允许所有期望的SPI中断。

3.配置SPMODE允许正常操作(非回路)、从设备模式、SPI启用和字符长度。

4.向SPITD写入待发送的第一个字符,确保一旦主设备开始传输时SPI准备就绪。