2019“计算机电路基础”作业

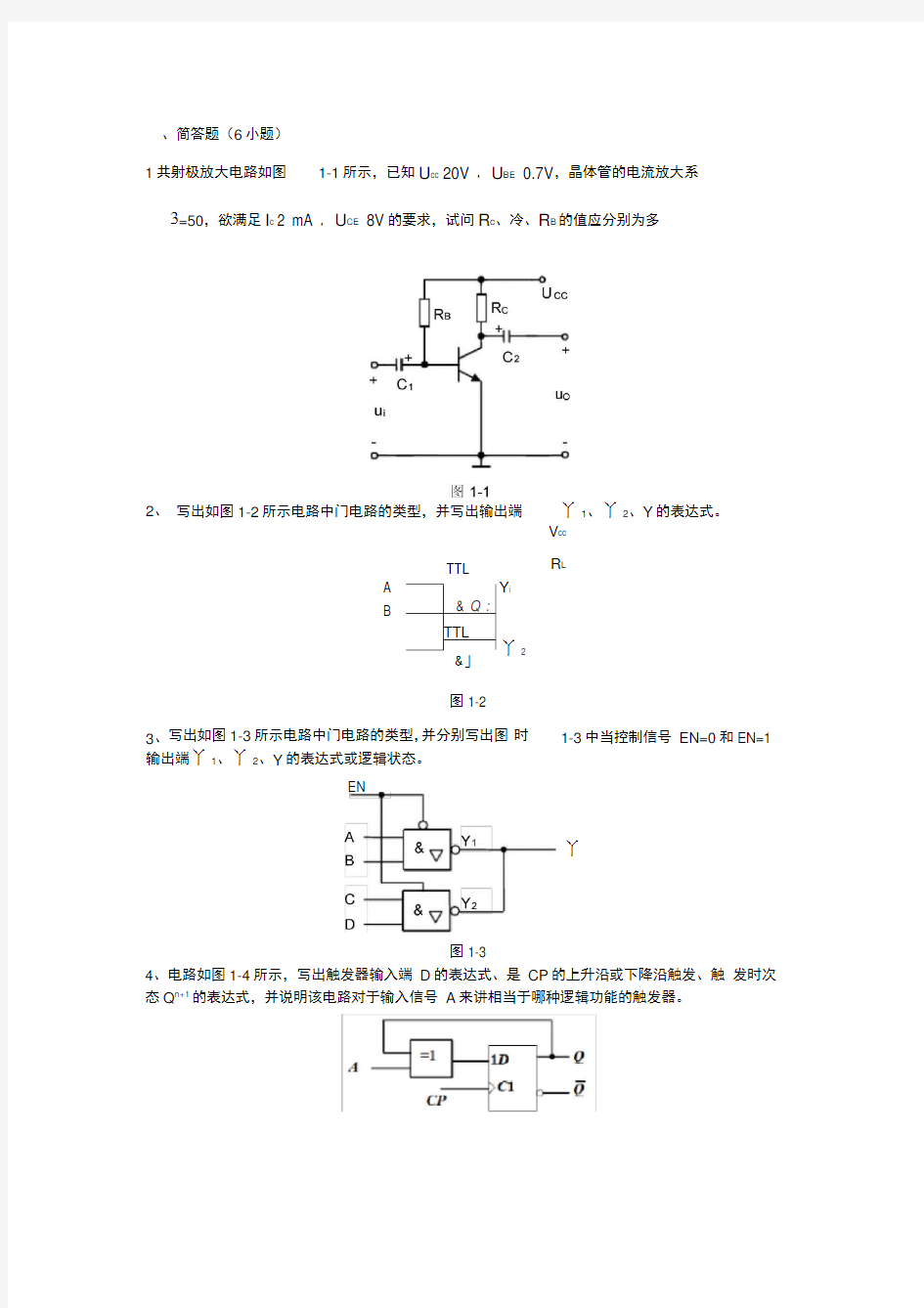

、简答题(6小题) 1共射极放大电路如图

1-1所示,已知U cc 20V , U BE 0.7V ,晶体管的电流放大系

3=50,欲满足I c 2 mA , U CE 8V 的要求,试问R c 、冷、R B 的值应分别为多

写出如图1-2所示电路中门电路的类型,并写出输出端

丫1、丫2、Y 的表达式。

V cc

4、电路如图1-4所示,写出触发器输入端 D 的表达式、是 CP 的上升沿或下降沿触发、触 发时次态Q n+1的表达式,并说明该电路对于输入信号 A 来讲相当于哪种逻辑功能的触发器。

2、 R L

& Q :

TTL

Y i

丫2

图1-2

写出如图1-3所示电路中门电路的类型,并分别写出图 时输出端丫1、丫2、Y 的表达式或逻辑状态。 3、 1-3中当控制信号 EN=0和EN=1

TTL

A B

&」 EN

丫

图1-3

5、电路如图1-5所示,写出触发器输入端J、K的表达式、是CP的上升沿或下降沿触发、触发时输出次态Q n+1的表达式,并说明该电路对于输入信号A来讲相当于哪种逻辑功能的触发器。

A 一* -----------

- 1 0—-

CP

图1-5

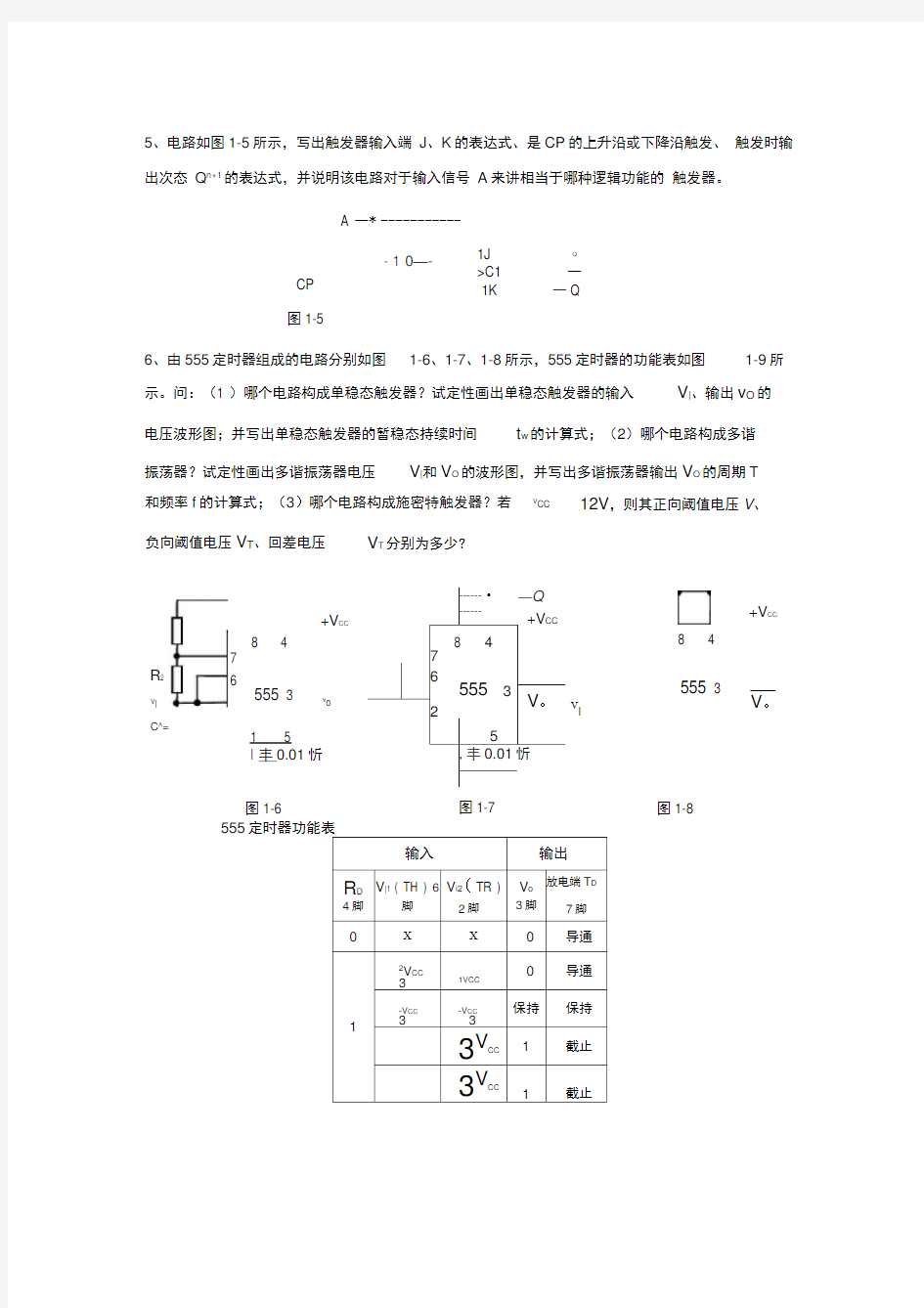

6、由555定时器组成的电路分别如图1-6、1-

7、1-8所示,555定时器的功能表如图1-9所示。问:(1 )哪个电路构成单稳态触发器?试定性画出单稳态触发器的输入V|、输出v O的

电压波形图;并写出单稳态触发器的暂稳态持续时间t w的计算式;(2)哪个电路构成多谐

振荡器?试定性画出多谐振荡器电压V|和V O的波形图,并写出多谐振荡器输出V O的周期T

555定时器功能表

输入输出

R D 4脚V|1 ( TH ) 6

脚

V i2( TR )

2脚

V o

3脚

放电端T D

7脚

0X X0导通

12V CC

31VCC

0导通

-V CC

3

-V CC

3

保持保持

3V CC1截止

3V CC

1截止

1J Q

>C1 一

1K 一Q

和频率f的计算式;(3)哪个电路构成施密特触发器?若V CC 12V,则其正向阈值电压V、负向阈值电压V T、回差电压V T分别为多少?

V I C^=

555 3

------ ?

------

―Q

+V CC

8 4

7

6

5553

2

V。

5

,丰0.01忻

+V CC

555 3

V。图1-6 图1-8

R2 7

6

8 4

图1-7

v o

+V CC

1 5

I 丰0.01忻

V I

8 4

二、直流电路计算(2小题)

1、电路如图2-1所示,试用电压源与电流源等效变换方法或戴维南定理求电流

2、电路如图2-2所示,试用结点电压法或支路电流法计算电压

3A 4

—

+

图2-2

与或式变换为与非-与非式。

排列)将Y (A, B,C,D )化简为最简与或式,并进一步将该最简与或式变换为与非

6VI +

()()

+

12V

2A

三、逻辑函数化简与变换(

2小题)

1、用公式法将逻辑函数 Y

ABC AB AB BC

化为最简与或式,并进一步将该最简

2、已知 Y (代 B,C,D) A C D

ABCD ABCD ,给定约束条件为

ABCD ABCD ABCD ABCD ABCD

ABCD 0,利用卡诺图(按图3-1 所示

-与非式。

U 。

图3-1

四、组合逻辑电路设计(3小题) 1设计一个全加器,设输入为 A 、B 、C ,输出为S (和)、C O (进位)。

(1) 列出真值表;

(2) 写出输出S 和C O 的最小项之和表达式;

(3) 利用卡诺图分别将 S 和C O 化为最简与或表达式;

(4) 画出用门电路构成的最简的逻辑电路图,假设各类型门电路齐备。 2、8选1数据选择器74LS151的功能表和逻辑符号分别如图

4-1、4-2所示,试用74LS151

实现组合逻辑函数 Y (A,B,C ) ABC ABC ABC ,画出相应的连线图。

74LS151的功能表

图4-1

图4-2

3、试用3线-8线译码器

74LS138和少量门电路,实现逻辑函数

R (A,B,C ) A 和

F 2(A, B,C ) A B 。74LS138的功能表和逻辑符号分别如图

4-3、4-4所示。

图4-4

输入

输出

S

A 2 A 1 A 0

丫

1

X X X

0 0 0 D 。 0

1

D 1

1 1 0 D e

1 1 1

D 7

Y

- S 2 10 01 2 3 4 5 67 AAA DDDDDDDD

输入

输出

0 S+ S

$

A

2

A 1

A

丫0 丫1 丫2

丫3 丫4 丫5 丫6 丫7

X X X X 1 1 1 1 1 1 1 1 X

1 X X

X

1 1 1

1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 1

1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 1

0 1 1 0 1 1 1 1 1 1 0 1 1

1

1 1

1 1 1

1

1

1

1 0

A S

52

53

Y o

丫

1

丫

2

丫

3

丫

4

丫

5

丫

图4-3 74LS13的功能表

CP

R

D

LD EP ET

功能 X

0 X X X 直接置零 r

1 0 X

X

预置数 X 1 1 0

1 保持 X

1 1

X

0 保持 (但

C=0) r 1

1

1

1

计数

EP D o D 1 D 2 D 3 C ET 74LS161 LD

>CP

Q o Q 1 Q 2 Q 3 R D

图5-4

五、时序逻辑电路分析和设计(3小题)

1逻辑电路如图5-1所示,各触发器的初始状态均为“

0”试分析:(1 )该计数器是同步

计数器还是异步计数器? ( 2)写出各触发器的驱动方程和状态方程; (3)按Q 2Q 1Q 0顺序

列出完整的状态转换表或画出完整的状态转换图;

(4)说明是几进制计数器,能否自启动。

图5-1

2、由十六进制计数器 74LS161和门电路构成的电路如图

5-2所示,74LS161的功能表和逻

辑符号分别如图5-3、5-4所示。(1)画出电路在 N=0时的状态转换图,并说明电路在 N=0 时是多少进制的计数器;(2)画出电路在N=1时的状态转换图,并说明电路在 N=1时是多 少进制的计数器。

ET D o D 1 D 2 D 3 C

EP

74LS161 一

LD

Q o

Q 1 Q 2 Q 3 R D

图5-2

74LS161的功能表

CP —、CP

计数脉冲 __ ____

计数脉冲_ 「「一 .

N

图5-3

3、试用同步4位二进制计数器 74LS161和尽量少的门电路设计一个 12进制计数器,已知

输入时钟为 CLK 。要求:采用反馈清零法,并写出 R D 的表达式,有关引脚不允许悬空。

74LS161的功能表和逻辑符号分别如图

5-5、图5-6所示。

图5-6

EP D o D 1 D 2 D 3 C

ET

74LS161 LD

CP

Q o Q 1 Q 2 Q 3 只。