第11章 MCS-51单片机系统扩展-第1部分 - 1

第十一章 MCS-51单片机系统扩展

11.1 8051/8751的最小系统

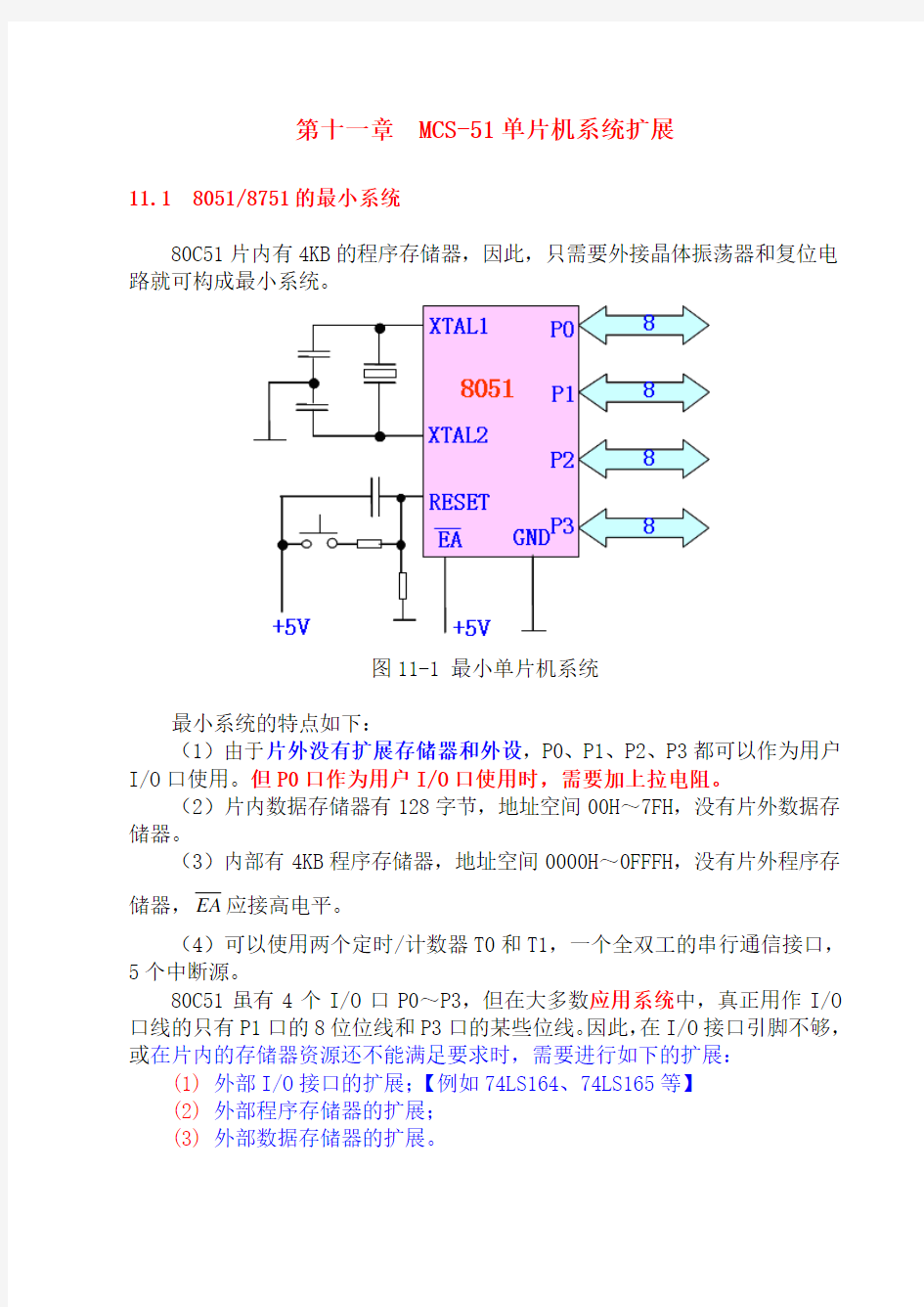

80C51片内有4KB的程序存储器,因此,只需要外接晶体振荡器和复位电路就可构成最小系统。

图11-1 最小单片机系统

最小系统的特点如下:

(1)由于片外没有扩展存储器和外设,P0、P1、P2、P3都可以作为用户I/O口使用。但P0口作为用户I/O口使用时,需要加上拉电阻。

(2)片内数据存储器有128字节,地址空间00H~7FH,没有片外数据存储器。

(3)内部有4KB程序存储器,地址空间0000H~0FFFH,没有片外程序存储器,EA应接高电平。

(4)可以使用两个定时/计数器T0和T1,一个全双工的串行通信接口,5个中断源。

80C51虽有4个I/O口P0~P3,但在大多数应用系统中,真正用作I/O 口线的只有P1口的8位位线和P3口的某些位线。因此,在I/O接口引脚不够,或在片内的存储器资源还不能满足要求时,需要进行如下的扩展:

(1) 外部I/O接口的扩展;【例如74LS164、74LS165等】

(2) 外部程序存储器的扩展;

(3) 外部数据存储器的扩展。

11.2 系统扩展结构

单片机采用总线结构,使扩展易于实现,单片机系统扩展结构如图11-2所示。

图11-2 80C51单片机的系统扩展结构

从图11-2可以看出,系统扩展主要包括存储器扩展和I/O接口部件扩展。存储器扩展包括程序存储器扩展和数据存储器扩展。

系统扩展是以单片机为核心,通过总线把单片机与各扩展部件连接起来。因此,首先要利用单片机的I/O口构造系统总线。系统总线按功能通常分为3组,如图11-2所示。

(1)地址总线AB(Address Bus):用于发送CPU发出的地址信号,以便进行存储单元和I/O接口芯片中的寄存器的选择。

地址总线宽度为16位,由P0口经地址锁存器(通常用74LS373)提供地址低8位,P2口直接提供地址高8位,地址信号是由CPU发出的单方向信号。

存储器芯片的地址线的数目由芯片的容量决定。容量(Q)与地址线数目(N)满足关系式:2N

Q 。存储器芯片的地址线与单片机的地址总线(A0~A15,P0口为低8位(需用74LS373锁存),P2口为高8位)按由低位到高位的顺序顺次相接。

一般来说,存储器芯片的地址线数目少于单片机地址总线的数目,因此连接后,单片机的高位地址线(P2口)应该有剩余。剩余的地址线一般作为译码线,译码器的输出与存储器芯片的片选信号线(CS或CE)相接。片选

信号线CS或CE与单片机系统的译码器输出相接后,就决定了存储器芯片的

地址范围。

【P153】地址总线的低8位(A0~A7)由P0口提供,由于P0口是地址和数据分时使用,所以P0口输出的低8位地址必须用锁存器锁存,可以利用ALE 的下降沿将P0口输出的地址信息锁存,P2口提供高8位(A8~A15)地址信息。由于P2口不是地址和数据分时使用,而且P2口有锁存功能,所以P2口不需要加锁存器。

(2)数据总线DB(Data Bus):数据总线由P0提供,用于单片机与外部存储器之间或与I/O接口之间传送数据,数据总线是双向的。【由单片机P0口提供,和外部存储器芯片或与I/O芯片的数据口相连】

连接时,存储器芯片的数据线与单片机的数据总线(P0.0~P0.7)按由低位到高位的顺序顺次相接。【要注意顺序,例如ADC0809的数据线就不规范】【P154】数据总线与哪个外设进行数据通信,由CPU输出的地址信号决定,选中的芯片数据线与单片机的数据总线相连,未选中的芯片数据线与单片机总线处于三态高阻状态【相当于断开状态】。

(3)控制总线CB(Control Bus):控制总线是单片机发出的各种控制信号线。【例如:单片机的ALE、PSEN和P3口的WR、RD】

如何构造系统的三总线。

1.P0口作为低8位地址/数据总线

80C51受引脚数目限制,P0口既可作为低8位地址总线,又可用作数据总线(分时复用),因此,需增加一个8位地址锁存器【配合ALE信号线】。单片机访问外部扩展的存储器单元或I/O接口寄存器时,先发出低8位地址送地址锁存器锁存,锁存器输出作为系统的低8位地址(A7~A0)。随后,P0口又作为数据总线口(D7~D0),如图11-3所示。【发出的地址由ALE控制地址锁存器进行锁存】

2.P2口的口线作为高位地址线

P2口用作系统的高8位地址线,再加上地址锁存器提供的低8位地址,便形成了系统完整的16位地址总线。使单片机系统的寻址范围可以达到64KB。

(216=64K)

图11-3 80C51单片机扩展的片外三总线

3.控制信号线【控制信号线=P3口的第二功能线+控制引脚】【P154】除地址线和数据线外,还要有系统的控制总线。这些控制信号线有的就是单片机引脚的第一功能信号,还有的则利用P3口第二功能信号线。包括:(1)PSEN(29)为外扩程序存储器的读选通控制信号。例如对于程序存储器来说,具有输出允许控制线OE,它与单片机的PSEN信号线相连。在执行访问外部程序存储器指令时,PSEN(外部程序存储器选通)信号有效。【注意:读取EPROM中数据(指令)时,不用RD信号,而用PSEN】(2)RD(P3.7)和WR(P3.6)为外扩数据存储器和I/O的读、写选通控

制信号。例如对于数据存储器,一般都有输出允许控制线OE和写控制线WE,

它们分别与单片机的读信号线RD和写信号线WR相连。在访问外部数据存储器【包括I/O】指令时,由P3口自动产生读/写(RD/WR)信号,通过P0口

对外部数据存储器单元进行读/写操作。

(3)ALE(30)作为P0口发出的低8位地址锁存控制信号。

(4)EA(31)为片内、片外程序存储器的选择控制信号。

可见,80C51的4个并行I/O口,由于系统扩展的需要,真正作为通用I/O 引脚用的部分,就剩下P1口和P3口的部分引脚了。

11.3 地址空间分配和外部地址锁存器

11.3.1 存储器地址空间分配

在设计实际系统时,可能既需要扩展程序存储器,又需要扩展数据存储器,如何把片外的两个64KB地址空间分配给各个程序存储器、数据存储器芯片,使一个存储单元只对应一个地址,避免单片机发出一个地址时,同时访问两个单元,发生数据冲突。这就是存储器地址空间分配需要解决的问题。

单片机发出的地址用于选择某个存储器单元,如果外扩多片存储器芯片时,单片机就必须进行两种选择:一是:选中该存储器芯片,这称为“片选”,未被选中的芯片不能被访问(三态-高阻)。二是:在“片选”的基础上再根据单片机发出的地址来对“选中”芯片的某一单元进行访问,即“单元选择”。【相当于两级方式,一是选中该芯片,然后用地址选择存储单元】【相当于找人,先问住哪栋楼(片选),再问哪房间号(单元选择)】

【先找学校,系别,班级,再找人。学校、学号是唯一的对应人】

【实验A楼,203房间】

为了实现片选,存储器芯片都有片选引脚CE,还有多条地址线引脚,以

便进行单元选择。注意,“片选”和“单元选择”都是单片机通过地址线一次发出的地址信号来完成选择。

通常把单片机系统的地址线分为低位地址线和高位地址线,“片选”都是使用高位地址线(P2口的线)。实际上,16条地址线中的高、低位地址线的数目并不是固定的,只是习惯上把用于“单元选择”的地址线,称为低位地址线,其余的为高位地址线。

常用的存储器地址空间分配方法有两种:线选法和地址译码法。

1.线选法

线选法是直接利用系统的某一高位地址线(P2口的某一根线)作为存储

器芯片(或I/O接口芯片)的“片选(CE)”控制信号。为此,只需要把用到

的高位地址线与存储器芯片的“片选”端直接连接即可。【在DAC0832中】线选法优点是电路简单,不需要另外增加地址译码器硬件电路,成本低。缺点是可寻址的芯片数目受到限制。另外,地址空间不连续,每个存储单元的地址不唯一,这会给程序设计带来不便,只适用于外扩芯片数目不多的单片机系统的存储器扩展。【因为P2口的一根线对应一个芯片】

【前面有的例子中,如果只有一片外扩芯片,也可以直接把片选信号线直接接地,但是有多片的话,不能直接接地】

2.译码法

存储器芯片的地址线与单片机系统的地址线顺次相接后,利用剩余的高位地址线参加译码。

使用译码器对80C51单片机的高位地址线进行译码,译码输出作为存储器芯片的片选信号。这种方法能够有效地利用存储器空间,适用于多芯片的存储器扩展。常用的译码器芯片有74LS138(3线-8线译码器)、74LS139(双2线-4线译码器)和74LS154(4线-16线译码器)。

【139――24;154――416】

下面介绍常用的译码器芯片。

(1)74LS138

3-8译码器,有3个数据输入端,经译码后产生8种状态。引脚如图11-4所示,真值表见表11-1。由表11-1可见,当译码器的输入为某一固定编码时,其输出仅有一个固定的引脚输出为低电平,其余的为高电平。输出为低电平

的引脚就作为某一存储器芯片的片选信号CS或CE。

表11-1 74LS138真值表

注:1表示高电平,0表示低电平,×表示任意【C为高位,A为低位】【G1接高电平,/G2A和/G2B接低电平】

【G1、2

G B必须分别为:“1”、“0”、“0”】

G A、2

图11-4 74LS138引脚图

先看一个简单的例子:【已通过138】

#include

void Delay(unsigned int count) // 延时子函数

{ unsigned char i;

while(count--)

for(i=0;i<120;i++); // 延时1ms

}

void main()

{ P2 = 0x00;

while(1)

{ P2 = (P2+1)%8; // 结果分别为1,2,3,4,5,6,7,0 Delay(500);

}

}

(2)74LS139

双2线-4线译码器。这两个译码器完全独立,分别有各自的数据输入端、译码状态输出端以及数据输入允许端,其引脚如图11-5所示,真值表见表8-2(只给出其中一组)。

图11-5 74LS139引脚图

【/1G、/2G接低电平。B为高位,A为低位】

#include

void Delay(unsigned int count) // 延时子函数

{

unsigned char i;

while(count--)

for(i=0;i<120;i++); // 延时1ms

}

void main()

{

P2 = 0x00;

while(1)

{

P2 = (P2+1)%4; // 结果分别为1,2,3,0

Delay(500);

}

}

(3)74LS154

D、C、B、A:译码地址输入端(低电平有效),D为高位

G、2

G:选通端(低电平有效)

1

0~15:输出端(低电平有效)

功能表:

说明: H-高电平;L-低电平;X-任意;*-其他输出为高电平

#include

void Delay(unsigned int count) // 延时子函数

{

unsigned char i;

while(count--)

for(i=0;i<120;i++); // 延时1ms

}

void main()

{

P2 = 0x00;

while(1)

{ P2 = (P2+1)%16; // 结果分别为1,2,3,4,5,6,7,8 Delay(500); // 9,10,11,12,13,14,15,0

}

}