数电实验 数据选择器

实验三数据选择器

一:实验目的

1.掌握中规模数据选择器的逻辑功能测试方法

2.学习数据选择器的使用方法

3.熟练掌握仿真软件仿真调试实验电路的方法

二:实验仪器及器件

稳压电源,数字多用表,数字电路实验箱,数字电路仿真平台运行环境。

三:实验原理及操作技能

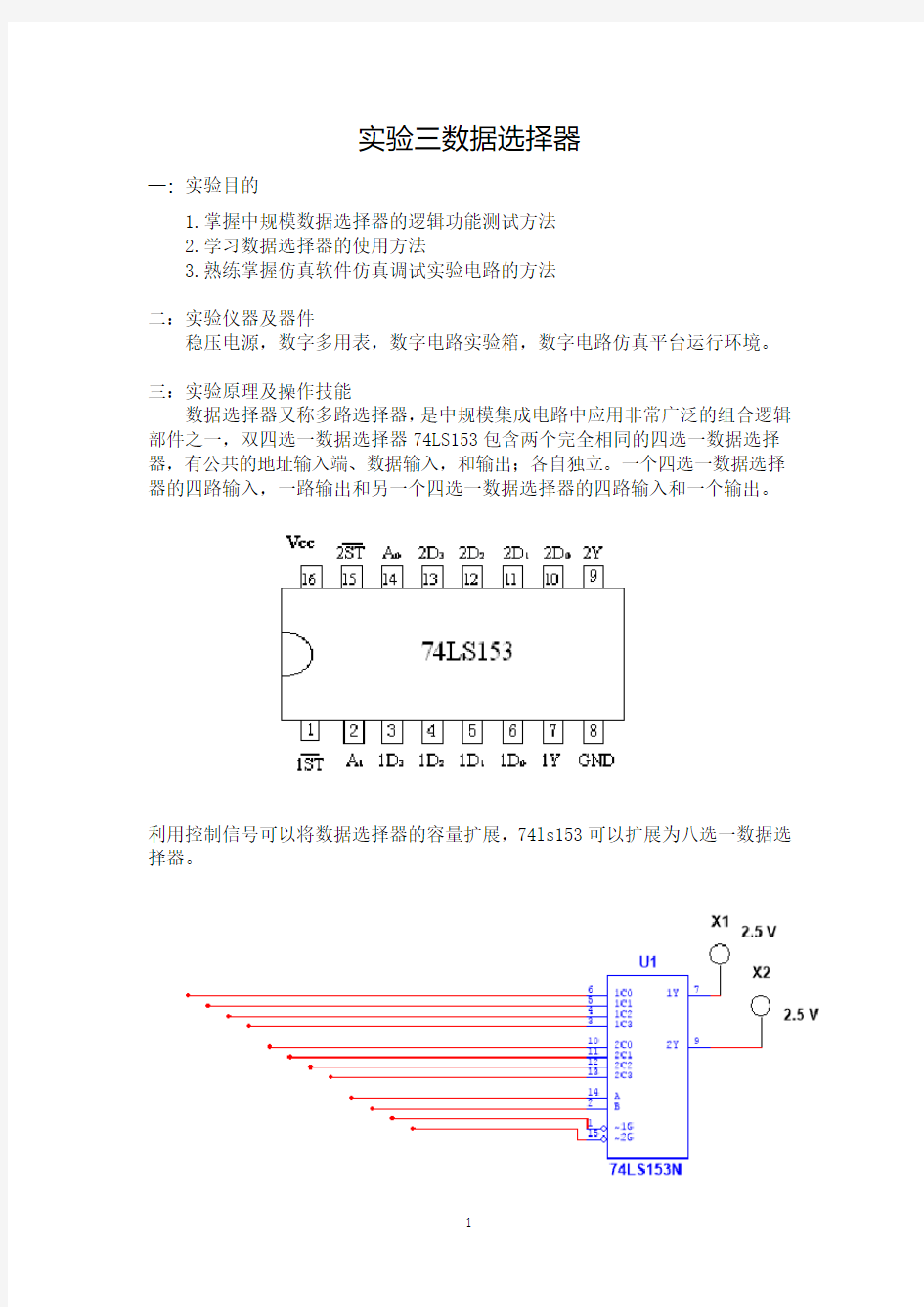

数据选择器又称多路选择器,是中规模集成电路中应用非常广泛的组合逻辑部件之一,双四选一数据选择器74LS153包含两个完全相同的四选一数据选择器,有公共的地址输入端、数据输入,和输出;各自独立。一个四选一数据选择器的四路输入,一路输出和另一个四选一数据选择器的四路输入和一个输出。

利用控制信号可以将数据选择器的容量扩展,74ls153可以扩展为八选一数据选择器。

74LS153测试电路:

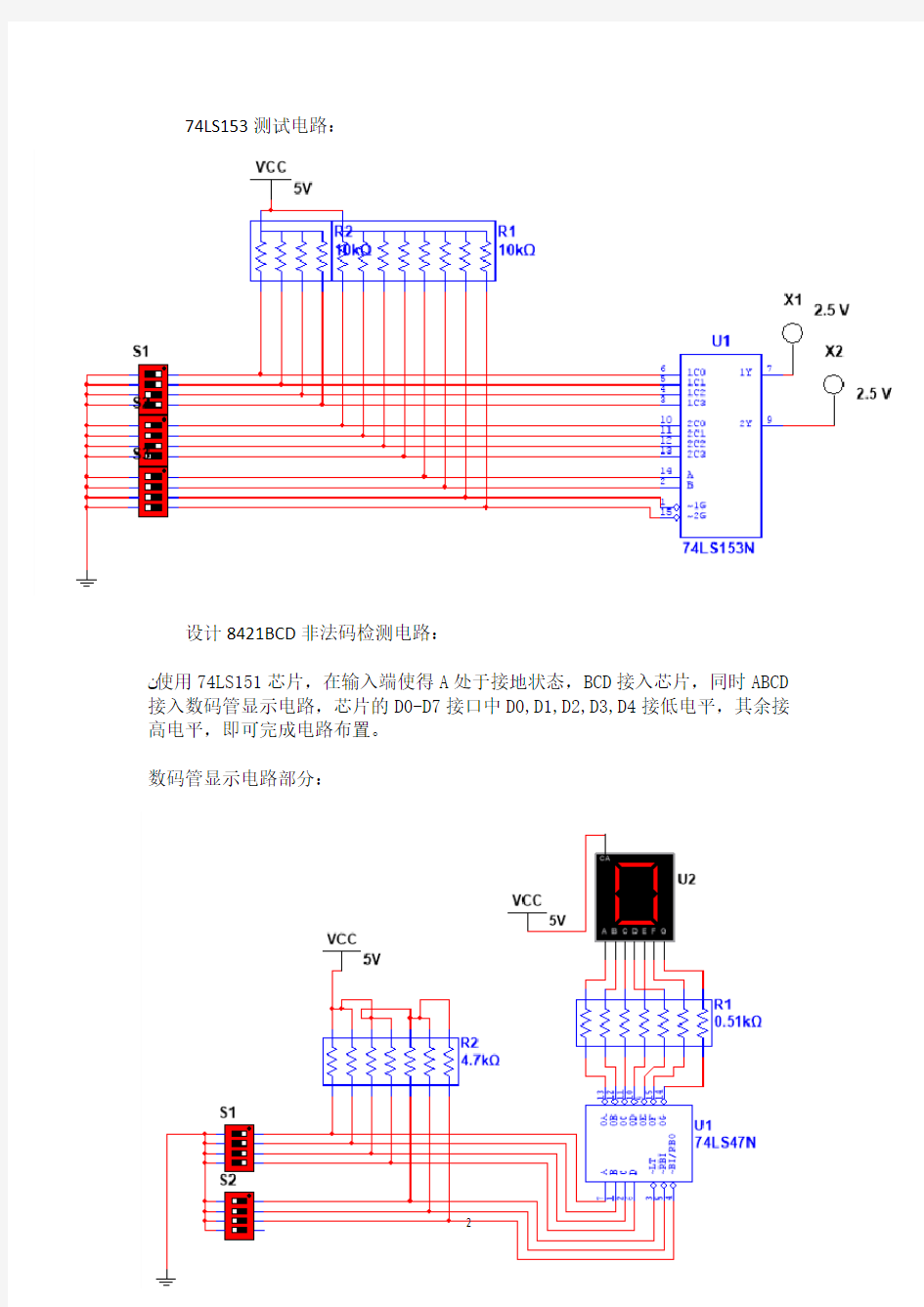

设计8421BCD非法码检测电路:

?使用74LS151芯片,在输入端使得A处于接地状态,BCD接入芯片,同时ABCD 接入数码管显示电路,芯片的D0-D7接口中D0,D1,D2,D3,D4接低电平,其余接高电平,即可完成电路布置。

数码管显示电路部分:

八选一数据选择器:

总体设计:

正常显示时指示灯不亮非法码出现时指示灯亮起

AT89C51单片机简易计算器的设计

AT89C51单片机简易计算器的设计 单片机的出现是计算机制造技术高速发展的产物,它是嵌入式控制系统的核心,如今,它已广泛的应用到我们生活的各个领域,电子、科技、通信、汽车、工业等。本设计是基于51系列单片机来进行的数字计算器系统设计,可以完成计算器的键盘输入,进行加、减、乘、除六位数范围内的基本四则运算,并在LCD上显示相应的结果。设计电路采用AT89C51单片机为主要控制电路,利用MM74C922作为计算器4*4键盘的扫描IC读取键盘上的输入。显示采用字符LCD静态显示。软件方面使用C语言编程,并用PROTUES仿真。 一、总体设计 根据功能和指标要求,本系统选用MCS-51系列单片机为主控机。通过扩展必要的外围接口电路,实现对计算器的设计。具体设计如下:(1)由于要设计的是简单的计算器,可以进行四则运算,为了得到较好的显示效果,采用LCD 显示数据和结果。 (2)另外键盘包括数字键(0~9)、符号键(+、-、×、÷)、清除键和等号键,故只需要16 个按键即可,设计中采用集成的计算键盘。 (3)执行过程:开机显示零,等待键入数值,当键入数字,通过LCD显示出来,当键入+、-、*、/运算符,计算器在内部执行数值转换和存储,并等待再次键入数值,当再键入数值后将显示键入的数

值,按等号就会在LCD上输出运算结果。 (4)错误提示:当计算器执行过程中有错误时,会在LCD上显示相应的提示,如:当输入的数值或计算得到的结果大于计算器的表示范围时,计算器会在LCD上提示溢出;当除数为0时,计算器会在LCD 上提示错误。 系统模块图: 二、硬件设计 (一)、总体硬件设计 本设计选用AT89C51单片机为主控单元。显示部分:采用LCD 静态显示。按键部分:采用4*4键盘;利用MM74C922为4*4的键盘扫描IC,读取输入的键值。 总体设计效果如下图:

计数器的设计实验报告

计数器的设计实验报告 篇一:计数器实验报告 实验4 计数器及其应用 一、实验目的 1、学习用集成触发器构成计数器的方法 2、掌握中规模集成计数器的使用及功能测试方法二、实验原理 计数器是一个用以实现计数功能的时序部件,它不仅可用来计脉冲数,还常用作数字系统的定时、分频和执行数字运算以及其它特定的逻辑功能。 计数器种类很多。按构成计数器中的各触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器。根据计数制的不同,分为二进制计数器,十进制计数器和任意进制计数器。根据计数的增减趋势,又分为加法、减法和可逆计数器。还有可预置数和可编程序功能计数器等等。目前,无论是TTL还是

CMOS集成电路,都有品种较齐全的中规模集成计数器。使用者只要借助于器件手册提供的功能表和工作波形图以及引出端的排列,就能正确地运用这些器件。 1、中规模十进制计数器 CC40192是同步十进制可逆计数器,具有双时钟输入,并具有清除和置数等功能,其引脚排列及逻辑符号如图5-9-1所示。 图5- 9-1 CC40192引脚排列及逻辑符号 图中LD—置数端CPU—加计数端CPD —减计数端CO—非同步进位输出端BO—非同步借位输出端 D0、D1、D2、D3 —计数器输入端 Q0、Q1、Q2、Q3 —数据输出端CR—清除端 CC40192的功能如表5-9-1,说明如下:表5-9-1 当清除端CR为高电平“1”时,计数

器直接清零;CR置低电平则执行其它功能。当CR为低电平,置数端LD也为低电平时,数据直接从置数端D0、D1、D2、D3 置入计数器。 当CR为低电平,LD为高电平时,执行计数功能。执行加计数时,减计数端CPD 接高电平,计数脉冲由CPU 输入;在计数脉冲上升沿进行8421 码十进制加法计数。执行减计数时,加计数端CPU接高电平,计数脉冲由减计数端CPD 输入,表5-9-2为8421 码十进制加、减计数器的状态转换表。加法计数表5-9- 减计数 2、计数器的级联使用 一个十进制计数器只能表示0~9十个数,为了扩大计数器范围,常用多个十进制计数器级联使用。 同步计数器往往设有进位(或借位)输出端,故可选用其进位(或借位)输出信号驱动下一级计数器。 图5-9-2是由CC40192利用进位

数据选择器实验报告.docx

谢谢欣赏实验三数据选择器 实验人员:班号:学号: 一、实验目的 (1) 熟悉并掌握数据选择器的功能。 (2) 用双4选1数据选择器74LS153设计出一个16选1的数据选择器。 (3) 用双4选1数据选择器74LS153 设计出一个全加法器。 二、实验设备 数字电路实验箱,74LS00,74LS153。 三、实验内容 (1) 测试双4选1数据选择器74LS153的逻辑功能。 74LS153含有两个4选1数据选择器,其中A0和A1为芯片的公共地址输入端,Vcc 和GND分别为芯片的公共电源端和接地端。Figure1为其管脚图: Figure 1 1Q=A1A01D0+A1A0?1D1+A1A0?1D2+A1A0?1D3 2Q=A1A02D0+A1A0?2D1+A1A0?2D2+A1A0?2D3 按下图连接电路: Figure 2 (2) 设某一导弹发射控制机构有两名司令员A、B和两名操作员C、D,只有当两名司令员均同意发射导弹攻击目标且有操作员操作,则发射导弹F。利用所给的实验仪器设计出一个符合上述要求的16选1数据选择器,并用数字电路实验箱上的小灯和开关组合表达实验结果。 思路: 由于本实验需要有四个地址输入端来选中16个数据输入端的地址之中的一个,进而实现选择该数据输入端中的数据的功能,即16选1。而公共的A0、A1两个地址输入端和S使能端(用于片选,已达到分片工作的目的,进而扩展了一位输入)一共可以提供三个地址输入端,故需要采用降维的方法,将一个地址输入隐藏到一个数据输入端Dx 中。本实验可以降一维,也可以降两位。由于两位比较复杂,本实验选择使用降一维的方式。 做法: 画出如应用题中实现所需功能的卡诺图: 谢谢欣赏

c计算器实验报告

简单计算器 姓名: 周吉祥 实验目的:模仿日常生活中所用的计算器,自行设计一个简单的计算器程序,实现简单的计算功能。 实验内容: (1)体系设计: 程序是一个简单的计算器,能正确输入数据,能实现加、减、乘、除等算术运算,运算结果能正确显示,可以清楚数据等。 (2)设计思路: 1)先在Visual C++ 6.0中建立一个MFC工程文件,名为calculator. 2)在对话框中添加适当的编辑框、按钮、静态文件、复选框和单选框 3)设计按钮,并修改其相应的ID与Caption. 4)选择和设置各控件的单击鼠标事件。 5)为编辑框添加double类型的关联变量m_edit1. 6)在calculatorDlg.h中添加math.h头文件,然后添加public成员。 7)打开calculatorDlg.cpp文件,在构造函数中,进行成员初始化和完善各控件 的响应函数代码。

(3)程序清单: 添加的public成员: double tempvalue; //存储中间变量 double result; //存储显示结果的值 int sort; //判断后面是何种运算:1.加法 2.减法 3.乘法 4.除法 int append; //判断后面是否添加数字 成员初始化: CCalculatorDlg::CCalculatorDlg(CWnd* pParent /*=NULL*/) : CDialog(CCalculatorDlg::IDD, pParent) { //{{AFX_DATA_INIT(CCalculatorDlg) m_edit1 = 0.0; //}}AFX_DATA_INIT // Note that LoadIcon does not require a subsequent DestroyIcon in Win32 m_hIcon = AfxGetApp()->LoadIcon(IDR_MAINFRAME); tempvalue=0;

数电实验二:简易计算器(实验报告)

数电实验2实验报告 1、设计修改方案 (1)加入编码器连接4选一数据选择器,控制进行运算的种类 (2)修改了输出端数据选择器的程序,使得当计算器没有任何输入时,结果显示保持为0,并且利用芯片自身的灭零管脚,让显示结果中,当十位为零时,十 位的零不显示。

2、实验数据及分析 (1)修改后电路图(附后) (2)仿真波形 设置输入2个4位二进制数为0110(十进制6)和0010(十进制2),计算方式控制SW[3:0]设为0111,即模拟除法操作,加入时钟信号。 ①模拟除法波形: 可以看到十位(商)的数码管显示中,1、2、3、4、7段亮,显示为数字3,而个位(余数)显示1、2、3、4、5、6段亮,显示数字0,相当于计算出6除2商3余0。满足计算要求。 ②模拟乘法波形:(SW[3:0]设为1011,其他输入同上)

可以看到个位的数码管显示中,1、4、5、6段亮,显示为C(化为十进制为12),而十位一直显示1、2、3、4、5、6段亮,显示数字0,相当于计算出6乘2等于0C,即等于12。当改变输入4和2是,显示结果为8,。满足计算要求。 ③模拟加法波形:(SW[3:0]设为1101,其他输入同上) 可以看到个位的数码管显示中,1、2、3、4、5、6、7段全亮,显示为数字8,而十位一直显示1、2、3、4、5、6段亮,显示数字0,相当于计算出6加2等于08,即等于8。满足计算要求。 ④模拟减法波形:(SW[3:0]设为1110,其他输入同上) 可以看到个位的数码管显示中,2、3、6、7段亮,显示为数字3,而十位一直显示1、2、3、4、5、6段亮,显示数字0,相当于计算出6减2等于03,即等于3。满足计算要求。 从上面加减乘除四种功能运算的波形仿真可以看出,本实验设计能够正确完成对输入数字的上述四种运算。满足题目要求。

数字钟设计报告——数字电路实验报告

数字钟设计实验报告 专业:通信工程 姓名:王婧 班级:111041B 学号:111041226

数字钟的设计 目录 一、前言 (3) 二、设计目的 (3) 三、设计任务 (3) 四、设计方案 (3) 五、数字钟电路设计原理 (4) (一)设计步骤 (4) (二)数字钟的构成 (4) (三)数字钟的工作原理 (5) 六、总结 (9) 1

一、前言 此次实验是第一次做EDA实验,在学习使用软硬件的过程中,自然遇到很多不懂的问题,在老师的指导和同学们的相互帮助下,我终于解决了实验过程遇到的很多难题,成功的完成了实验,实验结果和预期的结果也是一致的,在这次实验中,我学会了如何使用Quartus II软件,如何分层设计点路,如何对实验程序进行编译和仿真和对程序进行硬件测试。明白了一定要学会看开发板资料以清楚如何给程序的输入输出信号配置管脚。这次实验为我今后对 EDA的进一步学习奠定了更好的理论基础和应用基础。 通过本次实验对数电知识有了更深入的了解,将其运用到了实际中来,明白了学习电子技术基础的意义,也达到了其培养的目的。也明白了一个道理:成功就是在不断摸索中前进实现的,遇到问题我们不能灰心、烦躁,甚至放弃,而要静下心来仔细思考,分部检查,找出最终的原因进行改正,这样才会有进步,才会一步步向自己的目标靠近,才会取得自己所要追求的成功。 2

二、设计目的 1.掌握数字钟的设计方法。 2熟悉集成电路的使用方法。 3通过实训学会数字系统的设计方法; 4通过实训学习元器件的选择及集成电路手册查询方法; 5通过实训掌握电子电路调试及故障排除方法; 6熟悉数字实验箱的使用方法。 三、设计任务 设计一个可以显示星期、时、分、秒的数字钟。 要求: 1、24小时为一个计数周期; 2、具有整点报时功能; 3、定时闹铃(未完成) 四、设计方案 一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器和定时器组成。干电路系统由秒信号发生 3

八选一数据选择器和四位数据比较器verilog实验报告)

Verilog HDV 数字设计与综合 实验报告 微电子0901班 姓名:袁东明 _ 学号:_04094026 一、实验课题: 1.八选一数据选择器 2.四位数据比较器 二、八选一数据选择器Verilog程序: 2.1主程序 module option(a,b,c,d,e,f,g,h,s0,s1,s2,out); input [2:0] a,b,c,d,e,f,g,h; input s0,s1,s2; output [2:0] out; reg [2:0] out; always@(a or b or c or d or e or f or g or h or s0 or s1 or s2) begin case({s0,s1,s2}) 3'd0 : out=a;

3'd1 : out=b; 3'd2 : out=c; 3'd3 : out=d; 3'd4 : out=e; 3'd5 : out=f; 3'd6 : out=g; 3'd7 : out=h; endcase end endmodule 2.2激励程序 module sti; reg [2:0] A,B,C,D,E,F,G,H; reg S0,S1,S2; wire [2:0] OUT; option dtg(A,B,C,D,E,F,G,H,S0,S1,S2,OUT); initial begin A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=0;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=0;S1=1;S2=1; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=0; #100 A=3'd0;B=3'd1;C=3'd2;D=3'd3;E=3'd4;F=3'd5;G=3'd6;H=3'd7;S0=1;S1=0;S2=1;

微机原理实验简易计算器

【实验题目】 简易计算器设计 【实验目的】 综合测试学生微机接口技术及应用能力,包括系统构思设计、电路设计搭建、软件调试等; 结合应用实际,培养学生运用微机技术服务应用、服务实际的能力。 【基本要求】 1)利用实验箱上的4x4键盘及6位数码管,实现两个16位宽的非负整数(0~65535)进行+、-、×运算,计算结果限制在范围-65535~65535,超过范围在数码管最低位显示E; 2) 16个按键的分配可以自行指定; 【扩展要求】 1)按基本要求保持输入的范围不变(16位宽),扩展计算结果的范围到用足6位数码管,当计算结果超过-65535~999999时,显示E; 2)增加÷的功能,有小数显示; 【实验程序】 ;该程序实现了基本要求及扩展要求的2) DSEG SEGMENT BUFF DB 6 DUP() LED_7 DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH,77H,7CH,39 H,5EH,79H,71H,00H,40H POSITION DB 0DFH,0EFH,0F7H,0FBH,0FDH,0FEH UNIT10 DW 10000,1000,100,10,1 NEWNUM DB 0 COUNT DB 0 FLAG DB 0 ;是否有键按下的标志 NEGTI DB 0 ;是否为负数的标志 NUM DW 0 NUM1 DW 0 NUM2 DW 0 TAG DB 0 ;运算种类标志 POINT DB 0 ;除法结果添加小数点标志 RESULT DW 0 DSEG ENDS CSEG SEGMENT ASSUME DS:DSEG,CS:CSEG START: MOV AX,DSEG MOV DS,AX MOV DX,300CH ;8255初始化 MOV AL,81H OUT DX,AL LEA SI,BUFF MOV CX,6 NEXT: MOV BYTE PTR[SI],16 INC SI LOOP NEXT CALL SHOW ;将显示缓冲区中内容在LED上一次显示出来 MOV COUNT,0 ;记按下了几位数 NEXT2: CALL SHOW CALL SCAN ;判断是否有按键按下 CMP FLAG,1 JZ OK JMP NEXT2 OK: MOV FLAG,0 MOV POINT,0 MOV DX,3000H ;判断是哪一个键被按下 MOV AL,0FFH OUT DX,AL MOV CH,-1 ;CH用于保存当前被扫描的列号MOV CL,07FH XL: ROL CL,1 INC CH MOV DX,3000H MOV AL,CL OUT DX,AL MOV DX,3008H

数电实验报告 计数器

实验报告 实验七计数器原理测试及其设计 2.7.1 实验目的 1.掌握中规模集成计数器74LS160、74LS161、74LS163的逻辑功能及使用方法。 2.掌握同步清零与异步清零的区别及74LS160计数器的级联方法。 3.学习用中规模集成计数器设计任意进制计数器。 2.7.2 实验仪器设备与主要器件 实验箱一个;双踪示波器一台;稳压电源一台;函数发生器一台。 74LS160,74LS161和74LS163。 2.7.3 实验原理 计数器的功能是记录输入脉冲的个数。他所能记忆的最大脉冲个数称为该计数器的模。计数器不仅能统计输入脉冲的个数,还可以用作分频、定时、产生节拍脉冲等。根据进位方式,可分为同步和异步两类。根据进制,可分为二进制、十进制和任意进制等。根据逻辑功能,可分为加法计数器、减法计数器和可逆计数器等。根据电路集成度,可分为小规模集成计数器和中规模集成计数器。 2.7.4 实验内容 1.分别用74LS161和74LS163设计模13计数器,采用清零法实现,并用数码管显示实验结果。 设计思路:74LS161是十六进制计数器,所以我在它计数到13(1101)清零就行了,再利用二进制数与BCD码对应关系,即利用74LS283的逻辑功能使数码管显示实验结果。计数时电路状态转换关系: 0000→0001→0010→0011→0100→0101→0110→0111→1000→1001→1010→1011→1100→0000

设计思路:74LS163接法与74LS161基本一样,只是163的清零信号是12不是13,如图: 2.设计一个用3位数码管指示的六十进制计数器,并用三只开关控制计数器的数据保持、计数及清零功能。 设计思路:用Cr=0控制计数器清零,用EP*ET=0控制计数器数据保持,用高低电平和CP脉冲进行与运算控制计数器计数功能。U1的清零信号是在计数到6时,U1清零的同时U3开始计数,这样就能实现用3位数码管指示的六十进制计数器。如图:

:数据选择器设计(实验报告)

实验报告 一、实验目的 熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。 二、实验设备 GW48系列SOPC/EDA实验开发系统实验箱一台计算机一台 三、实验内容 1首先利用QuartusⅡ完成2选1多路选择器的文本编辑输入(mux21a.vhd)和仿真测试等步骤,给出下图所示的仿真波形。最后在实验系统上进行硬件测试,验证本项设计的功能。 源程序为: ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; ELSE y <= b ; END IF; END PROCESS; END ARCHITECTURE one ;

图(1 ) 2选1多路选择器的编译图 、图(2) 功能仿真的波形图 图(3 ) 功能引脚图

图(4) 2选1多路选择器的RTL电路 2. 将此多路选择器看成是一个元件mux21a,利用元件例化语句描述图,并将此文件放在同一目录中。并对上例分别进行编译、综合、仿真,并对其仿真波形做出分析说明。以下是程序: 图(5) 双二选一多路选择器的编译图

图(6) 双路数据选择器功能仿真图 图(7) 双二选一多路选择器的引脚锁定图图 5 双2选1多路选择器 图(8) 双路数据选择器RTL电路图

图(9) 编程下载图 3.、引脚锁定以及硬件下载测试。若选择目标器件是EP1C3,建议选实验电路模式5,用键1(PIO0,引脚号为1)控制s0;用键2(PIO1,引脚号为2)控制s1;a3、a2 和a1 分别接clock5(引脚号为16)、clock0(引脚号为93)和clock2(引脚号为17);输出信号outy仍接扬声器spker(引脚号为129)。通过短路帽选择clock0接256Hz信号,clock5 接1024Hz,clock2 接8Hz 信号。最后进行编译、下载和硬件测试实验(通过选择键1、键2,控制s0、s1,可使扬声器输出不同音调)。 图(10) 实验电路模式5

数电实验报告:实验4-计数器及应用161

广东海洋大学学生实验报告书(学生用表) 实验名称 课程名称 课程号 学院(系) 专业 班级 学生姓名 学号 实验地点 实验日期 实验4 计数器及其应用 一、实验目的 1、熟悉中规模集成计数器的逻辑功能及使用方法 2、掌握用74LS161构成计数器的方法 3、熟悉中规模集成计数器应用 二、实验原理 计数器是典型的时序逻辑电路,它是用来累计和记忆输入脉冲的个数.计数是数字系统中很重要的基本操作,集成计数器是最广泛应用的逻辑部件之一。计数器种类较多,按构成计数器中的多触发器是否使用一个时钟脉冲源来分,有同步计数器和异步计数器;根据计数制的不同,可分为二进制计数器、十进制计数器和任意进制计数器;根据计数的增减趋势,又分为加法、减法和可逆计数器。还有可预置数和可编程序功能计数器等。本实验主要研究中规模十进制计数器74LS161的功能及应用。 1、中规模集成计数器 74LS161 是四位二进制可预置同步计数器,由于它采用4 个主从JK 触发器作为记忆单元,故又称为四位二进制同步计数器,其集成芯片管脚如图1所示: 管脚符号说明:电源正端Vcc ,接+5V ;异步置零(复位)端Rd ;时钟脉冲CP ;预置数控制端 A 、B 、C 、D ;数据输出端 QA 、QB 、QC 、QD ;进位输出端 RCO :使能端EP ,ET ;预置端 LD ; 图1 74LS161 管脚图 GDOU-B-11-112

该计数器由于内部采用了快速进位电路,所以具有较高的计数速度。各触发器翻转是靠时钟脉冲信号的正跳变上升沿来完成的。时钟脉冲每正跳变一次,计数器内各触发器就同时翻转一次,74LS161的功能表如表1所示: 表1 74LS161 逻辑功能表 2、实现任意进制计数器 由于74LS161的计数容量为16,即计16个脉冲,发生一次进位,所以可以用它构成16进制以内的各进制计数器,实现的方法有两种:置零法(复位法)和置数法(置位法)。 (1) 用复位法获得任意进制计数器假定已有N进制计数器,而需要得到一个M进制计数器时,只要M<N,用复位法使计数器计数到M时置“0”,即获得M进制计数器。 (2) 利用预置功能获M进制计数器置位法与置零法不同,它是通过给计数器重复置入某个数值的的跳越N-M个状态,从而获得M进制计数器的,如图所法。置数操作可以在电路的任何一个状态下进行。这种方法适用于有预置功能的计数器电路。图2是上述二种方法的原理示意图。 图2(a) 图2(b) 三、实验内容与步骤 1、测试74LS161的逻辑功能。 2、在熟悉74LS161逻辑功能的基础上,利用74LS161设计9进制计数器。 附图74ls00和74ls20

单片机实验报告 计算器

单片机原理及其应用实验报告基于51单片机的简易计算器的设计 班级:12电子1班 姓名:金腾达 学号:1200401123 2015年1月6日

摘要 一个学期的51单片机的课程已经随着期末的到来落下了帷幕。“学以致用”不仅仅是一句口号更应该是践行。本设计秉承精简实用的原则,采用AT89C51单片机为控制核心,4X4矩阵键盘作为输入,LCD1602液晶作为输出组成实现了基于51单片机的简易计算器。计算器操作方式尽量模拟现实计算器的操作方式,带有基本的运算功能和连续运算能力。并提供了良好的显示方式,与传统的计算器相比,它能够实时显示当前运算过程和上一次的结果,更加方便用户记忆使用。本系统制作简单,经测试能达到题目要求。 关键词:简易计算器、单片机、AT89C51、LCD1602、矩阵键盘

目录 一、系统模块设计......................................................................................... 错误!未定义书签。 1.1 单片机最小系统 (1) 1.2 LCD1602液晶显示模块 (1) 1.3 矩阵按键模块 (2) 1.4 串口连接模块 (1) 二、C51程序设计 (2) 2.1 程序功能描述及设计思路 (2) 2.1.1按键服务函数 (2) 2.1.2 LCD驱动函数 (2) 2.1.3 结果显示函数 (2) 2.1.4状态机控制函数 (2) 2.1.5串口服务函数 (2) 2.2 程序流程图 (3) 2.2.1系统总框图 (3) 2.2.2计算器状态机流程转换图 (3) 三、测试方案与测试结果 (4) 3.1测试方案 (4) 3.3 测试结果及分析 (7) 4.3.1测试结果(仿真截图) (7) 4.3.2测试分析与结论 (7) 四、总结心得 (7) 五、思考题 (8) 附录1:整体电路原理图 (9) 附录2:部分程序源代码 (10)

数字逻辑电路课程课程设计--简易加减计算器

数字逻辑电路课程课程设计--简易加减计算器

摘要 本次课程设计的任务是设计一个具有加减运算功能的简易计算器,并通过合适的方式来显示最后的计算结果。此次设计电路的完成主要是利用简单的数字电路和电路逻辑运算来进行的。简易加减计算器电路主要是对数据的输入与显示,数据的加减运算,数据的输出与显示三个主要的方面来设计研究完成的。 在输入电路的部分,我们通过开关的闭合与断开来实现数据的输入,开关闭合接入高电平“1”,断开接入低电平“0”。而输入的数据将通过显示译码管以十进制的形式显示出来。由于输入二进制的位数较多,我们采用个位十位分别输入的方式来简化电路。

加减运算电路则主要通过加法器来实现的。设计电路时,我们将个位和个位、十位和十位分别接入一片加法器。在进行加法运算时我们所选择的加法器是完全符合要求的,但是在进行减法运算时加法器就不能满足我们的设计要求了。因此我们将减法转换为加法进行运算,运算时采用补码的形式。在进行减法时通过异或门将减数的原码全部转换为补码,输入加法器中进行相加。最后将进位信号加到十位的运算电路上就实现了加减法的运算电路。 在显示电路中,由加法器输出的数据是二进制码。这些码可能表示超过十的数字,所以显示译码管就不能正确的显示出数字了。此时要将二进制转化成BCD码,再将BCD码送到显示译码管中就可以将计算所得的数字显示出来了。

概述 1.1设计题目: 简易加减计算器 1.2设计任务和要求: 1)用于两位以下十进制数的加减运算。 2)以合适的方式显示输入数据及计算结果。 1.3设计方案比较: 方案一:输入十进制的数字,再通过编码器对十进制的数字进行编码,输出二进制的数据。运用显示译码器对输入的数字以十进制的形式进行显示。在进行加减计算的时候将二进制数字运用数模转换,然后再进行相加减。然后将这些模拟信号再次转换成数字信号转换成数字信号,再将数字信号输入到显示译码管中来显示数剧。

数电实验实验报告

数字电路实验报告

实验一 组合逻辑电路分析 一.试验用集成电路引脚图 74LS00集成电路 74LS20集成电路 四2输入与非门 双4输入与非门 二.实验内容 1.实验一 自拟表格并记录: 2.实验二 密码锁的开锁条件是:拨对密码,钥匙插入锁眼将电源接通,当两个条件同时满足时,开锁信号为“1”,将锁打开。否则,报警信号为“1”,则接通警铃。试分析密码锁的密码ABCD 是什么? X1 2.5 V A B C D 示灯:灯亮表示“1”,灯灭表示“0” ABCD 按逻辑开关,“1”表示高电平,“0”表示低电平

ABCD 接逻辑电平开关。 最简表达式为:X1=AB ’C ’D 密码为: 1001 A B C D X1 X2 A B C D X1 X2 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 1 1 0 0 1 1 0 0 0 1 0 0 1 1 0 1 0 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 0 1 0 1 0 1 0 1 1 1 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 1 1 三.实验体会: 1.分析组合逻辑电路时,可以通过逻辑表达式,电路图和真值表之间的相互转换来到达实验所要求的目的。 2.这次试验比较简单,熟悉了一些简单的组合逻辑电路和芯片 ,和使用仿真软件来设计和构造逻辑电路来求解。 实验二 组合逻辑实验(一) 半加器和全加器 一.实验目的 1. 熟悉用门电路设计组合电路的原理和方法步骤 二.预习内容 1. 复习用门电路设计组合逻辑电路的原理和方法步骤。 2. 复习二进制数的运算。 3. 用“与非门”设计半加器的逻辑图。 4. 完成用“异或门”、“与或非”门、“与 非”门设计全加器的逻辑图。 5. 完成用“异或”门设计的3变量判奇 电路的原理图。 三.元 件参考 U1A 74LS00D U1B 74LS00D U1C 74LS00D U1D 74LS00D U2A 74LS00D U2B 74LS00D U2C 74LS00D U3A 74LS20D X1 2.5 V X2 2.5 V VCC 5V A B C D

数据选择器_Mutisim仿真实验报告

电气工程学院电工电子教学基地 数字电子技术实验 实验报告 仿真实验1 用数据选择器设计函数发生器 学号:18291035 姓名:陈涟漪 班级:电气1802 成绩: 指导教师:周晖 完成时间:2020年5 月15 日

数字电子技术实验 仿真实验1 用数据选择器设计函数发生器 1 实验任务 使用数据选择器74LS151和适当门电路设计一函数发生器,能够实现4位二进制码数据范围指示功能。要求该函数发生器能区别以下三种情况: (1)0≤X≤4; (2)5≤X≤9; (3)10≤X≤15。 2 实验电路

3 实验步骤 采用A、B、C、D取0或1依次表示这四位二进制码的从高到低位的取值(例如:A=0,B=1,C=0,D=0表示四位二进制码0100)。则对于第一组来说,共有5个四位二进制码包含在其中,用卡诺图表示如下: 化简即得: 同理,也有5个数包含在第二组中,卡诺图如下: 化简即得: 第三组包含了6个数,卡诺图如下:

化简即得: 对以上三个式子都去两次非并利用摩根定律可得: 这样就完成了该问题的逻辑转化。 根据前面对该实验分析所得到的逻辑表达式可以发现,输入变量为A、B、C、D,但是在后面的逻辑运算中它们的“非”都用到了,也就是第一步我们要得到这四个变量的非。然后再进行后面的与非运算。三个输出变量的状态也可以用三个灯泡来表示,这里采用了三个颜色不同的灯泡用以区分。到这里,逻辑图就可以很容易的用Multisim软件模拟出来。 其中,最上面的X1灯泡亮时,表示输入数字在0≤X≤4范围内,X2亮时表示输入数字在5≤X≤9范围内,X3亮时表示输入数字在10≤X≤15范围内。这里还是用了四个开关,每个开关“开”表示1,“关”表示0,四个开关以ABCD的顺序来表示四位二进制数。四位二进制数同上,也有16中情况,这里不做一一展示,只对每一类给出一种模拟结果。

c计算器实验报告

c计算器实验报告集团标准化工作小组 #Q8QGGQT-GX8G08Q8-GNQGJ8-MHHGN#

简单计算器 姓名: 周吉祥 实验目的:模仿日常生活中所用的计算器,自行设计一个简单的计算器程序,实现简单的计算功能。 实验内容: (1)体系设计: 程序是一个简单的计算器,能正确输入数据,能实现加、减、 乘、除等算术运算,运算结果能正确显示,可以清楚数据等。 (2)设计思路: 1)先在Visual C++ 中建立一个MFC工程文件,名为calculator. 2)在对话框中添加适当的编辑框、按钮、静态文件、复选框和 单选框 3)设计按钮,并修改其相应的ID与Caption. 4)选择和设置各控件的单击鼠标事件。 5)为编辑框添加double类型的关联变量m_edit1. 6)在中添加头文件,然后添加public成员。 7)打开文件,在构造函数中,进行成员初始化和完善各控件的 响应函数代码。 (3)程序清单: 添加的public成员: double tempvalue; 法 2.减法 3.乘法 4.除法

int append; //判断后面是否添加数字 ●成员初始化: CCalculatorDlg::CCalculatorDlg(CWnd* pParent /*=NULL*/) : CDialog(CCalculatorDlg::IDD, pParent) { //{{AFX_DATA_INIT(CCalculatorDlg) m_edit1 = ; //}}AFX_DATA_INIT // Note that LoadIcon does not require a subsequent DestroyIcon in Win32 m_hIcon = AfxGetApp()->LoadIcon(IDR_MAINFRAME); tempvalue=0; result=0; sort=0; append=0; } ●各控件响应函数代码: void CCalculatorDlg::OnButton1() //按钮“1” { // TODO: Add your control notification handler code here if(append==1)result=0;

简易计算器设计实验报告

简易计算器设计实验报告 一.设计任务及要求 1.1实验任务: 根据计算器的原理设计一个具有加减乘除功能的简易计算器。如:5+3*4/8=4。 1.2 实验基本要求: (1)实现最大输入两位十进制数字的四则运算(加减乘除)。 (2)能够实现多次连算(无优先级,从左到右计算结果)。 如:12+34*56-78/90+9=36 (3)最大长度以数码管最大个数为限,溢出报警。 二.实验设计方案 (1)用QuartusII的原理图输入来完成系统的顶层设计。 (2)用VHDL编写以及直接拖模块来各功能模块。 (3)通过2个脉冲分别实现个位数和十位数的输入。 (4)通过选择每次的输出数值,将输出值反馈到运算输入端 (4)通过除法运算实现十六进制到十进制的转换输出。 其具体实现流程图如下:

三系统硬件设计 FPGA: EP2C5T144C8目标板及相应外围硬件电路。(从略) 四系统软件设计 1.数据输入模块 原理:用VHDL创建模块,通过两个脉冲分别对两个数码管进行输入控制,再通过相应运算模块将两个独立数据转化成两位十进制数字。 2.运算模块 原理:用VHDL创建模块,四种运算同步运行,通过按键加、减、乘、除选择输出对应的计算结果,当按键等号来时,将所得结果反馈给运算模块输入端。具体实现代码见附录二。 3.输出模块 原理:用VHDL创建模块,通过按键等号来控制显示运算对象还是运算结果,当等号按下时,输出计算结果,否则显示当前输入的数据,并且通过除法模块将十六进制转化为十进制。当输出结果溢出是LED0亮,同时数码管显示都为零。部分实现见附录二。 五实验调试 输入数据12,再按加法键,输入第二个数字25,按等号键,数码管显示37;按灭加法、等号键,输入第二个数据2,依次按等号键,减法键,数码管显示35;同上,按灭减法键、等号键,输入第三个数据7,依次按等号键,除法键,数码管显示5;按灭除法键、等号键,输入第四个数据99,依次按等号键,乘法键,数码管显示495,按灭乘法键、等号键,当前显示为99,依次按等号键、乘法键,数码管显示49005,同上进行若干次之后,结果溢出,LED0亮,同时数码管显示都为零。当输出为负数时,LED0灯变亮,同时数码管显示都为零。六实验结论 本实验基本实现了计算器的加减乘法运算功能,但是存在一个突出的缺陷,就是当输出结果时,必须先按等号键导通数据反馈,再按运算键选择输出结果。这与实际应用的计算器存在很大的差距。但是,本设计可以通过等号键实现运算对象和运算结果之间的切换。

秒篮球倒计时数电实验报告

秒篮球倒计时数电实验报告

————————————————————————————————作者:————————————————————————————————日期:

法商学院 《数字电路课程设计》 课程设计报告 专业:应用电子技术 班级:应电11301 姓名:周灵 姓名:李雄威 指导教师:沈田

课程设计任务书 设计题目:篮球竞赛24秒倒计时器 设计任务与要求: 设计一个篮球竞赛24秒倒计时电路,该电路能实现如下功能: 1)24秒倒计时显示功能; 2)设置外部控制开关,控制计数器的重置“24”、启动和暂停功能; 3)计数器递减至0(即时间到)时,数码管显示“00”,同时发出光电报警信号。 一、电路设计原理 经过对电路功能的分析,整个电路主要由控制电路、秒脉冲信号发生器、计数器、译码器和报警电路五个部分组成。示意图如图1所示。其中计数器和控制电路是系统的主要模块。计数器完成24秒计时功能,而控制电路完成计数器的直接清零、启动计数、暂停/连续计数、译码显示电路的显示与灭灯、定时时间到报警等功能。秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但本设计对此信号要求并不是太高,故电路可采用555集成电路或由TTL与非组成的多谐振荡器构成。主体电路:24秒倒计时。24秒计数芯片的置数端清零端共用一个开关,比赛开始后,24秒的置数端无效,24秒的倒数计时器开始进行倒计时,逐秒倒计一之到零。选取“00”这个状态,通过组合逻辑电路给出截断信号,让该信号与时钟脉冲在与门中将时钟截断,使计时器在计数到零时停止。 图1-1 24秒计时器系统设计框图 二、单元电路分析

实验三选数据选择器实验报告

实验三选数据选择器实 验报告 集团公司文件内部编码:(TTT-UUTT-MMYB-URTTY-ITTLTY-

实验三、八选一数据选择器 一、实验目的: 1.熟悉Quartus II6.0软件的使用和FPGA设计流程 2.用VHDL语言进行八选一数据选择器的设计 二、实验步骤: 一.建立文件夹:在D盘“xingming”的文件夹下建立一个名为“choice8”的文件夹。 二.建立新工程 1.双击桌面上Quartus II6.0 的图标,启动该软件。 2.通过File => New Project Wizard… 菜单命令启动新项目向导。在 随后弹出的对话框上点击Next按钮,在 What is the working directory for this project 栏目中设定新项目所使用的路径:D:\xingming\choice8;在 What is the name of this project 栏目中输入新项目的名字:choice8,点击 Next 按钮。在下一个出现的对话框中继续点击Next,跳过这步。 3.为本项目指定目标器件:选择器件系列为ACEX1K ,选择具体器件为 EP1K30TC144-3 1728 24576 ,再点击Next。在弹出的下一对话框中继续点击Next ,最后确认相关设置,点击Finish按钮,完成新项目创建。 三.设计输入 1.建立一个VHDL文件。通过 File => New 菜单命令,在随后弹出的对 话框中选择 VHDL File选项,点击 OK 按钮。通过 File => Save As 命令,将其保存,并加入到项目中。 2.在VHDL界面输入8选1数据选择器程序,然后通过File => Save

单片机课程设计——基于C51简易计算器

单片机十进制加法计算器设计 摘要 本设计是基于51系列的单片机进行的十进制计算器系统设计,可以完成计 算器的键盘输入,进行加、减、乘、除3位无符号数字的简单四则运算,并在LED上相应的显示结果。 设计过程在硬件与软件方面进行同步设计。硬件方面从功能考虑,首先选择内部存储资源丰富的AT89C51单片机,输入采用4×4矩阵键盘。显示采用3位7段共阴极LED动态显示。软件方面从分析计算器功能、流程图设计,再到程序的编写进行系统设计。编程语言方面从程序总体设计以及高效性和功能性对C 语言和汇编语言进行比较分析,针对计算器四则运算算法特别是乘法和除法运算的实现,最终选用全球编译效率最高的KEIL公司的μVision3软件,采用汇编语言进行编程,并用proteus仿真。 引言 十进制加法计算器的原理与设计是单片机课程设计课题中的一个。在完成理论学习和必要的实验后,我们掌握了单片机的基本原理以及编程和各种基本功能的应用,但对单片机的硬件实际应用设计和单片机完整的用户程序设计还不清楚,实际动手能力不够,因此对该课程进行一次课程设计是有必要的。 单片机课程设计既要让学生巩固课本学到的理论,还要让学生学习单片机硬件电路设计和用户程序设计,使所学的知识更深一层的理解,十进制加法计算器原理与硬软件的课程设计主要是通过学生独立设计方案并自己动手用计算机电路设计软件,编写和调试,最后仿真用户程序,来加深对单片机的认识,充分发挥学生的个人创新能力,并提高学生对单片机的兴趣,同时学习查阅资料、参考资料的方法。 关键词:单片机、计算器、AT89C51芯片、汇编语言、数码管、加减乘除

目录 摘要 (01) 引言 (01) 一、设计任务和要求............................. 1、1 设计要求 1、2 性能指标 1、3 设计方案的确定 二、单片机简要原理............................. 2、1 AT89C51的介绍 2、2 单片机最小系统 2、3 七段共阳极数码管 三、硬件设计................................... 3、1 键盘电路的设计 3、2 显示电路的设计 四、软件设计................................... 4、1 系统设计 4、2 显示电路的设计 五、调试与仿真................................. 5、1 Keil C51单片机软件开发系统 5、2 proteus的操作 六、心得体会.................................... 参考文献......................................... 附录1 系统硬件电路图............................ 附录2 程序清单..................................