s3c2410中断异常处理总结(重要)(精)

s3c2410中断异常处理

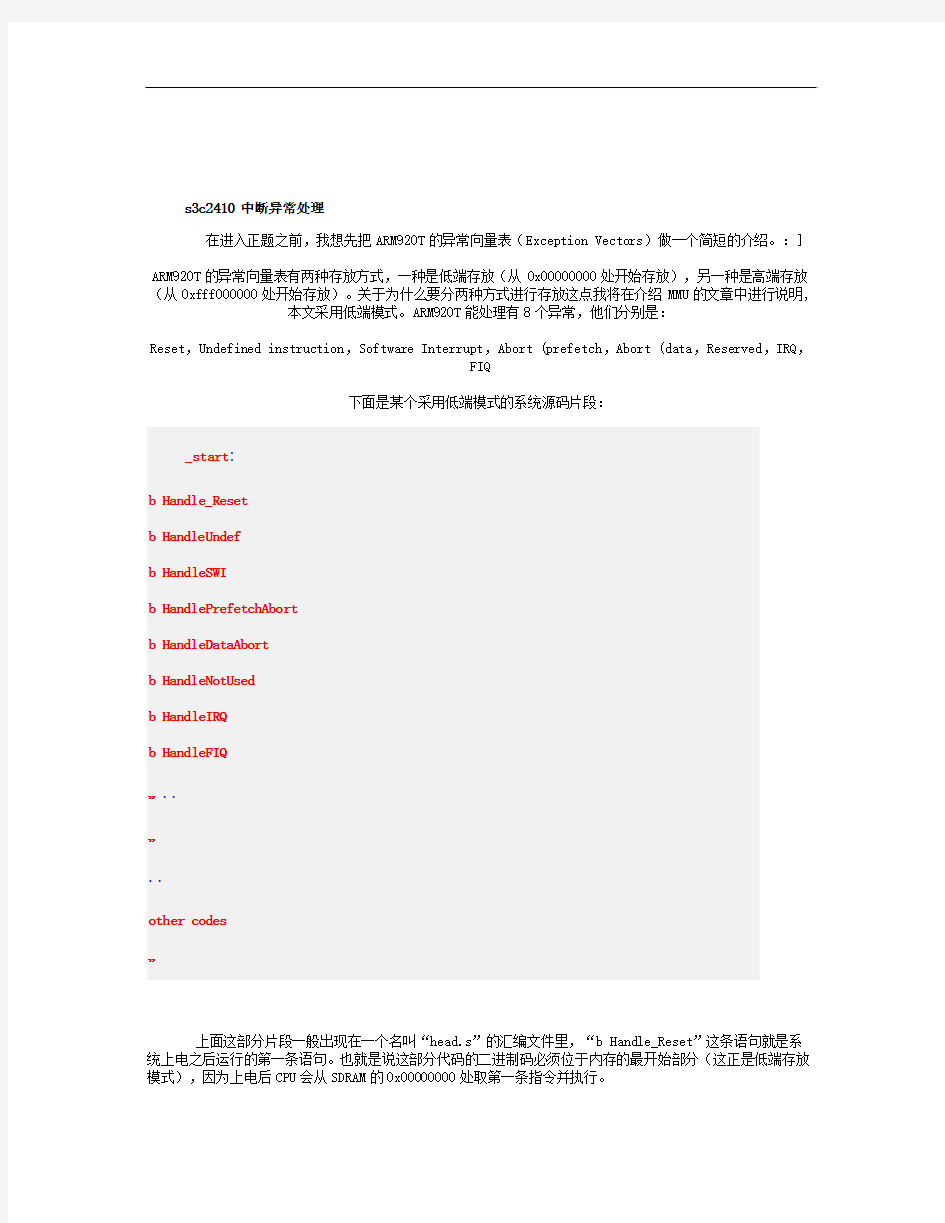

在进入正题之前,我想先把ARM920T的异常向量表(Exception Vectors)做一个简短的介绍。:]

ARM920T的异常向量表有两种存放方式,一种是低端存放(从0x00000000处开始存放),另一种是高端存放(从0xfff000000处开始存放)。关于为什么要分两种方式进行存放这点我将在介绍MMU的文章中进行说明,本文采用低端模式。ARM920T能处理有8个异常,他们分别是:

Reset,Undefined instruction,Software Interrupt,Abort (prefetch,Abort (data,Reserved,IRQ,

FIQ

下面是某个采用低端模式的系统源码片段:

_start:

b Handle_Reset

b HandleUndef

b HandleSWI

b HandlePrefetchAbort

b HandleDataAbort

b HandleNotUsed

b HandleIRQ

b HandleFIQ

…..

…

..

other codes

…

上面这部分片段一般出现在一个名叫“head.s”的汇编文件里,“b Handle_Reset”这条语句就是系统上电之后运行的第一条语句。也就是说这部分代码的二进制码必须位于内存的最开始部分(这正是低端存放模式),因为上电后CPU会从SDRAM的0x00000000处取第一条指令并执行。

Address Instruct

0x00000000: b Handle_Reset

0x00000004: b HandleUndef

0x00000008: b HandleSWI

0x0000000C: b HandlePrefetchAbort

0x00000010: b HandleDataAbort

0x00000014: b HandleNotUsed

0x00000018: b HandleIRQ

0x0000001C: b HandleFIQ

上面是该程序段在系统上电后加载到内存后的分布情况,我们可以看到每条指令占用了4个字节。

上电后,PC指针会跳转到Handle_Reset处开始运行。以后系统每当有异常出现,则CPU会根据异常号,从内存的0x00000000处开始查表做相应的处理,比如系统触发了一个IRQ异常,IRQ为第6号异常,则CPU将把PC指向0x00000018地址(4*6=24=0x00000018)处运行,该地址的指令是跳转到“中断异常服务例程”(HandleIRQ)处运行。以上就是我对异常向量表的一个简单介绍。现在可以进入我们文章的主题“中断异常处理”,s3c2410的中断分快中断(FIQ和普通中断(IRQ),我们讨论的重点是普通中断(IRQ)。

s3c2410的中断异常处理模块总共由以下寄存器构成

SRCPND(SOURCE PENDING REGISTER

INTMOD(INTERRUPT MODE REGISTER

INTMSK(INTERRUPT MASK REGISTER

PRIORITY( PRIORITY REGISTER

INTPND(INTERRUPT PENDING REGISTER

INTOFFSET(INTERRUPT OFFSET REGISTER

SUBSRCPND (INTERRUPT SUB SOURCE PENDING

INTSUBMSK (INTERRUPT SUB MASK REGISTER)

下面我将讲解每个寄存器在一个中断处理流程中所扮演的角色:

SRCPND/ SUBSRCPND这两个寄存器在功能上是相同的,它们是中断源引脚寄存器,在一个中断异常处理流程中,中断信号传进中断异常处理模块后首先遇到的就是SRCPND/

SUBSRCPND,这两个寄存器的作用是用于标示出哪个中断请求被触发。SRCPND的有效位为32,SUBSRCPND 的有效位为11,它们中的每一位分别代表一个中断源。SRCPND为主中断源引脚寄存器,SUBSRCPND为副中断源引脚寄存器。

这里列举出SRCPND的各个位信息:

每个位的初始值皆为0。假设现在系统触发了TIMER0中断,则第10bit将被置1,代表TIMER0中断被触发,该中断请求即将被处理(若该中断没有被屏蔽的话)。SUBSRCPND情况与SRCPND相同,这里就不多讲了。

INTMOD寄存器有效位为32位,每一位与SRCPND中各位相对应,它的作用是指定该位相应的中断源处理模式(IRQ还是FIQ)。若某位为0,则该位相对应的中断按IRQ模式处理,为1则以FIQ模式进行处理,该寄存器初始化值为0x00000000,即所有中断皆以IRQ模式进行处理。(详细请参考s3c2410操作手册)。INTMSK/ INTSUBMSK寄存器为中断屏蔽寄存器,INTMSK为主中断屏蔽寄存器,INTSUBMSK为副中断屏蔽寄存器。INTMSK有效位为32,INTSUBMSK有效位为11,这两个寄存器各个位与SRCPND和SUBSRCPND分别对应。它们的作用是决定该位相应的中断请求是否被处理。若某位被设置为1,则该位相对应的中断产生后将被忽略(CPU不处理该中断请求),设置为0则对其进行处理。这两个寄存器初始化后的值是0xFFFFFFFF和

0x7FF,既默认情况下所有的中断都是被屏蔽的。

到目前为止我们总共讲解了SRCPND,INTMOD,INTMSK,SUBSRCPND,INTSUBMSK

五个寄存器,在继续讲解PRIORITY寄存器之前我们先来看一张图。

先弄清楚一点,现在要讨论的是一个中断优先级的判断问题。为什么会有中断有先级的问题呢?我们知道CPU某个时刻只能对一个中断源进行中断处理,如果现在有3个中断同时发生了,那CPU要按什么顺序处理这个3个中断呢?这正是引入优先级判断的原因所在,通过优先级判断,CPU可以按某种顺序逐个处理中断请求。3sc2410的优先级判断分为两级。

如上图所示,SRCPND寄存器对应的32个中断源总共被分为6个组,每个组由一个ARBITER(0~5)寄存器对其进行管理。中断必须先由所属组的ARBITER(0~5)进行第一次优先级判断(第一级判断)后再发往ARBITER6进行最终的判断(第二级判断)。ARBITER(0~5)这六个组的优先级已经固定,我们无法改变,也就是说由ARBITER0控制的该组中断优先级最高(该组产生的中断进行第一级判断后永远会以REQ0向ARBITER6传递过去)其次是ARBITER1, ARBITER2, ARBITER4, ARBITER4, ARBITER5.我们能够控制的是某个组里面各个中断的优先级顺序。怎么控制?通过PRIORITY寄存器进行控制:]

以下是PRIORITY寄存器各个位的参数表

从表上我们可以知道PRIORITY寄存器内部各个位被分为两种类型,一种是ARB_MODE,另一种为

ARB_SEL, ARB_MODE类型有5组对应ARBITER(2~6)(PS:此处应更正为ARB_MODE类型有7组对应ARBITER (0~6),在datasheet中上表还有续表,为ARB_MODE1-0),ARB_SEL类型有7组对应ARBITER(0~6)。现

在我将以ARBITER2为例,讲解中断组与PRIORITY寄存器中ARB_SEL, ARB_MODE之间的相互关系。

首先我们看到ARBITER2寄存器管理的该组中断里包括了6个中断,分别是INT_TIMER0,INT_TIMER1,INT_TIMER2,INT_TIMER3,INT_TIMER4,INT_UART2,她们的默认中断请求号分别为REQ0,REQ1,REQ2,REQ3,REQ4,REQ5。我们先看PRIORITY寄存器中的ARB_SEL2,该参数由两个位组成,初始值为00。从该表可以看出00定义了一个顺序0-1-2-3-4-5,这个顺序就是这组中断组的优先级排列,这个顺序指明了以中断请求号为0(REQ0)的INT_TIMER0具有最高的中断优先级,其次是INT_TIMER1,INT_TIMER2…。假设现在ARB_SEL2的值被我们设置为01。则一个新的优先级次序将被使用,01对应的优先级次序为0-2-3-4-1-5,从中可以看出优先级最高和最低的中断请求和之前没有变化,但本来处于第2优先级的INT_TIMER1中断现在变成了第5优先级。从ARB_SEL2被设置为00,01,10,11各个值所出现的情况我们可以看出,除最高和最低的优先级不变以外,其他各个中断的优先级其实是在做一个旋转排列(rotate)。为了达到对各个中断平等对待这一目标,我们可以让优先级次序在每个中断请求被处理完之后自动进行一次旋转,如何自动让它旋转呢?我们可以通过ARB_MODE2达到这个目的,该参数只有1个 bit,置1代表开启对应中断组的优先级次序旋转,0则为关闭。事实上当该位置为1之后,每处里完某个组的一个中断后,该组的ARB_SEL便递增在1(达到11后恢复为00)。

现在我们另ARB_MODE2=1,ARB_SEL2=00,则当前ARBITER2的优先级顺序为0-1-2-3-4-5,假设现在该组的1号中断请求INT_TIMER1和2号中断请求INT_TIMER2被同时触发,CPU根据优先级判断后决定先把INT_TIMER1中断向ARBITER6进行发送(在ARBITER6做第最终优先级判断),接着再向ARBITER6发送

INT_TIMER2中断。请注意,在INT_TIMER1被处理完毕后,该组中段的优先级次序被自动做了一次旋转,旋转后ARBITER2的优先级顺序变为0-2-3-4-1-5。假设之后某个时刻该组的INT_TIMER1和INT_TIMER2又被同时触发,则此时CPU优先处理的会是INT_TIMER2。若我们另ARB_MODE2=0,则改组的中断优先级次序在任何情况下都不做任何改变,除非我们人为地重新设置了ARB_SEL2的值。

呼。。。好累。。。终于说完了麻烦的优先级-_-…继续。。。

INTPND寄存器可能是整个中断处理过程中我们要特别注意的一个寄存器了,他的操作比较特别,怎么特别?请听我慢慢道来.:]

先看一下该寄存器各位详细功能列表

正如你所见的,INTPND寄存器与SRCPND长得一模一样,但他们在中断异常处理中却扮演着不同的角色,如果说SRCPND是中断信号进入中断处理模块后所经过的第一个场所的话,那么INTPND则是中断信号在中断处理模块里经历的最后一个寄存器。它的每个位对应一个中断请求,若该位被置1,则表示相应的中断请

求被触发,描述到这里你可能会发现它不仅和SRCPND长得一模一样,就连功能都一样,其实不然,他们在功能上有着重大的区别。SRCPND是中断源引脚寄存器,某个位被置1表示相应的中断被触发,但我们知道在同一时刻内系统可以触发若干个中断,只要中断被触发了,SRCPND的相应位便被置1,也就是说SRCPND在同一时刻可以有若干位同时被置1,然而INTPND则不同,他在某一时刻只能有1个位被置1,INTPND 某个位被置1(该位对应的中断在所有已触发的中断里具有最高优先级且该中断没有被屏蔽),则表示CPU即将或已经在对该位相应的中断进行处理。于是我们可以有一个总结:SRCPND说明了有什么中断被触发了,INTPND说明了CPU即将或已经在对某一个中断进行处理。

特别注意:每当某一个中断被处理完之后,我们必须手动地把SRCPND/SUBSRCPND , INTPND三个寄存器中与该中断相应的位由1设置为0,刚才我说INTPND的操作很特别,它的特别之处就在于对当我们要把该寄存器中某个值为1的位设置为0时,我们不是往该位置0,而是往该位置1。假设SRCPND=0x00000003,

INTPND=0x00000001,该值说明当前0号中断和1号中断被触发,但当前正在被处理的是0号中断,处理完毕后我们应该这样设置INTPND和SRCPND:

SRCPND="0x00000002" //位0被置为0

INTPND =0x00000001 //位0被置为0(方法是往该位写入1)

INTOFFSET寄存器的功能则很简单,它的作用只是用于表明哪个中断正在被处理。下面是该寄存器各位详细功能列表

若当前INT_TIMER0被触发了,则该寄存器的值为10,以此类推。

现在我把整个中断流程用一个图加以说明

以上这个图清楚地说明了一个中断异常处理流程。

下面我用INT_TIMER0, INT_TIMER2和INT_UART0三个中断完整地介绍一次中断异常处理。首先我们得做几个假设:

假设1:这三个中断的屏蔽被取消。

假设2:PRIORITY寄存器中ARB_MODE2,ARB_MODE5皆为0,既不进行优先级的自动旋转排序,任何时候

ARBITER2,ARBITER5控制的中断组优先级次序分别为0-1-2-3-4-5和1-2-3-4。

假设3:这三个中断皆为IRQ类型。

假设4:这三个中断同时被触发。

INT_TIMER0,INT_TIMER2和INT_UART0三个中断被同时触发,此时三个中断信号流向SRCPND寄存器,使该寄存器中的第10位,12位,28位被置为1,中断信号继续向前流经INTMASK寄存器,这三个中断都没有被屏蔽,于是信号进一步流经INTMODE寄存器,这三个中断皆为IRQ类型,故中断信号继续向前流向PRIORITY寄存器,经过优先级判断,INT_TIMER0中断信号使INTPND寄存器的第10位置1(INT_TIMER0优先级最高),此时INTOFFSET寄存器的值为10,CPU转向相应的中断服务例程进行处理。处理完毕后,我们的程序将INTPND和SRCPND的第10置为0,至此INT_TIMER0中断处理完毕。此时SRCPND的第12位,28位仍为1(这两个中断请求未被处理),故他们会继续被CPU已刚才描述的方式进行处理。

中断异常处理就先讲到这吧:]

PS:

在对2410的裸板进行中断实验的过程中,从菜鸟的角度出发,我把学到了一些东西和之前ARM体系结构的理论结合起来:

1、在ARM处理器中,r13(sp)和r14(lr)分别对应6个不同状态下的物理寄存器,其中1个是用户、系统模式共用的,其他分别对应5种异常模式(Exception Mode)。要在后续程序中使用中断,则应先把要用到的各种模式的堆栈设置好,如设置IRQ和系统模式的sp:

msr cpsr_c, #0xd2 @进入IRQ模式,IRQ和FIQ都处于禁止状态

ldr sp,=0x33000000

msr cpsr_c, #0xdf @进入系统模式,IRQ和FIQ都处于禁止状态

ldr sp,=0x34000000

2、如果用到按键等中断控制,是属于外部中断的(External Interrupt),就需要配置EINT相关的寄存器。

中断管理函数

中断管理函数 CM3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且具有256级的可编程中断设置。但STM32并没有使用CM3内核的全部东西,而是只用了它的一部分。STM32有76个中断,包括16个内核中断和60个可屏蔽中断,具有16级可编程的中断优先级。而我们常用的就是这60个可屏蔽中断,所以我们就只针对这60个可屏蔽中断进行介绍。 在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体: typedef struct { vu32 ISER[2]; u32 RESERVED0[30]; vu32 ICER[2]; u32 RSERVED1[30]; vu32 ISPR[2]; u32 RESERVED2[30]; vu32 ICPR[2]; u32 RESERVED3[30]; vu32 IABR[2]; u32 RESERVED4[62]; vu32 IPR[15]; } NVIC_TypeDef; STM32的中断在这些寄存器的控制下有序的执行的。了解这些中断寄存器,你才能方便的使用STM32的中断。下面重点介绍这几个寄存器: ISER[2]:ISER全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。上面说了STM32的可屏蔽中断只有60个,这里用了2个32位的寄存器,总共可以表示64个中断。而STM32只用了其中的前60位。ISER[0]的

bit0~bit31分别对应中断0~31。ISER[1]的bit0~27对应中断32~59;这样总共60个中断就分别对应上了。你要使能某个中断,必须设置相应的ISER位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO口映射等设置才算是一个完整的中断设置)。具体每一位对应哪个中断,请参考 stm32f10x_nvic..h里面的第36行处。 ICER[2]:全称是:Interrupt Clear-Enable Registers,是一个中断除能寄存器组。该寄存器组与ISER的作用恰好相反,是用来清除某个中断的使能的。其对应位的功能,也和ICER一样。这里要专门设置一个ICER来清除中断位,而不是向ISER写0来清除,是因为NVIC的这些寄存器都是写1有效的,写0是无效的。具体为什么这么设计,请看《CM3权威指南》第125页,NVIC概览一章。 ISPR[2]:全称是:Interrupt Set-Pending Registers,是一个中断挂起控制寄存器组。每个位对应的中断和ISER是一样的。通过置1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写0是无效的。 ICPR[2]:全称是:Interrupt Clear-Pending Registers,是一个中断解挂控制寄存器组。其作用与ISPR相反,对应位也和ISER是一样的。通过设置1,可以将挂起的中断接挂。写0无效。 IABR[2]:全称是:Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和ISER一样,如果为1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。 IPR[15]:全称是:Interrupt Priority Registers,是一个中断优先级控制的寄存器组。这个寄存器组相当重要!STM32的中断分组与这个寄存器组密切相关。IPR寄存器组由15个32bit的寄存器组成,每个可屏蔽中断占用8bit,这样总共可以表示15*4=60个可屏蔽中断。刚好和STM32的可屏蔽中断数相等。IPR[0]的[31~24],[23~16],[15~8],[7~0]分别对应中中断3~0,依次类推,总共对应60个外部中断。而每个可屏蔽中断占用的8bit并没有全部使用,而是只用了高4位。这4位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几个位又要根据SCB->AIRCR中中断分组的设置来决定。 这里简单介绍一下STM32的中断分组:STM32将中断分为5个组,组0~4。该分组的设置是由SCB->AIRCR寄存器的bit10~8来定义的。具体的分配关系如下表所示:

中断异常处理流程

计算机体系结构中,异常或者中断是处理系统中突发事件的一种机制,几乎所有的处理器都提供这种机制。异常主要是从处理器被动接受的角度出发的一种描述,指意外操作引起的异常。而中断则带有向处理器主动申请的意味。但这两种情况具有一定的共性,都是请求处理器打断正常的程序执行流程,进入特定程序的一种机制。若无特别说明,对“异常”和“中断”都不作严格的区分。本文结合经过实际验证的代码对ARM9中断处理流程进行分析,并设计出基于S3C2410芯片的外部中断处理程序。 1.异常中断响应和返回 系统运行时,异常可能会随时发生。当一个异常出现以后,ARM微处理器会执行以下几步操作: 1) 将下一条指令的地址存入相应连接寄存器LR,以便程序在处理异常返回时能从正确的位置重新开始执行。 2)将CPSR复制到相应的SPSR中。 3)根据异常类型,强制设置CPSR的运行模式位。 4) 强制PC从相关的异常向量地址取下一条指令执行,从而跳转到相应的异常处理程序处。 这些工作是由ARM内核完成的,不需要用户程序参与。异常处理完毕之后,ARM微处理器会执行以下几步操作从异常返回: 1)将连接寄存器LR的值减去相应的偏移量后送到PC中。 2)将SPSR复制回CPSR中。 3) 若在进入异常处理时设置了中断禁止位,要在此清除。 这些工作必须由用户在中断处理函数中实现。为保证在ARM处理器发生异常时不至于处于未知状态,在应用程序的设计中,首先要进行异常处理。采用的方式是在异常向量表中的特定位置放置一条跳转指令,跳转到异常处理程序。当ARM处理器发生异常时,程序计数器PC会被强制设置为对应的异常向量,从而跳转到异常处理程序。当异常处理完成以后,返回到主程序继续执行。可以认为应用程序总是从复位异常处理程序开始执行的,因此复位异常处理程序不需要返回。 2.异常处理程序设计 2.1 异常响应流程

异常处理机制

异常的基本概念 异常是导致程序终止运行的一种指令流,如果不对异常进行正确的处理,则可能导致程序的中断执行,造成不必要的损失。 在没有异常处理的语言中如果要回避异常,就必须使用大量的判断语句,配合所想到的错误状况来捕捉程序中所有可能发生的错误。 Java异常处理机制具有易于使用、可自行定义异常类、处理抛出的异常同时又不会降低程序运行的速度等优点。因而在java程序设计时应充分地利用java的异常处理机制,以增进程序的稳定性及效率。 当程序中加入了异常处理代码,所以当有异常发生后,整个程序并不会因为异常的产生而中断执行。而是在catch中处理完毕之后,程序正常的结束。 在整个java异常的结构中,实际上有两个最常用的类,分别为Exception和Error 这两个类全都是Throwable的子类。 Exception:一般表示的是程序中出现的问题,可以直接使用try……catch处理。 Error:一般值JVM错误,程序中无法处理。 Java异常处理机制。 在整个java的异常处理中,实际上也是按照面向对象的方式进行处理,处理的步骤如下: 1)一旦产生异常,则首先会产生一个异常类的实例化对象。 2)在try语句中对此异常对象进行捕捉。 3)产生的异常对象与catch语句中的各个异常类型进行匹配,如果匹配成功则执行catch语句中的代码。 异常处理 在定义一个方法时可以使用throws关键字声明,表示此方法不处理异常,而交给方法的调用处进行处理,在方法调用处不管是否有问题,都要使用try……catch块进行异常的捕获与处理。 如果在主方法中使用throws关键字,则程序出现问题后肯定交由jvm处理,将导致程序中断。 与throws关键字不同的是,throw关键字人为的抛出一个异常,抛出时直接抛出异常类的实例化对象即可。 Exception在程序中必须使用try……catch进行处理。RuntimeException可以不使用try……catch进行处理,但是如果有异常产生,则异常将由JVM进行处理。(建议RuntimeException的子类也使用try……catch进行处理,否则产生的异常交给jvm处理会导致程序中断。) 继承关系: Exception》RuntimeException》lllegalArgumentException》NumberFormatException; 异常类必须继承于Exception 建议:继承Exception一般要添加全部父类型一样的构造器! class NameOrPwdException extends Exception { public NameOrPwdException() {

S3C2410触摸屏驱动程序原理图

S3C2410触摸屏驱动程序原理图 本文介绍了基于三星S3C2410X微处理器,采用SPI接口与ADS7843触摸屏控制器芯片完成触摸屏模块的设计。具体包括在嵌入式Linux操作系统中的软件驱动开发,采用内核定时器的下半部机制进行了触摸屏硬件中断程序设计,采用16个时钟周期的坐标转换时序,实现触摸点数据采集的方法,给出了坐标采集的流程。设计完成的触摸屏驱动程序在博创公司教学实验设备UP-NETARM2410-S平台上运行效果良好。 引言 随着信息家电和通讯设备的普及,作为与用户交互的终端媒介,触摸屏在生活中得到广泛的应用。如何在系统中集成触摸屏模块以及在嵌入式操作系统中实现其驱动程序,都成为嵌入式系统设计者需要考虑的问题。本文主要介绍在三星S3C2410X微处理器的硬件平台上进行基于嵌入式Linux的触摸屏驱动程序设计。 硬件实现方案 SPI接口是Motorola推出的一种同步串行接口,采用全双工、四线通信系统,S3C2410X是三星推出的自带触摸屏接口的ARM920T内核芯片,ADS7843为Burr-Brown生产的一款性能优异的触摸屏控制器。本文采用SPI接口的触摸屏控制器ADS7843外接四线电阻式触摸屏,这种方式最显著的特点是响应速度更快、灵敏度更高,微处理器与触摸屏控制器间的通讯时间大大减少,提高了微处理器的效率。ADS7843与S3C2410的硬件连接如图1所示,鉴于ADS7843差分工作模式的优点,在硬件电路中将其配置为差分模式。 图1触摸屏输入系统示意图 嵌入式Linux系统下的驱动程序 设备驱动程序是Linux内核的重要组成部分,控制了操作系统和硬件设备之间的交互。Linux 的设备管理是和文件系统紧密结合的,各种设备都以文件的形式存放在/dev目录下,成为设备文件。应用程序可以打开、关闭、读写这些设备文件,对设备的操作就像操作普通的数据文

STM32外部中断以及中断优先级

外部中断的初始化过程: 1.初始化IO为输入(可以设置上拉,下拉,浮空) 2.开启IO复用时钟 3.开启与该IO相对的线上(详解下) 4.配置NVIC,使能中断 5.编写中断服务函数 外部中断: Stm32中总共有19个外部中断 包括: 线0-15:IO输入中断(每条线上最多有7个IO,如GPIOA~GPIOG,但是每一条线每次只允许同时连接到一个IO)

线16:PVD 线17:RTC 线18:USB 关于优先级: CM3中内核支持256个中断(16个内核+240外部)和可编程256级中断优先级的设置

Stm32目前支持84个中断(16个内核+68个外部,注:不是指68个外部中断),16级可编程优先级(优先级设置寄存器中使用了4位)

注意:其中外部中断5-9和中断10-15向量存放在一起 优先级: 数值低的优先级要高于数值高的!!!!!! 上电复位后,系统默认使用的是组0; 一个系统只能使用一组优先级组,不可使用多个,优先级的设置不能超过组的范围,否则会产生不可预计的错误 1.高抢先级的中断可以打断低优先级的中断响应,构成中断嵌套 2.相同抢先级的中断不可以构成嵌套,系统会优先响应子优先级高的

3.当2(n)个相同抢先优先级和相同子优先级的中断出现,STM32首先响应中断通道所对应的中断向量地址低的那个中断 4.0号抢先优先级的中断,可以打断任何中断抢先优先级为非0号的中断;1号抢先优先级的中断,可以打断任何中断抢先优先级为2、3、4号的中断;……;构成中断嵌套。 5.所有外部中断通道的优先级控制字PRI_n也都是0,68个外部中断通道的抢先优先级都是0号,没有子优先级的区分。不会发生任何的中断嵌套行为,谁也不能打断当前正在执行的中断服务。当多个中断出现后,则看它们的中断向量地址:地址越低,中断级别越高,STM32优先响应

ARM异常中断机制.

ARM9(以S3C2410为例)中断机制 一、ARM异常机制介绍 ARM9处理器有7种工作模式。分别是(除了用户模式其他都是异常模式 用户模式(usr:ARM处理器正常的程序执行状态。 快速中断模式(fiq:用于高速数据传输或通道处理。 外部中断模式(irq:用于通用的中断处理。 管理模式(svc:操作系统使用的保护模式。 数据访问终止模式(abt:当数据或指令预取终止时进入该模式。 系统模式(sys:运行具有特权的操作系统任务。 未定义指令中止模式(und:当未定义的指令执行时进入该模式。 每种模式通过5位二进制编码进行标示: 用户模式10000 快速中断模式10001 外部中断模式10010 管理模式10011 数据访问终止模式10111 未定义指令中止模式11011 系统模式11111 模式编码存放在CPSR(程序当前状态寄存器,记录当前工作模式的编码的值)中的[4:0]。

快速中断模式、外部中断模式、数据访问终止模式、未定义指令中止模式、管理模式称为异常模式。 异常类型具体含义 复位当处理器的复位电平有效时,产生复位异常,程序跳转到复位异常处理程序处执行。 未定义指令遇到不能处理的指令时,产生未定义指令异常。 软件中断该异常由执行SWI指令产生,可用于用户模式下的程序调用特权操作指令。可使用该异常机制实现系统功能调用。 指令预取中止若处理器预取指令的地址不存在,或该地址不允许当前指令访问,存储器会向处理器发出中止信号,但当预取的指令被执行时,才会产生指令预取中止异常。 数据中止若处理器数据访问指令的地址不存在,或该地址不允许当前指令访问时,产生数据中止异常。 IRQ(外部中断请求)当处理器的外部中断请求引脚有效,且CPSR中的I 位为0时,产生IRQ异常。系统的外设可通过该异常请求中断服务。 FIQ(快速中断请求)当处理器的快速中断请求引脚有效,且CPSR中的F 位为0时,产生FIQ异常。 当多个异常发生时,处理器根据优先级进行处理。优先级

异常情况处理制度及流程

山西煤炭运销集团 蒲县昊锦塬煤业有限公司异常情况处理制度为认真贯彻落实国家、省、市关于集中开展安全生产大检查的工作安排要求,加强我矿信息监控系统管理水平,做好矿井生产过程中井下环境参数的有效监控,保障矿井安全生产,加强煤矿安全生产管理水平及抗灾能力,特制定本矿异常情况处理制度如下: 一、值班人员按《中心岗位责任制》规定,浏览查询煤矿安全信息,发现异常情况及时处理,并认真填写《异常情况报告处理表》,传真至县监控中心。 二、监控室值班人员发现系统发出异常报警后,值班人员必须立即通知监控室主任、分管领导,同时立即通知矿井调度部门,由监控室主任或分管领导组织相关人员对本次异常报警进行原因分析,并按规定程序及时报上一级网络中心。处理结果应记录备案。调度值班人员接到报警、断电信息后,应立即向矿值班领导汇报,矿值班领导按规定指挥现场人员停止工作,断电时撤出人员。处理过程应记录备案。当系统显示井下某一区域瓦斯超限并有可能波及其他区域时,矿井有关人员应按瓦斯事故应急预案手动遥控切断瓦斯可能波及区域的电源。值班人员接到网络中心发出的报警处理指令后,要立即处理落实,并将处理结果向网络中心反馈。 当工作面瓦斯浓度达到报警浓度时,值班人员应立即通知矿值班领导及监控室主任,并填写异常情况处理报告表传真上报至

县监控中心

;由分管领导或监控室主任安排相关人员进行原因分析,按照瓦斯超限分析原则:①按人工检测值与甲烷传感器对比分析; ②按报警地点的历史曲线对比分析;③按报警地点上风侧检测值对比分析。根据分析结果立即将处理措施下达至矿调度中心按处理措施严格执行。报警期间要采取安全措施,报警消除后将报警的起止时间、分析报告、采取措施和处理结果上报县监控室并存档备案。 三、当煤矿通讯中断、无数据显示时,值班人员要通过传真(或电话)向县监控中心报告,并查明原因,恢复通讯。情况紧急的,由值班人员立即向矿领导汇报,对因故造成通讯中断未及时上报的,要通过电话联系移动公司或长途线务局进行抢修。

实验五--单片机中断优先级实验

实验五单片机中断优先级实验 一、实验目的 1.理解AT89C51单片机中断优先级和优先权。 2.用PROTEUS设计、仿真基于AT89C51单片机的中断优先级实验。 3.掌握中断编程。 4.掌握发光二极管的控制方法。 二、实验要求 单片机主程序控制P0口数码管循环显示0~8;外中断(INT0)、外中断(INT1)发生时分别在P2、P1口依次显示0~8;INT1为高优先级,INT0为低优先级。 三、电路设计 ④CAP、CAP-ELEC:电容、电解电容; ⑤CRYSTAL:晶振; ⑥BUTTON:按钮。

2.放置元器件 3.放置电源和地 4.连线 5.元器件属性设置 6.电气检测 四、源程序设计、生成目标代码文件 1.流程图 2.源程序设计 通过菜单“sourc e→Add/Remove Source Files…”新建源程序文件:DZC35.ASM。 通过菜单“sourc e→DZC35.ASM”,打开PROTEUS提供的文本编辑器SRCEDIT,在其中编辑源程序。 程序编辑好后,单击按钮存入文件DZC35.ASM。 3.源程序编译汇编、生成目标代码文件 通过菜单“sourc e→Build All”编译汇编源程序,生成目标代码文件。若编译失败,可对程序进行修改调试直至汇编成功。 五、PROTEUS仿真 1.加载目标代码文件 2.全速仿真 单击按钮,启动仿真。 (1)低优先级INT0中断主程序:当主程序运行时,单片机控制与P0

口相接的数码管循环显示1~8;而P1、P2口的数码管不显示。当前主程序控制P0口显示“8”的时刻单击“低优先级输入”按钮,触发INT0如图所示,INT0服务程序控制P2口依次显示1~8,当前显示“2”。 (2)高优先级INT1中断低优先级INT0;在上一步的基础上,即主程序被INT0中断在P0口输出“8”,而在INT0服务程序在P2口输出“2”的时刻,单击“高优先级输入”按钮,触发高优先级INT1,所在INT0被中断在显示“2”,INT1服务程序控制P1口依次显示1~8。 3.仿真调试 六、思考题: 1.说明单片机中共有哪几种中断,它们的默认优先级是什么? 2.怎样修改中断优先级?例如在本实验中要使TIMER1成为优先级最高的中断,该怎么处理?

设备故障处置过程中的九大错误与解决办法

设备故障 处置过程中的九大错误与解决办法设备故障处理是设备管理和维修人员经常会面对的问题之 O 维修人员在日常的设备故障检查处理过程中,外部受时间、环境、人员等方面的压力,内部受维修人员本身的技术水平、经验、设备熟悉程度、人员身体精神状态等的影响,这些因素,会对故障快速、准确的处置造成一定的影响。 维修人员对设备故障的排查和处置不当,会导致故障处置时间、人力、成本等的增加,或为下次故障留下隐患。 问题一.不能正确判断分析故障,盲目大拆大卸 1、现象: —些维修人员由于对机械结构、原理不清楚,未认真分析清楚故障原因,不能准确判断故障部位,凭着〃大概、差不多〃的思想盲目对机械大拆大卸,结果不但原故障未排除,而且由于维修技能和工艺较差,又出现新的问题。 2、解决办法: 当机械出现故障后,要通过检测设备进行检测,如无检测设备,可通过"问、看、查、试〃等传统的故障判断方法和手段,结合工程机

械的结构和工作原理,确定最可能发生故障的部位。在判定工程机械故障时,一般常用〃排除法〃和〃比较法",按照从简单到复杂、先外表后内部、先总成再部件的顺序进行,切忌"不问青红皂白,盲目大拆大卸"。 问题二■盲目更换零部件,一味"换件修理" 1、现象: 有些维修人员一贯采用换件试验的方法,不论大件小件,只要认为可能是导致故障的零部件,一个一个更换试验,结果非但故障没排除,且把不该更换的零部件随意更换了,增加了消费者的开支。还有些故障零部件完全可以通过修理恢复其技术性能,不需要复杂修理工艺即可修复,但维修人员却要求用户更换新件,一味采取〃换件修理"的方法,造成严重的浪费。 2、解决办法: 在维修时,应根据故障现象认真分析判断故障原因及部位,对能修复的零部件要采取修理的方法恢复技术性能,杜绝盲目更换零部件的做法。 问题三、不检查新件质量,装配后出现故障 1、现象: 在更换配件前,有些维修人员对新配件不做技术检查,皇来后直接安装到设备上,这种做法是不科学的。目前市场上出售的零配件质量良

S3C2410中文手册第7章_时钟和功率管理

第七章时钟和功率管理 概述 时钟和功率管理模块由三部分组成:时钟控制,USB控制和功率控制。 S3C2410A的时钟控制逻辑能够产生系统所需要的时钟,包括CPU的FCLK,AHB总线接口的HCLK,和APB总线接口的PCLK。S3C2410A有两个PLL,一个用于FCLK,HCLK,PCLK,另一个用于USB模块(48MHZ)。时钟控制逻辑能够由软件控制不将PLL连接到各接口模块以降低处理器时钟频率,从而降低功耗。 S3C2410A有各种针对不同任务提供的最佳功率管理策略,功率管理模块能够使系统工作在如下4种模式:正常模式,低速模式,空闲模式和掉电模式。 正常模式:功率管理模块向CPU和所有外设提供时钟。这种模式下,当所有外设都开启时,系统功耗将达到最大。用户可以通过软件控制各种外设的开关。例如,如果不需要定时器,用户可以将定时器时钟断开以降低功耗。 低速模式:没有PLL的模式。与正常模式不同,低速模式直接使用外部时钟(XTIpll或者EXTCLK)作为FCLK,这种模式下,功耗仅由外部时钟决定。 空闲模式:功率管理模块仅关掉FCLK,而继续提供时钟给其他外设。空闲模式可以减少由于CPU核心产生的功耗。任何中断请求都可以将CPU从中断模式唤醒。 掉电模式:功率管理模块断开内部电源。因此CPU和除唤醒逻辑单元以外的外设都不会产生功耗。要执行掉电模式需要有两个独立的电源,其中一个给唤醒逻辑单元供电,另一个给包括CPU在内的其他模块供电。在掉电模式下,第二个电源将被关掉。掉电模式可以由外部中断EINT[15:0]或RTC唤醒。 功能描述 时钟结构 图7-1描述了时钟架构的方块图。主时钟源由一个外部晶振或者外部时钟产生。时钟发生器包括连接到一个外部晶振的振荡器和两个PLL(MPLL和UPLL)用于产生系统所需的高频时钟。 时钟源选择 表7-1描述了模式控制引脚(OM3和OM2)和选择时钟源之间的对应关系。OM[3:2]的状态由OM3和OM2引脚的状态在nRESET的上升沿锁存得到。 注意:1、尽管MPLL在系统复位的时候就开始产生,但是只有有效的设置号

STM32 中断优先级理解

CM3 内核支持256 个中断,其中包含了16 个内核中断和240 个外部中断,并且具有256级的可编程中断设置。但STM32 并没有使用CM3 内核的全部东西,而是只用了它的一部分。STM32 有84 个中断,包括16 个内核中断和68 个可屏蔽中断,具有16 级可编程的中断优先级。而我们常用的就是这68 个可屏蔽中断,但是STM32 的68 个可屏蔽中断,在STM32F103 系列上面,又只有60 个 (在107 系列才有68 个)。 在MDK 内,与NVIC 相关的寄存器,MDK 为其定义了如下的结构体: 点击(此处)折叠或打开 1.typedef struct 2.{ 3.vu32 ISER[2]; 4.u32 RESERVED0[30]; 5.vu32 ICER[2]; 6.u32 RSERVED1[30]; 7.vu32 ISPR[2]; 8.u32 RESERVED2[30]; 9.vu32 ICPR[2]; 10.u32 RESERVED3[30]; 11.vu32 IABR[2]; 12.u32 RESERVED4[62]; 13.vu32 IPR[15]; 14.} NVIC_TypeDef; STM32 的中断在这些寄存器的控制下有序的执行的。只有了解这些中断寄存器,才能了解STM32 的中断。下面简要介绍这几个寄存器: ISER[2]:I SER 全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。上面说了STM32F103 的可屏蔽中断只有60 个,这里用了 2 个32 位的寄存器,总共可以表示64 个中断。而STM32F103 只用了其中的前60 位。ISER[0]的bit0~bit31 分别对应中断0~31。ISER[1]的bit0~27 对应中断32~59;这样总共60 个中断就分别对应上了。你要使能某个中断,必须设置相应的ISER 位为1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO 口映射等设置才算是一个完整的中断设置)。具体每一位对应哪个中断,请参考stm32f10x_nvic..h 里面的第36 行处。 ICER[2]:全称是:Interrupt Clear-Enable Registers,是一个中断除能寄存器组。该寄存器组与ISER 的作用恰好相反,是用来清除某个中断的使能的。其对应位的功能,也和ICER 一样。这里要专门设置一个ICER 来清除中断位,而不是 向ISER 写0 来清除,是因为NVIC 的这些寄存器都是写 1 有效的,写0 是无效的。 ISPR[2]:全称是:Interrupt Set-Pending Registers,是一个中断挂起控制寄存器组。每个位对应的中断和ISER 是一样的。通过置1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写0 是无效的。

异常情况处理流程说明

异常情况处理流程说明 一、“异常情况”包括 1、质量不合格问题。主要包括制程质量问题、售后质量问题、技术设计或图纸下发后出现问题、调试中 质量问题、外购设备物资质量问题等; 2、交货期延误问题、采购交期延误问题及其他有关生产进度的问题等; 3、生产物料损耗异常问题; 4、生产设备损坏问题; 5、员工违纪问题; 6、其它异常问题。 二、员工出现异常问题,应及时按规定报于部门领导; 三、企管部(质检部)在日常工作中发现员工出现异常问题时,应作出《整改通知》或《整改报告》,由 责任部门签收; 四、员工所属部门部长应及时落实责任人并对问题组织处理。责任人是指直接或间接造成各类问题发生的 员工包括各级管理人员。 五、责任部门部长应督促责任人填写《异常情况处理报告》,责任人应根据问题发生的原因、经过、问题 的现象或后果、问题发生的时间和发现时间,进行详细如实填写,并随后签字确认; 六、责任人填写完毕交直接主管进行原因分析,提出解决措施,并填写《异常情况处理报告》,上交部门 负责人。 1、责任人的直接主管为班长的,该班长应根据问题的具体情况认真分析,确定属于哪种原因,并分析自 己在问题中所负的责任,必须认真填写明白,不得包庇、隐瞒; 2、责任人的直接主管为部长的,则由责任人所属部门部长填写; 3、责任人为部长的,责任人可以不填写此栏,只填写“问题描述”和“责任部门处理意见”; 4、责任人为副总的,责任人填写“问题描述”和“处理意见”; 七、责任人所属部门部长应详细调查、分析问题,确定解决措施,并填写处理报告,依据公司的有关规定 并分析自己在问题中所负的责任,做出公平、公正的处理意见;该部长应本着认真客观的态度对待问题,反思自己工作的欠缺,及时纠正并预防问题的再次发生。 八、责任部门将报告交分管副总,分管副总分析问题发生原因和相关负责人的处理意见,根据公司的有关 规定,对责任人做出处理意见;并由责任部门部长将报告交企管部(质检部); 九、企管部长(质检部长)实施监督职责,本着公平、公正地原则,对问题深入分析,不确定的问题应重 新调查,并分析责任部门的处理建议是否符合公司的有关规定。若符合规定则填写问题处理报告,做出企管部(质检部)的处理意见;若不符合有关规定,或责任部门的处理意见有失公平、公正,则需

S3C2410中断分析

S3C2410中断分析 具体详细解释 这段来自: https://www.360docs.net/doc/8711395164.html,/ghy0504/blog/item/db90649a0f554bbfc8eaf47a.html https://www.360docs.net/doc/8711395164.html,/renpine/archive/2009/10/04/4631854.aspx 具体写的很详细,后面画个图对流程进行详细解释,方便自己查阅,并结合wince里面底层中断的代码分析下。 S3C2410有24个外部中断引脚:EINT0~EINT23,但是对于EINT0~EINT3这4个外部中断而言,使用比较简单;对于其它20个而言,使用稍稍复杂一些。 首先,来看S3C2410的中断控制器,有6个中断裁决器分为2级,第1级5个,第2级1个。第1级的5个裁决器管理32个中断源,在这32个中断源中有2个是保留的,24个是给内部中断源的,而外部中断只给了6个中断:EINT0、EINT1、EINT2、EINT3、EINT4~7、EINT8~23。EINT4~EINT7、EINT8~EINT23都是共享一个中断。 中断控制器中主要的相关寄存器有:INTMSK、SRCPND、PRIORITY、INTPND,还有一个INTMOD。但是对于外部中断还有几个寄存器:EXTINTn、EINTMSK、EINTPEND等。 对于外部中断EINT0~EINT3由于没有共享,因此外部寄存器中只有EXTINT0和它们有关,进行中断触发电平信号的设置。 但是对于其他的20个外部中断而言,所有上面提到的寄存器都有关系。实际上对于 EINT4~EINT23,实际上可以看作有3级屏蔽,第1级屏蔽是CPSR中的I-Bit和F-Bit,第2级屏蔽是EINTMASK([4:23]每一位对应一个相应的外部中断),第3级屏蔽是INTMSK(Bit4、Bit5);对于EINT0~EINT3而言,只是INTMSK中的Bit0~Bit3,因此在变成初始化时应该要特别注意。 在外部中断有中断请求时,由于EINT4~7、EINT8~23分别共享中断,因此在SRCPND 中分别对应Bit4、Bit5,最终导致INTPND中的相应位置1(在任何时刻只能有一个位置1),但是如何分辨这些共享的中断?可以通过查询EINTPEND来进行(Bit4~Bit23分别对应1个外部中断)。由于在相应中断后在服务例程中应将挂起寄存器中相应的位清0来清除未处理状态,因此对于EINT4~7、EINT8~23这20个外部中断的清除挂起寄存器的顺序是: 1. EINTPEND(可能多位同事为1),方法:向要清0的位写1,其它位写0,但要注意由于第4位保留,因此不要试图向第4位写1,可能会导致不可预料的结果。 2.SRCPND(可能多位同时为1),方法:向要清0的位写1,其它位写0。 3.INTPND,方法:向其写本身的数据(即INTPND=INTPND)。

[重点]设备异常处理流程及规定

[重点]设备异常处理流程及规定 设备异常处理流程 序流程图责任人表单作业内容号 班组长/线长不能处生产异常出现时,生产部门/设备生产异常理或异常会导致停产时间超过30分钟 1 相关部门/ 时,应立即上报,或开出《生产异常发现者报告单》进行处理。 生产部负责人接到报告后应在10分钟生产部门/内赶赴现场;必要时可同时通知相关相关人员 2 相关部门/ 部门负责人,相关部门负责人接到通赶赴现场负责人知后应在10分钟内赶到现场( 相关部门负责人到达现场后立即对异相关部门异常分析 3 常进行分析,若部门负责人不能到场负责人应在10分钟内派人到达现场( 如不能立即处理应作出是否停产的意确定是总经办/总4 见,并注明预计恢复生产的时间(停否停产经理产应由总经理批准( 相关部门负责人针对问题应在30分钟制定应急相关部门生产异常 5 内制定出应急处理措施,制定措施时处理措施负责人报告单应尽可能地降低影响生产部门生产异常生产部门按应急措施进行生产按照处理6 负责人报告单调整生产措施生产 生产部/品 质部 NG 应急措施的有效性由生产部与品质部生产异常责任人措施7 共同验证,如验证不符合则重新制定报告单验证相关措施( YES 验证结果符合生产及品质相关要求,生产部负责恢复正8 可以在恢复生产后由品质部和生产部人常生产对异常进行跟进确认(

相关责任部生产恢复正常后相关部门应对问题的生产异常 9 制定长期门深层次的原因加以分析,并在两个工报告单预防措施负责人作日内制定出长期预防措施( 生产部生产异常生产部应协同品质部对责任部门的长10 负责人报告单期预防措施执行结果进行跟踪预防措施跟踪 异常处理规定 1(目的 为了更好的规范和完善公司生产异常处理作业,使生产问题发生后,各部门人员迅速、有效的处理,减免停工时间,提高生产效率,特制定本流程。 2(适用范围 适用于公司所有生产异常的处理。 3(职责 3(1 生产部门负责生产异常的反馈和处理措施验证。 3(2 品质部负责品质异常的处理及验证。 3(3 设备组负责设备异常的处理。 3(4 计控部负责物料异常的处理。 3(5 技术部负责技术、关键工序设备、工装模具、工艺异常的处理。 4(作业规范 4.1 生产异常反馈 4.1.1 当生产发生异常或有出现异常的趋势时,生产部发现人员和现场管理人员(如班组长)应即时给予分析,并主动积极寻求解决方法,包括与相关人员联系,如能及时解决则不在本流程规定内。

第5章中断系统课后习题答案

第5章中断系统 1)作业题 1.8051微控制器中,有几个中断源?几个中断优先级?中断优先级是如何控制的?在出 现同级中断申请时,CPU按什么顺序响应(按由高级到低级的顺序写出各个中断源)? 各个中断源的入口地址是多少? 答:8051微控制器中有五个中断源,两个中断优先级。通过IP进行优先级控制。IP为中断优先级寄存器,物理地址为B8H,其中的后五位PS PT1 PX1 PT0 PX0分别控制串行口、定时器/计数器1、外部中断1、定时器/计数器0、外部中断0的优先级。在出现同级中断申请时,CPU按如下顺序响应各个中断源的请求:INT0、T0、INT1、T1、串行口,各个中断源的入口地址分别是0003H、000BH、0013H、001BH、0023H。 2.8051微控制器中,各中断标志是如何产生的,又如何清0的? 答:每个中断源请求中断时会在SFR的某些寄存器中产生响应的标志位,表示该中断源请求了中断。INT0、INT1、T0和T1的中断标志存放在TCON(定时器/计数器控制寄存器)中,占4位;串行口的中断标志存放在SCON(串行口控制寄存器)中,占2位。 TF0:T0溢出标志,溢出时由硬件置1,并且请求中断,CPU响应后,由硬件自动将TF0清0;不用中断方式时,要用软件清0。 TF1:T1溢出标志,溢出时由硬件置1,并且请求中断,CPU响应后,由硬件自动将TF1清0;不用中断方式时,要用软件清0。 IE0:INT0中断标志,发生INT0中断时,硬件置IE0为1,并向CPU请求中断。 IE1:INT1中断标志,发生INT1中断时,硬件置IE1为1,并向CPU请求中断。SCON:串行口控制寄存器。 TI:串行口发送中断标志,发送完一帧数据时由硬件置位,并请求中断。 RI:串行口接受中断标志,接收到一帧数据时,由硬件置位,并且请求中断。 TI、RI标志,必须用软件清0。 3.简述8051微控制器中中断响应的过程。 答:单片机响应中断的条件:中断源有请求(响应的中断标志位置1),CPU允许所有中断(CPU中断允许位EA=1),中断允许寄存器IE中,相应中断源允许位置1;没有同级或者高级中断正在服务,现行指令已经执行完毕,若执行指令为RETI或者读/写IE或者IP指令时则该指令的下一条指令也执行完毕。 中断响应的过程: 1)CPU在每个机器周期的S5P2检测中断源。在下一个机器周期的S6按照优先次序查询各个中断标志。若查询到有中断标志为1时,按照优先级别进行处理,即响应中断;2)置相应的“优先级状态”触发器为1,即指出CPU当前正在处理的中断优先级,以阻断同级或者低级中断请求; 3)自动保护断点,即将现行PC内容(即断点地址)压入堆栈,并且根据中断源把相应的

驱动-异常处理结构、中断处理结构

一,Linux 异常处理体系结构框架: 1,按键按下时。 强制的跳到异常向量处执行(中断是异常的一种)。 2,CPU 发生中断。 3,“入口函数”是一条跳转指令。跳到某个函数:(作用) 将2440 作为单片机使用时:裸机程序时 ②,执行中断处理函数。 ③,恢复被中断的现场。 ①,保存被中断处的现场(各种寄存器的值)。 LINUX 中处理中断的过程: 1,写程序时先设置异常入口: 发生“中断”时,就跳到0x18 地址处,跳转到“HandleIRQ”是执行下面的指令: 中断处理完后,要返回去继续执行之前被中断的那个程序。 保存寄存器就是保存中断前那个程序的所用到的寄存器。 然后是处理中断,最后是恢复。 linux 中: 异常向量在哪里: LINUX 异常处理结构、中断处理结构: 2012年2月23日 11:03

①,LINUX的异常向量在哪里: ARM架构的CPU的异常向量基址可以是 0x0000 0000,也可以是 0xffff0000,LINUX内核 使用后者,只需要在某个寄存器里设置下,就可以将异常基址定位到这里来。这个地址并不代表实际的内存,是虚拟地址。当建立了虚拟地址与物理地址间的映射后,得将那些异常向量,即相当于把那些跳转指令(如:HandleSWI 等)复制拷贝到这个 0xffff0000这个地址处去。(“那些跳转指令”是指head.S中那些跳转)。 这个过程是在trap_init这个函数里做。 trap_init函数将异常向量复制到0xffff0000处,部分代码如下: 如上: 将 __vectors_start, __vectors_end -__vectors_start 这段代码拷贝到 vectors来。

S3C2410中文手册第7章_时钟及电源管理模块

第七章时钟及电源管理模块 时钟电源管理模块包含了3部分:Clock控制、USB控制、POWER控制. 时钟控制逻辑单元能够产生s3c2440需要的时钟信号,包括CPU使用的主频FCLK,AHB总线设备使用的HCLK,以及APB总线设备使用的PCLK.2440内部有2个PLL(锁相环):一个对应FCLK、HCLK、PCLK,另外一个对应的是USB使用(48MHz)。时钟控制逻辑单元可以在不使用PLL情况下降低时钟CLOCK的频率,并且可以通过软件来驱使时钟和各个模块的连接/断开,以减少电源消耗。 对于电源控制逻辑单元,2440有许多钟电源管理方案来针对所给的任务保持最优的电源消耗。S3c2440中的电源管理模块对应4种模式:NORMAL模式、SLOW模式,IDLE模式,SLEEP 模式。 NORMAL模式:这个模块给CPU时钟以及2440相应的外围设备提供时钟。这个模式下,当所有的外围设备都被打开,电源消耗被最大化。它允许用户通过软件来控制外部设备的操作。例如,如果一个定时器不需要时,那么用户可以通过CLKCON寄存器来关闭时钟和定时器的连接,来降低电源消耗。 SLOW模式:NON-PLL模式,不同于Normal模式,这个模式使用的一个外部时钟(XTlpll 或EXTCLK)来直接作为2440的主频FCLK,而没有使用PLL。在这个模式下,电源的消耗仅依赖于外部时钟频率,电源同PLL有关的消耗可以被排除。 IDLE模式:这个模式下CPU的时钟FCLK被断开,而还继续提供其他外围设备的时钟。因此空闲模式导致减少了CPU核相应的电源消耗。任何中断请求都能够将CPU唤醒。 Sleep模式:这个模式断开了内部电源。因此在这个模式下CPU&内部的逻辑单元都没有电源消耗,除了一个wake-up逻辑单元。激活sleep模式需要2个独立的电源。一个给wake-up逻辑模块提供电源,另外一个给内部逻辑包括CPU提供电源,并且其是对于power on/off可控的。在Sleep模式,提供给内部逻辑&CPU的电源模块将被关闭,而从Sleep 模式唤醒可以通过EINT[15:0]&RTC中断来引发。 7.1功能描述 7.1.1时钟结构 如图7-1所示时钟结构模块图。主时钟源来自外部晶振(XTIPLL)或者是外部时钟(EXTCLK).时钟生成器包含了一个振荡器(振荡放大器),其连接外部晶振,并且还有2个PLL,可以产生满足s3c2440所需的高频时钟。

STM32中断优先级彻底讲解

STM32中断优先级彻底讲解 一:综述 STM32 目前支持的中断共为 84 个(16 个内核+68 个外部), 16 级可编程中断优先级 的设置(仅使用中断优先级设置 8bit 中的高 4 位)和16个抢占优先级(因为抢占优先级最多可以有四位数)。 二:优先级判断 STM32(Cortex-M3)中有两个优先级的概念——抢占式优先级和响应优先级,有人把响应优先级称作'亚优先级'或'副优先级',每个中断源都需要被指定这两种优先级。 具有高抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说高抢占式优先级的中断可以嵌套低抢占式优先级的中断。 当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当一个中断到来后,如果正在处理另一个中断,这个后到来的中断就要等到前一个中断处理完之后才能被处理。如果这两个中断同时到达,则中断控制器根据他们的响应优先级高低来决定先处理哪一个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序

决定先处理哪一个。 三:优先级分组 既然每个中断源都需要被指定这两种优先级,就需要有相应的寄存器位记录每个中断的优先级;在Cortex-M3中定义了8个比特位用于设置中断源的优先级,这8个比特位在NVIC应用中断与复位控制寄丛器(AIRCR)的中断优先级分组域中,可以有8种分配方式,如下: 所有8位用于指定响应优先级 最高1位用于指定抢占式优先级,最低7位用于指定响应优先级 最高2位用于指定抢占式优先级,最低6位用于指定响应优先级 最高3位用于指定抢占式优先级,最低5位用于指定响应优先级 最高4位用于指定抢占式优先级,最低4位用于指定响应优先级 最高5位用于指定抢占式优先级,最低3位用于指定响应优先级 最高6位用于指定抢占式优先级,最低2位用于指定响应优先级 最高7位用于指定抢占式优先级,最低1位用于指定响应优先级 这就是优先级分组的概念。 Cortex-M3允许具有较少中断源时使用较少的寄存器位指定中断源的优先级,因此STM32把指定中断优先级的寄存器位减少到4位(AIRCR高四位),这4个寄存器位的分组方式如下: