基于FPGA数字秒表设计

数字秒表设计

一、实验目的

1、理解计时器的原理与V erilog/VHDL的编程方法;

2、掌握多模块设计及层次设计的方法。

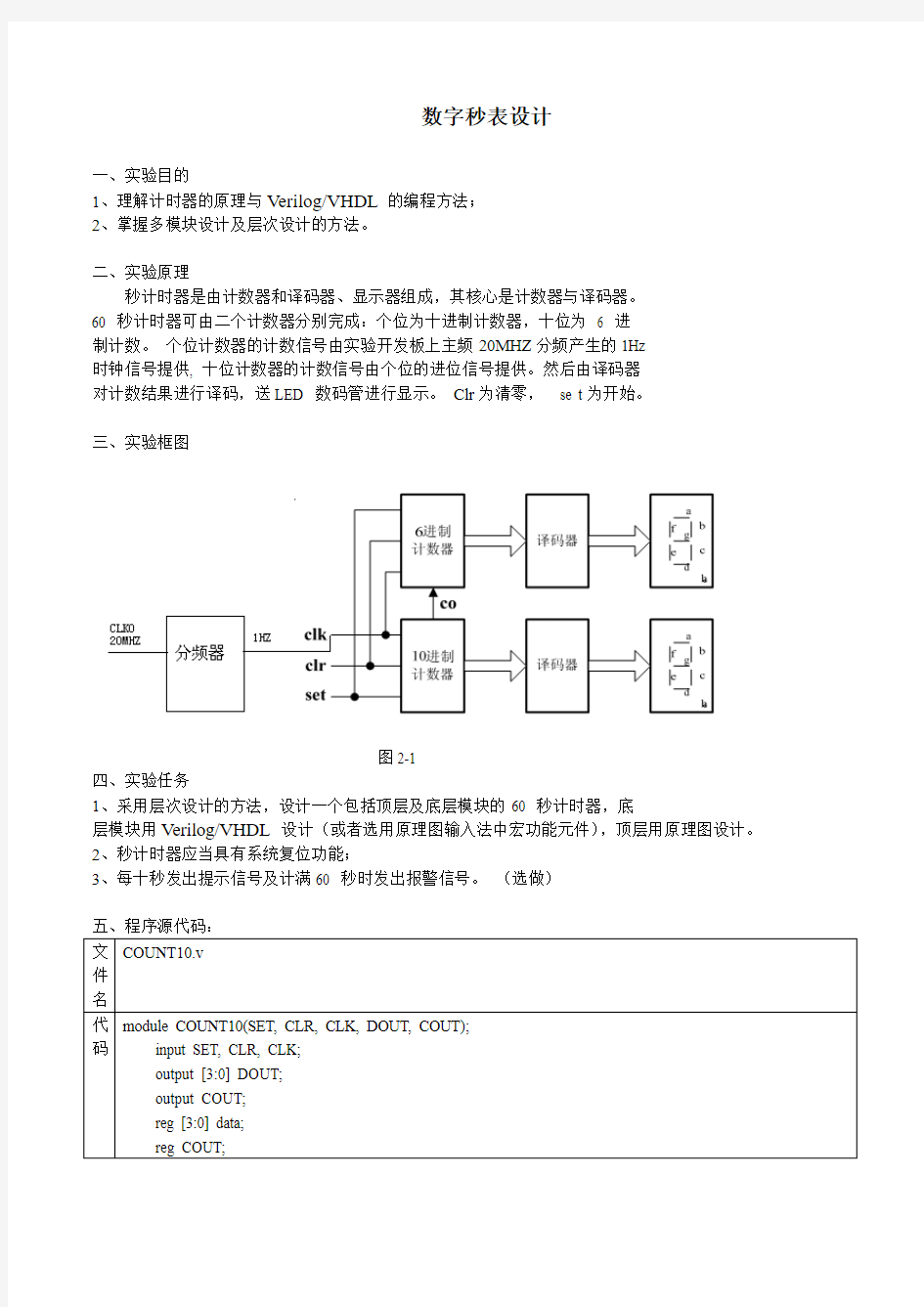

二、实验原理

秒计时器是由计数器和译码器、显示器组成,其核心是计数器与译码器。

60 秒计时器可由二个计数器分别完成:个位为十进制计数器,十位为6 进

制计数。个位计数器的计数信号由实验开发板上主频20MHZ分频产生的1Hz

时钟信号提供, 十位计数器的计数信号由个位的进位信号提供。然后由译码器

对计数结果进行译码,送LED 数码管进行显示。Clr为清零,se t为开始。

三、实验框图

图2-1

四、实验任务

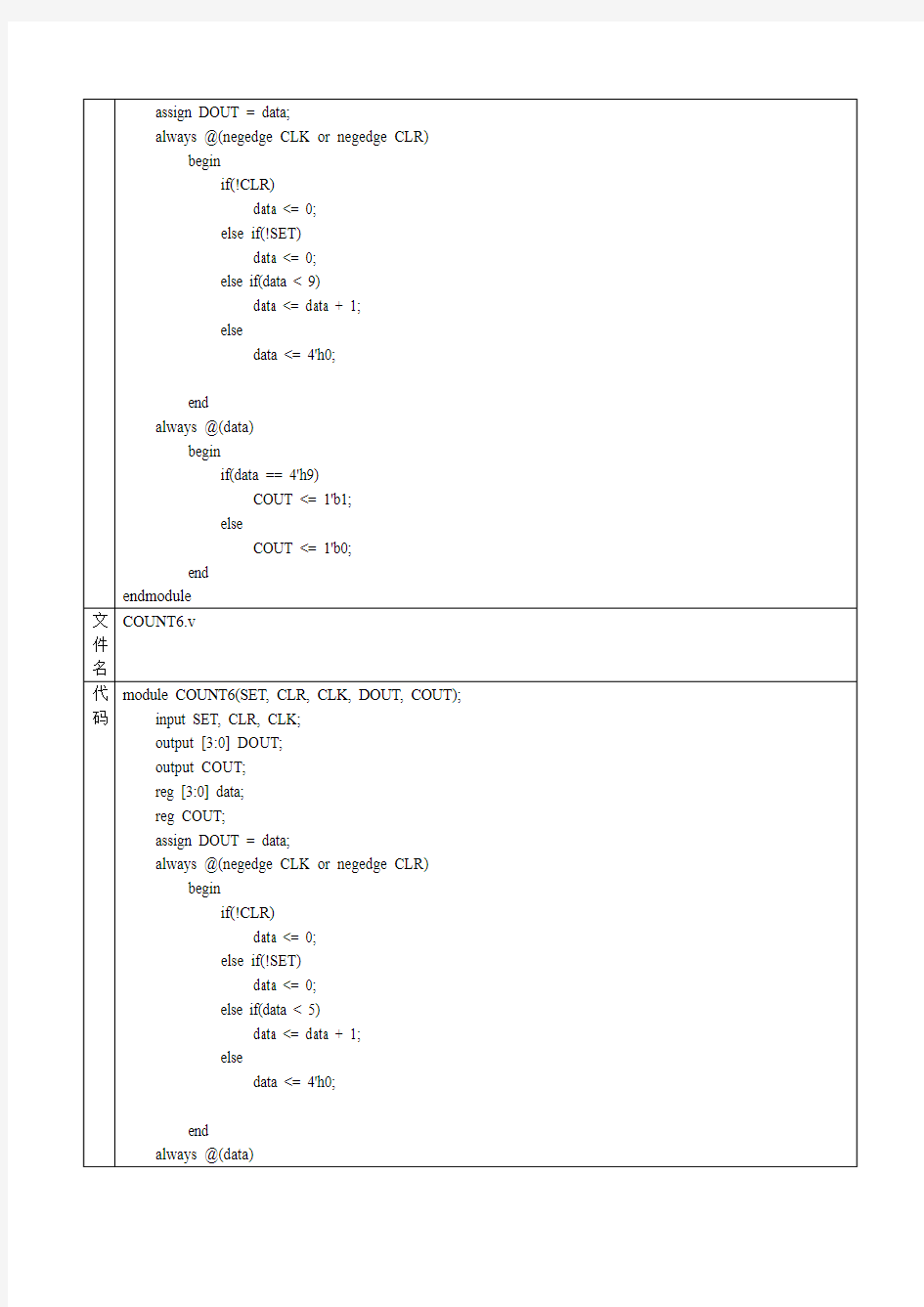

1、采用层次设计的方法,设计一个包括顶层及底层模块的60 秒计时器,底

层模块用Verilog/VHDL设计(或者选用原理图输入法中宏功能元件),顶层用原理图设计。

2、秒计时器应当具有系统复位功能;

3、每十秒发出提示信号及计满60 秒时发出报警信号。(选做)

名

原

理

图

五、实验步骤

1.创建工程

2.选择目标器件

3.编写verilog hdl 程序

4.编译

5.生成符号文件

6.创建编辑原理图

7.设置顶层文件

8.编译

9.创建编辑波形图文件

10.使用波形图仿真

11.锁定管脚 12.编译 13.下载至芯片

六、实验结果

1.编译结果

名

仿

真

结

果

名

仿

真

结

果

文COUNT60.v (为了简便将分频器设置2分频的)

相关主题