4输入双与非门74LS20

TL F 635554LS20 DM54LS20 DM74LS20 Dual 4-Input NAND Gates

June1989

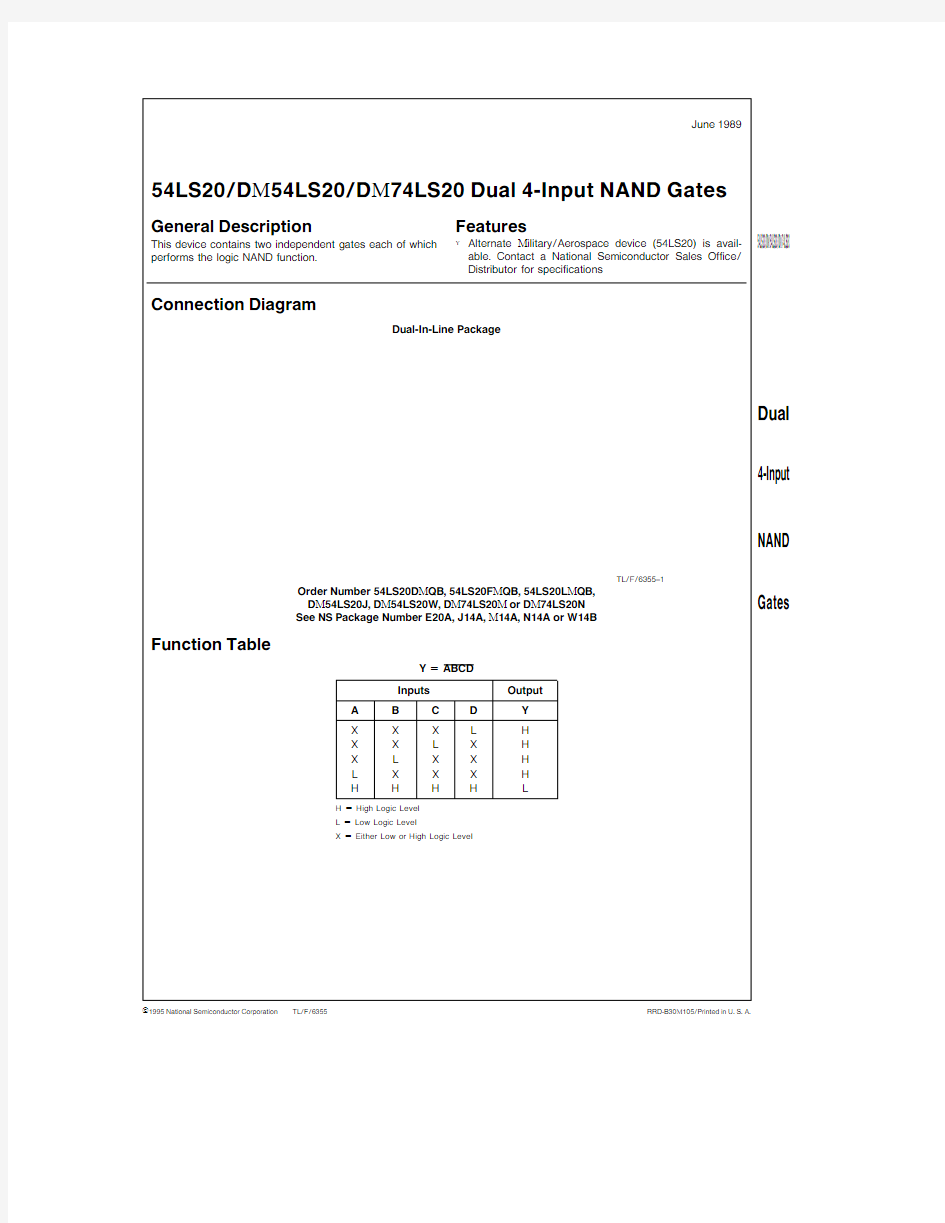

54LS20 DM54LS20 DM74LS20Dual4-Input NAND Gates General Description

This device contains two independent gates each of which

performs the logic NAND function

Features

Y Alternate Military Aerospace device(54LS20)is avail-

able Contact a National Semiconductor Sales Office

Distributor for specifications

Connection Diagram

Dual-In-Line Package

TL F 6355–1

Order Number54LS20DMQB 54LS20FMQB 54LS20LMQB

DM54LS20J DM54LS20W DM74LS20M or DM74LS20N

See NS Package Number E20A J14A M14A N14A or W14B

Function Table

Y e ABCD

Inputs Output

A B C D Y

X X X L H

X X L X H

X L X X H

L X X X H

H H H H L

H e High Logic Level

L e Low Logic Level

X e Either Low or High Logic Level

C1995National Semiconductor Corporation RRD-B30M105 Printed in U S A

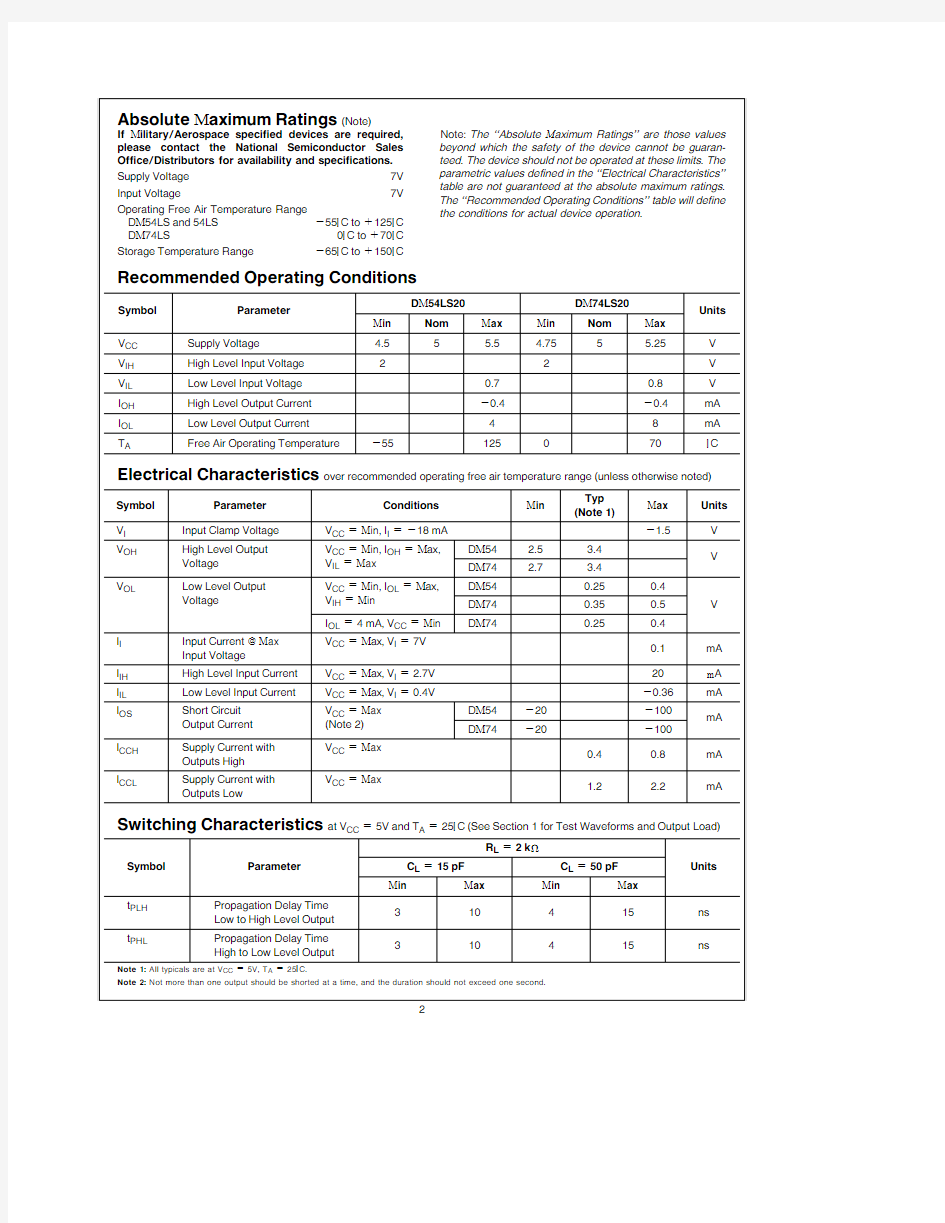

Absolute Maximum Ratings(Note)

If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage7V Input Voltage7V Operating Free Air Temperature Range

DM54LS and54LS b55 C to a125 C DM74LS0 C to a70 C Storage Temperature Range b65 C to a150 C Note The‘‘Absolute Maximum Ratings’’are those values beyond which the safety of the device cannot be guaran-teed The device should not be operated at these limits The parametric values defined in the‘‘Electrical Characteristics’’table are not guaranteed at the absolute maximum ratings The‘‘Recommended Operating Conditions’’table will define the conditions for actual device operation

Recommended Operating Conditions

Symbol Parameter

DM54LS20DM74LS20

Units Min Nom Max Min Nom Max

V CC Supply Voltage4 555 54 7555 25V V IH High Level Input Voltage22V V IL Low Level Input Voltage0 70 8V I OH High Level Output Current b0 4b0 4mA I OL Low Level Output Current48mA T A Free Air Operating Temperature b55125070 C Electrical Characteristics over recommended operating free air temperature range(unless otherwise noted)

Symbol Parameter Conditions Min

Typ

Max Units (Note1)

V I Input Clamp Voltage V CC e Min I I e b18mA b1 5V V OH High Level Output V CC e Min I OH e Max DM542 53 4

V Voltage V IL e Max DM742 73 4

V OL Low Level Output V CC e Min I OL e Max DM540 250 4 Voltage V IH e Min DM740 350 5V

I OL e4mA V CC e Min DM740 250 4

I I Input Current Max V CC e Max V I e7V

0 1mA

Input Voltage

I IH High Level Input Current V CC e Max V I e2 7V20m A I IL Low Level Input Current V CC e Max V I e0 4V b0 36mA

I OS Short Circuit V CC e Max DM54b20b100

mA Output Current(Note2)DM74b20b100

I CCH Supply Current with V CC e Max

0 40 8mA

Outputs High

I CCL Supply Current with V CC e Max

1 2

2 2mA

Outputs Low

Switching Characteristics at V CC e5V and T A e25 C(See Section1for Test Waveforms and Output Load)

R L e2k X

Symbol Parameter C L e15pF C L e50pF Units

Min Max Min Max

t PLH Propagation Delay Time

310415ns Low to High Level Output

t PHL Propagation Delay Time

310415ns High to Low Level Output

Note1 All typicals are at V CC e5V T A e25 C

Note2 Not more than one output should be shorted at a time and the duration should not exceed one second

2

3

Physical Dimensions inches(millimeters)

Ceramic Leadless Chip Carrier Package(E)

Order Number54LS20LMQB

NS Package Number E20A

14-Lead Ceramic Dual-In-Line Package(J)

Order Number54LS20DMQB or DM54LS20J

NS Package Number J14A

4

Physical Dimensions inches(millimeters)(Continued)

14-Lead Small Outline Molded Package(M)

Order Number DM74LS20M

NS Package Number M14A

14-Lead Molded Dual-In-Line Package(N)

Order Number DM74LS20N

NS Package Number N14A

5

54L S 20 D M 54L S 20 D M 74L S 20D u a l 4-I n p u t N A N D G a t e s

Physical Dimensions inches (millimeters)(Continued)

14-Lead Ceramic Flat Package (W)

Order Number 54LS20FMQB or DM54LS20W

NS Package Number W14B

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implant support device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectiveness

be reasonably expected to result in a significant injury to the user

National Semiconductor National Semiconductor National Semiconductor National Semiconductor Corporation

Europe

Hong Kong Ltd

Japan Ltd

1111West Bardin Road

Fax (a 49)0-180-5308586

13th Floor Straight Block Tel 81-043-299-2309

电路四输入与非门设计

课程设计任务书 学生姓名:专业班级:电子1003班 指导教师:封小钰工作单位:信息工程学院 题目: CMOS四输入与非门电路设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件。 (2)设计一个CMOS四输入与非门电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对CMOS四输入与非门电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6 提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

摘要........................................................................ I Abstract ................................................................... II 1 绪论 (1) 2 设计内容及要求 (2) 2.1 设计的目的及主要任务 (2) 2.2 设计思想 (2) 3软件介绍 (3) 3.1 OrCAD简介 (3) 3.2 L-Edit简介 (4) 4 COMS四输入与非门电路介绍 (5) 4.1 COMS四输入与非门电路组成 (5) 4.2 四输入与非门电路真值表 (6) 5 Cadence中四输入与非门电路的设计 (7) 5.1 四输入与非门电路原理图的绘制 (7) 5.2 四输入与非门电路的仿真 (8) 6 L-EDIT中四输入与非门电路版图的设计 (10) 6.1 版图设计的基本知识 (10) 6.2 基本MOS单元的绘制 (11) 6.3 COMS四输入与非门的版图设计 (13) 7课程设计总结 (14) 参考文献 (15)

双稳态电路图

作者:日期:

* 1 1. 1人工启动单稳 NE555为8脚时基集成电路, 各脚主要功能(集成块图在下面) 1 地 GND 2触发 3输出 4复位 应用十分广泛,可装如下几种电路: 1。 单稳类电路 作用:定延时,消抖动,分(倍)频,脉冲输出,速率检测等。 2。 双稳类电路 作用:比较器,锁存器,反相器,方波输出及整形等。 3。 无稳类电路 作用:方波输出,电源变换,音响报警,玩具,电控测量,定时等。 我们知道,555电路在应用和工作方式上一般可归纳为 3类。每类工作方式又有很多个 不同的电路。在实际应用中,除了单一品种的电路外,还可组合出很多不同电路,如: 多个单稳、多个双稳、单稳和无稳,双稳和无稳的组合等。这样一来,电路变的更加复 杂。为了便于我们分析和识别电路,更好的理解 555电路,这里我们这里按555电路的 结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。每个电路 除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的 用途。方便大家识别、分析555电路。下面将分别介绍这3类电路。 单稳类电路 单稳工作方式,它可分为3种。见图示 第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为 2个不同的 单元,并分别以1.1.1和1.1.2为代号。他们的输入端的形式,也就是电路的结构特点 是:“ RT-6.2- CT'和“ CT-6.2- RT'。 5控制电压 6门限(阈值) 7放电 8电源电压Vcc ---------- -------------------- Q IT VC 1 3 特点;KT-5 ^-CT,人 工启鲂f ^T )=0 >稳态r vn=i ?普稳直(td ) B 2〉公式! ra-1. 1ET*CT 37用逮:定时J 延时? 1-L.2人丁启动单穩 1)特点:CT-&.2-RT, A 工启动> TO- 1 J 稳态i vo=Or 暂穏态 t ?a > D E )企式:丁d=l. 1KT 札T 3 )用谨:定时「延时.

输入与非门电路版图设计

成绩评定表

课程设计任务书

目录 1 绪论 (1) 1.1设计背景 (1) 1.2设计目标 (1) 2 四输入与非门电路 (2) 2.1电路原理图 (2) 2.2四输入与非门电路仿真观察波形 (2) 2.3四输入与非门电路的版图绘制 (3) 2.4四输入与非门版图电路仿真观察波形 (4) 2.5LVS检查匹配 (5) 总结 (7) 参考文献 (8) 附录一:电路原理图网表 (9) 附录二:版图网表 (10)

1 绪论 1.1 设计背景 tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。 1.2设计目标 1.用tanner软件中的原理图编辑器S-Edit编辑四输入与非门电路原理图。 2.用tanner软件中的W-Edit对四输入与非门电路进行仿真,并观察波形。 3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。 4.用W-Edit对四输入与非门的版图电路进行仿真并观察波形。 5.用tanner软件中的layout-Edit对四输入与非门进行LVS检验观察原理图与版图的匹配程度。

双稳态电路

双稳态电路 一、工作原理 图一为双稳态电路,它是由两级反相器组成的正反馈电路,有两个稳定状态,或者是BG1 导通、BG2截止;或者是BG1截止、BG2导通,由于它具有记忆功能,所以广泛地用于计数电路、分频电路和控制电路中, 原理,图2(a)中,设触发器的初始状态为BG1导通,BG2截止,当触发脉冲方波从1端输入,经CpRp微分后,在A点产生正、负方向的尖脉冲,而只有正尖脉冲能通过二极管D1 作用于导通管BG1的基极是。ic1减小使BG1退出饱和并进入放大状态,于是它的集电极电位降低,经电阻分压器送到截止管BG2的基极,使BG2的基极电位下降,如果下降幅度足够时,BG2将由截止进入放大状态,因而产生下列正反馈过程(看下列反馈过程时,应注意:在图一的PNP电路中,晶体管的基极和集电极电位均为负值,所以uc1↓,表示BG1集电极电位降低,而uc1↑则表示BG1集电极电位升高,当BG1基极电位降低时,则ic1↑,反之当BG1基极电位升高时,ic1↓ ic1越来越小,ic2越来越大,最后到达BG1截止、BG2导通;接差触发脉冲方波从2端输入,并在t=t2时,有正尖脉冲作用于导通管BG2的基极,又经过正反馈过程,使BG1导通,BG2截止。以后,在1、2端的触发脉冲的轮流作用下,双稳电路的状态也作用相应的翻转,如图一(b)所示。 图一、双稳态电路 由上述过程可见:(1)双稳态电路的尖顶触发脉冲极性由晶体管的管型决定:PNP管要求正极性脉冲触发,而NPN管却要求负极性脉冲触发。(2)每触发一次,电路翻转一次,因此,从翻转次数的多少,就可以计算输入脉冲的个数,这就是双稳态电路能够计算的原理。双稳态电路的触发电路形式有:单边触发、基极触发、集电极触发和控制触发等。 图二给出几种实用的双稳态电路。电路(a)中D3、D4为限幅二极管,使输出幅度限制在-6伏左右;电路(b)中的D5、D6是削去负尖脉冲;电路(C)中的ui1、ui2为单触发,ui 为输入触发表一是上述电路的技术指标。

常用芯片引脚图

.v .. .. 常用芯片引脚 74LS00数据手册 74LS01数据手册 74LS02数据手册 74LS03数据手册 74LS04数据手册 74LS05数据手册 74LS06数据手册 74LS07数据手册 74LS08数据手册 74LS09数据手册 74LS10数据手册 74LS11数据手册

第2页 共8页 74LS12数据手册 74LS13数据手册 74LS14数据手册 74LS15数据手册 74LS16数据手册 74LS17数据手册 74LS19数据手册 74LS20数据手册 74LS21数据手册 74LS22数据手册 74LS23数据手册 74LS26数据手册 74LS27数据手册 74LS28数据手册

.v .. .. 74LS30数据手册 74LS32数据手册 74LS33数据手册 74LS37数据手册 74LS38数据手册 74LS40数据手册 74LS42数据手册 [1].要求0—15时,灭灯输入(BI )必须开路或保持高电平,如果不要灭十进制数零,则动态灭灯输入(RBI )必须开路或为高电平。 [2].将一低电平直接输入BI 端,则不管其他输入为何电平,所有的输出端均输出为低电平。 [3].当动态灭灯输入(RBI )和A,B,C,D 输入为低电平而试灯输入为高电平时,所有输出端都为低电平并且动态灭灯输入(RBO )处于第电平(响应条件)。 [4].]当灭灯输入/动态灭灯输出(BI/RBO )开朗路或保持高电平而试 灯输入为低电平时,所有各段输出均为高电平。 表中1=高电平,0=低电平。BI/RBO 是线与逻辑,作灭灯输入(BI )或动态灭灯(RBO )之用,或者兼为二者之用。

集成逻辑门电路及应用与门非门与非门

集成逻辑门电路及应用(与门,非门,与非门) 集成逻辑门电路的种类繁多,有反相器、与门和与非门、或门和或非门、异或门等,以下简单介绍几种常用的门电路及应 用电路。 1.集成逻辑门电路: (1)常用逻辑门电路图形符号 常用逻辑门电路图形符号见表1。 表1 常用逻辑门电路图形符号 (2)反相器与缓冲器 反相器是非门电路,74LS04是通用型六反相器,与该器件的逻辑功能且引脚排列兼容的器件有74HC04,CD4069等。74LS05也是六反相器,该器件的逻辑功能和引脚排列与74LS04相同,不同的是74LS05是集电极开路输出(0C门),在实际使用时,必须在输出端至电源正端接上拉电阻。 缓冲器的输出与输人信号同相位,它用于改变输人输出电平及提高电路的驱动能力,74LS07是集电极开路输出同相输出驱动器,该器件的输出高电压达30V,灌电流达40mA,与之兼容的器件有74HC07,74HCT07 等。 74LS04,CD4069引脚排列图如图1所示。

图1 74LS04,CD4069引脚排列图 (3)与门和门与非 与门和与非门种类繁多,常见的与门有2输入、3输入、4输入与门等;与非门有2输入、3输入、4输入、8输入等,常见的74LS系列(74HC系列)与门和与非门引脚排列图如图2所示。 图2 常见的74LS系列(74HC系列)与门和与非门引脚排列图 74LS08是四2输人与门,74LS00和CD4011是四2输入与非门,74LS20是双4输人与非门。 2.集成门电路的应用 (1)定时灯光提醒器 电路如图3所示,由六非门CD4069(仅用到其中两个非门,分别用IC-1和IC-2表示)和电阻、电容、电源等组成,此电路可以在1~25分钟内预定提醒时间,使用时,利用时间标尺预定时间,打开电源开关,定时器绿灯亮,表示开始计时,到了预定的时间,绿灯灭,红灯亮。

双稳态电路的工作原理)

双稳态电路的工作原理 双稳态电路是由什么组成的?他的工作原理是什么? 一、工作原理 图一为双稳态电路,它是由两级反相器组成的正反馈电路,有两个稳定状态,或者是BG1导通、BG2截止;或者是BG1截止、BG2导通,由于它具有记忆功能,所以广泛地用于计数电路、分频电路和控制电路中,原理,图2(a)中,设触发器的初始状态为BG1导通,BG2截止,当触发脉冲方波从1端输入,经CpRp 微分后,在A点产生正、负方向的尖脉冲,而只有正尖脉冲能通过二极管D1作用于导通管BG1的基极是。ic1减小使BG1退出饱和并进入放大状态,于是它的集电极电位降低,经电阻分压器送到截止管BG2的基极,使BG2的基极电位下降,如果下降幅度足够时,BG2将由截止进入放大状态,因而产生下列正反馈过程(看下列反馈过程时,应注意:在图一的PNP电路中,晶体管的基极和集电极电位均为负值,所以uc1↓,表示BG1集电极电位降低,而uc1↑则表示BG1集电极电位升高,当BG1基极电位降低时,则ic1↑,反之当BG1基极电位升高时,ic1↓ ic1越来越小,ic2越来越大,最后到达BG1截止、BG2导通;接差触发脉冲方波从2端输入,并在t=t2时,有正尖脉冲作用于导通管BG2的基极,又经过正反馈过程,使BG1导通,BG2截止。以后,在1、2端的触发脉冲的轮流作用下,双稳电路的状态也作用相应的翻转,如图一(b)所示。 图一、双稳态电路 由上述过程可见:(1)双稳态电路的尖顶触发脉冲极性由晶体管的管型决定:PNP管要求正极性脉冲触发,而NPN管却要求负极性脉冲触发。(2)每触发一次,电路翻转一次,因此,从翻转次数的多少,就可以计算输入脉冲的个数,这就是双稳态电路能够计算的原理。 双稳态电路的触发电路形式有:单边触发、基极触发、集电极触发和控制触发等。 图二给出几种实用的双稳态电路。电路(a)中D3、D4为限幅二极管,使输出幅度限制在-6伏左右;电路(b)中的D5、D6是削去负尖脉冲;电路(C)中的ui1、ui2为单触发,ui为输入触发表一是上述电路的技术指标。 图二、几种实用的双稳态电路 表一几种双稳态触发器的技术指标 图二(a)(b)(c)(d) 管型二极管2AP32AP152AK1C2AK17 三极管3AX31B3AG403AK203DK3B 信号电平“0”(无信号)(V)000+6 “1”(有信号)(V)-6-6-90 工作频率(KHz)1060010008000 抗干扰电压(V)≥1≥1.5≥20.8-1 触发灵敏度(V)≤4≤4.8≤72.5 输出端的吸收能力(mA)≤4≤6.7≤210 输出端的发射能力(mA)≤44≤12≤127 输出脉冲的上升时间(μs)2≤0.30≤0.1≤0.1 输出脉冲的下降时间(μs)2≤0.36≤0.15≤0.1 对β值的要求>5050-8060-90>50 元件参数的允许化△β<10,±5%△β<10,±5%△β<10,±5%△β<10,±5%

与非门

教学要求: 熟练掌握最简单的与、或、非门电路;掌握TTL 门电路、CMOS 门电路特点和逻辑功能(输入输出关系);掌握TTL 门电路、CMOS 门电路的电气特性;理解TTL 门电路、CMOS 门电路在应用上的区别。了解特殊的门电路,如OC 门,三态门,CMOS 传输门。 教学重点: TTL 门电路的外部特性,逻辑功能、电气特性。CMOS 门电路的外部特性,逻辑功能、电气特性。 2. 1 概述 门电路——用以实现各种基本逻辑关系的电子电路 正逻辑——用1 表示高电平、用0 表示低电平 负逻辑——用0 表示高电平、用1 表示低电子的情况。 2.2 分立元件门电路 2.2.1 二极管的开关特性 图2.2.1二极管静态开关电路及其等效电路 (a)电路图(b) 输入高电平时的等效电路(c)输入低电平时的等效电路

二、动态开关特性在高速开关电路中,需要了解二极管导通与截止间的快速转换过程。 图2.2.2二极管动态开关特性 (a)电路图(b)输入脉冲电压波形(c)实际电流波形 当输入电压U I 由正值U F 跃变为负值U R 的瞬间,V D 并不能立刻截止,而是在外加反向电压UR 作用下,产生了很大的反向电流I R ,这时i D =I R ≈- U R /R ,经一段时间 t rr后二极管V D 才进人截止状态,如图3. 2. 3 (c) 所示。通常将t rr称作反向恢 复时间。产生t rr 的主要原因是由于二极管在正向导通时,P 区的多数载流子空穴大 量流入N 区,N 区的多数载流子电子大量流入P 区,在P 区和N 区中分别存储了 大量的电子和空穴,统称为存储电荷。当U I 由U F跃变为负值U R 时,上述存储 电荷不会立刻消失,在反向电压的作用下形成了较大的反向电流I R ,随着存储电荷 的不断消散,反向电流也随之减少,最终二极管V D 转为截止。当二极管V D 由截 止转为导通时,在P 区和N 区中积累电荷所需的时间远比t rr 小得多,故可以忽略。 2. 2. 2 三极管的开关特性 一、静态开关特性及开关等效电路

数字电路组合逻辑电路设计实验报告

数字电路组合逻辑电路设 计实验报告 The Standardization Office was revised on the afternoon of December 13, 2020

实验三组合逻辑电路设计(含门电路功能测试)

一、实验目的 1.掌握常用门电路的逻辑功能 2.掌握小规模集成电路设计组合逻辑电路的方法 3.掌握组合逻辑电路的功能测试方法 二、实验设备与器材 Multisim 、74LS00 四输入2与非门、示波器、导线 三、实验原理 TTL集成逻辑电路种类繁多,使用时应对选用的器件做简单逻辑功能检查,保证实验的顺利进行。 测试门电路逻辑功能有静态测试和动态测试两种方法。静态测试时,门电路输入端加固定的高(H)、低电平,用示波器、万用表、或发光二极管(LED)测

出门电路的输出响应。动态测试时,门电路的输入端加脉冲信号,用示波器观测输入波形与输出波形的同步关系。 下面以74LS00为例,简述集成逻辑门功能测试的方法。74LS00为四输入2与非门,电路图如3-1所示。74LS00是将四个二输入与非门封装在一个集成电路芯片中,共有14条外引线。使用时必须保证在第14脚上加+5V电压,第7脚与底线接好。 整个测试过程包括静态、动态和主要参数测试三部分。 表3-1 74LS00与非门真值表 1.门电路的静态逻辑功能测试 静态逻辑功能测试用来检查门电路的真值表,确认门电路的逻辑功能正确与否。实验时,可将74LS00中的一个与非门的输入端A、B分别作为输入逻辑变量,加高、低电平,观测输出电平是否符合74LS00的真值表(表3-1)描述功能。

双稳态电路图简介

NE555为8脚时基集成电路, 各脚主要功能(集成块图在下面) 1地GND 2触发 3输出 4复位5控制电压 6门限(阈值)7放电 8电源电压Vcc 应用十分广泛,可装如下几种电路: 1。单稳类电路 作用:定延时,消抖动,分(倍)频,脉冲输出,速率检测等。 2。双稳类电路 作用:比较器,锁存器,反相器,方波输出及整形等。 3。无稳类电路 作用:方波输出,电源变换,音响报警,玩具,电控测量,定时等。 我们知道,555电路在应用和工作方式上一般可归纳为3类。每类工作方式又有很多个不同的电路。在实际应用中,除了单一品种的电路外,还可组合出很多不同电路,如:多个单稳、多个双稳、单稳和无稳,双稳和无稳的组合等。这样一来,电路变的更加复杂。为了便于我们分析和识别电路,更好的理解555电路,这里我们这里按555电路的结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。每个电路除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的用途。方便大家识别、分析555电路。下面将分别介绍这3类电路。

单稳类电路 单稳工作方式,它可分为3种。见图示。 第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1 和1.1.2为代号。他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。 第2种(图2)是脉冲启动型单稳,也可以分为2个不同的单元。他们的输入特点都是“RT-7.6-CT”,都是从2端输入。1.2.1电路的2端不带任何元件,具有最简单的形式;1.2.2电路则带有一个RC微分电路。

74LS系列芯片引脚图资料大全

74系列芯片引脚图资料大全 作者:佚名来源:本站原创点击数:57276 更新时间:2007年07月26日【字体:大中小】 为了方便大家我收集了下列74系列芯片的引脚图资料,如还有需要请上电子论坛https://www.360docs.net/doc/979228443.html,/b bs/ 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND

四输入或非门课程设计

四输入或非门专项实践任务书学生姓名:专业班级: 指导教师:工作单位: 题目: 四输入或非门的设计 初始条件: 计算机、ORCAD软件,L-EDIT软件 要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写 等具体要求) 1、集成电路专项实践工作量:1周 2、技术要求: (1)学习ORCAD软件,L-EDIT软件。 (2)设计一个四输入或非门电路。 (3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。 学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT软件绘制其版图,完成集成电路专项实践报告的撰写。 提交集成电路专项实践报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日

目录 摘要 ............................................................................................................................................................ Abstract ...................................................................................................................................................... I 1 绪论 0 2 设计内容及要求 (1) 设计的目的及主要任务 (1) 设计思路 (1) 3软件介绍 (1) OrCAD简介 (1) L-Edit简介 (3) 4四输入或非门 (4) 四输入或非门电路结构 (4) 四输入或非门电路仿真 (5) 四输入或非门的版图绘制 (6) NMOS管 (6) PMOS管 (7) 输出端口 (7) 四输入或非门 (7) 总结 (9) 参考文献 (11)

分立元件组成的双稳态电路

图是采用分立元件构成的双稳态电路,从电路中可以看出,一只三极管的集电极与另一只三极管的基极耦合,Uol、Uo2是这一双稳态电路的两个输出信号。两管的基极通过R3和R5接触发信号U。通常,这种电路中的元器件参数对称,即VT1、VT2性能参数一致,R1=R6,R2=R4,R3=R5。 (1)当没有输入触发信号时,接通直流工作电压VcC,虽然电路中元器件参数对称,但不可能是绝对一样的,设接通电源后VT1的导通程度大于VT2,这样VT1管的基极和集电极电流增大较快(VcC经Rl加到VT1集电极,R6和R4为VT1提供基极电流),使VT1的集电极电压下降较快,通过R2使VT2基极电压下降,其集电极电压上升,再经R4使VT1的基极电压进一步上升,其基极电流更大,显然这是正反馈过程,所以很快使VT1处于饱和状态。 由于VT1饱和后集电极电压(饱和压降)只有0.2V,这一电压经R2加到VT2的基极,使VT2处于截止状态。此时,VT1集电极输出电压Uo1为低电平;VT2集电极输出电压U02为高电平。只要外电路中没有出现有效的触发信号,这一电路将始终保持VT1饱和、VT2截止的稳定状态。 如若在电源接通之后设VT2导通电流大于VT1,则通过电路的正反馈过程,会使VT1处于截止、VT2处于饱和的稳定状态,此时Uol为高电平,U。。低电平。只要外电路中没有出现有效的触发信号,这一电路始终保持这一稳定状态。 (2)当有触发信号作用于电路时,电路的状态将发生变化。电路中,Cl和R7构成微分电路,输入脉冲信号U.经过微分后,获得正、负尖顶脉冲,由于二极管VD1的单向导电性,只能让负尖顶脉冲通过,将正尖顶脉冲去掉。 设初始时双稳态电路处于VT1饱和、VT2截止的稳态。触发电路送来的负尖顶脉冲通过R3和R5,同时加到VT1和VT2基极。由于VT2截止,所以负脉冲加到VT2基极后使基极电压更低,这对VT2无作用。 负脉冲加到饱和管VT1的基极后,使VT1的基极电压下降,其基极电流和集电极电流减小,集电极电压升高,通过R2耦合使VT2的基极电压升高,其集电极电压下降,又通过R4耦合使VT1的基极电压进一步下降,这一正反馈过程,很快使VT1从饱和转为截止,而VT2

74系列芯片引脚图

74系列芯片引脚图、功能、名称、资料大全(含74LS、74HC等),特别推荐为了方便大家,我收集了下列74系列芯片的引脚图资料。 说明:本资料分3部分:(一)、TXT文档,(二)、图片,(三)、功能、名称、资料。 (一)、TXT文档 反相器驱动器LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器LS86 译码器LS138 LS139 寄存器LS74 LS175 LS373

反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门 74LS04 ┌┴—┴—┴—┴—┴—┴—┴┐六非门(OC门) 74LS05 _ │14 13 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴—┴—┴—┴—┴—┴—┴┐ │14 13 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘

1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴—┴—┴—┴—┴—┴—┴┐ _ │14 13 12 11 10 9 8│ Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬—┬—┬—┬—┬—┬—┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴—┴—┴—┴—┴—┴—┴—┴—┴—┴┐ 8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│ DIR=1 A=>B │ 1 2 3 4 5 6 7 8 9 10│ DIR=0 B=>A └┬—┬—┬—┬—┬—┬—┬—┬—┬—┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND

(Multisim数电仿真)与非门逻辑功能测试及组成其它门电路

实验3.2 与非门逻辑功能测试及组成其它门电路 一、实验目的: 1.熟悉THD-1型(或Dais-2B型)数电实验箱的使用方法。 2. 了解基本门电路逻辑功能测试方法。 3.学会用与非门组成其它逻辑门的方法。 二、实验准备: 1. 集成逻辑门有许多种,如:与门、或门、非门、与非门、或非门、与或非门、异或门、OC门、TS门等等。但其中与非门用途最广,用与非门可以组成其它许多逻辑门。 要实现其它逻辑门的功能,只要将该门的逻辑函数表达式化成与非-与非表达式,然后用多个与非门连接起来就可以达到目的。例如,要实现或门Y=A+B, A ,可用三个与非门连根据摩根定律,或门的逻辑函数表达式可以写成:Y=B 接实现。 集成逻辑门还可以组成许多应用电路,比如利用与非门组成时钟脉冲源电路就是其中一例,它电路简单、频率范围宽、频率稳定。 2. 集成电路与非门简介: 74LS00是“TTL系列”中的与非门,CD4011是“CMOS系列”中的与非门。它们都是四-2输入与非门电路,即在一块集成电路内含有四个独立的与非门。每个与非门有2个输入端。74LS00芯片逻辑框图、符号及引脚排列如图

与非门的逻辑功能是:当输入端中有一个或一个以上是低电平时,输出端为高电平;只有当输入端全部为高电平时,输出才是低电平(即有“0”得“1”,全 “1”得“0”)。其逻辑函数表达式为:B =。 Y? A TTL电路对电源电压要求比较严,电源电压Vcc只允许在+5V±10%的范围内工作,超过5.5V将损坏器件;低于4.5V器件的逻辑功能将不正常。 CMOS集成电路是将N沟道MOS晶体管和P沟道MOS晶体管同时用于一个集成电路中,成为组合两种沟道MOS管性能的更优良的集成电路。CMOS电路的主要优点是: (1). 功耗低,其静态工作电流在10-9A数量级,是目前所有数字集成电路中最低的,而TTL器件的功耗则大得多。 (2).高输入阻抗,通常大于1010Ω,远高于TTL器件的输入阻抗。 (3). 接近理想的传输特性,输出高电平可达电源电压的99.9%以上,低电平可达电源电压的0.1%以下,因此输出逻辑电平的摆幅很大,噪声容限很高。 (4).电源电压范围广,可在+5V~+18V范围内正常运行。 3.集成电路芯片简介: 数字电路实验中所用到的集成电路芯片都是双列直插式的,其引脚排列规则如图3.2.3所示。识别方法是:正对集成电路型号(如74LS00)或看标记(左边的缺口或小圆点标记),从左下角开始按逆时针方向数1、2、3...依次数到最后一脚(在左上角)。在标准型TTL集成电路中,电源端Vcc一般排在左上角,接地端GND 一般排在右下角。如74LS00为14脚芯片,14脚为Vcc,7脚为GND。若芯片 集成电路使用注意事项:

设计一 四位与非门的电路设计

四位与非门的电路设计 一、课程设计的目的 1、学会使用电路设计与仿真软件工具Hspice ,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice 内部元件库。通过该实验,掌握Hspice 的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。 2、本次课程设计是用Hspice 软件来实现对四位与非门电路的设计与仿真,熟悉用MOS 器件来设计四位逻辑输入与非门电路,了解用MOS 器件设计与TTL 与非门的优缺点。 二、课程设计的内容和要求 1、内容:用仿真软件HSPICE ,用网表文件来描述模拟电路; 2、要求:用MOS 器件来设计四位逻辑输入与非门电路。 三、设计的原理 1、四输入与非门符号图及原理 A OUTPUT NAND4 1 2 3 45 D C B 真值表如下所示

A B C D Y 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1 0 0 0 1 1 0 0 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。每个输入端连到一个N沟道和一个P沟道MOS管的栅极。当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。设计电路图如下图所示:

双稳态电路图

双稳态电路图

————————————————————————————————作者:————————————————————————————————日期:

NE555为8脚时基集成电路, 各脚主要功能(集成块图在下面) 1地 GND 2触发 3输出 4复位5控制电压 6门限(阈值)7放电 8电源电压Vcc 应用十分广泛,可装如下几种电路: 1。单稳类电路 作用:定延时,消抖动,分(倍)频,脉冲输出,速率检测等。 2。双稳类电路 作用:比较器,锁存器,反相器,方波输出及整形等。 3。无稳类电路 作用:方波输出,电源变换,音响报警,玩具,电控测量,定时等。 我们知道,555电路在应用和工作方式上一般可归纳为3类。每类工作方式又有很多个不同的电路。在实际应用中,除了单一品种的电路外,还可组合出很多不同电路,如:多个单稳、多个双稳、单稳和无稳,双稳和无稳的组合等。这样一来,电路变的更加复杂。为了便于我们分析和识别电路,更好的理解555电路,这里我们这里按555电路的结构特点进行分类和归纳,把555电路分为3大类、8种、共18个单元电路。每个电路除画出它的标准图型,指出他们的结构特点或识别方法外,还给出了计算公式和他们的用途。方便大家识别、分析555电路。下面将分别介绍这3类电路。 单稳类电路 单稳工作方式,它可分为3种。见图示。 第1种(图1)是人工启动单稳,又因为定时电阻定时电容位置不同而分为2个不同的单元,并分别以1.1.1 和1.1.2为代号。他们的输入端的形式,也就是电路的结构特点是:“RT-6.2-CT”和“CT-6.2-RT”。

第2种(图2)是脉冲启动型单稳,也可以分为2个不同的单元。他们的输入特点都是“RT-7.6-CT”,都是从2端输入。1.2.1电路的2端不带任何元件,具有最简单的形式;1.2.2电路则带有一个RC微分电路。 第3种(图3)是压控振荡器。单稳型压控振荡器电路有很多,都比较复杂。为简单起见,我们只把它分为2个不同单元。不带任何辅助器件的电路为1.3.1;使用晶体管、运放放大器等辅助器件的电路为1.3.2。图中列出了2个常用电路。 双稳类电路 这里我们将对555双稳电路工作方式进行总结、归纳。555双稳电路可分成2种。 第一种(见图1)是触发电路,有双端输入(2.1.1)和单端输入(2.1.2)2个单元。单端比较器(2.1.2)可以是6端固定,2段输入;也可是2端固定,6端输入。

AT89C51引脚图及功能

AT89C51引脚图及功能 电子元件知识2010-03-04 23:12:41 阅读1759 评论1 字号:大中小订阅

89C51外部引脚图:(可以直接拷入ASM程序文件中,作注释使用,十分方便); ┏━┓┏━┓ ; P1.0 ┫1 ┗┛40┣Vcc

; P1.1 ┫2 39┣P0.0 ; P1.2 ┫3 38┣P0.1 ; P1.3 ┫4 37┣P0.2 ; P1.4 ┫5 36┣P0.3 ; P1.5 ┫6 35┣P0.4 ; P1.6 ┫7 34┣P0.5 ; P1.7 ┫8 33┣P0.6 ; RST/Vpd ┫9 32┣P0.7 ; RXD P3.0 ┫10 31┣-EA/Vpp(内1/外0 程序地址选择) ; TXD P3.1 ┫11 30┣ALE/-P (地址锁存输出) ; -INT0 P3.2 ┫12 29┣-PSEN (外部程序读选通输出) ; -INT1 P3.3 ┫13 28┣P2.7 ; T0 P3.4 ┫14 27┣P2.6 ; T1 P3.5 ┫15 26┣P2.5 ; -WR P3.6 ┫16 25┣P2.4 ; -RD P3.7 ┫17 24┣P2.3 ; X2 ┫18 23┣P2.2 ; X1 ┫19 22┣P2.1 ; GND ┫20 21┣P2.0 ; ┗━━━━┛ 引脚说明: ①电源引脚 Vcc(40脚):典型值+5V。 Vss(20脚):接低电平。 ②外部晶振 X1、X2分别与晶体两端相连接。当采用外部时钟信号时,X2接振荡信号,X1接地。 ③输入输出口引脚: P0口:I/O双向口。作输入口时,应先软件置“ 1”。 P1口:I/O双向口。作输入口时,应先软件置“ 1”。 P2口:I/O双向口。作输入口时,应先软件置“ 1”。 P3口:I/O双向口。作输入口时,应先软件置“ 1”。 ④控制引脚: RST/Vpd、ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。 RST/Vpd(9脚):复位信号输入端(高电平有效)。

实验二 TTL与非门电路参数测试

实验二 TTL 与非门电路参数测试 一、实验目的 ·掌握TTL 与非门主要参数的测试方法。 ·掌握TTL 与非门电压传输特性的测试方法。 ·熟悉集成元器件管脚排列特点。 二、实验原理 TTL 集成与非门是数字电路中广泛使用的一种基本逻辑门,使用时必须对它的逻辑功能、主要参数和特性曲线进行测试,以确定其性能好坏。 本实验采用TTL 集成元器件74LS00与非门进行测试。它是一个2输人端4与非门,形状为双列直插式,逻辑表达式为F =A ·B ,其逻辑符号及外引线排列图如图 1—1(a)(b)(c)(d)所示。

1.TTL与非门主要参数 (1)输出高电平V OH和输出低电平V OL V OH是指与非门一个以上的输入端接低电平或接地时,输出电压的大小。此时门电路处于截止状态。如输出空载,V OH必须大于标准高电平(V SH=2.4V),一般在3.6V左右。当输出端接有拉电流负载时,V OH将降低。 V OL是指与非门的所有输人端均接高电平时,输出电压的大小。此时门电路处于导通状态。如输出空载,V OL必须低于标准低电平(V SL=0.4V),约为0.1V左右。接有灌电流负载时,V OL将上升。 (2)低电平输入电流I IL I IL是指当一个输入端接地,而其他输入端悬空时,输入端流向接地端的电流,又称为输入短路电流。I IL的大小关系到前一级门电路能带动负载的个数。 (3)高电平输入电流I IH I IH是指当一个输入端接高电平,而其他输入端接地时,流过接高电平输入端的电流,又称为交叉漏电流。它主要作为前级门输出为高电平时的拉电流。当I IH太大时,就会因为“拉出”电流太大,而使前级门输出高电平降低。 (4)输入开门电平V ON和关门电平V OFF V ON是指与非门输出端接额定负载时,使输出处于低电平状态时所允许的最小输入电压。换句话说,为了使与非门处于导通状态,输入电平必须大于V ON。 V OFF是指使与非门输出处于高电平状态所允许的最大输人电压。 (5)扇出系数N0 N0是说明输出端负载能力的一项参数,它表示驱动同类型门电路的数目。N0的大小主要受输出低电平时,输出端允许灌人的最大电流的限制,如灌人负载电流超出该数值,输出低电平将显著抬高,造成下一级逻辑电路的错误动作。

四输入或非门课程设计

四输入或非门专项实践任务书 学生姓名:专业班级: 指导教师:工作单位: 题目:四输入或非门的设计 初始条件: 计算机、ORCAD软件,L-EDIT软件 要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写 等具体要求) 1、集成电路专项实践工作量:1周 2、技术要求: (1)学习ORCAD软件,L-EDIT软件。 (2)设计一个四输入或非门电路。 (3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2015619布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。 2015619-6.24学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2015.6.24-7.1用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT 软件绘制其版图,完成集成电路专项实践报告的撰写。 2015.7.1提交集成电路专项实践报告,进行答辩。 指导教师签名:年月日

系主任(或责任教师)签名: 目录 摘要 .................................................................................... I Abstract ................................................................................................................................................... II 1绪论 (1) 2设计内容及要求 (2) 2.1设计的目的及主要任务 (2) 2.2设计思路 (2) 3软件介绍 (2) 3.1 OrCAD 简介 (2) 3.2 L-Edit 简介 (4) 4四输入或非门 (5) 4.1 四输入或非门电路结构 (5) 4.2 四输入或非门电路仿真 (6) 4.3四输入或非门的版图绘制 (7) 4.3.1 NMOS 管 (7) 4.3.2 PMOS 管 (8) 4.3.3输出端口 (8) 4.3.4 四输入或非门 (8) 总结 (10) 参考文献 (12)