基于ARM的音频播放器设计毕业论文

基于ARM的音频播放器设计毕业论文

一、概述

音频播放一直是人们所钟爱的,琳琅满目的各种个样的MP3播放器随处可见,但其相应的驱动能力有限。本设计是采用S3C44B0X处理器的IIS音频接口和音频编码解码芯片UDA1341TS,并用DMA方式高效地来实现录音和播放声音时的数据传输。

二、音频播放器硬件设计

2.1 硬件体系结构设计

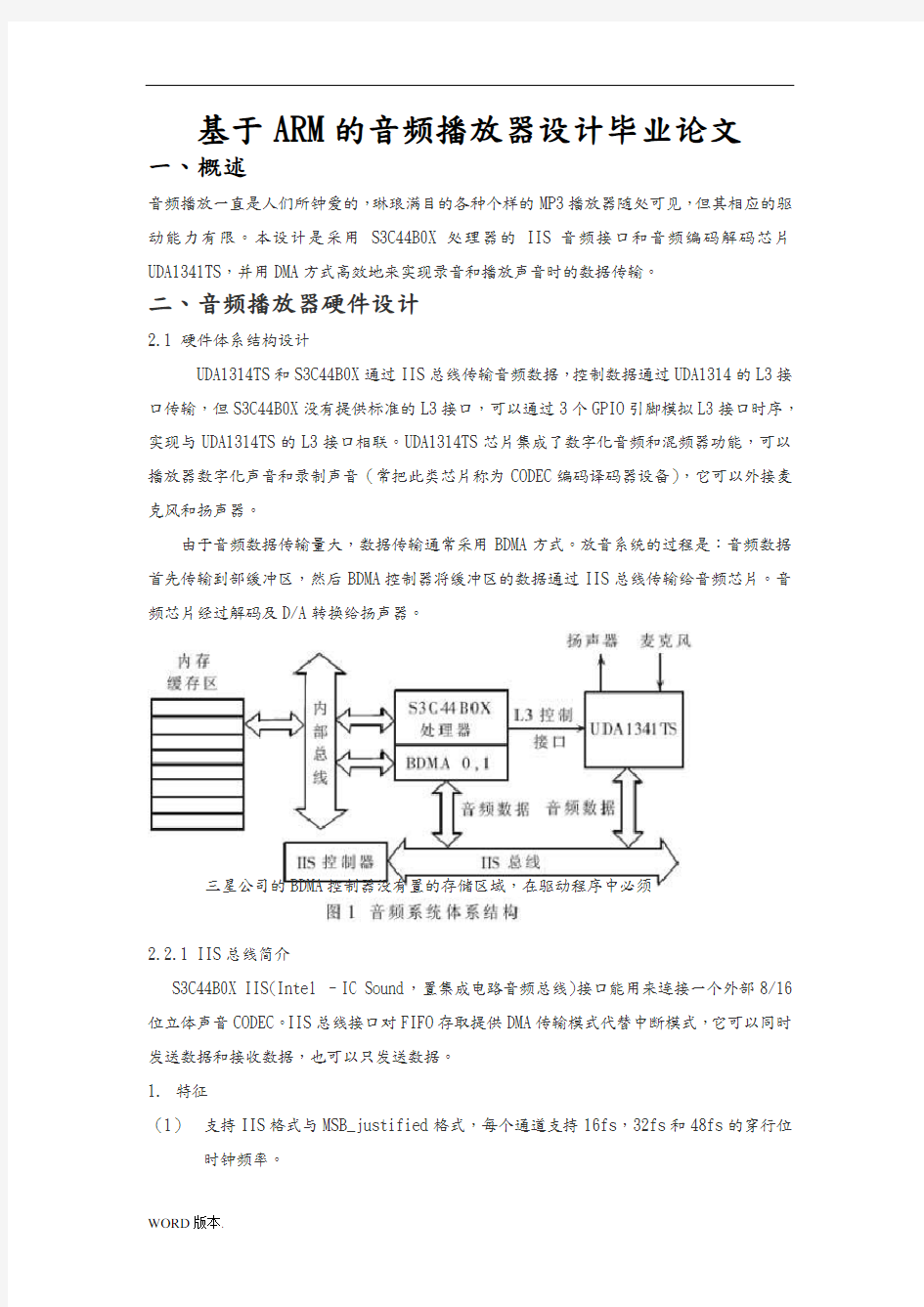

UDA1314TS和S3C44B0X通过IIS总线传输音频数据,控制数据通过UDA1314的L3接口传输,但S3C44B0X没有提供标准的L3接口,可以通过3个GPIO引脚模拟L3接口时序,实现与UDA1314TS的L3接口相联。UDA1314TS芯片集成了数字化音频和混频器功能,可以播放器数字化声音和录制声音(常把此类芯片称为CODEC编码译码器设备),它可以外接麦克风和扬声器。

由于音频数据传输量大,数据传输通常采用BDMA方式。放音系统的过程是:音频数据首先传输到部缓冲区,然后BDMA控制器将缓冲区的数据通过IIS总线传输给音频芯片。音频芯片经过解码及D/A转换给扬声器。

三星公司的BDMA控制器没有置的存储区域,在驱动程序中必须

2.2.1 IIS总线简介

S3C44B0X IIS(Intel –IC Sound,置集成电路音频总线)接口能用来连接一个外部8/16位立体声音CODEC。IIS总线接口对FIFO存取提供DMA传输模式代替中断模式,它可以同时发送数据和接收数据,也可以只发送数据。

1.特征

(1)支持IIS格式与MSB_justified格式,每个通道支持16fs,32fs和48fs的穿行位时钟频率。

(2) 每个通道可以支持8位或者16数据格式。 (3) 256fs 和384fs 主时钟

(4) 时钟和外部CODEC 时钟的可编程的频率分频器。 (5) 32字节的发送和接收FIFO

(6) 支持正常传输模式和DMA 传输模式。 2. IIS 总线结构 ADDR IISDI DATA IISDO

ONTL

BRFC 包括总线接口、部寄存器、状态机、控制总线接口和FIFO 访问;3位的双向分频器包括一个作为IIS 总线的主设备时钟发生器,另一个作为外部时钟编码器的时钟发生器;16字节发送和接收FIFO 完成发送数据写入发送FIFO ,接收数据从接收FIFO 中读出功能;主设备串行比特时钟发生器(主设备模块)将从主设备时钟中分频得到串行比特数时钟;声道发生器和状态器生成和控制IISCLK 和IISLRCK ,并且控制数据的接收和发送;16位移位寄存器在发送数据时将数据由并变串,接收数据时将数据由串变并。

IISCLK IISLRC 发生器和声 道控制器

(CHN C )

16字节发送FIFO

16字节接收FIFO

IIS 主时钟发生器

总线接口

FIFO 控制 (BRFC )

16

位移

位寄存器

3.系统的IIS总线的连接方式

IIS总线上最多只能有一个主控设备,由它产生所有的时钟信号。数据总是在时钟的触发下从发送端流向接收端。

4.数据传输方式的选择

IIS总线有三种传输方式,即:正常传输模式、DMA传输方式以及发送和接收同时模式。音频数据的发送和接收都通过了一个FIFO队列,但是只靠FIFO来保证声音的连续播放是困难的,有时根本不可能保证数据的连续播放,所以必须采取传输效率更高的DMA传输方式进行数据的传输,保证音频数据传输的高效性,保证音频播放的连续性。

播放音频数据时,系统一次设置完成DMA控制器的源数据地址(存中的数据),目的地址(音频FIFO)和数据长度等信息,DMA控制器就会自动发送缓冲区中的数据自动到FIFO中,直到发送完成设定的数据长度才向系统中申请中断,这样即可实现音频数据的连续播放。5.声音串口数据格式的设计

本系统采用IIS总线格式。

IIS总线格式,IIS有4条线,即串行数据输入(IISDI),串行数据输入(IISDO),左右声道选择(IISLRCK)和串行位时钟(IISCLK);产生IISLRCK和IISCLK信号的为主设备。

串行数据以2的补码发送,并且首先发送高位数据。发送器总是在IISLRCK变化的下一个时钟周期发送下一个字的高位。

发送器的串行数据发送可以在时钟信号的上升沿或下降沿被同步。可是串行数据必须在串行时钟信号的上沿锁存进接收器,所以当用发送数据用上升沿来同步有一些限制。

LR通道选择线指示当前正发送的通道。IISLRCK既可以在串行时钟的上升沿变化,也可以在时钟的下降沿变化,但不需要同步,在从模式的这个信号在串行时钟的上升沿被锁存。IISLRCK在高位发送之前变化一个时钟周期,这允许从发送方可以同步发送串行数据,更进一步,他允许接收放存储先前的字和清楚输入来接收下一个字。

6.采样频率和主时钟设计

IIS包含了左右两个声道的数据,IISLRCK的频率就是两个声道的采样频率(fs)。音频系统主时钟CODECLK一般为采样频率的256fs或者384fs倍,其中fs为采样频率。

CODECLK通过处理器主时钟分频得到,可以通过程序设定分频寄存器获得。分频因子可以为1-16。CODECLK与采样频率的对应关系如下表。应用中需要正确的选择IISLRCK和CODECLK。串行时钟频率IISCLK可以为采样频率的16倍、32倍、48倍。对于16位的数据,IISCLK至少要有32倍的采样频率,而通常要求提供给编码芯片的系统时钟为

256fs或者384fs,这里3个时钟要求同步。例如。声音的采样频率为44.1khz,则必须提供大概为256*44.1khz=11.290mhz或者384*44.1khz16.936mhz的CODECLK时钟。时钟越准确,声音的失真就越小。Iis接口的所有时钟信号都是由主控芯片产生的,与编解码器无关。

另外,处理器时钟可以通过配置锁相环寄存器进行调整。结合CODECLK的分频寄存器设置,可以获得所需要的CODECLK。

7.IIS操作

启动IIS操作需执行一下过程

(1)允许IISFCON寄存器的FIFO

(2)允许IISFCON寄存器的DMA请求

(3)允许IISFCON寄存器的启动

结束IIS操作

(1)不允许IISFCON寄存器的FIFO,如果还想发送FIFO的剩余数据,则跳过这一步。(2)步允许IISFCON寄存器的DMA请求。

(3)步允许IISFCON寄存器的启动。

IIS总线接口寄存器

1、控制寄存器

IISCON 位描述初始化状态

左右通道索引(只读)[8] 0=左通道

1=右通道

1

发送 FIFO 准备好

标志(只读)

[7] 0=没有准备好

1=准备好(非空)

接收 FIFO 准备好

标志(只读)

[6] 0=没有准备好(未满)

1=准备好(满)

发送 DMA 服务请求使能[5] 0=请求未使能

1=请求使能

接收DMA 服务请求使能[4] 0=请求未使能

1=请求使能

发送通道空闲命令[3] 空闲状态IISLRCK 未激

活的(暂停Rx)。这个位

仅在作为 IIS主机时有

效0=IISLRCK产生

2.IIS模式寄存器

3 IIS预定标寄存器

定标因子与分频因子的对应关系

4.IIS FIFO 控制寄存器

5 IIS FIFO寄存器

IIS总线接口包含两个16字节发送和接收FIFO,每个FIFO有8个16位单元,可以通过IISFIF 寄存器来存取和接收FIFO的数据。

IISFIF 位描述初始值

FENTRY(FIFO入口) [0:15] IIS发送、接收数据 0