数字电路低功耗设计(二)

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析。由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具;更精确的功耗分析可以采用PT,关于PT的功耗分析可以查阅其他资料,这里不涉及使用PT的进行功耗分析。

(1)功耗分析与流程概述

上一个小节中讲解了功耗的构成,并且结合工艺库进行简要地介绍了功耗的计算。但是实际上,我们根本不可能人工地计算实际的大规模集成电路的功耗,我们往往借助EDA工具帮我们分析电路的功耗。这里我们就介绍一下EDA工具分析功耗的(普遍)流程,然后下一小节我们将介绍低功耗电路的设计和优化。

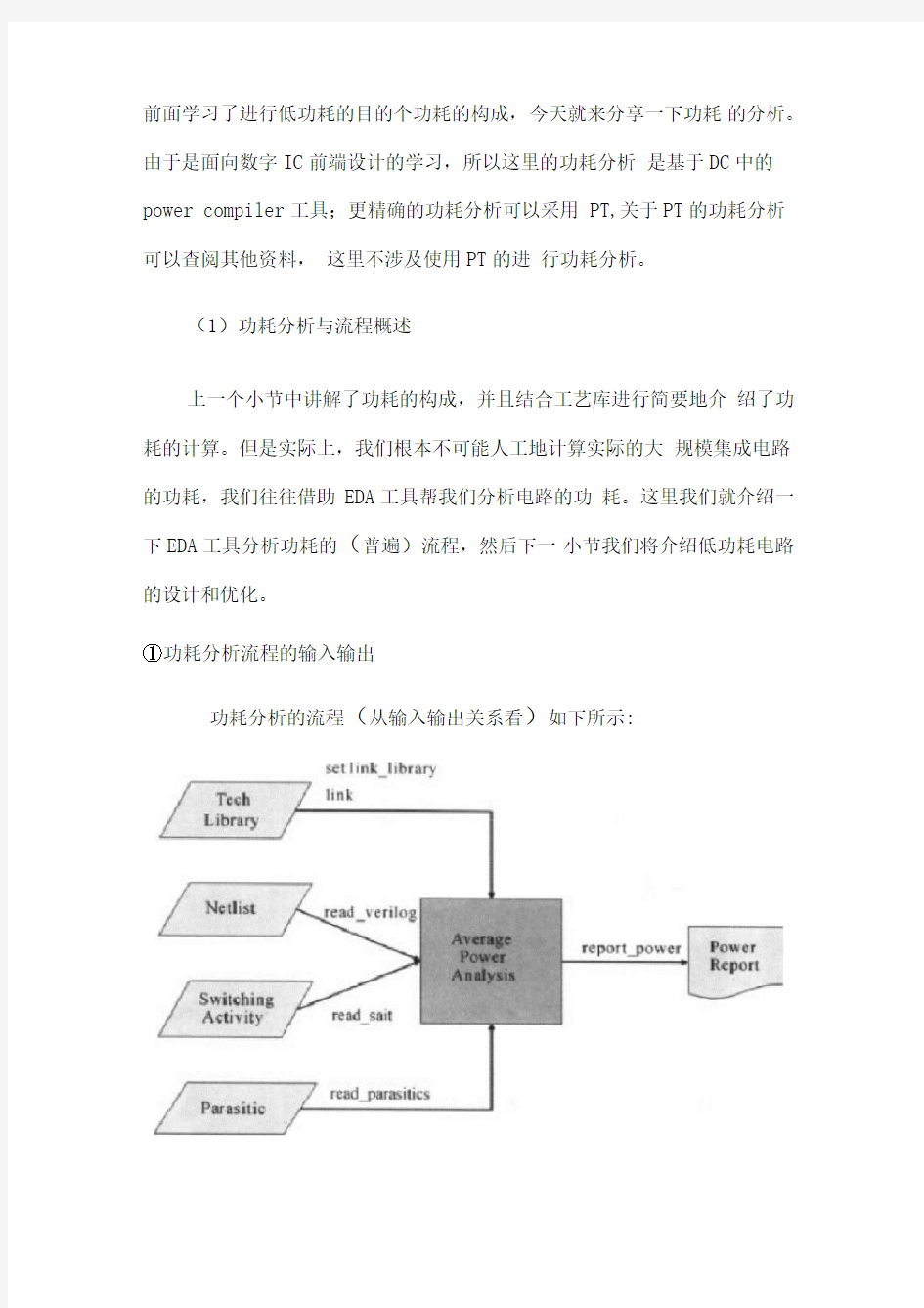

①功耗分析流程的输入输出

功耗分析的流程(从输入输出关系看)如下所示:

上面的图中,需要四种东西:

?tech library :这个就是包含功耗信息的工艺库了,比较精确

的库里面还应该包含状态路径(SDPD信息,代工厂提供。

?netlist :设计的门级网表电路,可以通过DC综合得到。

-parasitic :设计中连线等寄生参数,比如寄生电容、寄生电阻, 这个一般是后端RC寄生参数工具提供,简单的功耗分析可以不需要这个文件。

?switch activity :包含设计中每个节点的开关行为情况,比如

说节点的翻转率或者可以计算出节点翻转率的文件。这个开关行为输

入文件是很重要的。这个开关行为可以有不同的形式提供,因此就有

后面不同的分析功耗的方法。

(注意,不管使用什么方法进行功耗分析,功耗分析的时候,输入设

计文件的都是门级网表文件)

②开关行为的一些概念

说到开关行为,我们前面的翻转率也是一种开关行为。此外我们还有其他关于开关行为描述的概念,这里我们通过举例说明,如下图所示:

相关主题