VHDL数字钟实验报告

XXXXXXXXXXXXXXXXXX CPLD实验报告

实验名称:VHDL数字钟

姓名: XXXXXX

班级:电子与电气081

学号: 830702043

指导老师: XXXXXX

实验摘要

一、实验摘要

数字钟用到了很多我们数字电路里所学的数电知识,例如译码器、编码器、数据选择器、计数器等~。因此,做数字钟有着非常现实的意义。本实验使用VHDL 语句进行各模块的编写。由于本实验采用的是动态扫描的方式循环点亮四个共阳数码管,所以需要编写共阳显示译码器,三态门芯片、四进制计数器以及二~四译码器。

关键字:数字钟、CPLD、VHDL、动态扫描、三态门

实验目的

二、实验目的

学会使用Quartus Ⅱ这款EDA常用设计软件。

掌握在Quartus Ⅱ中VHDL语句的使用方法。

加强巩固层次设计思路、电路图的作法、仿真方法和作图技巧。

掌握CPLD实验箱的使用和电路的加载运行方法。

实验内容

三、实验内容

(1)认识VHDL

数字系统设计分为硬件设计和软件设计,但是随着计算机技术、超大规模集成电路(CPLD、FPGA)的发展和硬件描述语言的出现,软、硬件设计之间的界限被打破数字系统的硬件设计可以完全用软件来实现,只要掌握了HDL语言就可以设计出各种各样的数字逻辑电路。

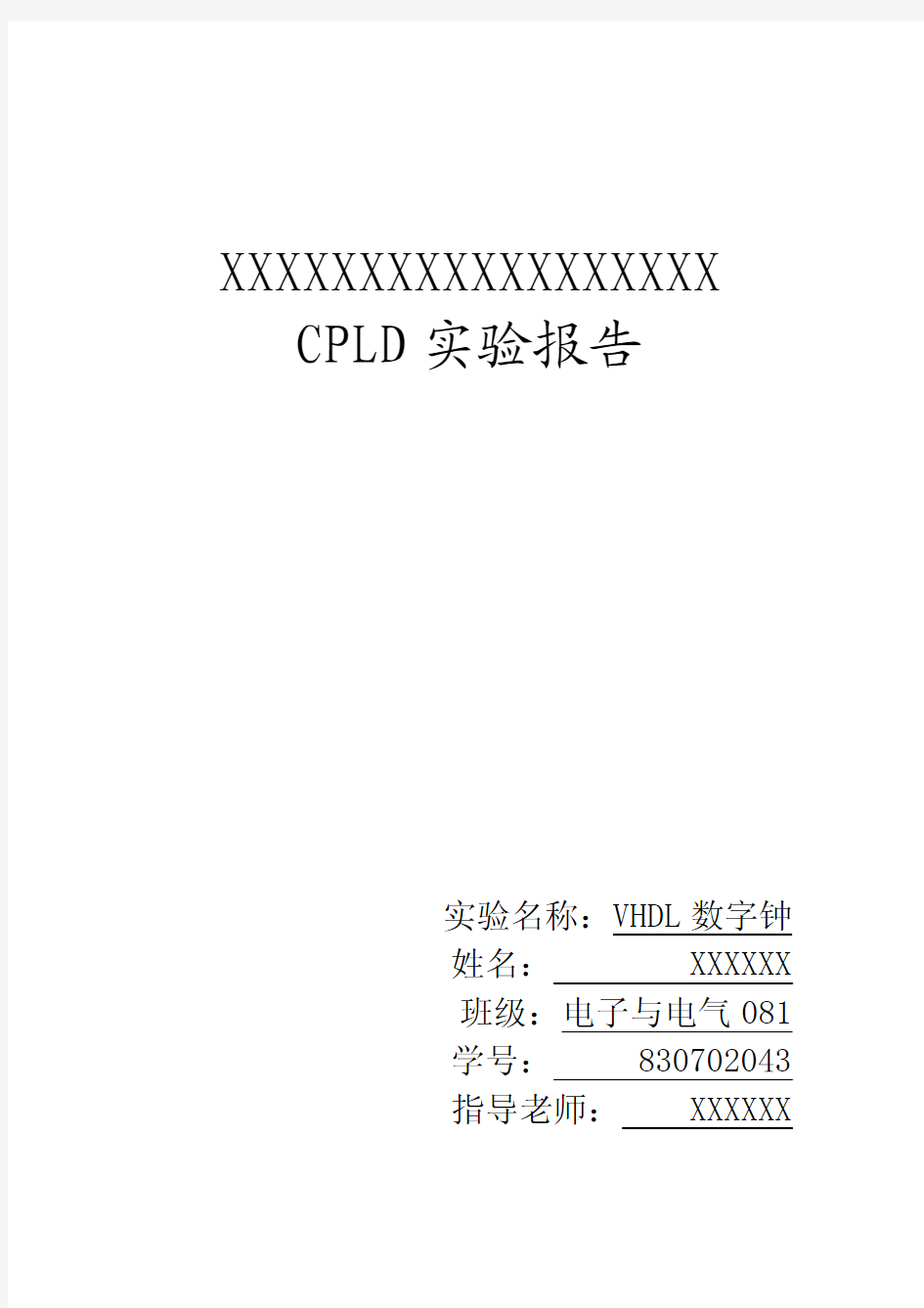

(2)60进制计数器的设计

60进制计数器输入信号:时钟脉冲,对于本次数字钟设计为节省资源占用可不设置清零输入,输出信号:两位BCD码输出,一个进位输出。

entity counter60v is

port(

clk :in bit;

ql :buffer integer range 9 downto 0;

qh :buffer integer range 5 downto 0;

jinwei:out bit);

end counter60v;

architecture c60 of counter60v is 生成的模块功能示意图:

begin

process( clk )

begin

if(clk'event and clk='1')then

if ql=9 then Array ql<=0;

if qh=5 then

qh<=0;

else

qh<=qh+1;

end if;

else

ql<=ql+1;

end if;

end if;

if(qh=5 and ql=9)then

jinwei<='1';

else

jinwei<='0';

end if;

end process;

end c60;

(3)24进制计数器的设计

24进制计数器输入信号:时钟脉冲,对于本次数字钟设计为节省资源占用可

不设置清零输入,输出信号:两位BCD 码输出,这里不需要进位输出。

entity counter24v is

port( clk :in bit; ql :buffer integer range 9 downto 0; qh :buffer integer range 2 downto 0 );

end counter24v;

architecture c24 of counter24v is

生成的模块功能示意图:

begin process( clk ) begin if(clk'event and clk='1')then if ql=3 and qh=2 then ql<=0; qh<=0; elsif ql=9 then ql<=0; qh<=qh+1; else ql<=ql+1; end if; end if; end process; end c24;

下面是仿真出的二十四进制波形图。

从上面的图可以看出在计24个数之后,高低位同时清零。 (3)4进制计数器的设计 用于动态扫描计数 输入信号:时钟脉冲, 输出信号:两位二进制码。

entity counter4v is port( clk1 :in bit; q :buffer integer range 3 downto 0 );

end counter4v;

architecture c4 of counter4v is begin process( clk1 )

begin if(clk1'event and clk1='1')then if q=3 then q<=0; else q<=q+1; end if; end if; end process; end c4;

下面是仿真出的四进制波形图。

(4)2-4译码器的设计

用于驱动数码管共阳端

输入信号:两位二进制输入

输出信号:四位二进制顺序输出

--可以使用多种语句编写

entity decode24v is--24译码器

port(

sel :in bit_vector(1 downto 0);

y :out bit_vector(3 downto 0)

);

end decode24v;

--配置

configuration xxy of decode24v is

for aa

end for;

end xxy;

--选择信号赋值

architecture aa of decode24v is

begin

with sel select

y <="1000" when "00",

"0100" when "01",

"0010" when "10",

"0001" when others;

end aa; ----条件赋值

architecture bb of decode24v is

begin

y <= "1000" when sel = "00" else

"0100" when sel = "01" else

"0010" when sel = "10" else

"0001";

end bb;

-----case语句

architecture dd of decode24v is

begin

process(sel)

begin

case sel is

when"00"=>

y<="0001";

when"01"=>

y<="0010";

when"10"=>

y<="0100";

when"11"=>

y<="1000";

end case;

end process;

end dd;

下面是仿真出2-4译码器波形图。

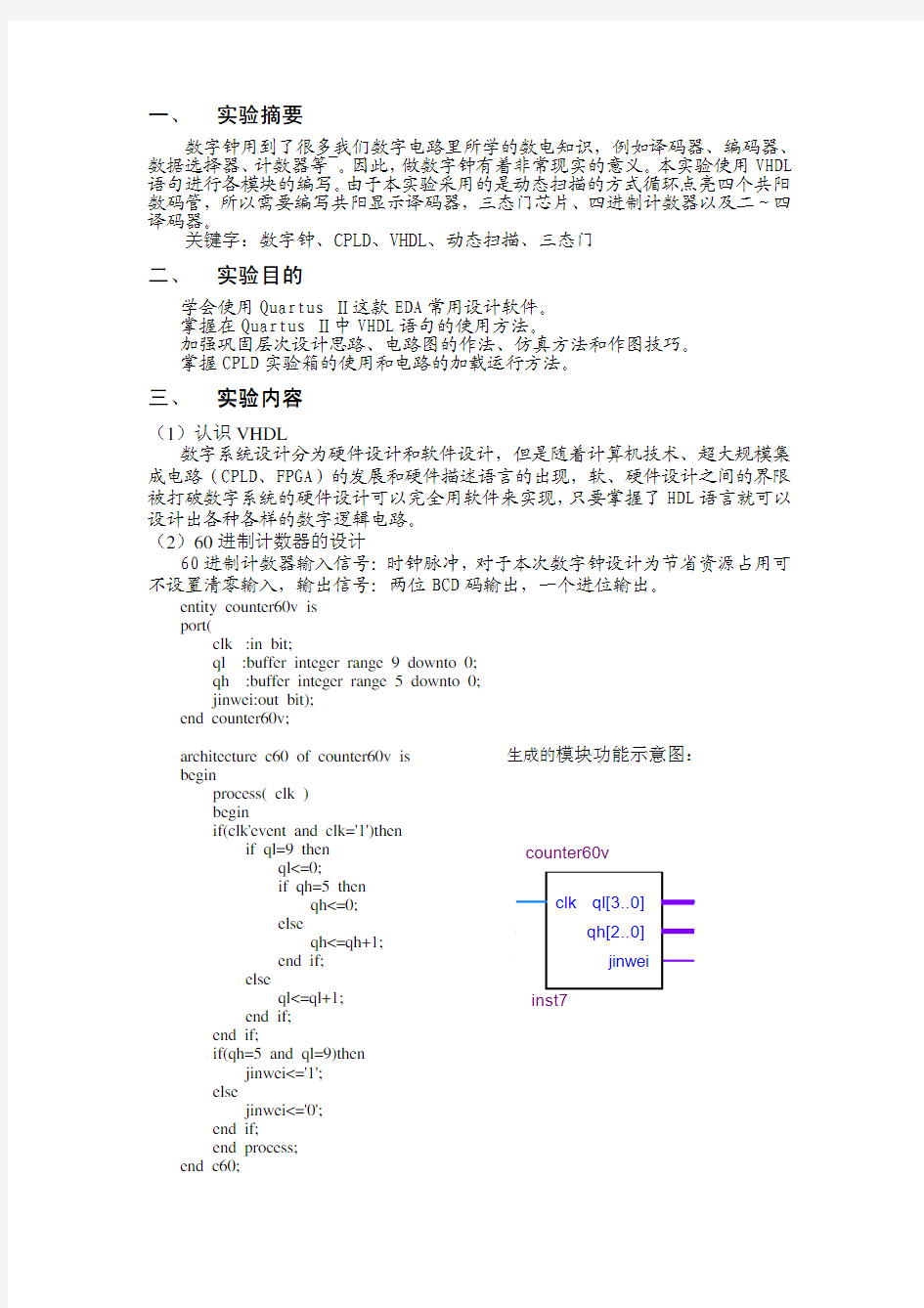

(5)数据选择器的设计

用于输出动态显示所需要的输入

输入信号:两位二进制输入,4组数据输入 输出信号:1组数据输出

--可以使用多种语句编写

entity mux4v is--数据选择器

port(

a,b,c,d:in bit_vector(3 downto 0);

sel :in bit_vector(1 downto 0);

result:out bit_vector(3 downto 0)

);

end mux4v; --配置

configuration xxy of mux4v is for dd

end for;

end xxy;

a[3..0]b[3..0]c[3..0]d[3..0]sel[1..0]result[3..0]mux4v

inst9

----if 语句

architecture cc of mux4v is begin process(sel, a,b,c,d) begin if sel="00"then result<=a; elsif sel="01"then result<=b; elsif sel="10"then result<=c; else result<=d; end if; end process; end cc;

-----case 语句

architecture dd of mux4v is begin process(sel, a,b,c,d) begin case sel is when"00"=> result<=d; when"01"=> result<=c; when"10"=> result<=b; when"11"=> result<=a; end case; end process; end dd; --选择信号赋值

architecture aa of mux4v is begin with sel select result <= a when "11", b when "10", c when "01", d when others; end aa;

----条件赋值

architecture bb of mux4v is begin result <= a when sel = "00" else b when sel = "01" else c when sel = "10" else d; end bb;

生成的模块功能示意图:

下面是仿真出数据选择器的波形图。

(6)码器的设计 entity m148 is port(

result :in bit_vector(3 downto 0); seg :out bit_vector(6 downto 0) );

end m148;

-------------case 语句------------ architecture bb2 of m148 is begin

process(result)

begin

case result is

when"0000"=> seg<="1111110";

when"0001"=> seg<="0110000";

when"0010"=> seg<="1101101";

when"0011"=> seg<="1111001";

when"0100"=> seg<="0110011";

when"0101"=> seg<="1011011";

when"0110"=> seg<="0011111";

when"0111"=> seg<="1100010";

when"1000"=> seg<="1111111";

when others=> seg<="1110011"; end case;

end process;

end bb2;

下面是仿真出74248译码器的波形图。

(7)将各模块组合

四、实验小结

通过本次实验对软件EDA软件有了更深的了解,掌握在Quartus Ⅱ中VHDL语句VHDL语句的编写、仿真方法和层次设计的意义。

在实现不同电路的功能时,使用不同的语句其实际电路是不一样的,在语句的编写过程中如果可以使用”=”,就尽量避免” >”或”<”的使用,这样可以减小对硬件的占用。类似的问题还有很多,在语句描写的时候,不仅仅要考虑功能的实现,减小对硬件的使用量也是非常重要的。

这次试验收获了很多,养成严谨以及对事物的细心观察的习惯,对问题的解决可以有很大的帮助。