实验一 匹配电路的设计与仿真

实验一 匹配电路的设计与仿真

一、实验目的

1、掌握阻抗匹配、共轭匹配的原理

2、掌握集总元件L 型阻抗抗匹配网络的匹配机理

3、掌握并(串)联单支节调配器、λ/4阻抗变换器匹配机理

4、了解ADS 软件的主要功能特点

5、掌握Smith 原图的构成及在阻抗匹配中的应用

6、了解微带线的基本结构

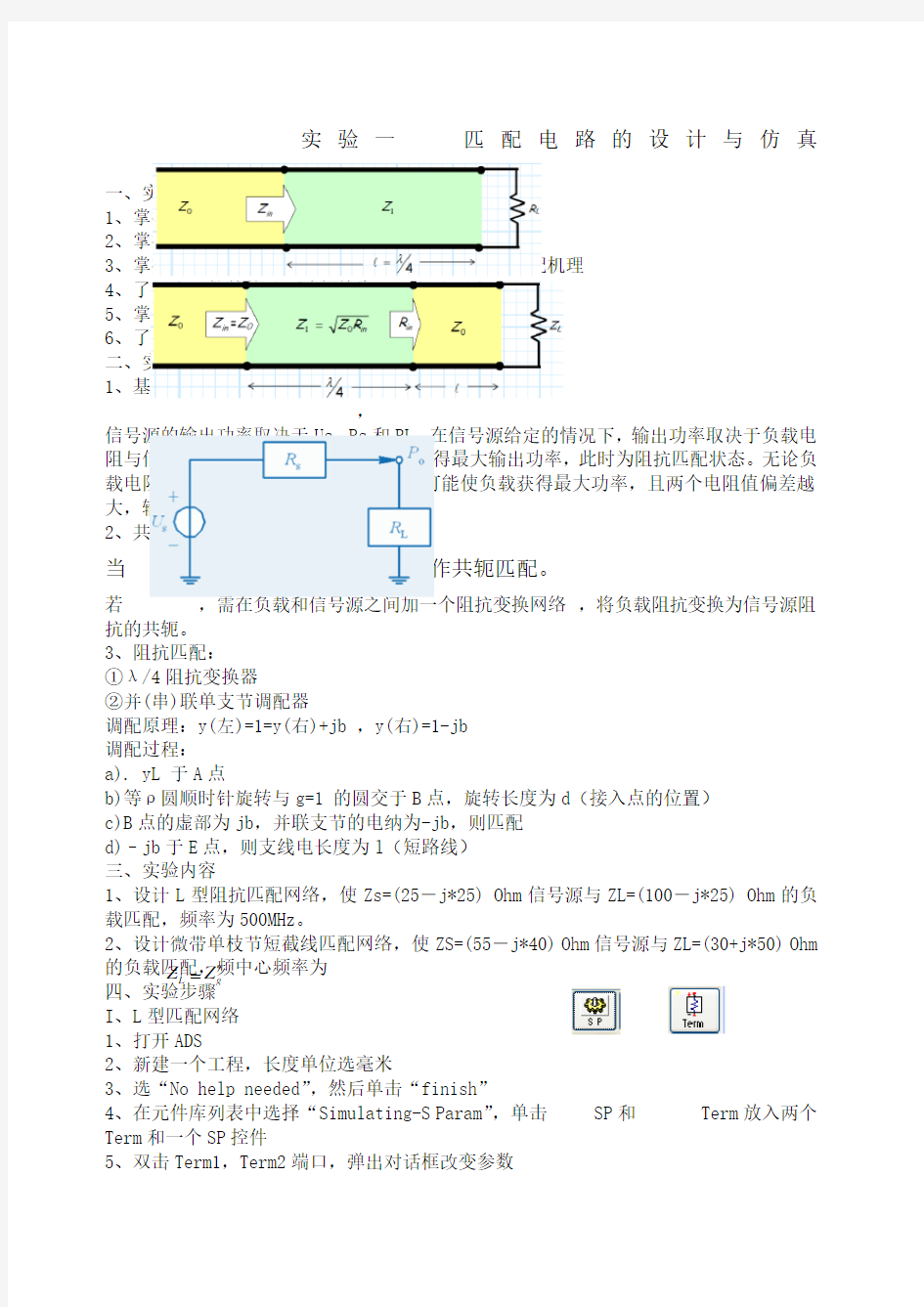

二、实验原理

1、基本阻抗匹配理论

,

信号源的输出功率取决于Us 、Rs 和RL 。在信号源给定的情况下,输出功率取决于负载电阻与信号源内阻之比k 。当RL=Rs 时可获得最大输出功率,此时为阻抗匹配状态。无论负载电阻大于还是小于信号源内阻,都不可能使负载获得最大功率,且两个电阻值偏差越大,输出功率越小。

2、共轭匹配:

当 ,源输出功率最大,称作共轭匹配。

若 ,需在负载和信号源之间加一个阻抗变换网络 ,将负载阻抗变换为信号源阻抗的共轭。

3、阻抗匹配:

①λ/4阻抗变换器

②并(串)联单支节调配器

调配原理:y(左)=1=y(右)+jb ,y(右)=1-jb

调配过程:

a). yL 于A 点

b)等ρ圆顺时针旋转与g=1 的圆交于B 点,旋转长度为d (接入点的位置) c)B 点的虚部为jb ,并联支节的电纳为-jb ,则匹配

d)–jb 于E 点,则支线电长度为l (短路线)

三、实验内容

1、设计L 型阻抗匹配网络,使Zs=(25-j*25) Ohm 信号源与ZL=(100-j*25) Ohm 的负载匹配,频率为500MHz 。

2、设计微带单枝节短截线匹配网络,使ZS=(55-j*40) Ohm 信号源与ZL=(30+j*50) Ohm

的负载匹配,频中心频率为 四、实验步骤

I 、L 型匹配网络

1、打开ADS

2、新建一个工程,长度单位选毫米

3、选“No help needed ”,然后单击“finish ”

4、在元件库列表中选择“Simulating-S Param ”,单击 SP 和 Term 放入两个Term 和一个SP 控件

5、双击Term1,Term2端口,弹出对话框改变参数

*g L Z Z

6、双击S-Paraemters控件,弹出对话框改变参数

7、选择元件库“Smith Chart Matching”,单击在原理图中添加“DA_SmithChart Matching”控件,单击工具栏,放置并连接原件

8、双击DA_SmithChartMatching控件,设置相关参数

9、执行菜单命令【

Tools】【Smith Chart】,弹出“SmartComponent Syne”对话框,选择“Update SmartComponent from Smith Chart Utility”,单击OK

10、改变Freq,单击“DefineSource/load Network terminations”按钮

11、采用分立元件LC匹配过程如下图

改变L、C位置,观察L、C值变化时输入阻抗变化轨迹

12、单击“Build ADS Circuit”按钮,即可生成相应的电路

13、选中DA_SmithChartMatch控件,单击菜单栏向下的箭头,以查看匹配电路

14、单击向上的箭头,返回到原理图

15、单击图标,进行仿真

16、单击,在结果窗口单击,选中要查看的图形,仿真结果输出

II、微带单支节短截线

1、新建一个工程,长度单位选毫米

2、在元件库列表中选择“Passive Circuit DG-Matching”,放置元件MSUB(微带基片)和SSMATH(微带单支节短截线)

3、执行菜单命令【Insert】【Template】,选择S_ Params,在原理图中加入S参数模块

4、双击MSUB元件,设置参数

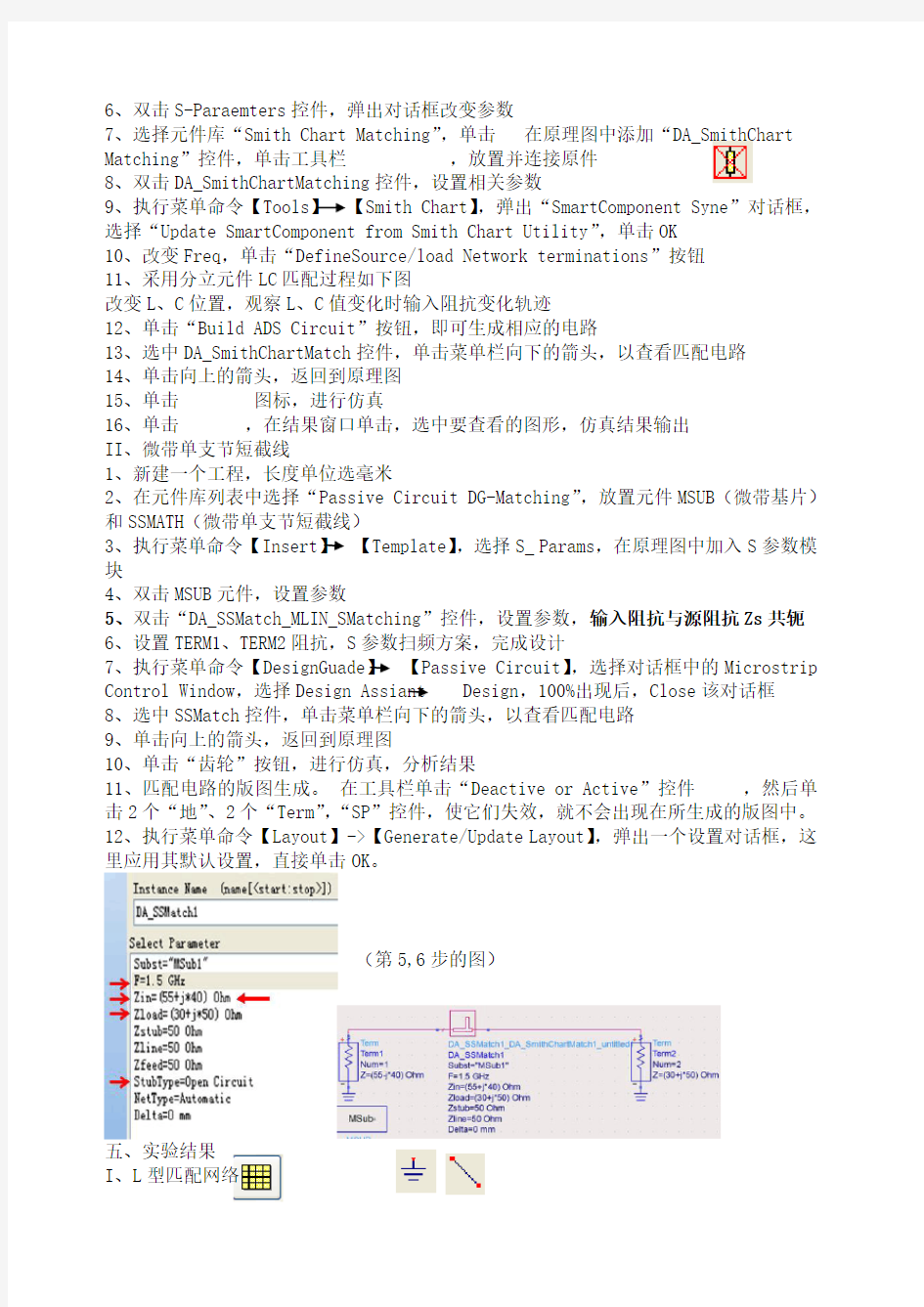

5、双击“DA_SSMatch_MLIN_SMatching”控件,设置参数,输入阻抗与源阻抗Zs共轭

6、设置TERM1、TERM2阻抗,S参数扫频方案,完成设计

7、执行菜单命令【DesignGuade】【Passive Circuit】,选择对话框中的Microstrip Control Window,选择Design Assiant Design,100%出现后,Close该对话框

8、选中SSMatch控件,单击菜单栏向下的箭头,以查看匹配电路

9、单击向上的箭头,返回到原理图

10、单击“齿轮”按钮,进行仿真,分析结果

11、匹配电路的版图生成。在工具栏单击“Deactive or Active”控件,然后单击2个“地”、2个“Term”,“SP”控件,使它们失效,就不会出现在所生成的版图中。

12、执行菜单命令【Layout】->【Generate/Update Layout】,弹出一个设置对话框,这里应用其默认设置,直接单击OK。

五、实验结果

I、L型匹配网络

(第5,6步的图)

由仿真结果可知在500MHz时反射系数最小,电压传输系数最大,系统性能最好。

II、微带单支节短截线

由仿真结果可知在时反射系数较小,电压传输系数最大,系统性能较好。

六、练习题

1、设计L型阻抗匹配网络,使Zs=(46-j×124) Ohm信号源与ZL=(20+j×100) Ohm的负载匹配,频率为2400MHz.

解:原理图:

匹配电路:

仿真结果如下:

2、设计微带单枝短截线线匹配电路,使MAX2660的输出阻抗ZS=(126-j*459)Ohm与ZL=50Ohm的负载匹配,频率为900MHz.

微带线板材参数:

相对介电常数:,相对磁导率:,导电率:,损耗角正切:1e-4

基板厚度:,导带金属厚度:

解:原理图:

匹配电路:

仿真结果:

版图生成如下:

七、思考题

1、常用的微波/射频EDA仿真软件有哪些?

答:微波/射频领域主要的EDA工具有Agilent公司的ADS软件和Ansoft公司的HFSS、Designer软件, Microwave Office, Ansoft Serenade ,CST等微波/射频电路设计软件,还有Smith圆图软件Winsmith等。

2、用ADS软件进行匹配电路设计和仿真的主要步骤有哪些?

答:画出原理图,添加DA_SmithChartMatching”控件,设置相关参数,执行菜单命令【Tools】→【Smith Chart】,弹出“SmartComponent Syne”对话框,选择“Update SmartComponent from Smith Chart Utility”,单击OK,在Smith Chart中并联电感串联电容或并联电容串联电感,改变电容电感的值,直至匹配。单击“Build ADS Circuit”按钮,即可生成相应的电路。在原理图中,选中DA_SmithChartMatch控件,单击菜单栏向下的箭头,以查看匹配电路,单击向上的箭头,返回到原理图。单击“齿轮”图标,进行仿真。

3、给出两种典型微波匹配网络,并简述其工作原理。

答:下图为两种典型微波匹配网络:

对于T型网络,它的输入输出阻抗和传输系数分别为:

其中A11,A12,A21,A22为网络A参数,通过上式可求得:

同时可求得 型网络的电路参数为:

4、画出微带线的结构图,若导带宽度w、εr增大,其特征阻抗Z0如何变化?

答:微带线的结构图如下图。介质微带特性阻抗随着W/h增大而减小;相同尺寸条件下,εr越大,特性阻抗Z0越小。

5、写出实验体会和建议。

通过此次试验了解了阻抗匹配网络的原理,重点学会了L型阻抗匹配网络的设计,学会用Smith原图进行阻抗匹配,对ADS软件有了初步的了解。此外,也学会了用微带单支节短截线进行阻抗匹配。

模拟电路自主设计实验

姓名_____________________班级_____________________学号_____________________ 日期_____________节次______________成绩__________教师签字__________________ 哈尔滨工业大学模拟电路自主设计实验 实验名称:运算放大器在限幅电路中的应用 一、实验目的 1、深入了解运算放大器的放大作用和深度负反馈; 2、灵活运用运算放大器的多种应用; 二、总体技术路线 2.1 当输入信号电压进入某一范围内,其输出信号的电压不再跟随输入信号电压的变化。 串联限幅电路:当输入电压U i <0或U i为数值较小的正电压时,D1截止,运算放大器的输出电压U0=0;仅当输入电压U i>0且U i为数值大于或等于某一个的正电压U th时,D1才正偏导通,电路有输出,且U0跟随输入信号U i变化。 并联限幅电路:当输入信号U i较小时,输出电压U0也较小,D1和D2没有击穿,U0跟随输入信号U i变化而变化,传输系数为:A uf=-R1 /R2;当U i幅值增大,使U0的幅值增大,并使D1和D2击穿,输出U0的幅度保持+(U z+U D)值不变,电路进入限幅工作状态。 2.2绝对值电路 当输入电压U i>0,则运算放大器的输出电压U1,D1导通,D2截止,输出电压U0 =0;当输入电压U i <0,则运算放大器的输出电压U1 >0,D2导通,D1截止,输出电压U0 =-R1 U i/R2。并通过反向放大器将整流信号放大两倍,再增加一个同相加法器,让输入信号的另一极性电

压不经整流,而直接送到加法器,与来自整流电路的输出电压相加,便构成了绝对值电路。 三、实验电路图 1、串联限幅电路: 2、并联限幅电路:

集成电路设计实验报告

集成电路设计 实验报告 时间:2011年12月

实验一原理图设计 一、实验目的 1.学会使用Unix操作系统 2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件 二:实验内容 使用schematic软件,设计出D触发器,设置好参数。 二、实验步骤 1、在桌面上点击Xstart图标 2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入 用户密码,在protocol:中选择telnet类型 3、点击菜单上的Run!,即可进入该用户unix界面 4、系统中用户名为“test9”,密码为test123456 5、在命令行中(提示符后,如:test22>)键入以下命令 icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。 出现的主窗口所示: 6、建立库(library):窗口分Library和Technology File两部分。Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。 7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输 入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。当然在Tool工具中还有很多别的

阻抗变换器的设计与仿真

摘要 射频设计的主要工作之一,就是使电路的某一部分与另一部分相匹配,在这两部分之间实现最大功率传输,这就需要在射频电路中加入阻抗变换器从而达到阻抗匹配的目的。本文介绍了一种中心频率为400MHz、频宽为40MHz的50~75欧姆T型阻抗变换器的设计与仿真过程。文中概述了射频阻抗变换器的种类、用途及发展。在分析了阻抗匹配理论基本知识的基础上,论述了射频阻抗变换器的设计过程,然后通过ADS软件进行设计和仿真,并对仿真结果进行了分析总结。 关键词:射频;阻抗匹配;阻抗圆图;VSWR(电压驻波比);ADS 目录 摘要 (1) ABSTRACT................................................ 错误!未定义书签。第一章引言 (2) 1.1 概述 (2) 1.2 射频阻抗变换电路的类型 (2) 1.3 射频阻抗变换器的用途 (2) 1.4射频阻抗变换器设计的发展 (3) 第二章基本原理 (3) 2.1 阻抗匹配 (3) 2.2 史密斯圆图 (4) 2.2.1 等反射圆 (4) 2.2.2 等电阻圆图和等电抗圆图 (5) 2.2.3 Smith圆图(阻抗圆图) (7) 2.3 电压驻波比 (8) 第三章 T型阻抗变换器的设计 (9) 3.1 T型阻抗变换器(R S 实验一 单级阻容耦合放大器设计 一、设计任务书 1.已知条件 电源电压V cc =+12V,信号源U s =10mV,内阻R s =600Ω,负载R L =2k Ω。 2.主要技术指标 输入电阻R i >2k Ω,频率响应20Hz ~500kHz,输出电压U o ≥0.3V,输出电阻R O <5k Ω,电路工作稳定。 3.实验用仪器 双踪示波器一台,信号发生器一台,直流稳压电源一台,万用表一台。 二、电路设计 1.电路形式讨论 由于电压增益A V =U O /U S =30,采用一级放大电路即可,要求电路工作稳定,采用分压式电流负反馈偏置电路,输入电阻比较大和频率响应比较宽,引入一定的串联负反馈,电路如图。 2.具体电路设计 (1)静态工作点选择 I CQ =2mA,V BQ =3V (选择硅管) (2)晶体管的选择 78) (2 =+=L s i V R R R A β取100, U CEO >V CC =12V,I CM >2I CQ =4mA, P CM >I CQ V CC =24mW, f T >1.5βf H =75MHz 选择9014:U CEO >20V,I CM >100mA, P CM >300mW,f T >80MHz,Cb'c<2.5pF (3)元件参数的计算 R E =(V BQ -0.7)/I CQ ≈1.2k Ω I BQ =I CQ /β=20μA 则 Ω== k I V R BQ BQ B 15102,R B2=15k Ω Ω=-= k I V V R BQ BQ CC B 45101,取标称值47k Ω Ω≈++=k mA I mV r EQ be 6.1) (26) 1(300β, 取R F =10Ω.则Ω=++=k R r R F be i 16.2)1('β Ω==k R R R R i B B i 12.2////'21,取A V =40, 电子科技大学成都学院 (微电子技术系) 实验报告书 课程名称:电路原理图设计及Hspice 学号: 姓名: 教师: 年06月15日 实验一基本电路图的Hspice仿真 实验时间:同组人员: 一、实验目的 1.学习用Cadence软件画电路图。 2.用Cadence软件导出所需的电路仿真网表。 3.对反相器电路进行仿真,研究该反相器电路的特点。 二、实验仪器设备 Hspice软件、Cadence软件、服务器、电脑 三、实验原理和内容 激励源:直流源、交流小信号源。 瞬态源:正弦、脉冲、指数、分线段性和单频调频源等几种形式。 分析类型:分析类型语句由定义电路分析类型的描述语句和一些控制语句组成,如直流分析(.OP)、交流小信号分析(.AC)、瞬态分析(.TRAN)等分析语句,以及初始状态设置(.IC)、选择项设置(.OPTIONS)等控制语句。这类语句以一个“.”开头,故也称为点语句。其位置可以在标题语句之间的任何地方,习惯上写在电路描述语句之后。 基本原理:(1)当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|> |UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD,即输出电平. (2)当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0<|UTP|,因此V2截止。此时UO=UOL≈0,即输出为低电平。可见,CMOS反相器实现了逻辑非的功能. 四、实验步骤 1.打开Cadence软件,画出CMOS反相器电路图,导出反相器的HSPICE网表文件。 2.修改网表,仿真出图。 3.修改网表,做电路的瞬态仿真,观察输出变化,观察波形,并做说明。 4.对5个首尾连接的反相器组成的振荡器进行波形仿真。 5.分析仿真结果,得出结论。 五、实验数据 输入输出仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos *.tran 200p 20n .dc vin 0 5 1m sweep data=w .print v(1) v(2) .param wp=10u wn=10u .data w wp wn 10u 10u 20u 10u 40u 10u 40u 5u .enddata vcc vcc 0 5 vin in 0 2.5 *pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=wp m2 out in 0 0 nch l=1u w=wn .alter vcc vcc 0 3 .end 图像: 瞬态仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos .tran 200p 20n .print tran v(1) v(2) vcc vcc 0 5 vin in 0 2.5 pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=20u 集成电路设计实习Integrated Circuits Design Labs I t t d Ci it D i L b 单元实验三(第二次课) 模拟电路单元实验-差分放大器版图设计 2007-2008 Institute of Microelectronics Peking University 实验内容、实验目的、时间安排 z实验内容: z完成差分放大器的版图 z完成验证:DRC、LVS、后仿真 z目的: z掌握模拟集成电路单元模块的版图设计方法 z时间安排: z一次课完成差分放大器的版图与验证 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page1 实验步骤 1.完成上节课设计放大器对应的版图 对版图进行、检查 2.DRC LVS 3.创建后仿真电路 44.后仿真(进度慢的同学可只选做部分分析) z DC分析:直流功耗等 z AC分析:增益、GBW、PM z Tran分析:建立时间、瞬态功耗等 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page2 Display Option z Layout->Options ->Display z请按左图操作 Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page3 由Schematic创建Layout z Schematic->Tools->Design Synthesis->Layout XL->弹出窗口 ->Create New->OK >选择Create New>OK z Virtuoso XL->Design->Gen From Source->弹出窗口 z选择所有Pin z设置Pin的Layer z Update Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page4 用LC 元件设计L 型的阻抗匹配网络 一 设计要求: 用分立LC 设计一个L 型阻抗匹配网络,使阻抗为Z s =25-j*15 Ohm 的信号源与阻抗为Z L =100-j*25 Ohm 的负载匹配,频率为50Mhz 。(L 节匹配网络) 二 阻抗匹配的原理 用两个电抗元件设计L 型的匹配网络,应该是匹配网络设计中最简单的一种, 但仅适用于较小的频率和电路尺寸的范围,即L 型的匹配网络有其局限性 在RF 理论中,微波电路和系统的设计(包括天线,雷达等),不管是无源电路还是有源电路,都必须考虑他们的阻抗匹配(impedance matching )问题。阻抗匹配网络是设计微波电路和系统时采用最多的电路元件。其根本原因是微波电路传输的是电磁波,不匹配会引起严重的反射,致使严重损耗。所以在设计时,设计一个好的阻抗匹配网络是非常重要的。阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。对于不同特性的电路,匹配条件是不一样的。在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。 根据最大功率传输定理,要获得信号源端到负载端的最大传输功率,需要满足信号源阻抗与负载阻抗互为共轭的条件,即L L S S iX R iX R +=+。若电路为纯电阻电路则0==L S X X , 即L S R R =。而此定理表现在高频电路上,则是表示无反射波,即反射系数为0.值得注意的是,要得到最佳效率的能量传输并不需要负载匹配,此条件只是避免能量从负载端到信号源端形成反射的必要条件。当RL=Rs 时可获得最大输出功率,此时为阻抗匹配状态。无论负载电阻大于还是小于信号源内阻,都不可能使负载获得最大功率,且两个电阻值偏差越大,输出功率越小. 阻抗匹配是无线电技术中常见的一种工作状态,它反映了输人电路与输出电路之间的功率传输关系。当电路实现阻抗匹配时,将获得最大的功率传输。反之,当电路阻抗失配时,不但得不到最大的功率传输,还可能对电路产生损害。阻抗匹配常见于各级放大电路之间、放大器与负载之间、测量仪器与被测电路之间、天线与接收机或发信机与天线之间,等等。 为了使信号和能量有效地传输,必须使电路工作在阻抗匹配状态,即信号源或功率源的内阻等于电路的输人阻抗,电路的输出阻抗等于负载的阻抗。在一般的输人、输出电路中常含有电阻、电容和电感元件,由它们所组成的电路称为电抗电路,其中只含有电阻的电路称为纯电阻电路。 L 型匹配网络通常不用于高频电路中,以及如果在窄带射频中选用了L 型匹配网络,也应该注意他的匹配禁区,在这个禁区中,无法在任意负载阻抗中和源阻抗之间实现预期的匹配,即应选择恰当的L 型匹配网络以避开其匹配禁区。 三 设计过程 1新建ADS 工程,新建原理图,在元件面板列表中选择“simulation S--param ”在原理图中 数字电路与系统设计实验报告 学院: 班级: 姓名: 实验一基本逻辑门电路实验 一、实验目的 1、掌握TTL与非门、与或非门和异或门输入与输出之间的逻辑关系。 2、熟悉TTL中、小规模集成电路的外型、管脚和使用方法。 二、实验设备 1、二输入四与非门74LS00 1片 2、二输入四或非门74LS02 1片 3、二输入四异或门74LS86 1片 三、实验内容 1、测试二输入四与非门74LS00一个与非门的输入和输出之间的逻辑关系。 2、测试二输入四或非门74LS02一个或非门的输入和输出之间的逻辑关系。 3、测试二输入四异或门74LS86一个异或门的输入和输出之间的逻辑关系。 四、实验方法 1、将器件的引脚7与实验台的“地(GND)”连接,将器件的引脚14与实验台的十5V连接。 2、用实验台的电平开关输出作为被测器件的输入。拨动开关,则改变器件的输入电平。 3、将被测器件的输出引脚与实验台上的电平指示灯(LED)连接。指示灯亮表示输出低电平(逻辑为0),指示灯灭表示输出高电平(逻辑为1)。 五、实验过程 1、测试74LS00逻辑关系 (1)接线图(图中K1、K2接电平开关输出端,LED0是电平指示灯) (2)真值表 2、测试74LS02逻辑关系 (1)接线图 (2)真值表 3、测试74LS86逻辑关系接线图 (1)接线图 (2)真值表 六、实验结论与体会 实验是要求实践能力的。在做实验的整个过程中,我们首先要学会独立思考,出现问题按照老师所给的步骤逐步检查,一般会检查处问题所在。实在检查不出来,可以请老师和同学帮忙。 实验二逻辑门控制电路实验 一、实验目的 1、掌握基本逻辑门的功能及验证方法。 2、掌握逻辑门多余输入端的处理方法。 3、学习分析基本的逻辑门电路的工作原理。 二、实验设备 1、基于CPLD的数字电路实验系统。 2、计算机。 三、实验内容 1、用与非门和异或门安装给定的电路。 2、检验它的真值表,说明其功能。 四、实验方法 按电路图在Quartus II上搭建电路,编译,下载到实验板上进行验证。 五、实验过程 1、用3个三输入端与非门IC芯片74LS10安装如图所示的电路。 从实验台上的时钟脉冲输出端口选择两个不同频率(约7khz和14khz)的脉冲信号分别加到X0和X1端。对应B和S端数字信号的所有可能组合,观察并画出输出端的波形,并由此得出S和B(及/B)的功能。 2、实验得真值表 实验报告 课程名称:集成电路原理 实验名称: CMOS模拟集成电路设计与仿真 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年6月12日 2017年6月12日 微电子与固体电子学院 一、实验名称:CMOS模拟集成电路设计与仿真 二、实验学时:4 三、实验原理 1、转换速率(SR):也称压摆率,单位是V/μs。运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。 2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。 3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。 4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。 5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。 6、输出电压摆幅:一般指输出电压最大值和最小值的差。 图 1两级共源CMOS运放电路图 实验所用原理图如图1所示。图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。M6、M7为二级放大电路,Cc为引入的米勒补偿电容。 其中主要技术指标与电路的电气参数及几何尺寸的关系: 转换速率:SR=I5 I I 第一级增益:I I1=?I I2 I II2+I II4=?2I I1 I5(I2+I3) 第二级增益:I I2=?I I6 I II6+I II7=?2I I6 I6(I6+I7) 单位增益带宽:GB=I I2 I I 输出级极点:I2=?I I6 I I 零点:I1=I I6 I I 正CMR:I II,III=I II?√5 I3 ?|I II3|(III)+I II1,III 负CMR:I II,III=√I5 I1+I II5,饱和 +I II1,III+I II 饱和电压:I II,饱和=√2I II I 功耗:I IIII=(I8+I5+I7)(I II+I II) 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。 五、实验内容 1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。 2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。 3、电路性能的优化与器件参数调试,要求达到预定的技术指标。 ADS软件学习及阻抗匹配电路的仿真设计 专业班级:电子信息科学与技术3班 姓名: 学号: 一、实验内容 用分立LC设计一个L型阻抗匹配网络,实现负载阻抗(30+j*40)(欧姆) 到50(欧姆)的匹配,频率为1GHz。 二、设计原理 阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态,它反映了输入电路与输出电路之间的功率传输关系。 要实现最大的功率传输,必须使负载阻抗与源阻抗匹配,这不仅仅是为了减小功率损耗,还具有其他功能,如减小噪声干扰、提高功率容量和提高频率响应的线性度等。通常认为,匹配网络的用途就是实现阻抗变换,就是将给定的阻抗值变换成其他更合适的阻抗值。 基本阻抗匹配理论: ——(1) ——(2),由(1)与(2)可得:——(3) 当RL=Rs时可获得最大输出功率,此时为阻抗匹配状态。无论负载电阻大于还是小于信号源内阻,都不可能使负载获得最大功率,且两个电阻值偏差越大,输出功率越小。 广义阻抗匹配: 阻抗匹配概念可以推广到交流电路,当负载阻抗ZL与信号源阻抗Zs共轭时,即ZL=Zs,能够实现功率的最大传输,称作共轭匹配或广义阻抗匹配。 如果负载阻抗不满足共轭匹配条件,就要在负载和信号源之间加一个阻抗变换网络N,将负载阻抗变换为信号源阻抗的共轭,实现阻抗匹配。 三设计过程 1、新建ADS工程,新建原理图。在元件面板列表中选择“Simulation S--param”,在原理图中放两个Term和一个S-Parameters控件,分别把Term1设置成Z=5Oohm,Term2 设置成Z=30+j*40ohm,双击S-Parameters控件,弹出设置对话框,分别把Start设置成10MHz,Stop设置成2GHz,Step-size设置成1MHz。 2、在原理图里加入Smith Chart Matching 控件,并设置相关的频率和输入输出阻抗等参数。 3、连接电路。 4、在原理图设计窗口,执行菜单命令tools->Smith Chart,弹出Smart Component,选择“Update SmartComponent from Smith Chart Utility”,单击“OK”。 5、设置Freq=0.05GHz,Z0=50ohm。单击DefineSource /load Network terminations 按钮,弹出“Network Terminations”对话框,设置源和负载阻抗,然后依次单击“Apply”和“OK”。 6、采用LC分立器件匹配。 7、单击“Build ADS Circuit”按钮,即可以生成相应的电路。 8、进行仿真,要求其显示S(1,1)和S(2,1)单位为dB的曲线。 模拟cmos集成电路设计实验 实验要求: 设计一个单级放大器和一个两级运算放大器。单级放大器设计在课堂检查,两级运算放大器设计需要于学期结束前,提交一份实验报告。实验报告包括以下几部分内容: 1、电路结构分析及公式推导 (例如如何根据指标确定端口电压及宽长比) 2、电路设计步骤 3、仿真测试图 (需包含瞬态、直流和交流仿真图) 4、给出每个MOS管的宽长比 (做成表格形式,并在旁边附上电路图,与电路图一一对应) 5、实验心得和小结 单级放大器设计指标 两级放大器设计指标 实验操作步骤: a.安装Xmanager b.打开Xmanager中的Xstart c.在Xstart中输入服务器地址、账号和密码 Host:202.38.81.119 Protocol: SSH Username/password: 学号(大写)/ 学号@567& (大写)Command : Linux type 2 然后点击run运行。会弹出xterm窗口。 修改密码 输入passwd,先输入当前密码,然后再输入两遍新密码。 注意密码不会显示出来。 d.设置服务器节点 用浏览器登陆http://202.38.81.119/ganglia/,查看机器负载情况,尽量选择负载轻的机器登陆,(注:mgt和rack01不要选取) 选择节点,在xterm中输入 ssh –X c01n?? (X为大写,??为节点名) 如选择13号节点,则输入ssh –X c01n13 e.文件夹管理 通常在主目录中,不同工艺库建立相应的文件夹,便于管理。本实验采用SMIC40nm工艺,所以在主目录新建SMIC40文件夹。 在xterm中,输入mkdir SMIC40 然后进入新建的SMIC40文件夹, 在xterm中,输入cd SMIC40. 电工电子综合试验——数字计时器实验报告 学号: 姓名: 学院: 专业:通信工程 目录 一,实验目的及要求 二,设计容简介 四,电路工作原理简述 三,设计电路总体原理框图五,各单元电路原理及逻辑设计 1. 脉冲发生电路 2. 计时电路和显示电路 3. 报时电路 4. 较分电路 六引脚图及真值表 七收获体会及建议 八设计参考资料 一,实验目的及要求 1,掌握常见集成电路实现单元电路的设计过程。 2,了解各单元再次组合新单元的方法。 3,应用所学知识设计可以实现00’00”—59’59”的可整点报时的数字计时器 二,设计容简介: 1,设计实现信号源的单元电路。( KHz F Hz F Hz F Hz F1 4 , 500 3 , 2 2 , 1 1≈ ≈ ≈ ≈ ) 2,设计实现00’00”—59’59”计时器单元电路。 3,设计实现快速校分单元电路。含防抖动电路(开关k1,频率F2,校分时秒计时器停止)。4,加入任意时刻复位单元电路(开关K2)。 5,设计实现整点报时单元电路(产生59’53”,59’55”,59’57”,三低音频率F3,59’59”一高音频率F4)。 三,设计电路总体原理框图 设计框图: 四,电路工作原理简述 电路由振荡器电路、分频器、计数器、译码器、显示器、校时电路和报时电路组成。振荡器产生的脉冲信号经过十二级分频器作为秒脉冲,秒脉冲送入计数器,计数器通过“时”、“分”、“秒”译码器显示时间,将分秒计时器分开,加入快速校分电路与防抖动电路,并控制秒计 时器停止工作。较分电路实现对“分”上数值的控制,而不受秒十位是否进位的影响,在60进制控制上加入任意时刻复位电路。报时电路通过1kHz或2kHz的信号和要报时的时间信号进行“与”的运算来实现的顶点报时的,通过两个不同频率的脉冲信号使得在不同的时间发出不同的声响。 五,各单元电路原理及逻辑设计 (1)脉冲发生电路 脉冲信号发生电路是危机时期提供技术脉冲,此次实验要求产生1HZ的脉冲信号。用NE555集成电路和CD4040构成。555定时器用来构成多谐振荡器,CD4040产生几种频率为后面电路使用。 实验电路如下(自激多谐振荡电路,周期矩形波发生电路) 震荡周期T=0.695(R1+2*R2)C,其中R1=1KΩ,R2=3KΩ,C=0.047uf,计算T=228.67*10-6 s ,f=4373.4Hz产生的脉冲频率为4KHz,脉冲信号发生电路 和CD4040连接成如图所示的电路,则从Q12输出端可以得到212分频信号F1,即1Hz的信号,Q11可以得到F2即2Hz的信号提供给D触发器CP和校分信号,Q3输出分频信号500Hz,Q2输出1KHz提供给报时电路 二,秒计时电路 应用CD4518及74LS00可以设计该电路,CD4518是异步清零,所以在进行分和秒十位计数的时候,需要进行清零,而在个位计数的时候不需要清零。所以Cr2=2QcQb,Cr4=4Qc4QB。当秒个位为1001时,秒十位要实现进位,此时需要EN2=1Qd,同理分的个位时钟EN3=2Qc,分十位时钟端EN4=3Qd。因此,六十进制计数器逻辑电路如下图所示 中山大学数字电路与逻辑设计实验报告 院系信息科学与技术学院学号 专业计算机科学类实验人 3、实验题目:AU(Arithmetic Unit,算术单元)设计。 实验内容: 设计一个半加半减器,输入为 S、A、B,其中S为功能选择口。当S=0时,输出A+B及进位;当S=1时,输出A-B及借位。 S 输入1 输入2 输出Y 进/借位Cn 0 A B A+B 进位 1 A B A-B 借位 利用三种方法实现。 (1)利用卡诺图简化后只使用门电路实现。 (2)使用74LS138实现。 (3)使用74LS151实现,可分两次单独记录和/差结果、进位借位结果或使用两块74LS151实现。 实验分析: 真值表 S A B Y Cn 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 0 0 1 0 1 1 1 1 1 0 1 0 1 1 1 0 0 卡诺图: S AB 0 1 通过卡诺图可得:Y=A B+A B 00 01 11 100 0 1 1 0 0 1 1 S AB 0 1 00 Cn=AB S +A BS 01 =(A S +A S)B 11 10 实验设计: (1)利用门电路实现。 ①利用74LS197的八进制输出端Q1、Q2、Q3作为B 、A 、S 的输入。 ②用异或门74LS86实现输出Y. ③用74LS86实现A ⊕B ,再用74LS08与B 实现与门。 (2)利用74LS138实现 ①将74LS197的Q3、Q2、Q1作为74LS138的S2、S1、S0输入,G2A 、G2B 接低电平,G1接高电平。 ②将74LS138的Y1、Y5、Y2、Y6利用74LS20实现与非门作为输出Y 。 ③ 将74LS138的Y3、Y5利用74LS00实现与非门作为输出Cn 。 0 0 0 1 1 0 0 0 北京邮电大学 实验报告 实验题目:cmos模拟集成电路实验 姓名:何明枢 班级:2013211207 班内序号:19 学号:2013211007 指导老师:韩可 日期:2016 年 1 月16 日星期六 目录 实验一:共源级放大器性能分析 (1) 一、实验目的 (1) 二、实验内容 (1) 三、实验结果 (1) 四、实验结果分析 (3) 实验二:差分放大器设计 (4) 一、实验目的 (4) 二、实验要求 (4) 三、实验原理 (4) 四、实验结果 (5) 五、思考题 (6) 实验三:电流源负载差分放大器设计 (7) 一、实验目的 (7) 二、实验内容 (7) 三、差分放大器的设计方法 (7) 四、实验原理 (7) 五、实验结果 (9) 六、实验分析 (10) 实验五:共源共栅电流镜设计 (11) 一、实验目的 (11) 二、实验题目及要求 (11) 三、实验内容 (11) 四、实验原理 (11) 五、实验结果 (14) 六、电路工作状态分析 (15) 实验六:两级运算放大器设计 (17) 一、实验目的 (17) 二、实验要求 (17) 三、实验内容 (17) 四、实验原理 (21) 五、实验结果 (23) 六、思考题 (24) 七、实验结果分析 (24) 实验总结与体会 (26) 一、实验中遇到的的问题 (26) 二、实验体会 (26) 三、对课程的一些建议 (27) 实验一:共源级放大器性能分析 一、实验目的 1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法; 2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真; 3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线; 4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响 二、实验内容 1、启动synopsys,建立库及Cellview文件。 2、输入共源级放大器电路图。 3、设置仿真环境。 4、仿真并查看仿真结果,绘制曲线。 三、实验结果 1、实验电路图 电子电路设计实验报告 电子线路专题实验Ⅱ 一、实验要求: 1. 认真阅读学习系统线路及相关资料 2. 将键盘阵列定义为0. 1. 2------ E. F,编程实现将键盘输入内容显示在LCD显示器上。 3. 编程实现将日历、时钟显示在LED显示屏上(注意仔细阅读PCF8563资料),日历、时钟轮回显示。 4. 利用D/A转换通道(下行通道)实现锯齿波发生器;输出(1~5V)固定电压转换成(4~20mA)电流。 5. 利用A/D转换通道(上行通道)实现数据采集,将采集信号显示在LED屏上。程序要求分别具有平均值滤波、中值滤波和滑动滤波功能。 6. 将按键阵列定义成与16个语音段对应,编写程序,实现按键播放不同的语音段。 二、实验设计思路: 本次实验用c语言实现,主要包括LCD,LED,AD,DA,日历芯片,测温传感芯片。受到嵌入式系统实验的启发,将LCD,LED,I2C总线协议,键盘扫描模块接口写成一个文件库(放在library文件夹下),尽量做到调用时与底层硬件无关。通过调用库文件中的函数,实现代码的重用性。键盘,LCD的代码由于与嵌入式实验具有相通之处,因此可将高层的函数(与底层硬件无关的函数)方便地移植过来。 三、实验设计: 1.矩阵键盘扫描模块 4×4的矩阵键盘,通过扫描可得到按下键的行列值,将行列值转换为相应的对应数字0~F。函数GetKey()实现获得按键的键值。对于键盘模块对于对按键的键值识别主要是通过两次扫描而取得。对于第一次扫描,给四行键全部赋予1,然后读回键盘值,对于第二次扫描,逐行为键盘送1,每次送1后再读回键盘值,若非零,说明此行有键按下,最终确定键值。 通过调用GetKey函数构造GetChar()函数,实现获取键盘字符(’0’~’F’)的功能。 1、 CMOS analog circuit design by P.E.ALLEN 评定:理论性90 实用性70 编写 100 精彩内容:运放的设计流程、比较器、 开关电容 这本书在国内非常流行,中文版也 翻译的很好,是很多人的入门教材。 建议大家读影印版,因为ic 领域 的绝大部分文献是以英文写成的。 如果你只能读中文版,你的学习资料 将非常有限。笔者对这本书的评价 并不高,认为该书理论有余,实用性 不足,在内容的安排上也有不妥的地 方,比如没有安排专门的章节讲述反 馈,在小信号的计算方面也没有巧方法。本书最精彩的部分应该就是运放的设计流程了。这是领域里非常重要的问题,像Allen 教授这样将设计流程一步一步表述出来在其他书里是没有的。这正体现了Allen 教授的治学风格:苛求理论的完整性系统性。但是,作为一项工程技术,最关键的是要解决问题,是能够拿出一套实用的经济的保险的方案。所以,读者会发现,看完最后一章关于ADC/DAC 的内容,似乎是面面俱到,几种结构的ADC 都提到了,但是当读者想要根据需求选择并设计一种ADC/DAC 时,却无从下手。书中关于比较器的内容也很精彩,也体现了Allen 教授求全的风格。不过,正好其它教科书里对比较器的系统讲述较少,该书正好弥补了这一缺陷。Allen 教授是开关电容电路和滤波器电路的专家。书中的相关章节很适合作为开关电容电路的入门教材。该书的排版、图表等书籍编写方面的工作也做的很好。像Allen 这样的理论派教授不管在那所大学里,大概都会很快的获得晋升吧。另外,Allen 教授的学生Rincon Moca 教授写的关于LDO 的书非常详尽,值得一读。 2、 CMOS Circuit Design Layout and Simulation CMOS Mixed-Signal Circuit Design by R.J.Baker 评定:理论性80 实用性100 编写80 精彩内容:数据转换器的建模和测量、hspice 网表这本书的风格和Allen 的书刚好相反: 理论的系统性不强,但是极为实用,甚至给出 大量的电路仿真网表和hspice 仿真图线。 这本书的中文版翻译的也很好。最近出了第二 版,翻译人员换了,不知道翻译的水平如何。 不过,第二版好贵啊~~ Baker 教授在工业界 的实战经验丰富,曾经参加过多年的军方项目 的研发,接收器,锁相环,数据转换器,DRAM 等曾设计过。所以,书中的内容几乎了包含 了数字、模拟的所有重要电路,Baker 教授 实验一 匹配电路的设计与仿真 一、实验目的 1、掌握阻抗匹配、共轭匹配的原理 2、掌握集总元件L 型阻抗抗匹配网络的匹配机理 3、掌握并(串)联单支节调配器、λ/4阻抗变换器匹配机理 4、了解ADS 软件的主要功能特点 5、掌握Smith 原图的构成及在阻抗匹配中的应用 6、了解微带线的基本结构 二、实验原理 1、基本阻抗匹配理论 , 信号源的输出功率取决于Us 、Rs 和RL 。在信号源给定的情况下,输出功率取决于负载电阻与信号源内阻之比k 。当RL=Rs 时可获得最大输出功率,此时为阻抗匹配状态。无论负载电阻大于还是小于信号源内阻,都不可能使负载获得最大功率,且两个电阻值偏差越大,输出功率越小。 2、共轭匹配: 当 ,源输出功率最大,称作共轭匹配。 若 ,需在负载和信号源之间加一个阻抗变换网络 ,将负载阻抗变换为信号源阻抗的共轭。 L L s s L o R R R U R I P 2 22 ) (+==s s i s L R U P kR R 2,==i o P k k P 2)1(+ =* g L Z Z =* g L Z Z ≠ 3、阻抗匹配: ①λ/4阻抗变换器 ②并(串)联单支节调配器 调配原理:y(左)=1=y(右)+jb ,y(右)=1-jb 调配过程: a). yL 于A点 b)等ρ圆顺时针旋转与g=1 的圆交于B点,旋转长度为d(接入点的位置) c)B点的虚部为jb,并联支节的电纳为-jb,则匹配 d)–jb于E点,则支线电长度为l(短路线) 三、实验内容 1、设计L型阻抗匹配网络,使Zs=(25-j*25) Ohm信号源与ZL=(100-j*25) Ohm 的负载匹配,频率为500MHz。 2、设计微带单枝节短截线匹配网络,使ZS=(55-j*40) Ohm信号源与ZL=(30+j*50) Ohm的负载匹配,频中心频率为1.5GHz 四、实验步骤 I、L型匹配网络 1、打开ADS 2、新建一个工程,长度单位选毫米 3、选“No help needed”,然后单击“finish” 4、在元件库列表中选择“Simulating-S Param”,单击 SP和 Term 放入两个Term和一个SP控件 5、双击Term1,Term2端口,弹出对话框改变参数 6、双击S-Paraemters控件,弹出对话框改变参数 7、选择元件库“Smith Chart Matching”,单击在原理图中添加“DA_SmithChart 数字电子设计 客房呼叫器 学院:通化师范学院 专业班级:物理系11级二班 小组成员:黄琳杰呼永建王继洋马一剑周建伟刘启宇郑伟清李楠楠 指导老师:李东康 时间:2013年12月3日 前言 物理实验是人们根据科学研究的目的,利用仪器设备人为地控制模拟自然现象,排除干扰突出主要因素,在有利条件下观察研究自然规律的活动。 因此,物理实验可以简化纯化研究对象和过程,可以强化研究条件,可以控制或再现和重复物理过程。物理实验有多种类型在本次试验设计中,我们采取模拟试验的方式来用数字电路设计餐厅客房服务器。 设计目的与要求 1.选用十个开关模拟某餐厅的十个包房,应用数字电路设计一个客房呼叫器。 2.用数码管显示呼叫服务的客房编号。 发挥部分:试想一下,若存在十个以上包房应如何设计。 总体框图 设计想法 1. 整体设计思路:根据对设计要求的分析,可以将整个呼叫器的逻辑电路划分为编码器,代码转换电路和数码显示电路三个部分。 2. 整体设计流程: a 编码器将客房给出的开关输入编成对应的二进制代码 b 代码转换电路将编码器输出的编码转换为七段显示译码器在显示时所要求的输入代码。 c 用一个数码管显示呼叫信号的号码。 选择器件 74ls147优先编码器管脚图和功能真值表 优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的输入信号进行编码,常用的集成优先编码器IC有10线-4线,8线-3线两种。10线-4线优先编码器常见的型号为54/74LS147,54/74147, 3线-8线优先编码器常见的型号为54/74148,54/74LS148. 下面我们以74ls147为例介绍优先编码器功能如图一所示 第九个脚NC为空74ls147优先编码器有九个输入端和四个输出端,某个输入端为0,代表输入某个十进制数当九个输入端全为1时,代表输入的十进制数为0. 74ls147优先编码器的输入端和输出端都是低电平有效即某一个输入端低电平0时,四个输出端就以低电平0的输出其对应的8421 BCD编码,当九个输入全为1时,4个输出也全为1呆比啊输入十进制数0的8421 BCD编码输出。 北京邮电大学数字电路实验报告 北京邮电大学 数字电路与逻辑设计实验 实验报告 实验名称:QuartusII原理图输入 法设计与实现 学院:北京邮电大学 班级: 姓名: 学号: 一.实验名称和实验任务要求 实验名称:QuartusII原理图输入法设计与实现 实验目的:⑴熟悉用QuartusII原理图输入法进行电路设计和仿真。 ⑵掌握QuartusII图形模块单元的生成与调用; ⑶熟悉实验板的使用。 实验任务要求:⑴掌握QuartusII的基础上,利用QuartusII用逻辑 门设计实现一个半加器,生成新的半加器图像模 块。 ⑵用实验内容(1)中生成的半加器模块以及逻辑门 实现一个全加器,仿真验证其功能,并能下载到实 验板上进行测试,要求用拨码开关设定输入信号, 发光二级管显示输出信号。 ⑶用3线—8线译码器(74L138)和逻辑门实现要求 的函数:CBA F+ C + =,仿真验证其 + B C B A A A B C 功能,,并能下载到实验板上进行测试,要求用拨 码开关设定输入信号,发光二级管显示输出信号。二.设计思路和过程 半加器的设计实现过程:⑴半加器的应有两个输入值,两个输出值。 a表示加数,b表示被加数,s表示半加和, co表示向高位的进位。 ⑵由数字电路与逻辑设计理论知识可知b a s ⊕=;b a co ?= 选择两个逻辑门:异或门和与门。a,b 为异或门和与门的输入,S 为异或门的输出,C 为与门的输出。 (3)利用QuartusII 仿真实现其逻辑功能,并生成新的半加器图形模块单元。 (4)下载到电路板,并检验是否正确。 全加器的设计实现过程:⑴全加器能够由两个半加器和一个或门构成。全加器有三个输入值a,b,ci ,两个输 出值s,co :a 为被加数,b 为加数,ci 为低 位向高位的进位。 ⑵全加器的逻辑表 示式为: c b a s ⊕⊕= b a ci b a co ?+?⊕=)(经典模拟、数字电路设计

电路原理图设计及Hspice实验报告

3.2模拟集成电路设计-差分放大器版图

ADS仿真作业用LC元件设计L型的阻抗匹配网络

数字电路与系统设计实验报告

电子科技大学集成电路原理实验CMOS模拟集成电路设计与仿真王向展

(完整版)ADS软件学习及阻抗匹配电路的仿真设计

模拟cmos集成电路设计实验

电子电工综合实验报告

中山大学数字电路与逻辑设计实验报告

cmos模拟集成电路设计实验报告

电子电路设计实验报告

模拟集成电路设计经典教材

实验一匹配电路的设计仿真

数字电路模拟设计实验报告

北京邮电大学数字电路实验报告