题5.14已知维持阻塞结构d触发器各输入端的电压波形

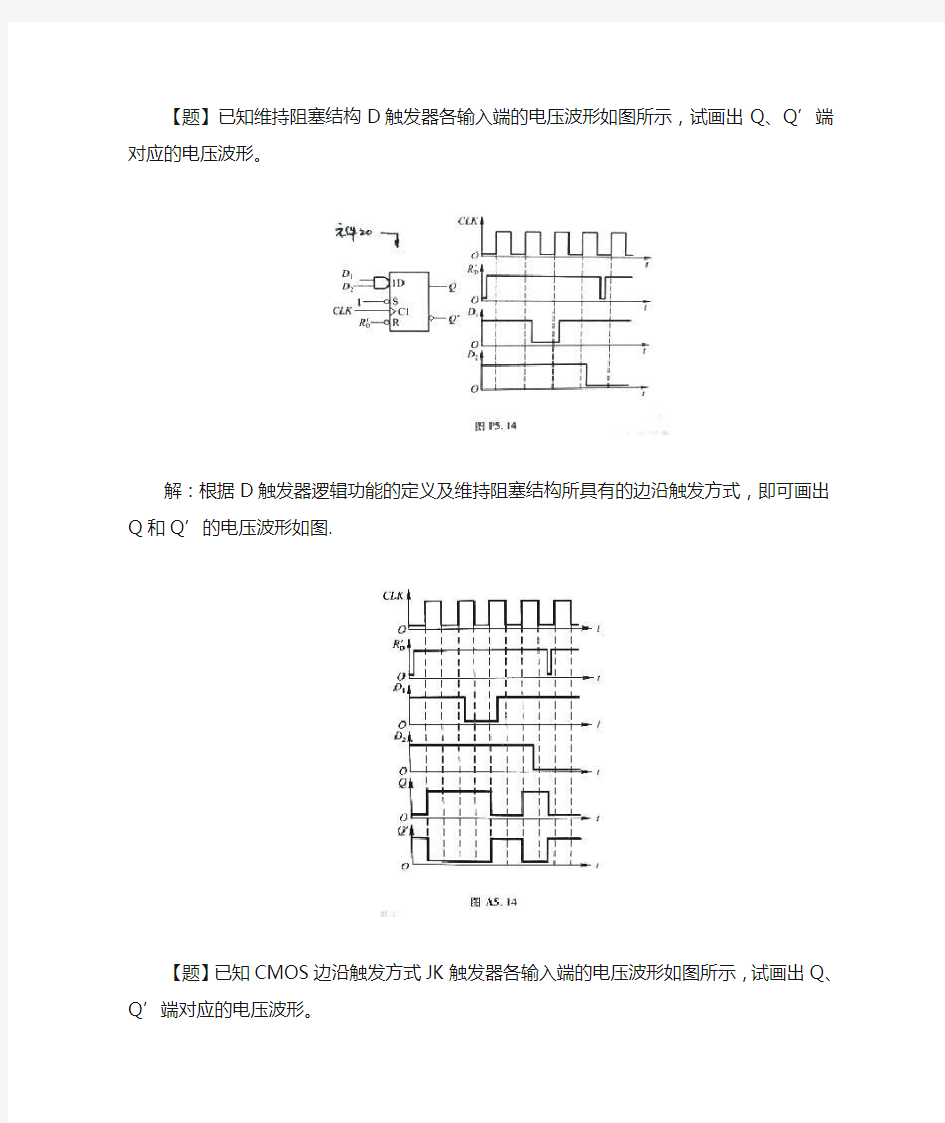

【题】已知维持阻塞结构D触发器各输入端的电压波形如图所示,试画出Q、Q’端对应的电压波形。

解:根据D触发器逻辑功能的定义及维持阻塞结构所具有的边沿触发方式,即可画出Q 和Q’的电压波形如图.

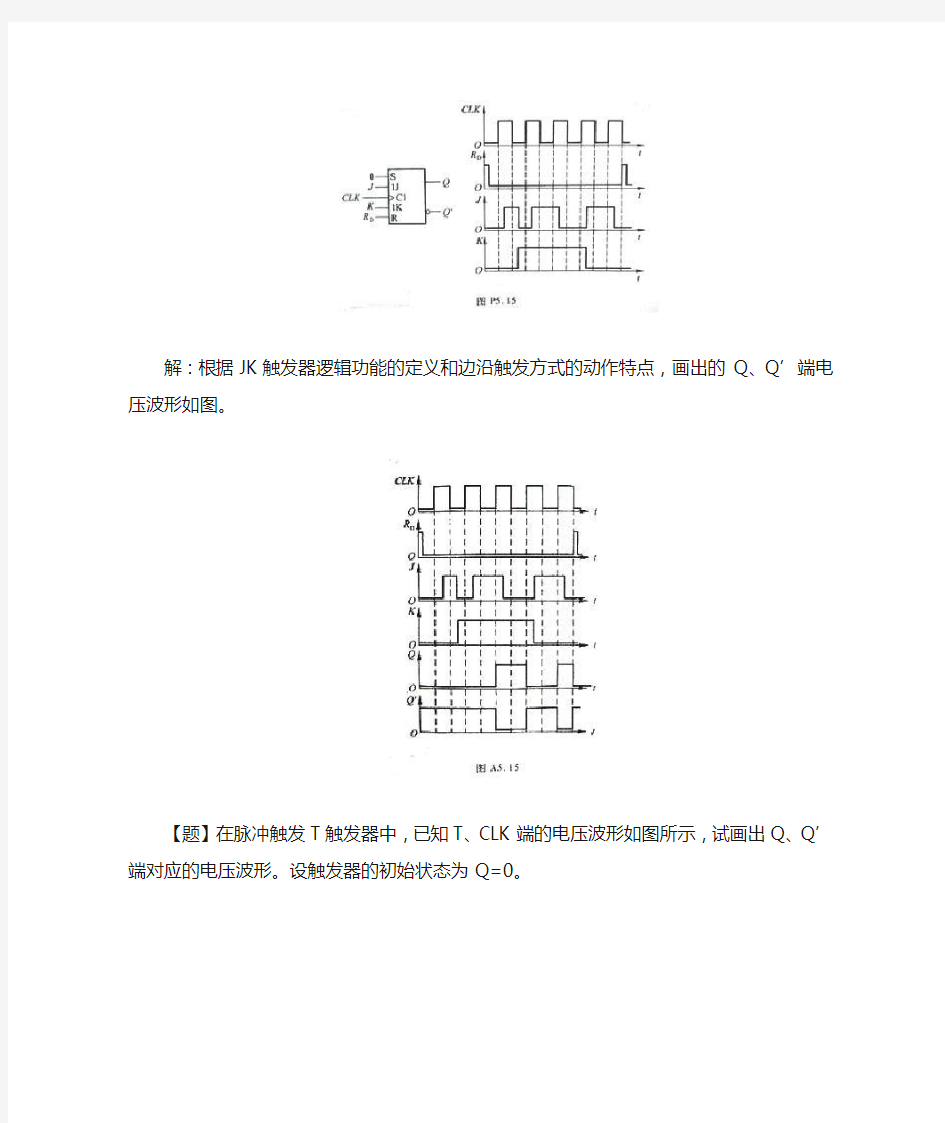

【题】已知CMOS边沿触发方式JK触发器各输入端的电压波形如图所示,试画出Q、Q’端对应的电压波形。

解:根据JK触发器逻辑功能的定义和边沿触发方式的动作特点,画出的Q、Q’端电压波形如图。

【题】在脉冲触发T触发器中,已知T、CLK端的电压波形如图所示,试画出Q、Q’端对应的电压波形。设触发器的初始状态为Q=0。

解:根据T触发器逻辑功能的定义以及脉冲触发方式的动作特点,画出的Q、Q’端电压波形如图.。

【题】在图的主从结构JK触发器电路中,已知CLK和输入信号T的电压波形如图所示,试画出触发器输出端Q和Q’的电压波形。设触发器的起始状态为Q=0。

解:将JK触发器的J和K接在一起作为输入端,就得到了T触发器。按照T触发器的逻辑功能和脉冲触发方式的动作特点,就到得到了图中Q、Q’端的电压波形。

【题】设图各触发器的初始状态皆为Q=0,试画出在CLK信号连续作用下各触发器输出端的电压波形。

解:根据每个触发器的逻辑功能和触发方式,画出输出端Q的电压波形,如图。

【题】试写出图(a)中各电路的次态函数(即Q1*、Q2*、Q3*、Q4*与现态和输入变量之间的函数式),并画出在图(b)给定信号的作用下Q1、Q2、Q3、Q4的电压波形。假定各触发器的初始状态均为Q=0。

解:由图中可写出触发器FF1的驱动方程为

J1=A’;K1=B’

将它们代入JK触发器的特性方程Q*=JQ’+K’Q,得到

Q1*=A’Q1’+BQ1

触发器FF2的驱动方程为

S2=AB;R2=(A+B)’

将它们代入SR触发器的特性方程Q*=S+R’Q,得到

Q2*=AB+(A+B)Q2

触发器FF3的驱动方程为T3=A☉B,将它代入T触发器的特性方程Q*=TQ’+T’Q=T⊕Q,于是得到

Q3*=(A☉B)⊕Q3

触发器FF4的驱动方程为D4=A⊕B,将它代入D触发器的特性方程Q*=D,得到

Q4*=A⊕B

从t=0开始依次根据每个触发器的状态方程求出它们在CLK信号作用后应有的次态,就可以画出Q1、Q2、Q3、Q4在一系列CLK信号作用下的电压波形了,如图所示。

【题】在图电路中已知输入信号u I的电压波形如图所示,试画出与之对应的输出电压u O的波形。触发器为维持阻塞结构,初始状态为Q=0。(提示:应考虑触发器和异或门的传输延迟时间。)

解:当u I=0、Q=0时,异或门的输出u O等于0。u I变为高电平以后,u O也变成高电平。因为u O也是触发器的时钟输入端,所以经过触发器的延迟时间后,Q端被置成1状态;再经过异或门的传输延迟时间,u O回到低电平。因此,u O高电平持续时间等于触发器的传输延迟时间与异或门的传输延迟时间之和。

u I从高电平跳变至低电平以后电路的工作过程与上述过程类似。这样就得到了图的u O电压波形。

【题】在图所示的主从JK触发器电路中,CLK和A的电压波形如图中所示,试画出Q 端对应的电压波形。设触发器的初始状态为Q=0。

解:在CLK=1期间主从JK触发器的主触发器接收输入信号。若此期间出现A=1的信号,则主触发器被置1,在CLK变为低电平后,从触发器随之被置1,使输出为Q=1。而当CLK 回到高电平以后与非门的输出变为低电平,于是又通过异步置0端R将触发器置0。这样我们就得到了图的波形图。

利用这个电路可以监视在CLK=1期间A端是否有高电平信号输入。如果A端由高电平输入信号,则Q端给出一个正脉冲;如果A端没有输入信号,则Q端始终为0。

【题】图所示是用CMOS边沿触发器和或非门组成的脉冲分频电路。试画出在一系列CLK 脉冲作用下Q1、Q2和Z端对应的输出电压波形。设触发器的初始状态皆为Q=0。

解:第1个CLK脉冲到来之前D1=1、D2=0,CLK上升沿到达后将两个触发器置成Q1=1、Q2=0。

第2个CLK脉冲到来之前D1=1、D2=1,CLK上升沿到达后Q1=1、Q2=1。

第3个CLK脉冲到来之前D1=0、D2=1,CLK上升沿到达后Q1=0、Q2=1。

但由于Q1的低电平接到了第2个触发器FF2的异步置0端,所以在Q1变为0以后立刻将FF2置0,于是电路回到了起始状态。据此即可画出Q1和Q2的电压波形。

根据Z=(Q1+CLK)’,就能很容易地从Q1和CLK的波形得到了Z的波形了,如图。

【题】图所示是用维持阻塞结构D触发器组成的脉冲分频电路。试画出在一系列CLK 脉冲作用下输出端Y对应的电压波形。设触发器的初始状态均为Q=0。

解:第1个CLK上升沿到达前D1=1,所以CLK上升沿到达后Q1=1。第1个CLK下降沿到达前D2=0,所以CLK下降沿到达后Q2=0。

第2个CLK上升沿到达前D1=0,所以CLK上升沿到达后Q1=0。第2个CLK下降沿到达前D2=1,所以CLK下降沿到达后Q2=1。

第3个CLK上升沿到达前D1=0,所以CLK上升沿到达后Q1=0。第3个CLK下降沿到达前D2=0,所以CLK下降沿到达后Q2=0,电路又回到了开始的状态。Q1、Q2的电压波形如图所示。

因为Y=(Q1+ Q2)’,所以从Q1和Q2的波形就可以画出Y的波形了,如图所示。

【题】试画出图所示的电路输出端Y、Z的电压波形。输入信号A和CLK的电压波形如图中所示。设触发器的初始状态均为Q=0。

解:根据给定的CLK和A的电压波形以及边沿触发D触发器的工作特性即可画出Q1端的电压波形。因为两个触发器之间是按移位寄存器接法连接的,所以将Q1的波形右移一个CLK时间,就是Q2的电压波形。由图可知

Z=(Q1 Q2’)’;Y=(Q1’ Q2)’

从得到的Q1、Q2的波形就得到了图中Z和Y的电压波形。

【题】试画出图电路输出端Q2的电压波形。输入信号A和CLK的电压波形与上题相同。假定触发器为主从结构,初始状态均为Q=0。

解:当A变为高电平时FF1的主触发器被置1,A回到低电平后从触发器置1,使Q1=1。随后到来的CLK下降沿使FF2置1,Q2’变为低电平,于是又将FF1置0。.下一个CLK信号到达后,FF2被置0,电路又返回开始时的Q1=Q2=0状态。由此画得Q2的电压波形如图所示。

【题】试画出图电路在一系列CLK信号作用下Q1、Q2、Q3端输出电压的波形。触发器均为边沿触发方式,初始状态为Q=0。

解:因为FF1和FF2接成了T触发器的T=1状态,所以每当它们的时钟信号下降沿到来时都要翻转,即Q*=Q’。据此便可画出Q1、Q2的波形了。而FF3的输入为J=K=Q2,所以当Q2=1时,FF3有时钟信号到达则状态翻转;而Q2=0时即使有时钟信号到来,FF3状态也不改

变。FF3的时钟信号取自Q1,由此便可画出Q3的电压波形了。Q1、Q2、Q3的电压波形如图所示。

【题】试画出图电路在图中所示CLK、R’D信号作用下Q1、Q2、Q3的输出电压波形,并说明Q1、Q2、Q3输出信号的频率与CLK信号频率之间的关系。

解:由于每个触发器都接成了D=Q’,所以Q*=Q’,即每次时钟到来后都要翻转,这样就得到了图的波形图。由图可见,若输入的CLK频率为f o,则Q1、Q2、Q3输出脉冲的频率依次为1/2 f o、1/4 f o、1/8 f o。

【题】设计一个4人抢答逻辑电路。具体要求如下:

(1)每个参赛者控制一个按钮,用按动按钮发出抢答信号。

(2)竞赛主持人另有一个按钮,用于将电路复位。

(3)竞赛开始后,先按动按钮者将对应的一个发光二极管点亮,此后其他3人再按动按钮对电路不起作用。

解:见图。图中A、B、C、D四个按钮各由一名参赛者控制,按钮J由主持人控制。

当A、B、C、D任何一个按钮首先按下时,对应的触发器被置1,这个触发器的Q’端随之变为低电平,将与非门G封锁,其余的触发器不再有CLK信号输入,不可能置1了。