实验2-全加器原理图设计

实验2 全加器原理图设计

实验目的

1.掌握在Quartus II利用原理图设计半加器电路的方法;

2.掌握元件的调用方法和顶层文件的设计;

3.掌握全加器原理图的制作;

4.复习原理图文件建立、编辑、编译、保存的操作,复习软件仿真的方法。

实验步骤

(1)打开QuartusII,新建一个原理图文件,文件名为h_adder.bdf,保存在文件夹adder 中。

(2)半加器的电路为:

在图形文件中添加元件,在路径.. \altera\quartus90\libraries\primitives\logic中,调入and2、not、xnor,在路径.. \altera\quartus90\libraries\primitives\pins中调入输入和输出端口,连接好元件。

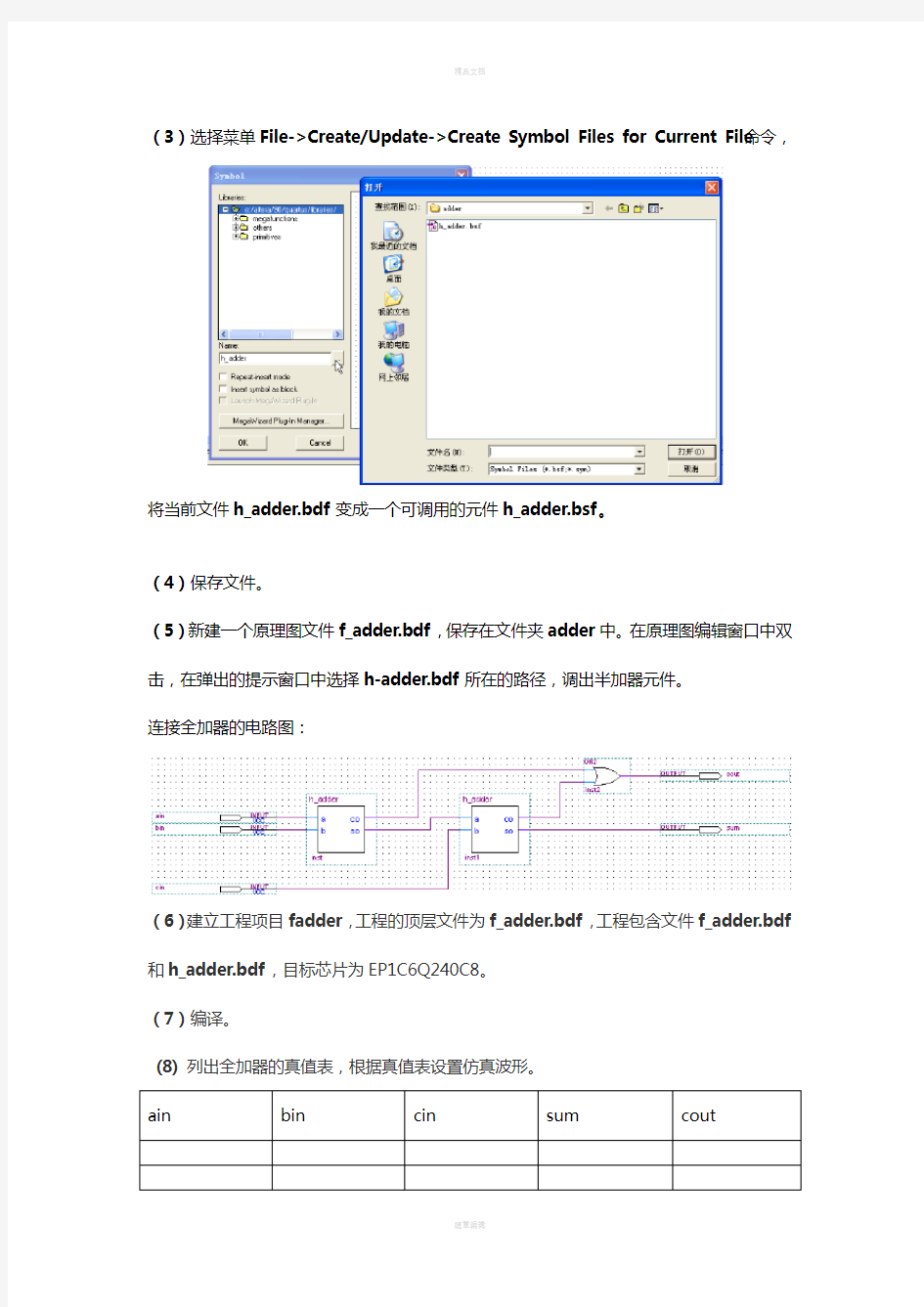

(3)选择菜单File->Create/Update->Create Symbol Files for Current File命令,

将当前文件h_adder.bdf变成一个可调用的元件h_adder.bsf。

(4)保存文件。

(5)新建一个原理图文件f_adder.bdf,保存在文件夹adder中。在原理图编辑窗口中双击,在弹出的提示窗口中选择h-adder.bdf所在的路径,调出半加器元件。

连接全加器的电路图:

(6)建立工程项目fadder,工程的顶层文件为f_adder.bdf,工程包含文件f_adder.bdf 和h_adder.bdf,目标芯片为EP1C6Q240C8。

(7)编译。

(8) 列出全加器的真值表,根据真值表设置仿真波形。

ain bin cin sum cout

(9)仿真,画出波形图,要标明时间刻度。

相关主题