同步时钟电路设计及其与异步时钟信号交互的问题

1同步时钟电路设计及其与异步时钟信号交互的问题

现在以及过去的四分之一世纪中,实际上大部分数字设计都是基于使用全局时钟信号,以时钟信号控制系统中所有部件的操作。它的优点显而易见:在一个理想的全局时钟的控制下,只要电路的各个功能环节都实现了时序收敛,整个电路就可以可靠的实现预定的功能。

1.1同步电路设计

1.1.1同步电路的定义

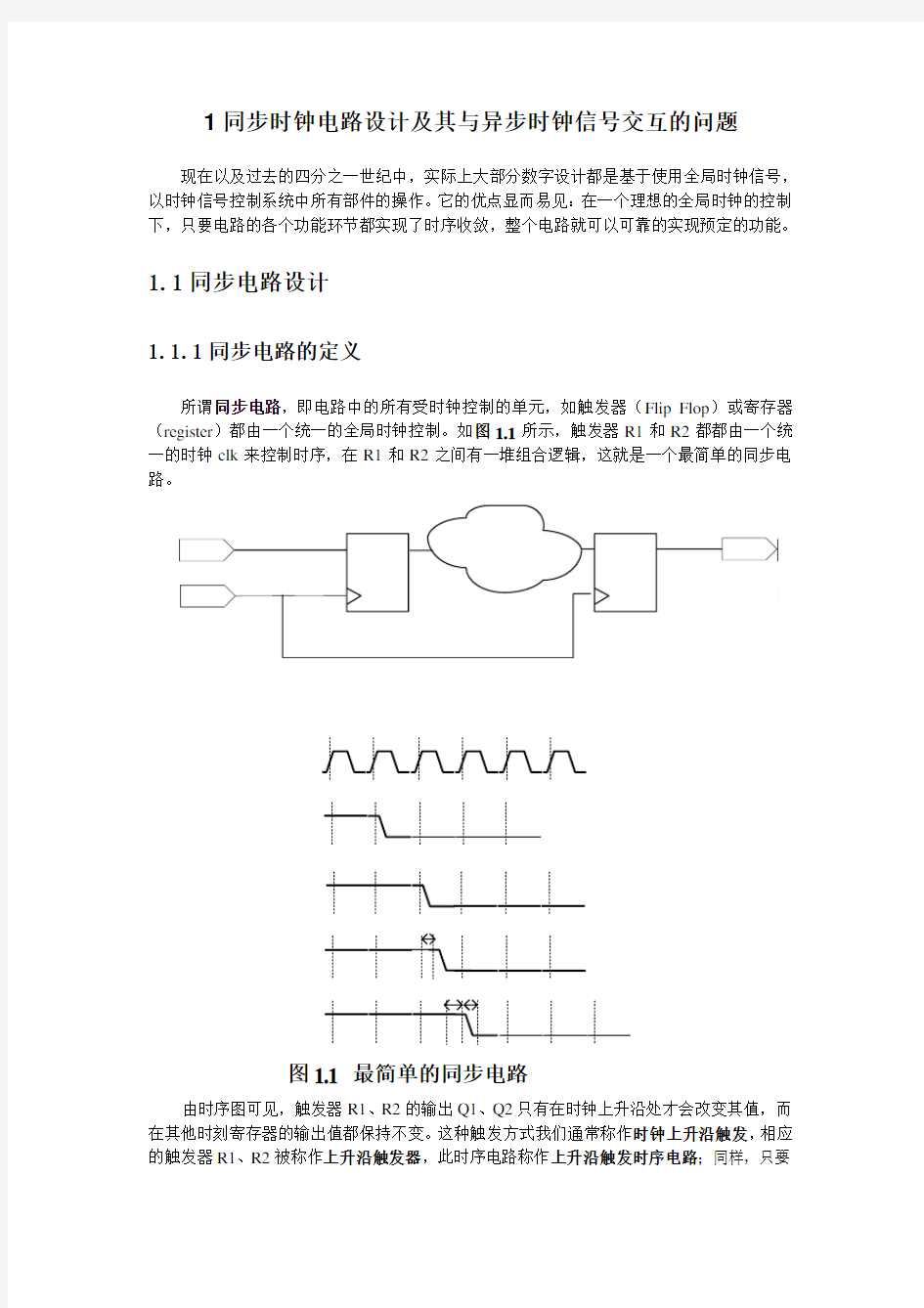

所谓同步电路,即电路中的所有受时钟控制的单元,如触发器(Flip Flop)或寄存器(register)都由一个统一的全局时钟控制。如图1.1所示,触发器R1和R2都都由一个统一的时钟clk来控制时序,在R1和R2之间有一堆组合逻辑,这就是一个最简单的同步电路。

图1.1 最简单的同步电路

由时序图可见,触发器R1、R2的输出Q1、Q2只有在时钟上升沿处才会改变其值,而在其他时刻寄存器的输出值都保持不变。这种触发方式我们通常称作时钟上升沿触发,相应的触发器R1、R2被称作上升沿触发器,此时序电路称作上升沿触发时序电路;同样,只要

我们选用不同触发方式的触发器组成电路,我们可以得到下降沿触发时序电路。

在实际电路设计中,根据不同的需求,我们既可以用到上升沿触发的时序电路,又可以用到下降沿触发的时序电路,甚至两者兼用。不过一般情况下在同步电路设计中,我们推荐使用统一的触发方式。

1.1.2 同步电路的时序收敛问题

时序电路的一个首要问题就是时序收敛问题。

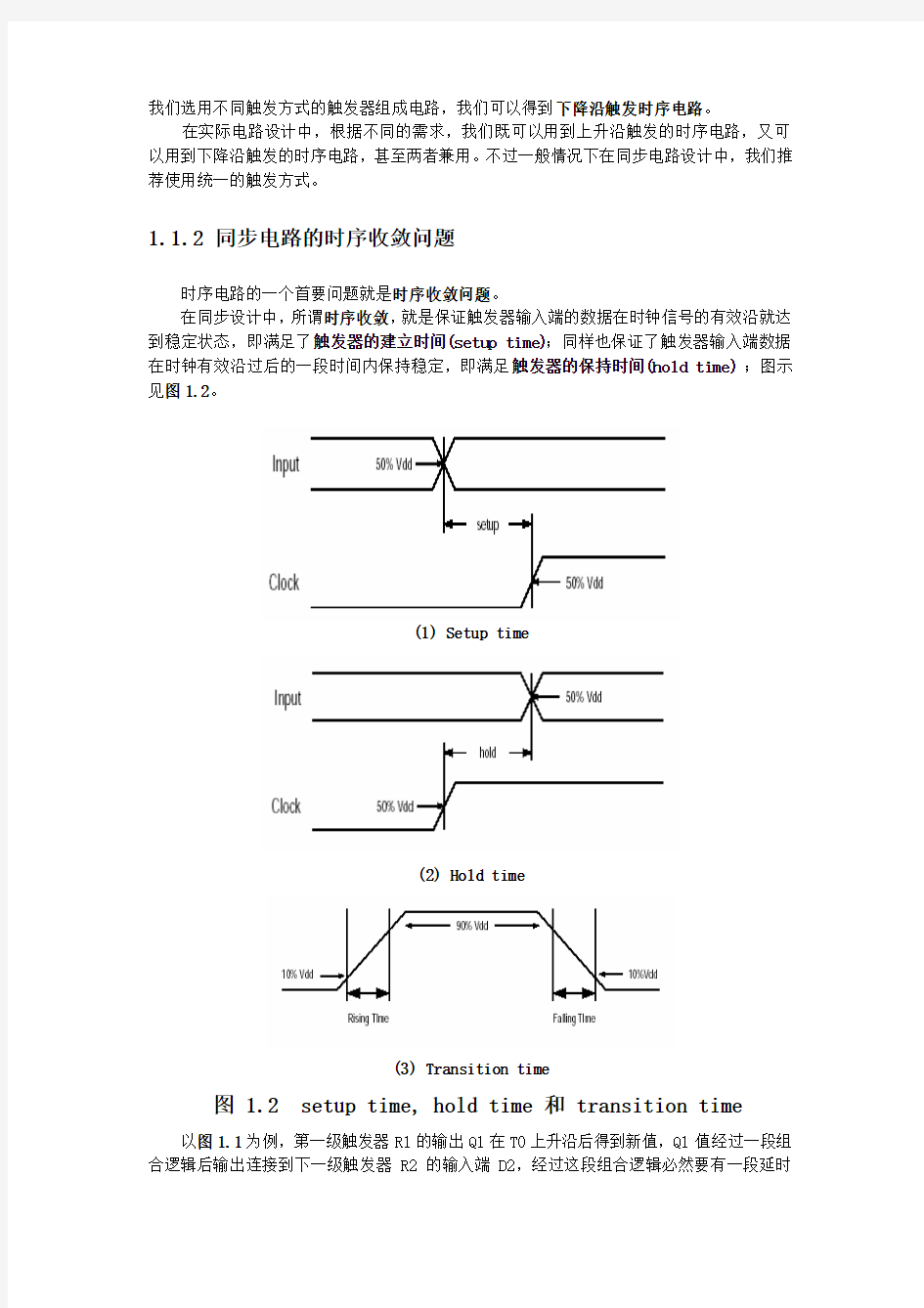

在同步设计中,所谓时序收敛,就是保证触发器输入端的数据在时钟信号的有效沿就达到稳定状态,即满足了触发器的建立时间(setup time);同样也保证了触发器输入端数据在时钟有效沿过后的一段时间内保持稳定,即满足触发器的保持时间(hold time) ;图示见图1.2。

(1) Setup time

(2) Hold time

(3) Transition time

图 1.2 setup time, hold time 和 transition time

以图1.1为例,第一级触发器R1的输出Q1在T0上升沿后得到新值,Q1值经过一段组合逻辑后输出连接到下一级触发器R2的输入端D2,经过这段组合逻辑必然要有一段延时

T delay输出才能最终稳定,假设触发器R2建立时间为T setup2,所谓满足时序收敛首先要满足时钟周期T 〉= T setup2 + T delay;同样为了保证D2在T1时刻的值能够被无误地锁存,其值必须在一段称作hold time的时间段T hold内保持稳定。这样整个同步电路就可以可靠无误的运行下去。

要保证整个电路时序收敛的确是件复杂而庞大的任务,可幸的是,IC设计发展到今天,设计同步电路时,我们已经可以用RTL来描述同步电路了,这样,在完成了同步电路系统的RTL代码后,只要设定一些合理的约束(如时钟周期值),综合软件DC不但可以完成RTL到物理标准单元库的映射,还可以很方便实现电路的收敛。

进一步地,后端的STA工具,也可以对布局布线之后的电路检查时序收敛情况,以保证同步电路的有效性。

值得一提的是,既然同步电路中控制电路动作的是一个全局的时钟信号,那么这个全局的时钟信号的周期数必须足够大,大到足以让电路中最长的时序路径收敛。在这里,这个最长的时序路径我们可以简单的看成电路中类似图1.1结构的由第一级触发器Q1端经一段组合逻辑到第二级触发器D2延时最长的一段。

1.1.3 同步设计的优点与缺陷

1.1.3.1 同步设计的优点

在功能上,同步电路设计方式具有很多的好处:

z在同步系统中,只要电路系统在时序上完全收敛,电路设计中令人头疼的竞争和冒险现象,得到了有效的避免。

z由于触发器只有在时钟边缘才改变取值,这就很大限度的减少了整个电路受噪声影响的可能。

在工程上,同步电路之所以如此受欢迎,这跟它得到EDA软件的广泛支持不无关系,正如前面提到的综合软件DC和STA工具,正是有了它们,同步设计才能在今天的数字设计中大行其道。

1.1.3.2 同步设计的缺陷

同步设计并不完美,也有一些问题一直困扰着同步设计者。

其中,最为令人头疼的是时钟偏斜问题(clock skew)。

同步设计成功有一个很重要的前提,就是所有信号在同一时钟跳变沿发生动作。但是在芯片或电路上,要做到这一点却不是那么简单。

图1.3 时钟偏斜问题示意图

如果没有经过处理,全局时钟线到达各个时序元件的时钟端的路径就不可能相同,如图1.3所示,clk到达触发器R1 clk1端的路径小于到达触发器R2 clk2端的路径。这样就得到图 1.3所示的时钟波形。我们称这种时钟到达时间在空间上的差别叫做时钟偏斜(clock skew)。

时钟偏斜造成的后果是非常严重的,试想如果clk2和clk1的时钟信号的偏差足够大,它可能会造成整个同步电路发生同步失败。

除了时钟偏斜,同步电路还受到时钟抖动(clock Jitter)的影响,,所谓时钟抖动指的是,芯片某一给定点上时钟周期的暂歇性变化,即时钟周期在不同的时间端可能长短不一。

有关时钟偏斜和时钟抖动的细节详见参考文献[1]。

不过,如今的EDA软件对以上提到的同步电路的缺陷都给予了很好的解决。

比方说,时钟偏斜可以通过用Astro长时钟树的方法解决。而且现在的EDA软件在施加约束的时候也都考虑了时钟抖动等问题。

由此,更能感到EDA软件对同步电路设计的推动作用。

1.1.4 同步电路设计与全异步电路设计

提到同步电路设计,就不能不谈全异步电路设计。

全异步设计跟同步设计最大的不同就是它的电路中所有操作的定时不是通过时钟来实现的。

在同步电路中,在一个全局时钟的控制之下,所有的时序单元在同一上升沿发生动作,前一级的触发器把当前值传递给下一级触发器;而后在下一个时钟跳变沿,时序单元再次同时发生动作,下一级触发器再把它在上一时钟沿得到的钱一级触发器的输出值传递给它的下一级触发器……如此循环下去,就在电路上实现了操作的定时。

在全异步电路中,电路中基本单元的值可以在任意时刻发生跳变,如图1.4是将时钟clk1控制下的电路输出连接到时钟clk2控制的电路的示例。虽然它不是完全意义上的异步电路,但是也可以说明问题。D2的输入端的数据值的跳变并不是在clk2的控制之下,它可能在时钟clk2的任意时间点发生跳变。

图1.4 异步电路示意图

由此可见,在全异步设计中,原来同步设计的避免竞争冒险现象、减少噪声影响的优点就都没有了。不但如此,要实现异步电路模块之间的交互只能通过复杂的握手原理。

而且目前所有的EDA软件都是基于同步设计思想,在如今动辄百万门的设计规模下,很难想象没了EDA软件,设计工作如何进行。

看起来异步设计似乎一无是处,但事实上跟同步电路相比异步电路还是有它的优点的:在同步设计中必须维持一个全局的时钟到整个电路的时序元件的时钟端,随着如今电路规模的指数级增长,维持这个全局时钟高速翻转的功耗实际上已经成了芯片系统功耗的很大一部分。在低功耗设计越来越得到IC设计者关注的今天,无需全局时钟的异步设计再一次得到了他们的关注。

此外由于同步设计中必须保证整个系统的时序收敛,这就可能因为某个小环节的速度而影响到整个系统的时钟频率的提升,这在人们对芯片处理能力需求越来越高的今天的确时有发生。

因此,随着技术的进步,也许某一天全异步设计也会在如今的商用芯片上占据很大的一席天地。

1.2异步时钟信号交互的问题及其RTL解决

1.2.1介绍

如前一节所述,在ASIC设计中,我们通常采用的是同步时钟的设计方法:在一个理想的全局时钟的控制下,只要电路的各个环节都实现了时序收敛,整个电路就可以可靠的实现预定的功能。这看起来很理想,但是,实际上,用一个统一的时钟来设计一个系统或一块SOC的思想是不可能。

在现实中,无论是一个系统或一块soc中,总是会存在一些低速的设备,跟cpu或core 相比它们运行在一个较低的频率上。以PC的北桥芯片为例,它需要负责CPU和内存、显卡及南桥芯片的数据交换,CPU是工作在自己的数GHz的频率,它跟北桥芯片通信是基于自己的远远高于PCI总线的前端总线,内存、显卡和南桥芯片则是工作在的数百兆的频率上,因此北桥芯片一个重要功能就是处理好不同时钟原信号的同步问题。同样,在SOC中,让一些诸如UART、SSI之类低速设备工作在系统总线的高速时钟频率下,既不实际,也造成不必要的功耗浪费。

在应用中,就算强行让所有的设备或模块都工作在同一时钟频率下,也会使为了满足最慢设备或模块的速度而使系统不得不工作在相对较低的频率下,这样显然降低了系统性能。

由此可见,在实际中,完全采用同步的设计方法,既不现实也不经济。异步与同步设计在整个系统或SOC中不可避免的会采用到。

值得注意的是,这里所谓的异步设计并不是前一节所说的IC设计中的全异步设计方法,这里的异步设计针对的是对工作在不同时钟频率下同步电路之间交互问题的处理。

1.2.2 首要问题 :亚稳态

在同步设计中,只要设计中的所有路径满足了时序收敛,整个同步电路就可以可靠无误的运行下去,这些都是同步设计本身所能保证的——都可以通过EDA工具做到。

但是,在包含多个时钟的同步设计中,我们却不能保证这一点。

1.2.2.1 亚稳态现象揭秘及危害

为了说明这个问题,首先介绍几个约定俗成的术语

通常,我们把两个或多个彼此不同频率的时钟称为不同时钟;把两个彼此上升沿不对齐的时钟称作彼此异步时钟,两个不同的时钟不一定是异步时钟,因为他们可能是来自同一参考时钟的分频,两者的相在理论上是严格对齐的;将处于某个时钟控制下的信号或模块称作在工作在某个时钟域下;将处在异步时钟的模块简单说成工作在异步时钟域。

异步时钟域的信号之间不可避免地需要交互,一般的,我们把需要传输到一个不同于它所在时钟域的信号相对于目的时钟域称作异步输入信号(或异步信号)。

图 1.5 亚稳态示意图[2]

如图1.5所示,信号adat在aclk时钟域;它相对于bclk异步输入信号;aclk、bclk 称为异步时钟;adat和bdat1工作在不同时钟域下。

因为处在异步时钟域的信号之间缺乏统一的定时机制,它们都会按照自己所在时钟控制下改变取值,而且每个信号在改变取值的时候都需要一段时间(所谓的transition time,转变时间,见图1.2)。由图1.5的波形图可见,异步信号adat的下降沿正好发生在bclk 时钟的上升沿附近,这样就违反了触发器的建立时间或保持时间,从而第二个触发器锁到一个不确定的值,这个值可以是1,也可以是0,更有可能是一个物理上的不定态x。我们把这种违反了触发器保持或建立时间且使触发器锁存到一个无效电平的状态称作亚稳态现象。

值得一提的是,这个不定态x和逻辑上的x并不是同一个概念。逻辑上的x指当前寄存器的值为未知,我们不知道它是1还是0,但能肯定它在物理上是个有效的电平。而亚稳态中出现的不定态x却不一样了,它实质上是因为触发器输入端的信号的电平没有达到触发器内物理器件的有效电平的噪声容限内,导致由接成反馈回路的两个反向器构成的触发器稳定在非有效电平处的第三稳定点。这就可能使后续的电路对此信号产生不同的解释,后续电路可能会把这个信号解释为正确的电平,也有可能解释错误。

这个解释错误又是什么意思呢?

我们知道在ASIC中所有的标准单元都是使用的CMOS工艺,它是由PMOS和NMOS 的处在不同的导通关断产生高低电平来区别0和1的状态,而且P管和N管不可能同时处于导通状态,见图 1.6。而亚稳态现象的时候却打破了这个原则。最简单的情况,以后续电路为反向器为例,正常的时候D端为1,N管导通,P管关闭,Q端输出为0;当D端为0,P管

导通,N管关闭,Q端为1。现在当D端的输入信号没有达到有效电平的噪声容限的时候(它稳定后的值是1),这时可能会出现P管和N管同时导通或同时截止的现象,这是一个没有定义的状态,既不对应于逻辑0也不对应于逻辑1;更糟的是,这个状态可能会继续往下传播,造成后面的电路的完全功能失效。

D Q

图1.6 CMOS 工艺Inverter

由此可见,异步信号直接连到异步时钟的触发器输入端的时候不但可能传输一个错误的逻辑信号(信号实际值是1但是异步触发器采到的是0,或反之),更有可能使触发器进入亚稳态现象并将其传播下去,造成严重的系统错误,见图1.7。

事实上,由上面的分析也可见到,亚稳态现象除了会造成系统的错误之外,还会造成非常大的系统功耗损失(双管同时导通产生极其大的泄漏电流)。

图 1.7 亚稳态信号的传播[2]

1.2.2.2 亚稳态问题的解决及其RTL实现

事实上,由于如今的ASIC都是在超深亚微米的工艺下制成的,电路中的线与线之间不

可避免存在串扰,而亚稳态状态在微小噪声的作用下就可能偏离此状,因此亚稳态现象在现实电路中维持的时间实际上可以说微乎其微。

而且根据Jan M.Rabaey在《数字集成电路设计透视》第一版影印版P534-538中分析得出,只要在采到异步信号后等待足够长的时间,处在亚稳态的触发器就会回复到一个有效的电平状态上去。而这个延时通常通过在采样异步信号的触发器后再加入一级触发器来实现,也就是说,异步信号只有在经过目的时钟域的两级触发器采样后,才会对目的时钟域的后续电路起作用。这样的由双触发器构成的异步信号采样逻辑被称作同步器(synchronizer)。

图1.8 亚稳态现象的解决[2]

由图1.8可见,虽然第一级触发器在采样异步信号的时候可能进入亚稳态,但是经过一个时钟周期的延时,当第二级触发器采样其输出端信号时,它已经回复到一个有效电平的稳定状态,从而第二级触发器不会再出现亚稳态,从而防止了亚稳态在整个电路中的传播。

其RTL实现如下:

module synchronizer (

bclk, //目的时钟,跟aclk异步时钟

reset_b, //全局异步复位信号

adat, //异步输入信号,工作在aclk

bdat, //同步器输出

);

input bclk;

input reset_b;

input adapt;

output bdat;

bdat;

wire

bdat1;

reg

bdat2;

reg

always @ (posedge bclk or negedge reset_b)

(reset_b)

if

2’b0;

{bdat2,bdat1}

<=

else

{bdat1,adat};

<=

{bdat2,bdat1}

assign bdat = bdat2;

endmodule

值得注意的是,完全解决亚稳态现象的方法是不存在的。触发器可能正好采到输入信号的变化中点,从此点回复到稳定电平的状态所需要等待的时间为无穷大。这样,第二级触发器同样将采到第一级触发器输出的亚稳态电平而处在亚稳态状态。

但是事实上实际电路的极其小的噪声或环境的变化都会使触发器脱离亚稳态。所以只要满足了足够大小的等待时间,亚稳态问题出现的可能性就可以减小到在工程中可以忽略或接受的地步。

如果系统的工作频率过于高,系统采到亚稳态的本能性就会增大,此时两级触发器构成的同步器不足以解决亚稳态问题,必须通过增加同步器触发器的级数来延长等待时间的方法来解决,带来的代价是异步信号的交互会带来更大的延时。

1.2.3 常见的异步控制信号的同步问题及其RTL实现

从本质上说,亚稳态问题是异步信号连入到目的时钟域固有的问题,它是由同步电路设计的内在机理所造成,正是因为其的不可避免性,可以称它为异步时钟信号交互的物理(或固有的)问题。

在前一节的基础上,我们现在可以撇开亚稳态现象,从逻辑上来考虑一下异步时钟域信号交互所带来的问题。

在这里,我们把异步信号采样到目的时钟域的动作简称为同步。

异步时钟域之间的信号交互无外乎两种类型:控制信号和数据信号。

通常数据信号的同步总是伴随着控制信号的同步,因为我们总是在控制信号的通知下才能知道当前时候数据总线上的数据是否有效。更何况数据的读写总要伴随着读、写、选通等控制信号。因此,在这一节里我们首先谈谈异步控制信号的同步。

1.2.3.1 快时钟同步慢时钟域下的异步控制信号

在这里可能发生的问题是,异步控制信号虽然在自己的慢时钟域内只维持了一个时钟的有效时间,而在快时钟域中,可能已经被采了好几次了。假设这是一个异步读操作请求信号,那么在目的时钟域内,就有可能把这一次读请求误以为是多次读请求。

原始信号RTL处理后

图 1.9 快时钟同步慢时钟信号示意图

如图1.9所示,clk_slow下的两级触发器rd_en_s2f1和rd_en_s2f2构成的同步器同步clk_slow的信号rd_en。图中clk_fst上升沿1处正好跟rd_en的上升时间重合,所以rd_en_s2f 采到的是0而不是1,同样在clk_fst上升沿4处正好又跟rd_en的下降时间重合,所以rd_en_s2f1采到的是1而不是0;因此,在快时钟域clk_fst中,rd_en_s2f一共维持了3个时钟的有效时间,如果不加处理的话,可能clk_fst端的电路会误以为这是三次读操作。

显然,应该在设计上避免这种错误的发生。

这个问题需要在系统定义的时,对接口信号动作的做出规定:

1.跨越不同时钟域的信号只有一个在电路功能上有效的(asserted)电平(1.1)2.此信号有效后,在第二次有效前必须回复到无效的状态(1.2)这两个规定实际上是相辅相成的。以图1.9为例,rd_en为1有效,在一次有效后它回到了无效状态0。

满足了这两点在RTL上,我们可以作相应处理,仍以图1.9的例子。

(

module synchronizer

clk_fst.,

reset_b,

rd_en,

rd_en_s2f

);

input clk_fst;

input reset_b;

input rd_en;

output rd_en_s2f;

wire

rd_en_s2f;

rd_en_s2f1;

reg

rd_en_s2f2;

reg

rd_en_s2f3;

reg

always @ (posedge clk_fst or negedge reset_b)

if (!reset_b)

{rd_en_s2f3,rd_en_s2f2,rd_en_s2f1} <= 3'b111;

else

{rd_en_s2f3,rd_en_s2f2,rd_en_s2f1}<={rd_en_s2f2,rd_en_s2f1,rd_en};

always @ (rd_en_s2f3 or rd_en_s2f2)

case ({rd_en_s2f3,rd_en_s2f2})

2'b01 :

rd_en_s2f <= 1'b1;

default :

rd_en_s2f <= 1'b0;

endcase

这样问题就得到了圆满的解决,解决后的波形见图1.9。

1.2.3.2 慢时钟同步快时钟域下的异步控制信号

慢时钟同步快时钟下的控制信号带来的问题是可能在慢时钟沿的上升沿到来之前,控制信号已经无效,这样就丢失了请求信号,显然造成了功能错误,示意波形见图1.10。

其实还有可能带来更严重的问题,就是在慢时钟临接的两个上升沿的期间,快时钟域下的控制信号可能经过了多次翻转,这样其实就丢掉了数个请求控制信号。

图 1.10慢时钟同步快时钟信号示意图[2]

对待这个问题,其实有两个处理方法:

1.在快速时钟域里面对此控制信号采用保持逻辑。直到将通过异步时钟接受方、的信号反馈后从而确认对方已经收到此有效控制信号才无效此控制信号。

我们称这种同步机制为握手。

其实,异步信号经过反馈保持逻辑之后,就可以按照快时钟同步慢时钟的控制信号的方式来同步此异步信号。

显然在此控制信号也要在逻辑上也满足规定(1.1)和规定(1.2)。

值得一提的是,反馈到快时钟的信号因为已经同步到慢时钟的时钟域,所以它也要需要通过同步器才能在快时钟域里面起作用,具体实现见图1.11。

图1.11握手机制解决慢时钟同步快时钟控制信号原理图[2]

在此只给出快时钟控制信号的产生保持的RTL代码, 代码以图1.11的图示为例。

module adapt_gen (

aclk, //快时钟

reset_b, //系统复位信号

adat, //原始控制信号

abdat2, //从慢时钟域反馈回来的同步控制信号

adat1 //经过保持后的信号输出

);

input aclk;

input reset_b;

input adat;

input abdat2;

output adat1;

reg adat1;

always @ (posedge aclk or negedge reset_b)

(!reset_b)

if

1’b

<=

adat1

else

(abdat2)

if

1’b0;

adat1

<=

else

if (adat)

1’b1;

<=

adat1

endmoudule

我想细心的读者可能已经发现,这种方法其实并不能解决上面提到的控制信号在两个临接的慢速时钟上升沿间多次翻动的问题;事实上,握手机制默认了这种情况在逻辑上并不存在。也就是说在设计的时候,我们必须在逻辑上保证控制信号adat的两次有效时间有个最小值的限制。这个最小值必须大于控制信号整个反馈回路中的时间和异步时钟同步器中第一级触发器恢复到无效值的时间之和。

第二种方法其实可以解决这个限制。

2.在快时钟控制信号产生端增加停时钟的逻辑。

它的思想是这样的,当发现控制信号有效之后,由组合逻辑发出停止时钟的如图1.12所示的stall_b信号(低电平有效)拉平快速时钟的下一个时钟的上升沿。既然时钟都已经停掉了,由触发器输出的控制信号就不会再改变了,这样就可以保证慢速时钟能够采到有效的控制信号。在收到从目的时钟返回的反馈信号之后得知异步时钟已经采到了此控制信号,satll_b信号再会拉高从而恢复快速时钟。

有关停时钟的细节在本书低功耗设计的章节中会有详细叙述,在此就不再赘叙。

仍然以前面rd_en的例子,停时钟的方法应用后的电路图和具体波形见图1.12。

(2)时序图

图1.12 停时钟解决同步的方法以下给出停时钟的stall_b信号产生的RTL代码:

module stall_logic (

rd_en,

rd_en_ack_s2f,

stall_b

);

input rd_en;

input rd_en_ack_s2f;

output stall_b;

stall_b;

wire

always @ (rd_en or rd_en_ack_s2f)

(rd_en_ack_s2f)

if

1’b1;

<=

stall_b

else

if

(rd_en)

<=

1’b0;

stall_b

else

1’b1;

stall_b

<=

endmodule

同样停时钟的方法也要求在设计时使rd_en信号满足规定(1)和(2)。

因为停了时钟,所以显然在慢时钟相邻的两个上升沿间不可能存在多个rd_en有效信号,方法一不能解决的问题这里我们用釜底抽薪的方法解决了。

理论上,rd_en信号的两次有效之间还是有个最小时间的限制。这个限制要满足rd_en 有效的下一个上沿到来之前异步时钟同步器的第一级触发器已经回复到无效状态。只有满足这一点,在异步时钟域端才能把两次不同的异步请求区分开。

在实际应用中,不可能伴随着异步控制信号的同步总是会对应着一系列操作。实际上,快时钟被停的时间会远远大于图中所示的时钟数。

rd_en信号虽然只有在时钟恢复后才能复位,但是我们可以用发出一个rd_en1的信号给异步时钟域,等到接到对方的反馈之后就立刻复位rd_en1,紧接着异步时钟端的同步器的第一级触发器就被复位了,而此时,在逻辑上,可能被停的快时钟还没有被恢复或刚刚恢复,这样在快时钟域内rd_en就不存在那个两次有效间的最短时间的限制,而且异步时钟端也可以区分两次不同的有效信号rd_en了。

事实上,在应用中,实际情况往往如此。

此外控制信号同步后伴随的一些操作的信号必然会具有一些耦合关系,巧妙的利用这些耦合关系可以在没有异步控制信号反馈的情况下达到异步控制信号反馈一样的效果。

最后要说的是,不知道,读者有没有感到疑惑,在第一种方法中我提到目的时钟域的反馈信号再快时钟域中也必须经过同步器才能连入快速时钟域的电路,同步器的正常工作是需要时钟信号的,而此时快速时钟信号已经被停掉了,同步器如何正常工作呢?

解决方法很简单,只要将同步器的时钟信号连到全速时钟上去而不是可关断时钟就行了,在图示中这点可以看地很清楚。

1.2.3.3 未知速度关系时钟域间控制信号的同步

既然不知道两个时钟间的关系,那么前面两节提到的问题就都有可能出现。

如果实际应用中是出现这种情况,我们应该怎么处理呢?

其实,方法在前面已经给出来了。对,就是停时钟的方法。

其实在前一节中谈到慢时钟同步快时钟域的控制信号的时候的处理方法的时候就可以看到解决方法的实质是将其转换为快时钟同步慢时钟的控制信号的方法。由此就可见,两者的处理是相通的。

由前面的分析可以看到,停时钟的方法不但解决了异步信号交互时可能带来的逻辑错误,而且对异步控制信号的限制也是最小的。

结合前两节的内容,读者可以自己详细分析一下未知速度关系下停时钟实现控制信号的同步的波形。

综合以上三小节的分析,可以知道,停时钟加反馈的方法是处理不同速时钟间控制信号最保险且限制最小的方法。

1.2.4 异步时钟域的数据同步及其RTL实现

有了控制信号同步的知识作基础,我们就可以讨论异步时钟域的数据的同步问题了。

1.2.4.1 握手机制

我们通常采用的同步异步数据最简单的方法是基于握手机制的。

这种方法通常用在快时钟采样比它慢很多时钟域下的数据的方法。

它的基础是一位写控制信号的同步。

波形示意如图1.13

图1.13 握手同步异步数据

1.2.4.2.1 简述

显然基于握手机制的数据的同步的方法是最简单的,但是其限制也很大,就是要求被采数据的时钟相对于采样始终必须足够慢,从而确保数据被采到。其实这就是当时控制信号两次有效的时钟沿的最小时钟差的限制。

显然这不能完全满足异步时钟数据交互的应用高速需求。

在这种情况下我们会采用FIFO来解决问题。

简单的说,FIFO是由一个双端口的存储器和一组控制逻辑构成的。

双端口存储器的一个端口用来写memory,而另一个端口用来读memory,读和写可以同时进行,而且读写的时钟可以是完全不相同的时钟(这就符合了我们异步时钟交互的要求)。Memory的读写地址是由后面提到的控制逻辑产生的。

在这里,我们把需要同步的数据端所在时钟域电路的对FIFO的动作称作FIFO写;把目的时钟域电路对FIFO的动作称作FIFO读。

控制逻辑是由读写地址控制指针和FIFO空、满的标志位组成。

一组递增的读写指针是用来实现先写的数据先被读出,即FIFO名字的由来First In First Out。初始时,读写时钟都为0,即指向双端口Memory的同一地址;每一次FIFO写动作都会将数据写入当前写指针对应的存储器地址,然后写指针将会加1,指向一个新的未写的Memory空间;同样每次FIFO读动作,FIFO当前读指针所指的数据将会被读出,然后读指针会加1,指向下一个代读数据的地址空间。这样就实现了数据的先写先读的时序要求,这跟我们异步数据数据同步时前后数据的时序是完全一致的。

FIFO空标志位指示当前FIFO中没有数据未读,此时读写指针值相同;

FIFO空

FIFO满

图1.14 FIFO空/满图示

FIFO满标志位指示当前FIFO已满,不能再写入数据。这是因为任何memory都有大小的限制,此时写指针比读指针小1。

有了这两个标志信号之后,异步时钟读写两端就能实现正确的同步。

因为FIFO完全可以满足时钟没有任何关系的两方间同步,为了区分数据同步的源/目的两端,在这里,我们把读FIFO的一方(同步数据的目的方)称作读者,写FIFO的一方(同步数据的源方)称作写者。

以下是FIFO实现同步的整个过程:

写者需要发送待同步数据到写者时,它首先检查发现FIFO满信号(Full)为无效时,就将数据写到FIFO中,等待读者来读;直到满信号(Full)为有效时,写者停止写动作,等到FIFO满信号(Full)再次无效时,写者恢复将待同步的数据写入FIFO。

同时,读者发现FIFO空信号(Empty)无效后,就开始读FIFO,这样整个同步过程就以读者读到数据宣告成功。

由此可见,借助于FIFO的Full/Empty信号,数据同步就可以准确无误的完成。

但同时这也说明Full/Empty的产生非常关键:

如果Full在FIFO已满的时候没有有效,写者就会继续写FIFO,从而将读者第一个未读的数据给覆盖;

同样如果Empty在FIFO已空的时候没有有效,读者就会继续读FIFO,从而只会得到错误的数据;

显然,这两种情况发生后造成的后果都非常严重。

怎样正确地产生Full/Empty信号呢?在下一节,我们会详细介绍。

综上所述,有了FIFO之后,在同步异步时钟的数据时,电路的行为是这样的:

1.待同步的数据时钟域的会在其写信号的控制之下,将数据写入到FIFO中。

2.目的时钟域在发现空标志位无效后,执行FIFO读动作,读出被异步时钟域写入FIFO 的数据。

3.如果只要同步一个数据那么此时,空标志位再次有效。

4.如果需要同步多个数据,因为FIFO的读写之间可以不受影响的进行,所以待同步 时钟会一直写FIFO,直到所有的需要同步的数据已经写完;而目的时钟域就根据空标志位来判断是否还有异步数据没有同步过来,直到空标志位再次有效标志这次同步完成。

FIFO的结构图如图:

“Wptr & Full control”模块负责产生FIFO写地址wptr和FIFO满信号full;

“Rptr & Empty control”模块负责产生FIFO读地址rptr和FIFO空信号empty;

双端口存储器“Dual Port memory”负责存储暂存的数据。

图1.15 FIFO结构图

1.2.4.2.2问题

看起来在数据同步过程中,我们前面所提到的问题都没有了。

这是解决问题的模型的抽象程度高低给你造成的错觉。

确实,FIFO结构可以有效地解决两个没有任何关系时钟源间数据同步的问题,但是这是以牺牲ASIC中巨大的电路面积的代价为基础的;

更何况,FIFO结构并不可能解决异步时钟的固有的亚稳态问题。只是,亚稳态的问题都被隐藏到FIFO空信号的产生逻辑上了。

要知道当前FIFO是否为空,必然比较读写指针是否相等。

而因为读写指针属于不同的时钟域,两者显然不能直接连到比较器的两端来产生空信号。否则会造成读FIFO的目的时钟域的电路碰到亚稳态现象。

这样就需要将写指针同步到读FIFO的时钟域来,看起来问题又解决了。

可是显然指针是一个多位的信号,从前面的分析我们知道同步多位编码控制信号时,如果编码的多个值同时发生改变时被采到的可能会得到莫名其妙的值,用着这个值来跟读指针比较产生空信号显然是不合适的。

可是我们知道我们正常编码的二进制在加1动作之后不可避免地要有多位数据翻动。

这就要用到格雷码(Gray Code),它的特点是加1操作后,前后两个编码之间只可能有一位数据翻动。

从表1.1可以很直观地看到这一点。

0 000000

1 001001

2 010011

3 011010

4 100110

5 101111

6 110101

7 111100

表1.1 二进制和格雷码的对比

由此可见,通过以下两个途径可以解决FIFO结构中固有的异步时钟亚稳态问题:1.以格雷码编码表示读写指针,用格雷码加法器来实现读写地址的加一动作;

2.在1的基础之上,用同步器将读指针同步到FIFO满标志的产生逻辑,同样用同步器将写指针同步到FIFO空标志的产生逻辑中

由此,给出新的异步FIFO的结构框图,见图1.16:

图1.16 新的FIFO结构图

1.2.4.2.3 FIFO的RTL实现

考虑到整个FIFO设计的过于庞大,以下将只给出格雷码加法器的代码

module graycntr (

clk,

reset_b,

基于某52单片机电子时钟的设计论文设计(纯总汇编语言编写)

编号 单片机课程设计 (2013级) 题目:基于52单片机电子时钟的设计 学院:物理与机电工程学院 专业:电子信息科学与技术 作者姓名:陈??党??杜?? 指导教师:张??职称:教授 完成日期:2016 年7月2日 二〇一六年七月

基于52单片机电子时钟的设计 摘要 本次设计的多功能时钟系统采用STC89C52单片机为核心器件,利用其定时器/计数器定时和记数的原理,结合液晶显示电路、时钟芯片DS1302电路、电源电路以及按键电路来设计计时器。将软硬件有机地结合起来,使得系统能够实现液晶显示,显示有年、月、日、时、分、秒以及星期,还可以设置闹钟和整点报时。其中软件系统采用单片机汇编语言编写程序,包括显示程序、闹钟程序、中断、延时程序,按键消抖程序等,并在keil中调试运行,硬件系统利用PROTEUS 强大的功能来实现,简单且易于观察,在仿真中就可以观察到实际的工作状态。 关键词:STC89C52芯片;时钟芯片DS1302;单片机汇编语言;液晶显示电路

1 设计任务及要求分析 1.1 设计任务:基于单片机的电子时钟设计 1.2 要求: 1.2.1 用LCD液晶作为显示设备 1.2.2 可以分别设定小时、分钟和秒,复位后时间为 00 00 00 1.2.3 能实现日期的设置年、月、日 1.3 扩展要求:如闹钟功能、显示星期、整点音乐报时等 2 系统方案 2.1 系统整体方案的论证 电路原理设计是基于小系统板包括电源电路、复位电路、按键电路、DS1302时钟电路、液晶显示驱动电路、输出控制电路。电源部分是用电池来提供的3v-5v,晶体振荡器采用的是12MHz的石英晶体振荡器。 整个系统用单片机为中央控制器,由单片机执行采集时钟芯片的时间信号并通过显示模块来输出信号及相关的控制功能。时钟芯片产生时钟信号,利用单片机的I/O口传给单片机;并通过I/O口实现LCD的显示。系统设有4个独立式按键可以对时间年、月、日和星期进行调整,还可以设置闹钟。具体如图2.1所示: 图2.1 系统整体框图

时间同步系统的要求

4.3.12时间同步系统的要求 4.3.12.1总的要求 4.3.12.1.1 时间同步系统的构成 1)时间同步系统由一级主时钟和时钟扩展装置组成。 2)一级主时钟用于接收卫星或上游时间基准信号,并为各时间扩展装置提供时间信号。3)一级主时钟与时钟扩展装置均配置时间保持单元,保证在输入信号中断的情况下,依然不间断地提供高精度的输出信号。 4.3.12.1.2时间同步系统的布置 根据本期工程情况,将配置1面主时钟装置屏和2面时钟扩展装置屏。主时钟本体装置屏安装在集控楼内,主时钟屏配置的2台主时钟为整个时间同步系统提供2路冗余的时间基准信号输出。机组保护室和网络继电器室各设1面时钟扩展装置屏,主时钟装置与时钟扩展装置之间采用光纤连接。时间同步系统天线安装在集控楼楼顶上。 4.3.12.1.3时间同步系统的运行条件 1)电源要求 同步时钟装置(一级主时钟和二级扩展)采用两路AC220V电源供电,投标方应配置双电源自动切换装置(美国ASCO 7000系列产品)实现双电源自动切换。 2)工作环境 工作温度: -10~+55℃ 贮存温度: -40~+55℃ 湿度: 5%~95%(不结露)。 所有设备均可放置在无屏蔽、无防静电措施的机房内。 4.3.12.1.4 时间同步系统的电磁兼容性 时间同步系统在集控楼的电磁场环境下能正常工作,符合“GB/T13926-1992 工业过程测量和控制装置的电磁兼容性”中有关规定的要求,并达到Ш级及以上标准。 4.3.12.2功能要求 4.3.12.2.1 时间同步系统配置的主时钟及时间同步信号扩展装置对厂内DCS、SIS、电气控制装置及其他需要时钟同步的设备进行时间同步,并应能提供满足这些设备需要的各种时间同步信号及接口(含接口装置、通讯电缆等设备)。 4.3.12.2.2时间同步系统两台主时钟的时间信号接收单元应能独立接收GPS卫星和我国北斗卫星发送的无线时间信号作为主外部时间基准信号。当某一主时钟的时间接收单元发生故

简易数字钟设计(已仿真)

简易数字钟设计 摘 要 本文针对简易数字钟的设计要求,提出了两种整体设计方案,在比较两个方案的优缺点后,选择了其中较优的一个方案,进行由上而下层次化的设计,先定义和规定各个模块的结构,再对模块内部进行详细设计。详细设计的时候又根据可采用的芯片,分析各芯片是否适合本次设计,选择较合适的芯片进行设计, 最后将设计好的模块组合调试,并最终在EWB 下仿真通过。 关键词 数字钟,EWB ,74LS160,总线,三态门,子电路 一、引言:所谓数字钟,是指利用电子电路构成的计时器。相对机械钟而言,数字钟能达到准确计时,并显示小时、分、秒,同时能对该钟进行调整。在此基础上,还能够实现整点报时,定时报闹等功能。 设计过程采用系统设计的方法,先分析任务,得到系统要求,然后进行总体设计,划分子系统,然后进行详细设计,决定各个功能子系统中的内部电路,最后进行测试。 二、任务分析:能按时钟功能进行小时、分钟、秒计时,并显示时间及调整时间,能整点报时,定点报时,使用4个数码管,能切换显示。 总体设计 本阶段的任务是根据任务要求进行模块划分,提出方案,并进行比较分析,最终找到较优的方案。 方案一、采用异步电路,数据选择器 将时钟信号输给秒模块,秒模块的进位输给分模块,分模块进位输入给时模块,切换的时候使用2选1数据选择器进行切换,电路框图如下: 该方案的优点是模块内部简单,基本不需要额外的电路,但缺点也很明显,该方案结构不清晰,模块间关系混乱,模块外还需使用较多门电路,不利于功能扩充,且使用了异步电路,计数在59的时候,高一级马上进位,故本次设计不采用此方案。 方案二、采用同步电路,总线结构 时钟信号分别加到各个模块,各个模块功能相对独立,框图如下: 显示 切换 秒钟 分钟 小时 控制 1Hz 脉冲信号 闹钟

硬盘录像机服务器时间同步方法

PC、硬盘录像机时间同步设置 一.原理:利用NTP服务实现。NTP服务器【Network Time Protocol(NTP)】是用来使计算机时间同步化的一种协议,它可以使计算机对其服务器或时钟源(如石英钟,GPS 等等)做同步化,它可以提供高精准度的时间校正(LAN上与标准间差小于1毫秒,W AN 上几十毫秒),且可介由加密确认的方式来防止恶毒的协议攻击。 二.如何使局域网内的电脑时钟同步 首先要在互联网上寻找一台或几台专门提供时间服务的电脑(以下称为“主时间服务器”),在百度和Google里搜索一下,时间服务器还是很多的,笔者推荐pool.ntp.org这个地址。其次设置局域网时钟服务器。选择单位中能上外网的一台电脑,让它与主时间服务器同步,然后把它设为局域网内部的时间服务器(以下称为时间服务器),以后局域网内所有电脑依它为准进行时间校对。 最后设置客户端。如果客户机为win2000、XP或Linux系统,不需要安装任何软件。如客户机为Win98系统时要根据时间服务器类型的不同而区别对待:如果时间服务器选用SNTP协议进行时钟同步,则Win98机上需安装一个sntp客户端软件,如时间服务器由Windows电脑通过netbios协议提供,则Win98上也不需要安装任何软件。 三.如何设置时间服务器 以下分Win2000、XP分别介绍,而且只介绍sntp服务的架设。 1.Windows2000、XP做时间服务器 第一步:指定主时间服务器。在DOS里输入“net time /setsntp:pool.ntp.org”,这里我们指定pool.ntp.org是主时间服务器。 第二步:与主时间服务器同步。先关闭windows time服务,再开启该服务。在DOS里输入“net stop w32time”、“net start w32time”。 第三步:设置电脑的Windows time服务的启动方式为自动,在“管理工具”的“服务”界面下完成(xp系统默认是自动)。 注意:这台windows主机不能加入任何域,否则无法启动windows time服务。此时,这台windows电脑已经是互联上主时间服务器的客户了,以后每次电脑启动时,都会自动与主时间服务器校对时间。如果网络不通,电脑也会过45分钟后再次自动校对时间。需要提醒的是电脑的时钟与标准时间误差不能超过12个小时,否则不能自动校对,只有手动校正了。

新型多功能电子闹钟设计毕业设计论文

本科生毕业设计(论文)

毕业设计(论文)原创性声明和使用授权说明 原创性声明 本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。 作者签名:日期: 指导教师签名:日期: 使用授权说明 本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在

不以赢利为目的前提下,学校可以公布论文的部分或全部内容。 作者签名:日期:

2009届 本科毕业设计(论文)资料第一部分毕业论文

(2009届) 本科毕业设计(论文) 新型多功能电子闹钟设计 2009年6月

摘要 本文提出了一种基于AT89C51单片机的新型多功能电子闹钟。通过对设计方案的比较与论证,选择了适合本设计的时钟模块、闹铃模块、温度检测模块、键盘及显示模块、电源模块设计方案。其中实时时钟采用DS12C887实现年月日时分秒等时间信息的采集和闹钟功能;温度检测模块由DS18B20集成温度传感器对现场环境温度进行实时检测;键盘和数码管与ZLG7289连接,通过键盘数码管可方便地校对时钟和设置闹钟时间;用蜂鸣器进行声音指示;采用7805 三端稳压集成芯片稳定输出5V直流电压。通过对AT89C51单片机最小系统的原理分析,结合论文的设计要求,完成了系统流程图及系统程序的设计。 本设计可实现时间显示、闹钟设置、环境温度测量、交直流供电电源等功能。 关键词:单片机,电子闹钟多功能设计,温度检测,交直流供电

时钟同步系统施工方案

时钟同步系统施工方案

施工方案审批表 审核单位:审核意见:审核人: 日期:监理单位:监理意见:监理人: 日期:批准单位:审批意见:审批人: 日期:

目录 一、施工方案综述............................................................................................... - 3 - 二、工程概况及特点........................................................................................... - 4 - 三、施工步骤....................................................................................................... - 5 - 四、风险分析..................................................................................................... - 14 - 五、生产安全及文明施工................................................................................. - 14 - 一、施工方案综述 根据中韩(武汉)石油化工有限公司PLC系统的改造技术要求和我公司对改造要求的理解来编制施工方案。

数字钟电路pcb设计

¥ 摘要 本设计针对数字钟PCB板设计较为复杂的问题,利用国内知名度较高、应用最广泛的电路辅助设计软件protel99se进行了电路板的设计。本设计介绍了各部分电路的构成及准确完成了数字钟PCB电路板的设计。本设计数字钟原理图分析入手,说明了在平台中完成原理图设计,电气检测,网络表生成,PCB设计的基本操作程序。数字钟的主要电路是由电源电路、显示电路、校时电路、晶体振荡电路组成。PCB是电子元器件的支撑体,是电子元器件电气连接的提供者。PCB的设计是以电路原理图为根据,实现电路设计者所需要的功能。优秀的版图设计可以节约生产成本,达到良好的电路性能和散热性能。 关键词:数字钟;PCB;原理图;芯片 — 【

目录 前言 (1) 第一章@ 第二章绪论 (2) 数字钟的研究背景和意义 (2) 数字钟的发展和趋势 (2) 第二章系统电路的绘制 (3) 电路组成方框图 (3) 电路原理图制作 (3) 原理图环境设置 (4) 绘制原理图 (5) $ 电气规则检查及网络表输出 (7) 原理图分析 (10) 晶体振荡器 (10) 分频器 (11) 计数器电路 (12) 显示和译码电路 (12) 电源电路 (13) 第三章电路板PCB设计 (14) , PCB设计规范 (14) PCB设计流程 (17) 输出光绘文件 (21) PCB制件作 (23)

心得体会 (25) 参考文献 (26) 附图 (27) 附表 (28) "

前言 PCB(Printed Circuit Board),中文名称为印制线路板,简称印制板,是电子工业的重要部件之一。几乎每种电子设备,小到电子手表、计算器,大到计算机,通讯电子设备,军用武器系统,只要有集成电路等电子元器件,为了它们之间的电气互连,都要使用印制板。在较大型的电子产品研究过程中,最基本的成功因素是该产品的印制板的设计、文件编制和制造。印制板的设计和制造质量直接影响到整个产品的质量和成本,甚至导致商业竞争的成败。 Protel系列电子设计软件是在EDA行业中,特别是在PCB设计领域具有多年发展历史的设计界软件,由于其功能强大,操作简单实用,近年来成为国内发展最快。 Protel 99已不是单纯的PCB(印制电路板)设计工具,而是由多个模块组成的系统工具,分别是SCH(原理图)设计、SCH(原理图)仿真、PCB(印制电路板)设计、Auto Router(自动布线器)和FPGA设计等,覆盖了以PCB为核心的整个物理设计。该软件将项目管理方式、原理图和PCB图的双向同步技术、多通道设计、拓朴自动布线以及电路仿真等技术结合在一起,为电路设计提供了强大的支持。 随着计算机事业的发展,在信息化时代,电路设计中的很多工作都可以用计算机来完成。这样就大大减轻了设计人员的体力劳动强度,并且保证了设计的规范性准确性。而Protel99SE技术已越来越为人们所关注,人们利用protel99SE绘制各种原理图,进而制作出各种各样的科技产品已经成为当今世界的一个不可或缺的组成部分,所以说Protel99SE技术已越来越显得重要。

时钟同步技术概述

作为数字通信网的基础支撑技术,时钟同步技术的发展演进始终受到通信网技术发展的驱动。在网络方面,通信网从模拟发展到数字,从TDM网络为主发展到以分组网络为主;在业务方面,从以TDM话音业务为主发展到以分组业务为主的多业务模式,从固定话音业务为主发展到以固定和移动话音业务并重,从窄带业务发展到宽带业务等等。在与同步网相关性非常紧密的传输技术方面,从同轴传输发展到PDH,SDH,WDM和DWDM,以及最新的OTN和PTN技术。随着通信新业务和新技术的不断发展,其同步要求越来越高,包括钟源、锁相环等基本时钟技术经历了多次更新换代,同步技术也在不断地推陈出新,时间同步技术更是当前业界关注的焦点。 2、时钟技术发展历程 时钟同步涉及的最基本技术包括钟源技术和锁相环技术,随着应 用需求的不断提高,技术、工艺的不断改进,钟源技术和锁相环 技术也得到了快速的演进和发展。 (1) 钟源技术

时钟振荡器是所有数字通信设备的基本部件,按照应用时间的先后,钟源技术可分为普通晶体钟、具有恒温槽的高稳晶振、原子钟、芯片级原子钟。 一般晶体振荡器精度在nE-5~nE-7之间,由于具有价格便宜、尺寸小、功耗低等诸多优点,晶体振荡器在各个行业和领域中得到广泛应用。然而,普通晶体钟一般受环境温度影响非常大,因此,后来出现了具有恒温槽的晶体钟,甚至具有双恒温槽的高稳晶体钟,其性能得到很大改善。随着通信技术的不断发展,对时钟精度和稳定性提出了更高的要求,晶体钟源已经难以满足要求,原子钟技术开始得到应用,铷钟和铯钟是其中最有代表性的原子钟。一般来说,铷钟的精度能达到或优于nE-10的量级,而铯钟则能达到或优于1E-12的量级。 然而,由于尺寸大、功耗高、寿命短,限制了原子钟在一些领域的应用,芯片级原子钟有望解决这个难题。目前民用的芯片级原子钟基本上处于试验阶段,其尺寸只有立方厘米量级,耗电只有百毫瓦量级,不消耗原子,延长了使用寿命,时钟精度在nE-10量级以上,具有很好的稳定性。芯片级原子钟将在通信、交通、电力、金融、国防、航空航天以及精密测量等领域有着广泛的应用前景。 (2) 锁相环技术 锁相环技术是一种使输出信号在频率和相位上与输入信号同步的电路技术,即当系统利用锁相环技术进入锁定状态或同步状态后,系统的震荡器输出信号与输入信号之间相差为零,或者保持为常数。锁相环路技术是时钟同步的核心技术,它经历了模拟锁相环

毕业设计论文_单片机电子时钟的设计

单片机电子时钟的设计 摘要 单片机自20世纪70年代问世以来,以其极高的性能价格比,受到人们的重视和关注,应用很广、发展很快。单片机体积小、重量轻、抗干扰能力强、环境要求不高、价格低廉、可靠性高、灵活性好、开发较为容易。由于具有上述优点,在我国,单片机已广泛地应用在工业自动化控制、自动检测、智能仪器仪表、家用电器、电力电子、机电一体化设备等各个方面,而51单片机是各单片机中最为典型和最有代表性的一种。这次毕业设计通过对它的学习、应用,以AT89S51芯片为核心,辅以必要的电路,设计了一个简易的电子时钟,它由4.5V直流电源供电,通过数码管能够准确显示时间,调整时间,从而到达学习、设计、开发软、硬件的能力。 关键词:单片机 AT89S51 电子时钟数码管

Design of the singlechip electronics clock Abstract Single slice machine from published in 70's for 20 centuries, is compare with its very high function price, is value by people and pay attention to, apply very widely, develop very quickly. Single slice the machine physical volume is small,the weight is light,the anti- interference ability is strong,the environment haven't high request,the price is cheap,the credibility is high,vivid good,develop more easy. In order to having an above-mentioned advantage, at the our country, single slice the machine is broadly applied already to turn an equipment at industrial automation control,automatic examination,intelligence instrument appearance,home appliances,electric power electronics,the machine electricity integral whole etc. each aspect, but 51 machines is is a typical model most and have a representative most in each machine of a kind. This graduation design passes to its study and application, Take the AT89S51 chips as core, assist with the electric circuit of the necessity, design a simple electronics clock, it from the 4.5 V direct current power supply power supply, pass the figures tube can accurate manifestation time, adjust time。Arrive a study and design, develop thus soft,the ability of the hardware . Keywords:MCU AT89S51electronics clock digital tube

VHDL_电子时钟的设计

实验报告书 实验项目名称:数字电子钟的设计 实验项目性质:普通试验 所属课程名称:VHDL程序设计 实验计划学时:4学时 一、实验目的 掌握VHDL程序设计方法 二、实验内容和要求 能够实现小时(24进制)、分钟和秒钟(60进制)的计数功能 具有复位功能 功能扩展:具有复位、整点报时提示、定时闹钟等功能 在软件工具平台上,进行VHDL语言的各模块编程输入、编译实现和仿真验证。 三、实验主要仪器设备和材料 计算机 四、实验方法、步骤及结果测试 1、设计思路: 根据实验要求,将设计分为3个主要部分,时钟功能模块、整点报时模块和闹钟功能模块在时钟模块中,包括复位和预置数,分为时、分和秒三个进程,其主要思路如下: 秒钟的模块:设计一个60进制的计数器,以clk为其时钟信号,每60个clk后产生一个进位信号AOUT给分钟模块,作为分钟进程的响应信号。 分钟的模块:同理于秒钟的模块,设计一个60进制的计数器,以AOUT为其时钟信号,每60个AOUT后产生一个进位信号BOUT给小时模块,作为小时模块进程的响应信号。小时的模块:为24进制计数器,在分的进位信号BOUT的激发下计数,从0到23的时候产生一个信号COUT,全部清0,重新开始计时。

闹钟模块:同INPUT作为闹钟的设定,当时钟信号等于INPUT设定的时候,N为高电平,即是闹钟信号。 整点报时模块:用两个信号M,F,当M,F同时为0的时候,Z产生高电平,即是当做报时信号。 在时钟模块中,如有复位信号,则各小模块在复位信号的激励下进行各位置零; 共有5个进程。 2.程序代码: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY lyk IS PORT(CLK,RST,EN,SET:IN STD_LOGIC; INPUT:IN STD_LOGIC_VECTOR(10 DOWNTO 0); HA,HB:OUT STD_LOGIC_VECTOR(5 DOWNTO 0); HC:OUT STD_LOGIC_VECTOR(4 DOWNTO 0); Z,N:OUT STD_LOGIC ); SIGNAL AOUT,BOUT,COUT :STD_LOGIC; END ENTITY lyk; ARCHITECTURE CLOCK OF lyk IS SIGNAL M,F:STD_LOGIC_VECTOR(5 DOWNTO 0); SIGNAL S:STD_LOGIC_VECTOR(4 DOWNTO 0); BEGIN PROCESS(CLK,RST,EN) ---------秒钟进程 V ARIABLE GOD:STD_LOGIC_VECTOR(5 DOWNTO 0); BEGIN IF RST='1' THEN GOD:=(OTHERS =>'0'); ELSIF CLK'EVENT AND CLK='0'

数字时钟设计(完全数字电路)

数字时钟设计 姓名 学号 专业电子信息技术 指导教师 成绩 日期

基于555的数字时钟显示 摘要:数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。 数字钟从原理上讲是一种典型的数字电路,通过555定时器改装的多谐震荡器发出的脉冲频率具有一定的准确性。在这次设计中对分频器、计数器、、译码器和显示器进行研究编译,并完成了各种器件的编译工作,实现数字钟的功能。有准确计时,以数字形式显示时、分、秒的时间和校时功能。秒和校时功能都有一个共同特点就是它们都要用到振荡电路提供的1Hz脉冲信号。在计时出现误差时电路还可以进行校时和校分,为了使电路简单所设计的电路不具备校秒的功能。并且要用数码管显示时、分、秒,各位均为两位显示。 1引言 随着科技的快速发展,数字电子钟在实际生活中的应用越来越广泛,小到普通的电子表,大到航天器等高科技电子产品中的计时设备。数字钟是一个将“时”,“分”,“秒”显示于人的视觉器官的计时装置。它的计时周期为24小时,显示满刻度为23时59分59秒,另外应有整点报时附加功能。因此,一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器、报时电路和振荡器组成。作为电子技术的一名学生掌握并能够独立自主设计一个数字电子钟是必要和必须的,既可以加深对课本上理论知识的理解又能锻炼自己的思考和解决问题的能力。于是,经过查阅许多相关书籍和浏览许多网络未找到目录项。资源,我做了这款简单数字电子钟的设计。 2 方案论证 2.1 原理设计和功能描述 2.1.1 数字计时器的设计思想 要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。而脉冲源产生的脉冲信号地频率较高,因此,需要进行分频,使得高频脉冲信号变成适合于计时的低频脉冲信号,即“秒脉冲信号”(频率为1Hz)。经过分频器输出的秒脉冲信号到计数器中进行计数。由于计时的规律是:60秒=1分,60分=1小时,24小时=1天,就需要分别设计60进制,12进制计数器,并发出驱动信号。各计数器输出信号经译码器、驱动器到数字显示器,是“时”、“分”、“秒”得以数字显示出来。 2.1.2 数字电子钟总体框架图

NTP服务时间同步设置

一、市局集中端服务器上搭建NTP服务的服务端 1、在市局集中端服务器上,通过开始菜单,输入regedit命令后打开注册表设定画面。 2、修改以下选项的键值 HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\TimeProviders\ NtpServer内的「Enabled」设定为1,打开NTP服务器功能

3、修改以下键值 HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\Config\ AnnounceFlags设定为5,该设定强制主机将它自身宣布为可靠的时间源,从而使用内置的互补金属氧化物半导体(CMOS) 时钟。 4、在dos命令行执行以下命令,确保以上修改起作用 net stop w32time net start w32time 那么为了避免服务器和internet上的ntp同步,最好追加以下配置: HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\TimeProviders\

NtpClient的「enable」设定为0 以防止作为客户端自动同步外界的时间服务 二、硬盘录像机设置NTP服务的客户端 (注:只有新版型号的硬盘录像机才有NTP的功能) 1、在市局服务器IE浏览器地址栏输入硬盘录像机IP地址,进入到登陆界面,输入用户名:admin 密码:12345 端口号:8000 登陆后选择菜单“配置”, 2、在“配置”页面左边选择“远程配置”,出来“远程参数配置”页面,在“远程参数配置”页面里选择“网络参数”→“NTP设置”,“启用NTP”打上钩,“服务器地址”统一为市局集中端服务器地址,“NTP端口号”为123,校时间隔:4320(统一设置为三天,这里的单位是分钟),选择时区: ,点儿“保存”按钮。

基于51单片机多功能电子时钟设计论文报告-毕设论文

单片机课程设计报告 多功能电子数字钟 姓名: 学号: 班级: 指导教师:

目录 一课程设计题目-------------------------------- 3 二电路设计--------------------------------------- 4 三程序总体设计思路概述------------------- 5 四各模块程序设计及流程图---------------- 6 五程序及程序说明见附录------------------- ** 六课程设计心得及体会---------------------- 11 七参考资料--------------------------------------- 12

一题目及要求 本次单片机课程设计在Proteus软件仿真平台下实现,完成电路设计连接,编程、调试,仿真出实验结果。具体要如下:用8051单片机设计扩展6位数码管的静态或动态显示电路,再连接几个按键和一个蜂鸣器报警电路,设计出一个多功能电子钟,实现以下功能: (1)走时(能实现时分秒,年月日的计时) (2)显示(分屏切换显示时分秒和年月日,修改时能定位闪 烁显示) (3)校时(能用按键修改和校准时钟) (4)定时报警(能定点报时) 本次课程设计要求每个学生使用Proteus仿真软件独立设计制作出电路图、完成程序设计和系统仿真调试,验收时能操作演示。最后验收检查 结果,评定成绩分为: (1)完成“走时+显示+秒闪”功能----及格 (2)完成“校时修改”功能----中等 (3)完成“校时修改位闪”----良好 (4)完成“定点报警”功能,且使用资源少----优秀

电力时钟同步系统解决方案

电力GPS时钟同步系统解决方案 北京创想京典科技发展有限公司 科 技 领先铸就最佳

什么是时间? 时间是一个较为抽象的概念,爱因斯坦在相对论中提出:不能把时间、空间、物质三者分开解释,"时"是对物质运动过程的描述,"间"是指人为的划分。时间是思维对物质运动过程的分割、划分。 在相对论中,时间与空间一起组成四维时空,构成宇宙的基本结构。时间与空间都不是绝对的,观察者在不同的相对速度或不同时空结构的测量点,所测量到时间的流逝是不同的。广义相对论预测质量产生的重力场将造成扭曲的时空结构,并且在大质量(例如:黑洞)附近的时钟之时间流逝比在距离大质量较远的地方的时钟之时间流逝要慢。现有的仪器已经证实了这些相对论关于时间所做精确的预测,并且其成果已经应用于全球定位系统。另外,狭义相对论中有“时间膨胀”效应:在观察者看来,一个具有相对运动的时钟之时间流逝比自己参考系的(静止的)时钟之时间流逝慢。 就今天的物理理论来说时间是连续的,不间断的,也没有量子特性。但一些至今还没有被证实的,试图将相对论与量子力学结合起来的理论,如量子重力理论,弦理论,M理论,预言时间是间断的,有量子特性的。一些理论猜测普朗克时间可能是时间的最小单位。

什么是时间? 根据斯蒂芬·威廉·霍金(Stephen William Hawking)所解出广义相对论中的爱因斯坦方程式,显示宇宙的时间是有一个起始点,由大霹雳(或称大爆炸)开始的,在此之前的时间是毫无意义的。而物质与时空必须一起并存,没有物质存在,时间也无意义。

卫星时钟系统为什么含有精确的时间信息? 地球本身是一个不规则的圆,加上地球自转和公转的误差,如果仅仅依靠经度、纬度、海拔高度三个参数来定位的偏差会很大,所以 引入了一个时间参数,每个卫星都内置了一个高稳定度的原子钟!

数电 简易数字计时时钟电路设计

闽南师范大学物理与信息工程院 课程设计报告课题:简易数字计时电路设计 姓名: 学号: 系别: 专业: 年级: 指导教师: 2013年11 月3 日

摘要:本课设是以并联谐振方式经过二分频产生一个秒脉冲,依次通过十分频、六分频、十分频三个电路产生一个时间能达到九分五十九秒的时钟。具有报警、清零、启动计时、暂停计时及继续计时等功能。在电源上也是采用简单实用的稳压电源。该电路节省成本,电路原理清晰,稍作修改可以用来当做闹钟、计时等。 关键词:计时报警 74LS161 CD4060 CD4011 74LS48

目录 1.设计任务 (4) 1.1 设计目的 (4) 1.2 设计要求 (4) 2.设计方案 (5) 2.1 设计总框图 (5) 2.1.1 设计思路 (5) 2.2 直流稳压电源 (5) 2.3 秒脉冲信号发生器电路 (6) 2.4 分频电路 (7) 2.5 显示及其驱动电路 (8) 2.6 即时时间设置电路 (8) 2.7 报警选频电路 (10) 2.8 蜂鸣器驱动电路 (10) 3.系统测试 (11) 3.1 电路的检查 (11) 3.2 电路板的调试及其问题 (11) 3.3 数据测量 (12) 4.结论 (14) 5.参考资料 (14) 6.附录 (14) 6.1 元器件清单 (14) 6.2 仪器设备清单 (15) 6.3 原理图 (15) 6.4 PCB图 (16) 6.5 实物图 (17)

1.设计任务 1.1设计目的 1.熟悉中、小规模数字集成电路的使用方法。 2.熟悉常用分频、计数、译码、显示等电路。 3.掌握数字电路设计、组装、调试方法。 1.2设计要求 1.具有“分”“秒”显示的计时电路(9分59秒)。 2.具有随时计时清零的功能。 3.秒信号产生、系统电源设计。 4.具有调整“分”“秒”的功能。 5.计时将满时具有声音提示功能: 9分51秒、53秒、55秒、57秒、59秒输出前4响低音,后1响高音鸣叫。步长为1秒,最后1响结束时正好为整点。(低音500Hz左右,高音1000Hz左右)。 7.用中小规模集成电路实现,画出系统框图、各单元逻辑电路图。 6.铺铜板板的大小(10cm * 10cm)。 2. 设计方案 2.1 设计总框图 图2.1简易数字计时电路设计总框图

基于单片机的电子钟设计方案毕业论文。。.doc

基于单片机的电子时钟设计 摘要 20 世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。 现代生活的人们越来越重视起了时间观念,可以说是时间和金钱划上了等号。对于那些对时间把握非常严格和准确的人或事来说,时间的不准确会带来非常大的麻烦,所以以数码管为显示器的时钟比指针式的时钟表现出了很大的优势。数码管显示的时间简单明了而且读数快、时间准确显示到秒。而机械式的依赖于晶体震荡器,可能会导致误差。 数字钟是采用数字电路实现对“时”、“分”、“秒”数字显示的计时装置。数字钟的精度、稳定度远远超过老式机械钟。在这次设计中,我们采用LED数码管显示时、分、秒,以24 小时计时方式,根据数码管动态显示原理来进行显示,用 12MHz的晶振产生振荡脉冲,定时 器计数。在此次设计中,电路具有显示时间的其本功能,还可以实现对时间的调整。数字 钟是其小巧,价格低廉,走时精度高,使用方便,功能多,便于集成化而受广大消费的喜爱,因此得到了广泛的使用。 关键字:数字电子钟单片机 数字电子钟的背景 20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各 个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产 品性能进一步提高,产品更新换代的节奏也越来越快。时间对人们来说总是那么宝贵,工作的忙碌性和繁杂性容易使人忘记当前的时间。忘记了要做的事情,当事情不是很重要的时候,这种遗忘无伤大雅。但是,一旦重要事情,一时的耽误可能酿成大祸。 目前,单片机正朝着高性能和多品种方向发展趋势将是进一步向着 CMOS化、低功耗、小体积、大容量、高性能、低价格和外围电路内装化等几个方面发展。下面是单片机的主要发 展趋势。单片机应用的重要意义还在于,它从根本上改变了传统的控制系统设计思想和设计方 法。从前必须由模拟电路或数字电路实现的大部分功能,现在已能用单片机通过软件方法

GPS时钟系统(GPS同步时钟)技术方案(1)

GPS 时钟系统(GPS 同步时钟技术方案 技术分类:通信 | 2010-11-08 维库 在电力系统、 CDMA2000、 DVB 、 DMB 等系统中 , 高精度的 GPS 时钟系统(GPS 同步时钟对维持系统正常运转有至关重要的意义。 那如何利用 GPS OEM来进行二次开发 , 产生高精度时钟发生器是一个研究的热点问题。如在 DVB-T 单频网 (SFN中 , 对于时间同步的要求 , 同步精度达到几十个 ns, 对于这样高精度高稳定性的系统 , 如何进行商业级设计 ? 一、引言 在电力系统的许多领域,诸如时间顺序记录、继电保护、故障测距、电能计费、实时信息采集等等都需要有一个统一的、高精度的时间基准。利用 GPS 卫星信号进行对时是常用的方法之一。 目前, 市场上各种类型的 GPS-OEM 板很多, 价格适中, 具有实用化的条件。利用 GPS-OEM 板进行二次开发,可以精确获得 GPS 时间信息的 GPS时钟系统 (GPS 同步时钟。本文就是以加拿大马可尼公司生产的 SUPERSTAR GPS OEM板为例介绍如何开发应用于电力系统的的 GPS 时钟系统(GPS 同步时钟。 二、 GPS 授时模块 GPS 时钟系统 (GPS 同步时钟采用 SUPERSTAR GPS OEM 板作为 GPS 接受模块, SUPERSTAR GPS OEM 板为并行 12跟踪通道,全视野 GPS 接受模块。 OEM 板具有可充电锂电池。 L1频率为 1575.42MHz ,提供伪距及载波相位观测值的输出和 1PPS (1 PULSE PER SECOND脉冲输出。 OEM 板提供两个输入输出串行口,一个用作主通信口,可通过此串行口对 OEM 板进行设置,也可从此串口读取国际标准时间、日期、所处方位等信息。另一个串行口用于 RTCM 格式的差分数据的输出,当无差分信号或仅用于 GPS 授时,此串行口可不用。 1PPS 脉冲是标准的 TTL 逻辑

数字电子时钟设计

电子技术课程设计 数字电子时钟的设计 摘要: 设计一个周期为24小时,显示满刻度为23时59分59秒,具有校时功能和报时功能的电子钟。本系统的设计电路由时钟译码显示电路模块、脉冲逻辑电路模块、时钟脉冲模块、整电报时模块、校时模

块等部分组成。计数器采用异步双十进制计数器74LS90,发生器使用石英振荡器,分频器4060CD及双D触发器74LS74D,整电报时电路用门电路及扬声器构成。 一、设计的任务与要求 电子技术课程设计的主要任务是通过解决一,两个实际问题,巩固和加深在“模拟电子技术基础”和“数字电子技术基础”课程中所学的理论知识和实验技能,基本掌握常用电子电路的一般设计方法,提高电子电路的设计和实验能力,为以后从事生产和科研工作打下一定的基础。电子技术课程设计的主要内容包括理论设计、仿真实验、安装与调试及写出设计总结报告。衡量课程设计完成好坏的标准是:理论设计正确无误;产品工作稳定可靠,能达到所需要的性能指标。 本次课程设计的题目是“多功能数字电子钟电路设计”。要求学生运用数字电路,模拟电路等课程所学知识完成一个实际电子器件设计。 二、设计目的 1、让学生掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统 的设计、安装、测试方法; 2、进一步巩固所学的理论知识,提高运用所学知识分析和解决实 际问题的能力; 3、提高电路布局﹑布线及检查和排除故障的能力; 4、培养书写综合实验报告的能力。

三、原理方框图如下 1、图中晶体振荡电路由石英32.768KHZ及集成芯。 2、图中分频器4060BD芯片及D触发器构成分频器。 3、计数器由二——五——十73LS90芯片构成。 4、图中DCD_HEX显示器用七段数码显示器且本身带有译码器。 5、图中校时电路和报时电路用门电路构成。 四、单元电路的设计和元器件的选择 1、十进制计数电路的设计 74LS90集成芯片是二—五—十进制计数器,所以将INB与QA 相连;R0(1)、R0(2)、R9(1)、R9(2)接地(低电平);INA

时间同步服务器设置

默认情况下,服务器Windows2003 Server是作为时间同步客户端的。你可以双击系统时间,在“Internet时间”属性页里有时间同步的设置,显然系统默认是作为客户端的。所以,必须通过修改设置,使系统作为时间同步的服务端。 1,修改注册表以下项的键值 HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\TimeProviders\NtpServer 内的“Enabled”设置为“1”,打开时间同步服务功能。 2,修改以下键值HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\Config里的“AnnounceFlags”设置为“5”,表示强制主机将它自身宣布为可靠的时间源,从而使用CMOS时钟。如果设置为“a”,则表示为采用外面的时间服务器。 3,重启Win32Time服务执行如下命令:net stop w32time && net start w32time 客户端设置: 1,客户端的设定更改注册表即可。 HKEY_LOCAL_MACHINE\SYSTEM\CurrentControlSet\Services\W32Time\TimeProviders\NtpClient里的“SpecialPollInterval”时间间隔(单位为秒,43200为12小时);“SpecialPollTimeRemaining”时间同步的服务器,格式为:“IP address,0”,例如:192.168.1.1,0。 2,重启win32time服务net stop w32time && net start w32time这样,设置完成了,无需重启电脑。如果想立刻时间的变化,可以把时间设置成1、2秒。