(整理)Allegro PCB布线.

PCB布线

孙海峰在PCB设计的整个过程中,布线时非常重要的一环,无论是原理图的绘制工作,还是后期网表的导入和PCB板布局工作,都是为了实现布线工作做准备的。

在Cadence平台中,布线方式分为自动布线和手动布线两种。通常简单电路用自动布线,而复杂电路则采用手动布线,设计者可以根据自己的设计要求,制定合适的设计规则,然后进行自动布线或者严格的手动布线。下面从这两个方式入手,来了解Allegro PCB Editor平台下的电路板布线工作。

一、自动布线

自动布线的布通率取决于布线前的准备工作,即电路板的布局和布线规则的设置。一般先要进行探索式布线,连通短线,然后进行迷宫式布线;先对电路板进行全局布线,再根据需要进行布线路径优化,试着重新布线用来改进整体效果,必要时,对比较严格的连线进行手动布线。

1、自动布线规则设置

Cadence为设计者提供了强大的自动布线器,在PCB自动布线之前,设计者需要根据要求设置布线规则,在Allegro PCB平台中,所有PCB设计规则,都由Allegro Constraint Manager进行编辑和管理。

(1)查看之前设计中定义的规则

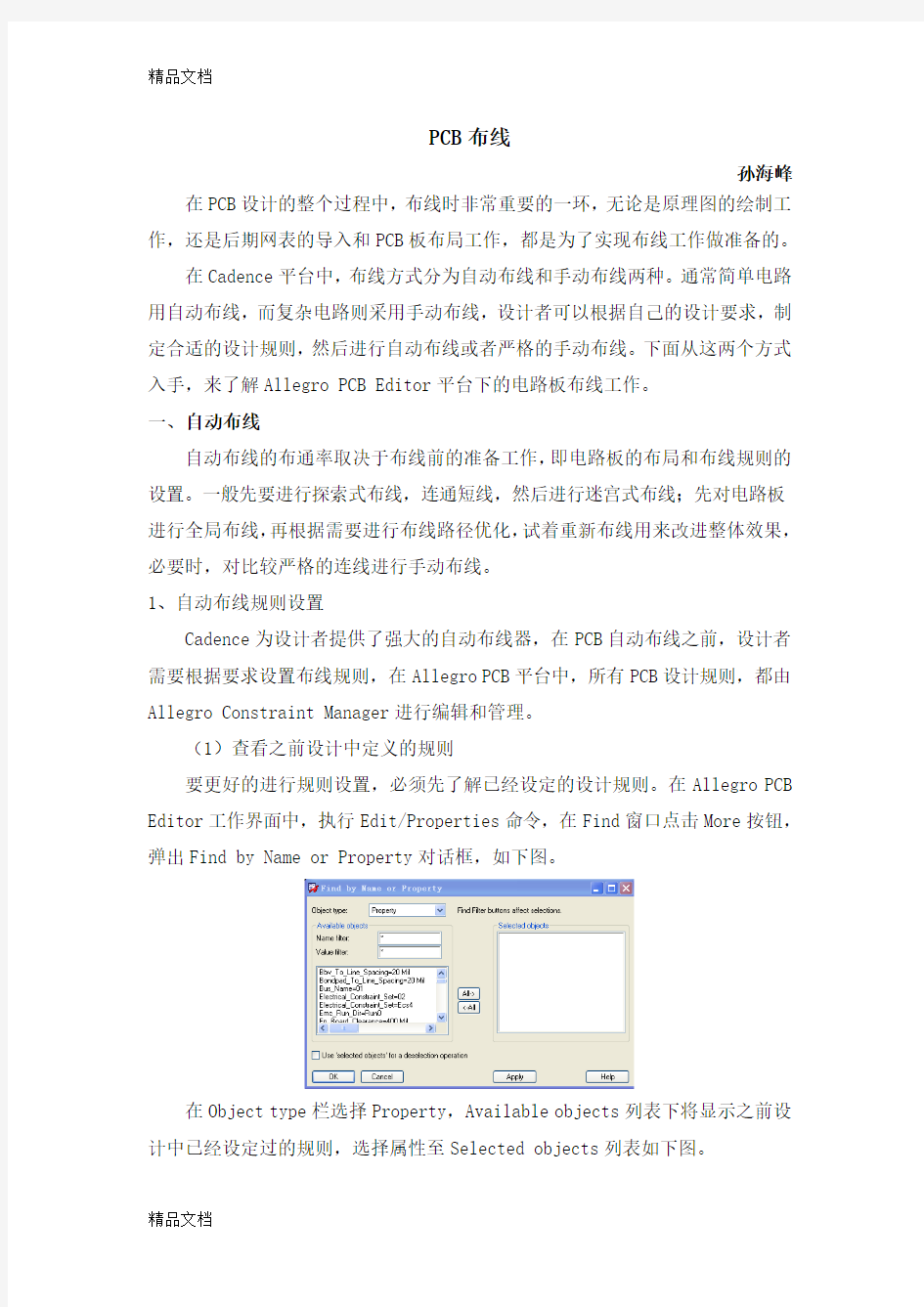

要更好的进行规则设置,必须先了解已经设定的设计规则。在Allegro PCB Editor工作界面中,执行Edit/Properties命令,在Find窗口点击More按钮,弹出Find by Name or Property对话框,如下图。

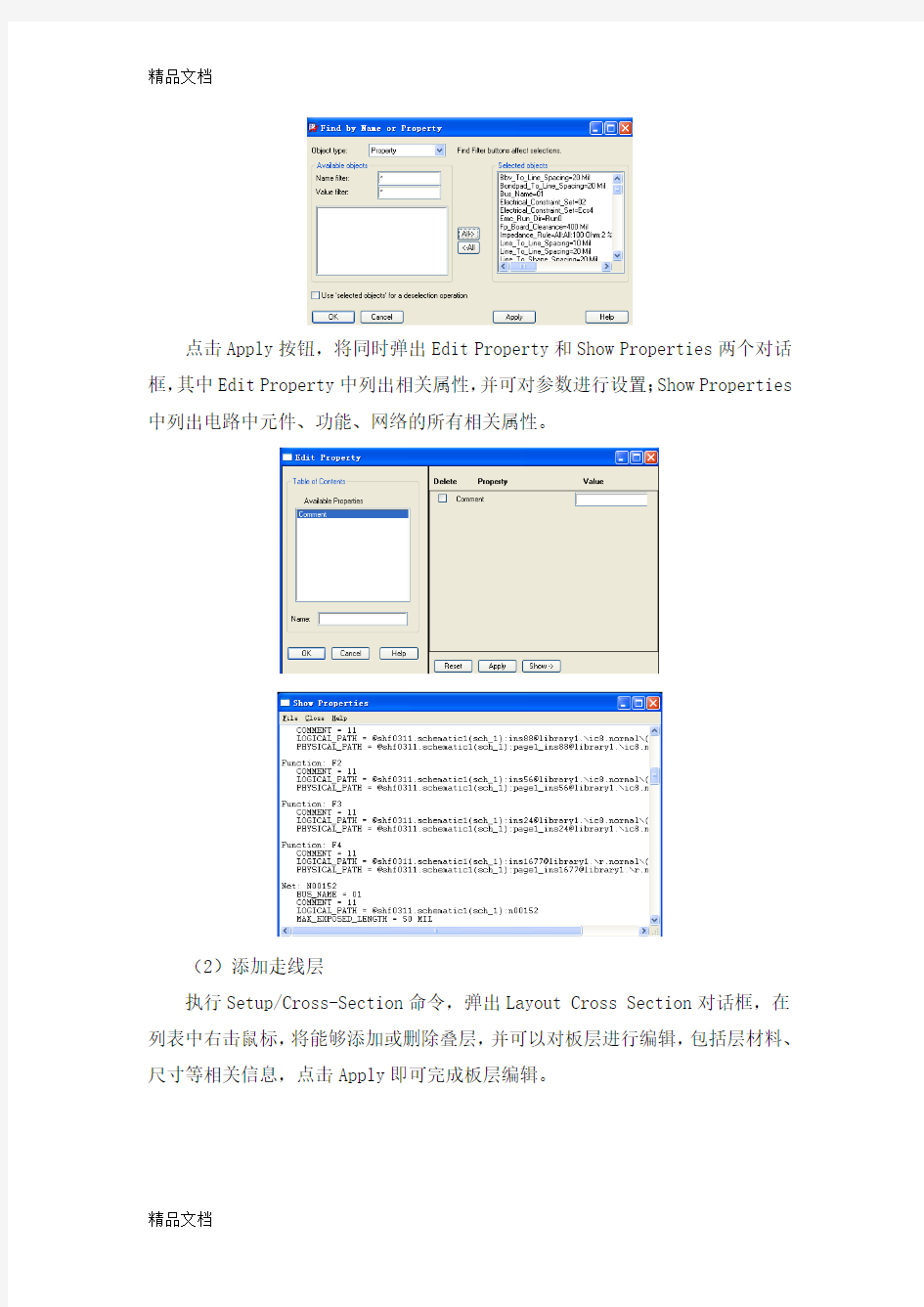

在Object type栏选择Property,Available objects列表下将显示之前设计中已经设定过的规则,选择属性至Selected objects列表如下图。

点击Apply按钮,将同时弹出Edit Property和Show Properties两个对话框,其中Edit Property中列出相关属性,并可对参数进行设置;Show Properties 中列出电路中元件、功能、网络的所有相关属性。

(2)添加走线层

执行Setup/Cross-Section命令,弹出Layout Cross Section对话框,在列表中右击鼠标,将能够添加或删除叠层,并可以对板层进行编辑,包括层材料、尺寸等相关信息,点击Apply即可完成板层编辑。

(3)指定网络布线规则

执行Edit/Properties命令,并在Find窗口点击More命令,将弹出Find by Name or Property对话框,在Object type菜单下选择Net,在Available objects 栏中选择需要属性编辑的网络,点击Apply命令,则弹出Edit Property和Show Property对话框,前者可用来编辑网络规则,后者来显示网络具体属性和走线

规则。

执行Setup/Constraints/Modes命令,弹出Analysis Modes对话框,进行

设计规则前将对应选项卡中DRC modes区域均选择on状态,以便设置设计规则时同时进行DRC检查,避免规则设置错误。

执行Setup/Constraints/Constraint Manager命令,将弹出Allegro Constraint Manager对话框,如下图。

在此对话框中,Electrical 可以选择不同的节点进行不同的电气规则设置;Physical可以对不同目标进行物理规则设置;Spacing可以对不同目标进行间距设置;Same Net Spacing可以来设置相同网络间距规则;Properties用来设置网络、元件的相关属性;DRC用来设置布线时发生的DRC错误。

2、使用Auto Router自动布线

当规则设置完成后就可以根据现有规则进行初步自动布线了,Allegro为设计者提供了一个外部自动布线软件,功能十分强大。执行Route/PCB

Router/Route Automatic命令,弹出Automatic Router对话框如下图。

其中对话框中有四个选项卡,在Router Setup选项卡如上图所示,Strategy 区域用以设置布线模式:Specify routing passes表示具体在Routing Passes 选项卡中设置,Use smart router则表示调用Smart Router选项卡中的设置,Do file表示通过Do文件来进行布线;Options区域设置一下内容:Limit via creation表示限制过孔,Limit wraparounds表示限制绕线,Protect existing routes表示保持原有走线,Turbo Stagger表示增强交错布线,Enable diagonal routing表示允许斜线布线;Wire grid用以设置布线栅格点;Via grid用以设置过孔栅格点;Routing Subclass表示布线板层;Routing Direction表示布线方向;Protect表示该板层是否保持不变。

当上面布线模式选择Specify routing passes是时,Routing Passes选项卡有效,如下图所示:

其中Preroute and route区域选择布线动作;Post Route用以选择布线效果:Critic为精确布线,Filter routing passes为过滤布线途径,Center wires 为中心线,Spread wires为展开导线,Milter corner为45°斜线布线,Delete conflicts为删除冲突布线。

当布线模式选择Use smart router时,Smart Router选项卡如下图。

在该选项卡中,Grid区域用以设置过孔、走线的最小栅格点;Fanout区域用以设置扇出;Generate Testpoints区域用以设置全局测试点;Milter after route表示布线后走线。

Sections选项卡如下图所示,在Objects to route区域选择布线网络,可以选择全部网络,也可以选择部分网络。

完成以上这些设置后,点击Route按钮,Automatic Router将会为电路板实施自动布线,如下图。

布线完成后,如果对布线结果不满意,设计者还可以取消这次布线,重新设置参数即可重新进行布线。

3、使用CCT布线器自动布线

Allegro还提供CCT布线器可进行电路板的自动布线,而且设计者通过CCT 布线器可以动态的观察布线的全过程,包括布线条数、重布线条数、未连接条数、布线冲突、布通率等。

执行Route/PCB Router/Route Editor命令进入Allegro PCB Router自动布线器如下图。

在CCT自动布线器中可以在Rules菜单下设置自动布线规则,可以在Autoroute菜单下确定布线基本设置,不再赘述,与以上设置相仿。执行Autoroute/Route命令,弹出AutoRoute对话框,完成基本设置,点击Apply即可进行布线。

完成布线后点击OK关闭Auto Route对话框,系统重新检查布线。执行Report/Route Status命令,可以看到整个布线状态信息。

二、手动布线

手动布线时设计者以手工的方式将图纸离得飞线布成铜箔走线,这是布线工作最基本、最主要的方法。在自动布线之前,设计者都需要将一些重要网络进行手动布线,如高频时钟、主电源等网络,因为它们对布线距离、线宽、间距等规则往往比较特殊,自动布线很难完成。

手动布线主要有以下操作,它们构成了手动布线的基础。

1、添加连接线

执行Route/Connect命令,然后点击需要连接的引脚,开始走线,在走线过程中Options窗口用以设置走线方式。

其中Act设置走线层,Alt显示双击自动切换层,Line lock设定走线形式和拐角,Line width设定线宽,Bubble设定绕线方式,Gridless设定走线走线是否在栅格点,Clip dangling clines设定是否剪切空置走线,Smooth设定自动调整走线的方式,Snap to connect point设定走线是否从引脚、过孔的中心引出,Replace设定是否允许替换存在的走线。

设置好Options窗口中走线属性后,开始走线至另一连接点即可,右击Done 命令完成,Oops取消。

2、删除走线

执行Edit/Delete命令或者点击按钮,然后在Options、Find窗口中均选择Clines如下图,再双击需要删除的走线,右击Done即可删除该走线了。

3、添加过孔

走线时如果需要添加过孔,在Options窗口中设定好Act层(走线层)以及Alt层(转换层),再在适合要求的位置双击即可完成过孔的添加。

4、扇出布线

在PCB 设计中扇出就是从SMC引脚拉一小段走线后打过孔,进入内层走线。

执行Route/Create Fanout命令,或者执行Route/PCB Router/Fanout by pick

命令,再在Options窗口确定扇出基本设置,在Find窗口选择建立扇出的对象。

再点击需要扇出的元件、引脚或群组,即可完成相应的扇出操作。完成扇出的元件如下图所示。

5、群组布线

群组布线就是一次进行多条路径布线,只能在一个层内进行群组布线,不可用过孔。

执行Route/Connect命令,再用鼠标拉选需要一起布线的群组引脚,然后就可以进行群组布线了。而且右击鼠标,在下拉菜单中可以编辑群组布线方式。

6、建立差分对布线

差分信号又称差动信号,是由两根长度相同、极性相反的信号传输一路数据的电平差来决定的。进行差分信号布线,关键在于保证两根信号完全一致,另外还需要保证两根信号线保持平行,且距离保持不变,进而可以保证信号品质。

(1)执行Setup/Constraints/Constraint Manager命令,进入Constraint Manager约束管理器,在Electrical标签卡下,选择Net/Routing/Differential Pair如下图。

点击需要建立差分信号的其中一个网络,按住shift键,再选择另一个网络,而后右击,执行Create Differential Pair命令可创建差分对,然后在后面列

表中设置差分对走线的约束规则。

(2)执行Logic/Assign Differential Pair命令,进入Assign Differential Pair界面。

点击所需建立差分信号的两个网络,然后点击Add命令,则建立差分信号了,在Diff Pair name列表下将建立对应差分对,而后在Constraint Manager中进行差分对规则设置。

7、

8、建立蛇形走线

蛇形走线用于满足延时或等长要求。

执行Route/Delay Tune命令,即开始蛇形布线,再在Options窗口内进行蛇形走线的布线设置。

在Options窗口,设置蛇形走线层,设置差分信号布线方式,设置蛇形走线是否按中心线分布,设置蛇形走线间距和绕线角度,设置是否同时显示DRC错误。

PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前,用交互式预先对要求比较严格的线进行布线。

后仿真流程

synplify,ISE,ModelSim后仿真流程 我想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。 首先,我把我用到的软件说明一下。如果你发现根据我的操作,你还是解决不了ModelSim 后仿真的问题,那就可能是软件版本的问题。 1,ModelSim Se 6.1b 2,Synplify Pro 7.5.1 3,ISE 5.2i (这个是老了点) 4,WindowsXP(这个应该没有多大的关系) 还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。 下面的这些方法,是我这3天搞出来的。当然也参考了一些文章。如果谁有更方便的方法,欢迎指出来。我的邮箱是vf1983cs@https://www.360docs.net/doc/b710142560.html,。有空大家多交流。 一,为modelsim生成3个库。 首先,介绍一下这三个库。 Simprim_ver:用于布局布线后的仿真。 Unisim_ver :如果要做综合后的仿真,还要编译这个库。 Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。 我们要为modelsim生成的是标准库。所谓的标准库就是modelsim运行后,会自动加载的库。不过这方面我还不是很肯定。因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。 第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。 第二步:新建库,库名起作s imprim_ver。我们首先就是要建的就是这个库。

Allegro教程-17个步骤

Allegro教程-17个步骤 Allegro® 是Cadence 推出的先进 PCB 设计布线工具。 Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品Cadence® OrCAD® Capture 的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完美解决方案。 Allegro 拥有完善的 Constraint 设定,用户只须按要求设定好布线规则,在布线时不违反 DRC 就可以达到布线的设计要求,从而节约了烦琐的人工检查时间,提高了工作效率!更能够定义最小线宽或线长等参数以符合当今高速电 路板布线的种种需求。 软件中的 Constraint Manger 提供了简洁明了的接口方便使用者设定和查看 Constraint 宣告。它与 Capture 的结合让 E.E. 电子工程师在绘制线路图时就能设定好规则数据,并能一起带到Allegro工作环境中,自动在摆零件及 布线时依照规则处理及检查,而这些规则数据的经验值均可重复使用在相同性 质的电路板设计上。 Allegro 除了上述的功能外,其强大的自动推挤 push 和贴线 hug 走线以及完善的自动修线功能更是给用户提供极大的方便;强大的贴图功能,可以提 供多用户同时处理一块复杂板子,从而大大地提高了工作效率。或是利用选购 的切图功能将电路版切分成各个区块,让每个区块各有专职的人同时进行设 计,达到同份图多人同时设计并能缩短时程的目的。 用户在布线时做过更名、联机互换以及修改逻辑后,可以非常方便地回编 到 Capture 线路图中,线路图修改后也可以非常方便地更新到 Allegro 中; 用户还可以在 Capture 与 Allegro 之间对对象的互相点选及修改。 对于业界所重视的铜箔的绘制和修改功能, Allegro 提供了简单方便的内层分割功能,以及能够对正负片内层的检阅。对于铺铜也可分动态铜或是静态铜,以作为铺大地或是走大电流之不同应用。动态铜的参数可以分成对所有铜、单一铜或单一对象的不同程度设定,以达到铜箔对各接点可设不同接续效果或 间距值等要求,来配合因设计特性而有的特殊设定。 在输出的部分,底片输出功能包含 274D 、 274X 、 Barco DPF 、 MDA 以及直接输出 ODB++ 等多样化格式数据当然还支持生产所需的 Pick & Place 、NC Drill 和 Bare-Board Test 等等原始数据输出。Allegro 所提供的强大输 入输出功能更是方便与其它相关软件的沟通,例如 ADIVA 、 UGS(Fabmaster) 、VALOR 、Agilent ADS… 或是机构的 DXF 、IDF……… 。为了推广整个先进EDA 市场 ,Allegro 提供了Cadence? OrCAD? Layout 、 PADS 、 P-CAD 等接口,让想转换 PCB Layout 软件的使用者,对于旧有的图档能顺利转换至Allegro 中。 Allegro 有着操作方便,接口友好,功能强大,整合性好等诸多优点,是一家公司投资 EDA 软件的理想选择。

allegro布线的注意事项

A. 创建网络表 1. 网络表是原理图与PCB的接口文件,PCB设计人员应根据所用的原理图和PCB设计工具的特性,选用正确的网络表格式,创建符合要求的网络表。 2. 创建网络表的过程中,应根据原理图设计工具的特性,积极协助原理图设计者排除错误。保证网络表的正确性和完整性。 3. 确定器件的封装(PCB FOOTPRINT). 4. 创建PCB板 根据单板结构图或对应的标准板框, 创建PCB设计文件; 注意正确选定单板坐标原点的位置,原点的设置原则: A. 单板左边和下边的延长线交汇点。 B. 单板左下角的第一个焊盘。 板框四周倒圆角,倒角半径3.5mm。特殊情况参考结构设计要求。 B. 布局 1. 根据结构图设置板框尺寸,按结构要素布置安装孔、接插件等需要定位的器件,并给这些器件赋予不可移动属性(锁定)。按工艺设计规范的要求进行尺寸标注。 2. 根据结构图和生产加工时所须的夹持边设置印制板的禁止布线区、禁止布局区域。根据某些元件的特殊要求,设置禁止布线区。 3. 综合考虑PCB性能和加工的效率选择加工流程。 加工工艺的优选顺序为:元件面单面贴装——元件面贴、插混装(元件面插装焊接面贴装一次波峰成型)——双面贴装——元件面贴插混装、焊接面贴装。 4. 布局操作的基本原则 A. 遵照“先大后小,先难后易”的布置原则,即重要的单元电路、核心元器件应当优先布局. B. 布局中应参考原理框图,根据单板的主信号流向规律安排主要元器件. C. 布局应尽量满足以下要求:总的连线尽可能短,关键信号线最短;高电压、大电流信号与小电流,低电压的弱信号完全分开;模拟信号与数字信号分开;高频信号与低频信号分开;高频元器件的间隔要充分. D. 相同结构电路部分,尽可能采用“对称式”标准布局; E. 按照均匀分布、重心平衡、版面美观的标准优化布局; F. 器件布局栅格的设置,一般IC器件布局时,栅格应为5--20 mil,小型表面安装器件,如表面贴装元件布局时,栅格设置应不少于5mil。 G. 如有特殊布局要求,应双方沟通后确定。 5. 同类型插装元器件在X或Y方向上应朝一个方向放置。同一种类型的有极性分立元件也要力争在X或Y 方向上保持一致,便于生产和检验。 6. 发热元件要一般应均匀分布,以利于单板和整机的散热,除温度检测元件以外的温度敏感器件应远离发热量大的元器件。 7. 元器件的排列要便于调试和维修,亦即小元件周围不能放置大元件、需调试的元、器件周围要有足够的空间。 8. 需用波峰焊工艺生产的单板,其紧固件安装孔和定位孔都应为非金属化孔。当安装孔需要接地时, 应采用分布接地小孔的方式与地平面连接。 9. BGA与相邻元件的距离>5mm。其它贴片元件相互间的距离>0.7mm;贴装元件焊盘的外侧与相邻插装元件的外侧距离大于2mm;有压接件的PCB,压接的接插件周围5mm内不能有插装元、器件,在焊接面其周围5mm内也不能有贴装元、器件。

modelsim仿真详细过程

由于我们只需要了解仿真的完整过程,所以不需要自己写源文件和测试文件(也称为testbench)。一下就是简单的源文件和测试文件(亲自测试过)。 //源文件 module compare(equal,a,b); input a,b; output equal; assign equal=(a==b)?1:0; endmodule //测试文件 `timescale 1ns/1ns `include"./compare.v" module comparetest; reg a,b; wire equal; initial begin a=0; b=0; #100 a=0;b=1; #100 a=1;b=1;

#100 a=1;b=0; #100 $stop; end compare compare1(.equal(equal),.a(a),.b(b)); endmodule 有了源文件和测试文件下面就开始用modelsim进行仿真了。 步骤一:新建工程和.v文件(也就是源文件和测试文件) 打开modelsim软件,点击file,选择new—>project 然后就会弹出下面窗口: 然后在project name那一栏写上工程名(随便去,一般是字母),在project location选择工程路径(路径最好没有中文,听说的),然后点OK。进入下个界面:

然后点击小框里面的“create new file”.弹出界面: 在file name中写下源文件名,由于这是比较两数的大小,我取为:compare。在“add file as type”中选择verilog,点OK,然后有:

modelsim使用 + 前仿真 + 后仿真 + verilog

Modelsim 6.0 使用教程 1. Modelsim简介 Modelsim仿真工具是Model公司开发的。它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。 对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。 2.安装 同许多其他软件一样,Modelsim SE同样需要合法的License,通常我们用Kengen产生license.dat。 ⑴.解压安装工具包开始安装,安装时选择Full product安装。当出现Install Hardware Security Key Driver时选择否。当出现Add Modelsim To Path选 择是。出现Modelsim License Wizard时选择Close。 ⑵.在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后 复制到该文件夹下。 ⑶.修改系统的环境变量。右键点击桌面我的电脑图标,属性->高级->环境变量-> (系统变量)新建。按下图所示内容填写,变量值内如果已经有别的路径了, 请用“;”将其与要填的路径分开。LM_LICENSE_FILE = c:\flexlm\license.dat

Allegro差分线走线规则

SOFER TECHNICAL FILE Allegro 15.x 差分线布线规则设置 Doc Scope : Cadence Allegro 15.x Doc Number : SFTCA06001 Author :SOFER Create Date :2005-5-30 Rev : 1.00

Allegro 15.x差分线布线规则设置 文档内容介绍: 1.文档背景 (3) 2.Differential Pair信号介绍 (3) 3.如何在Allegro中定义Differential Pair属性 (4) 4.怎样设定Differential Pair在不同层面控制不同线宽与间距 (8) 5.怎样设定Differential Pair对与对之间的间距 (11)

1.文档背景 a)差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,差分线 大多为电路中最关键的信号,差分线布线的好坏直接影响到PCB板子信号质量。 b)差分线一般都需要做阻抗控制,特别是要在多层板中做的各层的差分走线阻抗都 一样,这个一点要在设计时计算控制,否则仅让PCB板厂进行调整是非常麻烦的 事情,很多情况板厂都没有办法调整到所需的阻抗。 c)Allegro版本升级为15.x后,差分线的规则设定与之前版本有很大的改变。虽然 Allegro15.0版本已经发布很长时间了,但是还是有很多人对新版本的差分线规 则设置不是很清楚。 2.Differential Pair信号介绍 差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关 键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?在PCB设计中又如何能保证其良好的性能呢?带着这两个问题,我们进行下一部分的讨论。何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值 来判断逻辑状态“0”还是“1”。而承载差分信号的那一对走线就称为差分走线。 差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面: a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎 是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可 以被完全抵消。 b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场 可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。 c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端 信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差, 同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。 …… 由于篇幅问题,这里对差分信号不做深入介绍了。

反相器设计前仿与后仿流程

目录 前端电路设计与仿真 (2) 第一节双反相器的前端设计流程 (2) 1、画双反相器的visio原理图 (2) 2、编写.sp文件 (2) 第二节后端电路设计 (4) 一、开启linux系统 (4) 2、然后桌面右键重新打开Terminal (6) 双反相器的后端设计流程 (7) 一、schematic电路图绘制 (7) 二、版图设计 (21) 画版图一些技巧: (29) 三、后端验证和提取 (30) 第三节后端仿真 (37) 其它知识 (40)

前端电路设计与仿真 第一节双反相器的前端设计流程1、画双反相器的visio原理图 in V DD M2 M3 out 图1.1 其中双反相器的输入为in 输出为out,fa为内部节点。电源电压V DD=1.8V,MOS 管用的是TSMC的1.8V典型MOS管(在Hspice里面的名称为pch和nch,在Cadence里面的名称为pmos2v和nmos2v)。 2、编写.sp文件 新建dualinv.txt文件然后将后缀名改为dualinv.sp文件 具体实例.sp文件内容如下:

.lib 'F:\Program Files\synopsys\rf018.l' TT 是TSMC用于仿真的模型文件位置和选择的具体工艺角*****这里选择TT工艺角*********** 划红线部分的数据请参考excel文件《尺寸对应6参数》,MOS管的W不同对应的6个尺寸是不同的,但是这六个尺寸不随着L的变化而变化。 划紫色线条处的端口名称和顺序一定要一致 MOS场效应晶体管描述语句:(与后端提取pex输出的网表格式相同) MMX D G S B MNAME

ALLEGRO DDR布线规则

ALLEGRO约束规则设置步骤(以DDR为例) Dyyxh@pcbtech tzyhust@https://www.360docs.net/doc/b710142560.html, 本文是我对约束规则设置方面的一些理解,希望对新手能有所帮助.由于本人水平有限, 错误之处难免,希望大家不吝赐教! 在进行高速布线时,一般都需要进行线长匹配,这时我们就需要设置好constraint规则,并 将这些规则分配到各类net group上.下面以ddr为例,具体说明这些约束设置的具体步骤. 1. 布线要求 DDR时钟: 线宽10mil,内部间距5mil,外部间距30mil,要求差分布线,必需精确匹 配差分对走线误差,允许在+20mil以内 DDR地址,片选及其他控制线:线宽5mil,内部间距15mil,外部间距20mil,应走成 菊花链状拓扑,可比ddrclk线长1000-2500mil,绝对不能短 DDR数据线,ddrdqs,ddrdm线:线宽5mil,内部间距15mil,外部间距20mil,最好在 同一层布线.数据线与时钟线的线长差控制在50mil内. 2. 根据上述要求,我们在allegro中设置不同的约束 针对线宽(physical),我们只需要设置3个约束:DDR_CLK, DDR_ADDR,

DDR_DATA 设置好了上述约束之后,我们就可以将这些约束添加到net上了.点击physical rule set 中的attach……,再点击右边控制面板中的more, 弹出对话框 如上图所示,找到ckn0和ckp0,点击apply,则弹出 选中左边列表中的NET_PHYSICAL_TYPE, 在右边空格内输入DDR_CLK, 点击apply, 弹出 即这两个net已经添加上了NET_PHYSICAL_TYPE属性,且值为DDR_CLK. 类似的,可以将DDR数据线,数据选通线和数据屏蔽线的NET_PHYSICAL_TYPE设 为DDR_DATA, DDR地址线,片选线,和其他控制线的NET_PHYSICAL_TYPE设为 DDR_ADDR. 上述步骤完成后,我们就要将已经设好的约束分配到这些net group上. 如下图点击assignment table…… 弹出对话框 如下图所示,我们对不同的信号组选择各自的physical约束 有人可能会问,为什么你这还有area0,area1啊这是因为你的这些约束有的地方不可 能达到的,比如在bga封装的cpu内,你引线出来,线间距不可能达到

ModelSim的前后仿真(Quartus)

利用Quartus5.0实现功能仿真 1)打开一个工程文件。 2)打开Settings设置栏,选择Fitting Settings下的Simulator栏。在右边出现的设置栏中将 “Simulation Mode”的下拉菜单选择“Functional”,即可以实现软件下的功能仿真。(下拉菜单中有“Functional”、“Timing”和“Timing using Fast Timing Model”,分别代表可以在Quartus软件下实现功能仿真,时序仿真和快速时序仿真。最后一项一般不选,如果在Settings->Timing Requirement->More Settings下“Report Combined Fast/Slow Timing” 选项设为“On”,就可以选择最后一项。编译的报告里也会分别列出最快和最慢的时序报告。) 3)选择“Processing”菜单下的“Generate Functional Simulation Netlist”命令,否则将无法 启动仿真。 4)新建一个波形仿真文件,文件后缀名为.vwf。选择File菜单下的New->Other Files->Vector Waveform File。如下图所示,左边空白栏处是节点名的列表区,右边空白栏处是仿真波形的显示区。波形编辑窗口默认时间为1us,如果想改变仿真时间,可以选择Edit菜单下End Time,在弹出的对话框中选择需要的时间。将新建的波形仿真文件保存下来。

5)将需要仿真的信号加入波形编辑窗口。在列表区任一位置双击或者点击右键选择“Insert Node or Bus…”,弹出的对话框点击“Node Finder”按钮。在“Node Finder”界面中点击“List”按钮,有关信号的列表会出现在界面的左边,双击需要观察的信号加入至界面右边。如果工程中用到了很多信号,在左边列表中也会显示很多(Named编辑框默认的是*通配符),可以在Named编辑框中添加需要的信号名称实现模糊查找。界面中“Filter”下拉框中默认的是“Pins: all”,也就是说将要列出的信号都是IO管脚。如果需要观察一些内部信号,可以改变下拉框的参数,比如“Registers: Pre-Synthesis”。下图显示了仿真信号加入波形编辑窗口的情况。对于有些总线信号可以改变其显示的进制格式,比如二进制、八进制、十进制和十六进制。在列表中对应信号点击右键选择 “Properties”,弹出的对话框中选择“Radix”下拉框实现进制的转换。

Allegro PCB设计

第八章Allegro PCB设计 本章主要讲解如何使用Cadence公司的PCB Editor软件来进行印制电路板(PCB)的设计。由于前面已经讲述了焊盘以及PCB封装的制作,本章主要讲解如何创建PCB外形框图符号、PCB Editor的使用、PCB设计的规则设置以及PCB设计的布局、布线等几个方面。 对于一个项目的设计,如果把原理图的设计看作设计的前端,那么PCB设计就是这个项目的后端,PCB设计是由原理图设计来约束、决定的,一个项目的PCB设计是从原理图输出到PCB设计环境开始的。 一、PCB Editor软件介绍 1、PCB Editor软件的打开 在前面的学习过程当中,我们一直是从项目界面中点击“Layout”按钮来启动PCB Editor软件,另一种方法就是直接启动“开始菜单/程序/Allegro SPB 15.5.1/PCB Editor”。 2、Allegro界面 Allegro是Cadence公司的PCB设计工具,提供了一个完整、易操作的PCB 设计环境,其用户界面包括、标题栏、菜单栏、工具栏、编辑窗口、控制面板、状态栏、命令栏及视窗栏组成,如图8_1所示。 8_1

下面详细介绍一下各栏: 1)标题栏 标题栏是显示当前打开的界面的位置及所选的模块信息。 2)菜单栏 Allegro的菜单栏共由File(文件类)、Edit(编辑类)、View(查看类)、Add (添加类)、Display(显示类)、Setup(设置类)、Shape(敷铜类)、Logic(逻辑类)、Place(布局类)、Route(布线类)、Analyze(分析类)、Manufacture(制造类)、Tools(工具类)以及Help(在线帮助)等14个下拉菜单组成。 (1)File 文件类的下拉菜单中的命令主要包括:新建、打开、查看最近的设计及保存文件,输入、输出一些文件信息,查看一些临时文件,打印设置、打印预览、打印、设定文件属性、更改产品模块,录制scr文件及退出命令。 (2)Edit 编辑栏的下拉菜单中主要包括:移动、复制、镜像、选装、更改、删除、敷铜(Z-copy)、负片层处理、调整线、编辑字符、编辑组、编辑属性、编辑网名的属性、前进及返回上一步命令。 (3)View 查看栏的下拉菜单主要是有关界面的操作,如放大显示、缩小、适中显示、颜色的设置、更新及用户自定义界面等命令。 (4)Add 添加栏的下拉菜单主要包括:添加一条线、添加一个圆弧、添加一个圆、添加矩形、添加字符等命令。 (5)Display 显示栏的下拉菜单中包括:各条目颜色的设置、查看信息、测量、查看各属性、高亮显示、取消高亮显示、显示特定的飞线、不显示飞线等命令。 (6)Setup 设置栏的下拉菜单主要是对Allegro的属性进行设置,如制图参数设置、制图状态设置、字号的设置、设置子层、设置叠层结构及材料、设置过孔、设置规则、定义属性、定义列表、设置特定的区域、设置边框及用户自定义的设置等命令。 (7)Shape 敷铜栏的下拉菜单主要是有关正片敷铜的一些命令,这里的敷铜不仅仅是信号层的敷铜,也包括一些区域和禁止布线区域等。此下拉菜单主要包括:敷铜、选中一个敷铜或避让、手动避让、编辑敷铜的边界、删除孤立的铜、改变敷铜的类型、合并敷铜、检查及动态敷铜的设置等。 (8)Logic 逻辑栏的下拉菜单主要是有关逻辑类的操作,如更改网名、定义网络拓扑、定义差分对、定义直流变量、更改位号、定义分部分、终端分配等命令。 (9)Place 布局栏的下拉菜单基本上都是与布局相关的操作,如手动添加元件、自动添加元件、自动布局、调整引脚映射、更新库、更新设置文件等。 (10)Route

Allegro IBIS仿真流程

Allegro IBIS仿真流程 2009-09-27 20:08:36| 分类:Pcb | 标签:|字号大中小订阅 https://www.360docs.net/doc/b710142560.html,/EDA/20090214105502.htm 第一章在Allegro中准备好进行SI 仿真的PCB 板图 1)在Cadence 中进行SI 分析可以通过几种方式得到结果: * Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。 * 使用SpecctreQuest 打开*.brd,进行必要设置,通过处理直接得到结果。这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。 * 直接打开SigXplore 建立拓扑进行仿真。 2)从PowerPCB 转换到Allegro 格式 在PowerPCb 中对已经完成的PCB 板,作如下操作: 在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。 图1.1 在PowerPCB 中输出通用ASC 格式文件

图1.2 PowerPCB 导出格式设置窗口 点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格 式,否则Allegro 不能正确导入。 3)在Allegro 中导入*.ascPCB 板图 在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数: 图1.3 转换阿三次文件参数设置窗口 i. 在的一栏那填入源asc 文件的目录 ii. 在第二栏指定转换必须的pads_in.ini 文件所在目录(也可将此文件拷入工作目录中,此例) iii. 指定转换后的文件存放目录 然后运行“Run”,将在指定的目录中生成转换成功的.brd 文件。 注:pads_in.ini 所在目录路:.\Psd_14.2\Tools\PCB\bin 中。

ASIC设计cadence自动布局布线工具_图文(精)

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。 首先输入 8位全加器 verilog 代码: module adder8(Cout,S,A,Cin; output Cout; output [7:0]S; input [7:0]A; input [7:0]B; input Cin; reg [8:0]SUM; reg [7:0]S; reg Cout; wire [7:0]A,B; always @(Aor B or Cin begin SUM [8:0]=A+B+Cin; S =SUM [7:0]; Cout =SUM [8];

end endmodule 打开综合工具 DC (psyn_gui& File->Read..

读入代码

File->Setup..设置 3 个相关工艺库将带红色 *号的 3

个库设置如下图 Design->CompileDesign.. 编译 Schematic->NewDesign Schematic View.. 可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构 为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。 在 psyn_gui-xg-t> 后输入如下命令 下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm & File->Import->LEF… 导入库的转换格式 注意此文件的路径! File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息

仿真分析步骤

例2:以P214例3.2.1说明仿真过程。 仿真分析步骤(P214例3.2.1) 1、选择菜单:放置(Place)\元件(Component)… 数据库(Database):主数据库(Master Database)组(Group):电源(Sources) 系列(Family):电源(POWER_SOURCES) 元件(Component):直流电压源(DC_POWER),单击OK按钮。 Ctrl+M设置属性后放置(或放置后,双击该元件设置属性): 在参数(value)属性页中V oltage(V)选2V,单击OK(确定)按钮。 同法放置接地:GROUND, 同法放置直流电压源:DC_POWER为4V。 在value属性页中V oltage(RMS)选4V。 同法放置直流电流源:系列(Family):电源(SIGNAL_CURRENT_SOURCES) 元件(Component):DC_CURRENT为3A。 双击该元件,在参数(value)属性页中Current(A)选2V,单击OK(确定)按钮。 同法放置直流电流源:DC_CURRENT为2A。 2、选择菜单:放置(Place)\元件(Component)… 数据库(Database):主数据库(Master Database)组(Group):Basic 系列(Family):RESISTOR 元件(Component):1Ω,单击OK按钮。 Ctrl+M设置属性后放置(或放置后,双击该元件设置属性): 在参数(value)属性页中Resistance选2Ω(Ohm),单击OK(确定)按钮。 按Ctrl+R旋转900。 同法放置其余电阻。 3、选择菜单:放置(Place)\导线(Wire) 连线如图所示,在需要的地方放置节点:放置(Place)\节点(Join)。 4、选择菜单“仿真(Simulate)/分析(Analyses)/ 直流工作点分析(DC Operation Point Analysis)”,弹出图3.2.5 所示分析参数设置对话框,“输出(Output variables)”用于选择所 要分析的结点、电源和电感支路。“电路变量(Variables in circuit)”栏中列出了电路中可以

modelsim+ISE后仿真流程

一、为modelsim 添加ISE的3 个仿真库。 首先,介绍一下这三个库。 Simprim_ver:用于布局布线后的仿真。 Unisim_ver :如果要做综合后的仿真,还要编译这个库。 Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。 我们要为modelsim生成的是标准库。所谓的标准库就是modelsim运行后,会自动加载的库。不过这方面我还不是很肯定。因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。 第二步:新建库,库名起作simprim_ver。我们首先就是要建的就是这个库。 第三步:在modelsim的命令栏上,打下如下命令: vlog -work simprim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src/simprims/*.v (注意斜线的方向是与windows默认方向相反的) 其中的c:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。以下凡是要根据自己系统环境改变的内容,我都会用绿色标出,并加一个下划线。编译完之后,你会发现你的工程文件夹下出现了一个simprim文件夹,里面又有很多个文件夹。这些就是我们要的库了。 第四步:按照上面的方法,编译另外两个库。所需要键入的命令分别如下: vlog –work unisim_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /unisims/*.v vlog -work xilinxcorelib_ver C:/Xilinx/12.4/ISE_DS/ISE/verilog/src /XilinxCoreLib/*.v

modelsim后仿真详解

modelsim后仿真 想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。 首先,我把我用到的软件说明一下。如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。 1, ModelSim Se 6.1b 2, Synplify Pro 7.5.1 3, ISE 5.2i (这个是老了点) 4, WindowsXP(这个应该没有多大的关系) 还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。 下面的这些方法,是我这3天搞出来的。当然也参考了一些文章。如果谁有更方便的方法,欢迎指出来。我的邮箱是vf1983cs@https://www.360docs.net/doc/b710142560.html,。有空大家多交流。 一、为modelsim生成3个库。 首先,介绍一下这三个库。 Simprim_ver:用于布局布线后的仿真。 Unisim_ver :如果要做综合后的仿真,还要编译这个库。 Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。 我们要为modelsim生成的是标准库。所谓的标准库就是modelsim运行后,会自动加载的库。不过这方面我还不是很肯定。因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。 第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。 第二步:新建库,库名起作simprim_ver。我们首先就是要建的就是这个库。

allegro差分布线知识

Doc Scope : Cadence Allegro 15.x Doc Number : SFTCA06001 Author :SOFER Create Date :2005-5-30 Rev :1.00

Allegro 15.x差分线布线规则设置 文档内容介绍: 1.文档背景 (3) 2.Differential Pair信号介绍 (3) 3.如何在Allegro中定义Differential Pair属性 (4) 4.怎样设定Differential Pair在不同层面控制不同线宽与间距 (8) 5.怎样设定Differential Pair对与对之间的间距 (11)

1.文档背景 a)差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,差分线 大多为电路中最关键的信号,差分线布线的好坏直接影响到PCB板子信号质量。 b)差分线一般都需要做阻抗控制,特别是要在多层板中做的各层的差分走线阻抗都 一样,这个一点要在设计时计算控制,否则仅让PCB板厂进行调整是非常麻烦的事情,很多情况板厂都没有办法调整到所需的阻抗。 c)Allegro版本升级为15.x后,差分线的规则设定与之前版本有很大的改变。虽然 Allegro15.0版本已经发布很长时间了,但是还是有很多人对新版本的差分线规则设置不是很清楚。 2.Differential Pair信号介绍 差分信号(Differential Signal)在高速电路设计中的应用越来越广泛,电路中最关键的信号往往都要采用差分结构设计,什么另它这么倍受青睐呢?在PCB设计中又如何能保证其良好的性能呢?带着这两个问题,我们进行下一部分的讨论。何为差分信号?通俗地说,就是驱动端发送两个等值、反相的信号,接收端通过比较这两个电压的差值来判断逻辑状态“0”还是“1”。而承载差分信号的那一对走线就称为差分走线。 差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面: a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。 b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。 c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。 …… 由于篇幅问题,这里对差分信号不做深入介绍了。

利用ModelSim进行的功能仿真,综合后仿真,时序仿真

利用ModelSim进行的功能仿真,综合后仿真,时序仿真 功能仿真,就是在理想状态下(不考虑延迟),验证电路的功能是否符合设计的要求。 功能仿真需要: 1.TestBench或者其他形式的输入激励 2.设计代码(HDL源程序) 3.调用器件的模块定义(供应商提供,如FIFO,RAM等等) 值得一提的是,可以在ModelSim直接编写TestBench,使用View->Source->Show language templates. 综合后仿真(门级仿真),实际上就是将对综合后的门级网表进行仿真,只考虑门延迟,而没有加入时延文件。在功能仿真之后检验综合的结果是否满足功能要求。 综合后仿真需要: 1.综合后的门级网表,注意这里变成了*.vo文件,而不是原来功能仿真中所需要的HDL源代码. 2.测试激励 3.元件库Altera的仿真库位置为 *:\altera\quartus\eda\sim_lib 所谓时序仿真,就是在综合后仿真的基础上加上时延文件(sdf文件),综合考虑了路径延迟和门延迟的情况,验证电路是否存在时序违规。 时序仿真需要: 1.综合后的门级网表,注意这里变成了*.vo文件,而不是原来功能仿真中所需要的HDL源代码. 2.测试激励 3.元件库Altera的仿真库位置为 *:\altera\quartus\eda\sim_lib 4.较门级仿真还需要具有包含时延信息的反标记文件*.sdf 可以有两种方法实现门级仿真,或时序仿真。

1.工程编译成功后,自动启用ModelSim来运行门级仿真,前提是要在Quartus II的Options中设置好ModelSim的路径(和有些参考PDF上说的环境变量好像无关,至少我用的Quartus II 9.0 Web Edtion是这样的)具体方法是,进入Quartus9.0->Tools->Options,在Categroy里选中General 下的EDA Tool Options,在ModelSim右边的Location of Executable中双击来改变路径,就并且在工程中设置了自动启动ModelSim,就可以自动启用了。 1.在EDA Tool Settings,首先将仿真工具设置为ModelSim,然后点击让它自动启动。 2.NativeLink settings中选择testbench,完成相关的设置,例如test bench name,top level module in test bench,Design instance name in test bench,仿真时间,然后编译时会自动启动ModelSim然后完成所有操作,大概这就是Altera所指的和很多EDA工具的无缝连接。 另外一种方法,则是现在quartus ii中生成门级网表和延时文件,然后调用ModelSim进行仿真 1.在quartus ii设置仿真工具为ModelSim,这样设置完成后,在当前目录下会生成一个simulation的目录,该目录下有一个simulation文件夹,里面包含了网标文件和时延反标文件,vhdl语言对应的是网表文件为*.vho,时延文件为*.sdo。Verilog则为*.vo,*.sdo。 2.建立库并映射到物理目录,编译TestBench,执行仿真。 对库的理解: 我想所谓库,实际上就是一个代替文件夹的符号,区别就是,库中的文件的表述皆是经过了编译的实体或者module,一切操作都在库中进行。 ModelSim有两种库,一种是资源库,一种是工作库(默认名为work,保存当前工程下已通过编译的所有文件,资源库放置work库已编译文件所要调用的资源)。所以编译前,一定要有work库,而且只能有一个。

FPGA仿真流程

QuartusII的设计流程 QuartusII软件的使用方法 一、设计输入 1.建立工程 任何一项设计都是一项工程(Project),都必须首先为此工程建立一个放置与此工程相关的所有设计文件的文件夹。此文件夹将被EDA软件默认为工作库(Work Library)。一般,不同的设计项目最好放在不同的文件夹中,而同一工程的所有文件都必须放在同一文件夹中。 首先建立工作库目录,以便存储工程项目设计文件。在D盘下新建文件夹并取名Mydesign。双击QuartusII软件启动图标,即可启动QuartusII软件,启动界面如图1-2所示。 使用New Project Wizard 可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称,还可以指定要在工程中使用的设计文件、其他源文件、用户库和EDA 工具,以及目标器件系列和具体器件等。在此要利用“New Preject

Wizard”工具选项创建此设计工程,并设定此工程的一些相关的信息,如工程名、目标器件、综合器、仿真器等。(1)打开建立新工程管理窗。选择菜单File→New Preject Wizard 命令,即弹出“工程设置”对话框(图1-3),以此来建立新的工程。 (2)在单击图1-3后,出现了设置工程的基本信息,如图1-4所示。单击此对话框最上一栏右侧的“… ”按钮,可以选择工程存放在硬盘上的位置,此例中将工程放在D盘Mydesign文件夹下。这三行的第一行的d:\Mydesign表示工程所在的工作库文件夹;第二行的half_add 表示此项工程的工程名,工程名可以取任何其他的名,也可直接用顶层文件的实体名作为工程名,在此就是按这种方式取的名;第三行是当前工程顶层文件的实体名,这里即为half_add。 (2)将设计文件加入工程中。单击图1-4中的Next 按钮,弹出对话框如图1-5所示,在对话框中单击File name 右侧的“… ”按钮,可以将与工程相关的所有VHDL 文件(如果有的话)加入进此工程,此工程文件加入的方法有两种:第1 种方法是单击“Add … ”按钮,从工程目录中选出相关的VHDL 文件;第2 种方法是单击Add All 按钮,将设定