双端口存储器原理实验

实验名称双端口存储器原理实验

实验时间2011年10月20日实验地点6308 实验人

姓名楚阵合作者

学号200948140518 实验小组

实验成绩:

评阅教师签名:

一.实验目的

1.了解双端口静态随机存储器IDT7132的工作特性及使用方法。

2.了解半导体存储器怎样存储和读出数据。

3.了解双端口存储器怎样进行并行读写。

二.实验内容及实验结果记录

1,先填好下表,然后根据该表将有关控制信号和二进制考官对应接好

(实验处于单拍状态)DP DB DZ (禁止IA R、ALU、RF向DBUS

送数据)

RS_BUS# IAR_BUS# ALU_BUS

(AR2从DBUS取得地址数

据)

M3

1 0 0 1 1 0 1

CEL# LRW CER LDAR1 LDAR2 SW_BUS# LDIR

K0 K1 K2 K3 K4 K5 K6

2.向存储器RAM中写数,并读出进行检查

操作AR1/AR2 IR/DBUS QD SW0-SW7 K0 K1 K2 K3 K4 K5 K6

数据00H 送00H单元地址00H

—>AR1

AR1 DBUS 1 00000000 1 1 0 1 0 0 0

数据00H

—>00H单

元

AR1 DBUS 1 00000000 0 0 0 0 0 0 0

数据11H 送10H单元地址10H

—>AR1

AR1 DBUS 1 00010001 1 1 0 1 0 0 0

数据110H

—>10H单

元

AR1 DBUS 1 00010000 0 0 0 0 0 0 0

数据22H 送20H单元地址20H

—>AR1

AR1 DBUS 1 00100010 1 1 0 1 0 0 0

数据22H

—>20H单

元

AR1 DBUS 1 00100000 0 0 0 0 0 0 0

据33H送30H单

元地址30H

—>AR1

AR1 DBUS 1 00110011 1 1 0 1 0 0 0

数据33H

—>30H单

元

AR1 DBUS 1 00110000 0 0 0 0 0 0 0

数据44H 送40H单元地址40H

—>AR1

AR1 DBUS 1 01000100 1 1 0 1 0 0 0

数据44H

—>40H单

元

AR1 DBUS 1 01000000 0 0 0 0 0 0 0

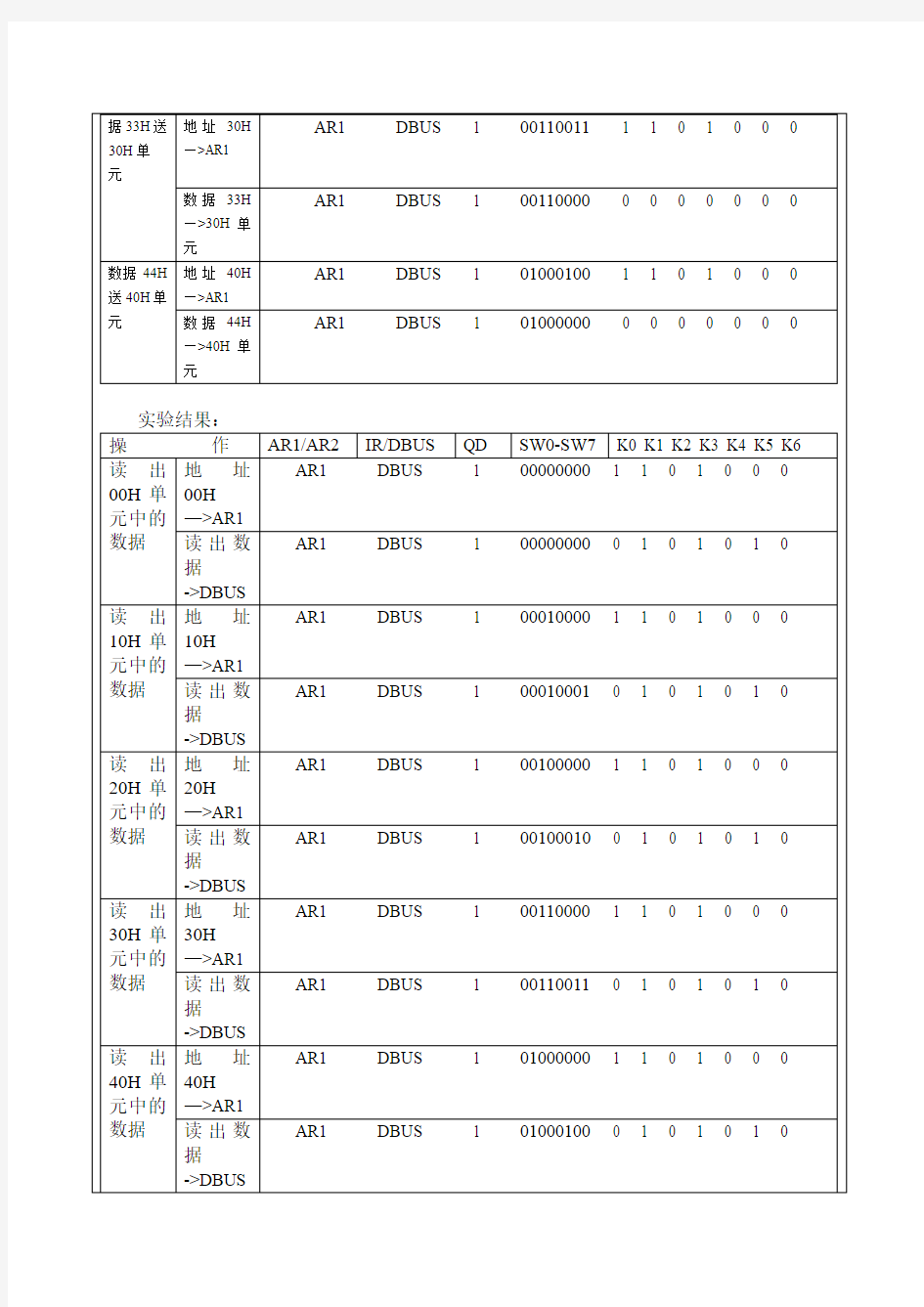

实验结果:

操作AR1/AR2 IR/DBUS QD SW0-SW7 K0 K1 K2 K3 K4 K5 K6

读出00H单元中的数据地址

00H

—>AR1

AR1 DBUS 1 00000000 1 1 0 1 0 0 0

读出数

据

->DBUS

AR1 DBUS 1 00000000 0 1 0 1 0 1 0

读出10H单元中的数据地址

10H

—>AR1

AR1 DBUS 1 00010000 1 1 0 1 0 0 0

读出数

据

->DBUS

AR1 DBUS 1 00010001 0 1 0 1 0 1 0

读出20H单元中的数据地址

20H

—>AR1

AR1 DBUS 1 00100000 1 1 0 1 0 0 0

读出数

据

->DBUS

AR1 DBUS 1 00100010 0 1 0 1 0 1 0

读出30H单元中的数据地址

30H

—>AR1

AR1 DBUS 1 00110000 1 1 0 1 0 0 0

读出数

据

->DBUS

AR1 DBUS 1 00110011 0 1 0 1 0 1 0

读出40H单元中的数据地址

40H

—>AR1

AR1 DBUS 1 01000000 1 1 0 1 0 0 0

读出数

据

->DBUS

AR1 DBUS 1 01000100 0 1 0 1 0 1 0

操作AR1/AR2 IR/DBUS QD SW0-SW7 K0 K1 K2 K3 K4 K5 K6

读出00H单元中的数据地址

00H

—>AR1

AR2 IR 1 00000000 1 1 0 0 1 0 0

读出数

据->IR

AR2 IR 1 00000000 1 1 1 0 0 0 1

读出10H单元中的数据地址

10H

—>AR1

AR2 IR 1 00010000 1 1 0 0 1 0 0

读出数

据->IR

AR2 IR 1 00010001 1 1 1 0 0 0 1

读出20H单元中的数据地址

20H

—>AR1

AR2 IR 1 00100000 1 1 0 0 1 0 0

读出数

据->IR

AR2 IR 1 00100010 1 1 1 0 0 0 1

读出30H单元中的数据地址

30H

—>AR1

AR2 IR 1 00110000 1 1 0 0 1 0 0

读出数

据->IR

AR2 IR 1 00110011 1 1 1 0 0 0 1

读出40H单元中的数据地址

40H

—>AR1

AR2 IR 1 01000000 1 1 0 0 1 0 0

读出数

据->IR

AR2 IR 1 01000100 1 1 1 0 0 0 1

三.总结实验过程中调试所遇到的问题和解决方法,写出经验和体会。

通过做本次实验,基本上了解了往存储器中写入数据的流程,从存储器中读出数据,并且将数据写入指令寄存器IR的过程。但是在做实验时,必须十分认真,有时候线头松动等的小问题也会对实验造成很大的影响。遇到问题还得更加认真细心的检查,一个个的排除造成错误的可能情况,这样问题才会得到解决。

静态存储器扩展实验报告

静态存储器扩展实验报告告圳大学实验报深

微机原理与接口技术 课程名称: 静态存储器扩展实验实验项目名称: 信息工程学院学院: 专业:电子信息工程

指导教师:周建华 32012130334 学号:班级:电子洪燕报告人:班 2014/5/21 实验时间: 实验报告提交时间:2014/5/26 教务部制. 一.实验目的与要求: 1. 了解存储器扩展的方法和存储器的读/写。 2. 掌握CPU对16位存储器的访问方法。

二.实验设备 PC机一台,TD-PITE实验装置或TD-PITC实验装置一套,示波器一台。 三.实验原理VCC28A141WE27A122A1326A73A8254A6存储器是用来存储信息的A924A55A1123A46OE22A3762256A10218A2CS209A1部件,是计算机的重要组成部D719A010D618D011D517D112D416D213D315GND14管组成的是由MOS分,静态RAM触发器电路,每个触发器可以存放1位

信息。只要不掉电,所储存的信息就不会丢失。因此,静态RAM工作稳定,不要外加刷新电路,使用方便。 但一般SRAM 的每一个触发器是由6个晶体管组成,SRAM 芯片的集成度不会太高,目前较常用的有6116(2K×8位),图4.1 62256引脚图6268位)622532位。本验平台上选. 用的是62256,两片组成32K×16位的形式,共64K字节。 62256的外部引脚图如图4.1所示。 本系统采用准32位CPU,具有16位外部

数据总线,即D0、D1、…、D15,地址总线为BHE#(#表示该信号低电平有效)、BLE #、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BHE#和BLE#选通。 存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BHE#和BLE#同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要

实验十四 存储器扩展机读写实验

实验十四存储器扩展机读写实验 一、实验目的 (1)通过阅读并测试示例程序,完成程序设计题,熟悉静态RAM的扩展方法。 (2)了解8086/8088与存储器的连接,掌握扩展存储器的读写方法。 二、实验内容 1.实验原理(62256RAM介绍) 62256是32*8的静态存储器,管脚如图所示。其中:A0~A14为地址线,DB0~DB7为数据线,/cs为存储器的片选,/OE为存储器数据输出选通信号,/WE为数据写入存储器信号。62256工作方式如下图。 /CS /WE /OE 方式DB-~DB7 H X X 未选中高阻 L H H 读写禁止高阻 L L H 写IN L H L 读OUT 2.实验内容 设计扩展存储电器的硬件连接图并编制程序,讲字符A~Z循环存入62256扩展RAM 中,让后再检查扩展存储器中的内容。 三、程序设计 编写升序,将4KB扩展存储器交替写入55H和0AAH。 程序如下: RAMADDR EQU 0000H RAMOFF EQU 9000H COUNT EQU 800H CODE SEGMENT ASSUME CS:CODE START: PROC NEAR MOV AX,RAMADDR MOV DS,AX MOV BX,RAMOFF MOV CX,COUNT MOV DL,55h MOV AX ,0AAH REP: MOV [BX],DL INC BX MOV [BX],AX INC BX LOOP REP JMP $ CODE ENDS END START 四、实验结果 通过在软件上调试,运行时能够看到内存地址的改变,证明此扩展的程序成功实现了。 五、实验心得

实验一扩展存储器读写实验

实验一:扩展存储器读写实验 一.实验要求 编制简单程序,对实验板上提供的外部存贮器(62256)进行读写操作。 二.实验目的 1.学习片外存储器扩展方法。 2.学习数据存储器不同的读写方法。 三.实验电路及连线 将P1.0接至L1。CS256连GND孔。 四.实验说明 1.单片机系统中,对片外存贮器的读写操作是最基本的操作。用户藉此来熟悉MCS51单片机编程的基本规则、基本指令的使用和使用本仿真实验系统调试程序的方法。 用户编程可以参考示例程序和流程框图。本示例程序中对片外存贮器中一固定地址单元进行读写操作,并比较读写结果是否一致。不一致则说明读写操作不可靠或该存储器单元不可靠,程序转入出错处理代码段(本示例程序通过熄灭一个发光二极管来表示出错)。读写数据的选用,本例采用的是55(0101,0101)与AA(1010,1010)。一般采用这两个数据的读写操作就可查出数据总线的短路、断路等,在实际调试用户电路时非常有效。 用户调试该程序时,可以灵活使用单步、断点和变量观察等方法,来观察程序执行的流程和各中间变量的值。 2.在I状态下执行MEM1程序,对实验机数据进行读写,若L1灯亮说明RAM读

写正常。 3.也可进入LCA51的调试工具菜单中的对话窗口,用监控命令方式读写RAM,在I状态执行SX0000↓ 55,SPACE,屏幕上应显示55,再键入AA,SPACE,屏幕上也应显示AA,以上过程执行效果与编程执行效果完全相同。 注:SX是实验机对外部数据空间读写命令。 4.本例中,62256片选接地时,存储器空间为0000~7FFFH。 五.实验程序框图 实验示例程序流程框图如下: 六.实验源程序: ORG 0000H LJMP START ORG 0040H START:

存储器的工作原理

存储器的工作原理 1、存储器构造 存储器就是用来存放数据的地方。它是利用电平的高低来存放数据的,也就是说,它存放的实际上是电平的高、低,而不是我们所习惯认为的1234这样的数字,这样,我们的一个谜团就解开了,计算机也没什么神秘的吗。 图2

图3 让我们看图2。这是一个存储器的示意图:一个存储器就像一个个的小抽屉,一个小抽屉里有八个小格子,每个小格子就是用来存放“电荷”的,电荷通过与它相连的电线传进来或释放掉,至于电荷在小格子里是怎样存的,就不用我们操心了,你可以把电线想象成水管,小格子里的电荷就像是水,那就好理解了。存储器中的每个小抽屉就是一个放数据的地方,我们称之为一个“单元”。 有了这么一个构造,我们就可以开始存放数据了,想要放进一个数据12,也就是00001100,我们只要把第二号和第三号小格子里存满电荷,而其它小格子里的电荷给放掉就行了(看图3)。可是问题出来了,看图2,一个存储器有好多单元,线是并联的,在放入电荷的时候,会将电荷放入所有的单元中,而释放电荷的时候,会把每个单元中的电荷都放掉,这样的话,不管存储器有多少个单元,都只能放同一个数,这当然不是我们所希望的,因此,要在结构上稍作变化,看图2,在每个单元上有个控制线,我想要把数据放进哪个单元,就

给一个信号这个单元的控制线,这个控制线就把开关打开,这样电荷就可以自由流动了,而其它单元控制线上没有信号,所以开关不打开,不会受到影响,这样,只要控制不同单元的控制线,就可以向各单元写入不同的数据了,同样,如果要某个单元中取数据,也只要打开相应的控制开关就行了。 2、存储器译码 那么,我们怎样来控制各个单元的控制线呢?这个还不简单,把每个单元的控制线都引到集成电路的外面不就行了吗?事情可没那么简单,一片27512存储器中有65536个单元,把每根线都引出来,这个集成电路就得有6万多个脚?不行,怎么办?要想法减少线的数量。我们有一种方法称这为译码,简单介绍一下:一根线可以代表2种状态,2根线可以代表4种状态,3根线可以代表几种,256种状态又需要几根线代表?8种,8根线,所以65536种状态我们只需要16根线就可以代表了。 3、存储器的选片及总线的概念 至此,译码的问题解决了,让我们再来关注另外一个问题。送入每个单元的八根线是用从什么地方来的呢?它就是从计算机上接过来的,一般地,这八根线除了接一个存储器之外,还要接其它的器件,如图4所示。这样问题就出来了,这八根线既然不是存储器和计算机之间专用的,如果总是将某个单元接在这八根线上,就不好了,比如这个存储器单元中的数值是0FFH另一个存储器的单元是00H,那么

存储器扩展实验

实验5 存储器扩展实验 一、实验目的 1.掌握PC存储器扩展的方法。 2.熟悉6264芯片的接口方法。 3.掌握8031内部RAM和外部RAM的数据操作 二、实验设备 PC机、星研Star16L仿真器系统+仿真头PODPH51(DIP)、EL-Ⅱ型通用接口板实验电路,PROTEUS仿真软件。 三、实验内容 1)向外部存储器的7000H到8000H区间循环输入00~0FFH数据段。设置断点,打开外部数据存储器观察窗口,设置外部存储器的窗口地址为7000H—7FFFH。全速运行程序,当程序运行到断点处时,观察7000H—7FFFH的内容是否正确。 四、实验原理 实验系统上的两片6264的地址范围分别为:4000H~5FFFH,6000H~7FFFH,既可作为实验程序区,也可作为实验数据区。6264的所有信号均已连好。(3000H~3FFFH也可用) 五、实验方法 1、运用PROTUES软件进行虚拟仿真实验。按照实验要求用PROTUES软件绘制电路,编制程序,并通过调试。 2、运用星研仿真系统进行实际系统仿真实验。将星研仿真器与微机和目标板相互连接构成完整的硬件仿真系统,按照实验要求在通用实验板上进行硬件系统连接,并用星研仿真器进行系统仿真运行调试。 3、实验说明 在采用星研仿真时,若CPU选型为8051则,应将P2、P3口修改为总线模式(默认为IO口模式)。若为8031CPU则无此选项,因此不必修改。 4、星研仿真器设置时,注意,在项目工作环境设置选项中的存储器借出方式中,不能借用仿真器的外部数据空间(直接选择默认方式即可),否则无法正确测试实验箱上的存储器。 5、利用星研仿真器,在选择用户板外部RAM方式下,可以在存储器窗口中,通过直接对外部存储器单元的内容进行修改来确定该单元是否可用,可以修改的单元,表明用户可用,如果无法修改(无论键盘输入任何数字与字符,始终显示FF),则表明该存储单元不可用。 六、实验电路 1、PROTEUS 仿真电路

有机浮栅存储器的工作原理

有机浮栅存储器的工作原理 1.1 有机场效应晶体管(OFET)的基本结构和工作原理 1.1.1 有机场效应晶体管的基本结构 有机场效应晶体管的具有很多的优点:材料来源广、可以大量生产和能够实现低成本、可与柔性衬底兼容。应用前景十分广泛,如有机集成电路、存储器件、柔性显示屏等。自20世纪80年代有机场效应晶体管诞生,有机场效应晶体管得到迅速发展,到目前为止,一些有机场效应晶体管已经得到实用化的程度,在载流子迁移率、开关电流比方面已经可与非晶硅相媲美。 有机场效应晶体管按照源漏极和有机半导体的相对位置有两种结构(图2-1)底接触和顶接触,按照沟道中起传输作用的载流子的种类的不同,可以分为两种:n沟道场效应晶体管和p沟道场效应晶体管[8,9]。 图2-1 两种OFET结构:顶接触(左) 底接触(右) 1.1.2 有机场效应晶体管的工作原理 有机场效应晶体管的工作原理与无机场效应晶体管的工作原理类似。下面通过对一个顶接触的p-沟的OFET进行分析,如图2-2所示:

图2-2 有机场效应管的原理示意图 我们在栅极上施加一个相对于源极的负偏压时(源极是接地的),栅极表面出现负电荷,相应的在沟道表面感应出正电荷。当增大栅极电压时,在沟道表面形成积累层并进而形成含有可动载流子-空穴-的薄层,源漏之间的电流主要是由空穴贡献,这是与无机场效应晶体管最大的不同,通过控制栅极电压来改变沟道中空穴的数量,进而控制漏极电流[10]。 由于我们使用的是有机材料作为有源区,我们在引用传统的EEPROM的模型时必须要进行修改。在本文中,我们考虑了Pool-Frenkel效应[11],在半导体和绝缘层接触面的电荷,接触势垒,陷阱效应,采用修正以后的漂移-扩散模型(DDM)[12],借助TCAD求解泊松方程和连续性方程(2-1),(2-2),(2-3)[13],来模拟有机场效应晶体管的电学特性。 其中为静电势,为有机材料的介电常数,G为产生率, 和分别为捕获的电子和空穴的密度,和分别为电子和空穴的 电流密度。R是电子和空穴的复合率。[14,15],

存储器和IO扩展实验,计算机组成原理

科技学院 课程设计实验报告 ( 2014--2015年度第一学期) 名称:计算机组成原理综合实验题目:存储器和I/O扩展实验 院系:信息工程系 班级: 学号: 学生姓名: 指导教师:李梅王晓霞 设计周数:一周 成绩: 日期:2015 年1 月

一、目的与要求 1. 内存储器部件实验 (1)熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处;学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。 (2)理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案; (3)了解静态存储器系统使用的各种控制信号之间正常的时序关系; (4)了解如何通过读、写存储器的指令实现对58C65 ROM芯片的读、写操作; (5)加深理解存储器部件在计算机整机系统中的作用。 2. I/O口扩展实验 学习串行口的正确设置和使用。 二、实验正文 1.主存储器实验内容 1.1实验的教学计算机的存储器部件设计(说明只读存储器的容量、随机读写器的容量,各选用了什么型号及规格的芯片、以及地址空间的分布) 在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区(ROM,存放监控程序等) 和随读写存储区(RAM)两部分,ROM存储区选用4片长度8位、容量8KB 的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片 实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分 成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序, 2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作为监 控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩 展内存容量(存储器的字、位扩展)的教学实验。 1.2扩展8K字的存储空间,需要多少片58C65芯片,58C65芯片进行读写时的特殊要求 要扩展8K字的存储空间,需要使用2片(每一片有8KB容量,即芯片内由8192个单元、每个单元由8个二进制位组成)存储器芯片实现。对 58C65 ROM芯片执行读操作时,需要保证正确的片选信号(/CE)为低点平, 使能控制信号(/OE)为低电平,读写命令信号(/WE)为高电平,读58C65 ROM 芯片的读出时间与读RAM芯片的读出时间相同,无特殊要求;对58C65 ROM 芯片执行写操作时,需要保证正确的片选信号(/CE)为低电平,使能控制信 号(/OE)为高电平,读写命令信号(/WE)为低电平,写58C65 ROM芯片的 维持时间要比写RAM芯片的操作时间长得多。为了防止对58C65 ROM芯片执 行误写操作,可通过把芯片的使能控制引脚(/OE)接地来保证,或者确保读 写命令信号(/WE)恒为高电平。 1.3在实验中思考为何能用E命令直接写58C65芯片的存储单元,而A命令则有时不正确;

微机原理实验---存储器的扩展实验

深圳大学实验报告 课程名称:_____________ 微机计算机设计__________________ 实验项目名称:静态存储器扩展实验______________ 学院:_________________ 信息工程学院____________________ 专业:_________________ 电子信息工程____________________ 指导教师:____________________________________________ 报告人:________ 学号:2009100000班级:<1>班 实验时间:_______ 2011.05. 05 实验报告提交时间:2011. 05. 31 教务处制 一、实验目的 1. 了解存储器扩展的方法和存储器的读/ 写。 2. 掌握CPU寸16位存储器的访问方法。 二、实验要求

编写实验程序,将OOOOH H OOOFH共16个数写入SRAM的从0000H起始的一段空间中,然后通过系统命令查看该存储空间,检测写入数据是否正确。 三、实验设备 PC 机一台,TD-PITE 实验装置或TD-PITC 实验装置一套。 四、实验原理 1、存储器是用来存储信息的部件,是计算机的重要组成部分,静态RAM是由MOS 管组成的触发器电路,每个触发器可以存放1 位信息。只要不掉电,所储存的信息就不会丢失。此,静态RAM工作稳定,不要外加刷新电路,使用方便。 2、本实验使用两片的62256芯片,共64K字节。本系统采用准32位CPU具有16 位外部数据总线,即D0 D1、…、D15,地址总线为BHE^(#表示该信号低电平有效)、BLE#、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BH四和BLE#选通。存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BH即和BLE #同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要两个时钟周期,第一个时钟周期BH即有效,访问奇字节;第二个时钟周期BLE#有效,访问偶字节。处理器访问字节只需要一个时钟周期,视其存放单元为奇或偶,而BH四或BLE#有效,从而选通奇体或偶体。 五、实验过程 1、按图接线好电路。 2. 编写实验程序,经编译、链接无误后装入系统。 实验部分代码如下: STACK SEGMENT STACK DW 32 DUP(?) STACK ENDS CODE SEGMENT START PROC FAR ASSUME CS:CODE MOV AX, 8OOOH ; MOV DS, AX AAO: MOV SI, OOOOH ; MOV CX, OO1OH MOV AX, OOOOH AA1: MOV [SI], AX

存储程序工作原理

一、存储程序工作原理 二、计算机的三个基本能力:一是采用二进制,二是能够存储程序,三是能够自动地执行程序。 三、计算机是利用“存储器”(内存)来存放所要执行的程序的,而称之为CPU的部件可以依次从存储器中取出程序中的每一条指令,并加以分析和执行,直至完成全部指令任务为止。 四、总线(Bus):是微型计算机中用于连接CPU、存储、输入/输出接口等部件的一组信号线和控制电路,是系统内各种部件之间共享的一组公共数据传输线路。 五、回收站:硬盘的部分存储区域 六、文件:新建打开保存另存为页面设置打印 七、编辑:撤消重复复制粘贴查找替换 八、格式:字体段落分栏文字方向背景 九、表格:绘制表格插入表格合并单元格绘制斜线表头表格属性 十、计算机网络是指通过通信设备将地理位置分散、具有独立功能的多个计算机连接起来,按照协议进行数据通信,以实现资源共享和信息传递的系统。 十一、计算机网络的物理组成:计算机传输介质连接设备 十二、网络连接设备:网络适配器集线器交换机中继器网桥路由器网关调制解调器 十三、国标字符集有6763个常用汉字 十四、由三部分组成: 十五、字母、数字和各种符号,共687个 十六、一级常用汉字,共3755个,按汉语拼音排列 十七、二级常用汉字,共3008个,按偏旁部首排列 十八、基本思想:先把编制的程序存储起来,再用程序来控制计算机的运行. 十九、“存储程序”工作原理:在计算机中设置存储器,将二进制编码表示的计算步骤与数据一起存放在存储器中,机器一经启动,就能按照程序指定的逻辑顺序依次取出存储内容进行译码和处理,自动完成由程序所描述的处理工作 二十、计算机网络的概念:概念:计算机网络是通信技术与计算机技术相结合的产物,是以资源共享为主要目的、以通信媒体互连起来的计算机的集合二十一、计算机:服务器、客户机和同位体。 二十二、传输介质:计算机与通信设备之间、以及通信设备之间都通过传输介质互连,具体有双绞线、同轴电缆、光纤、电话线、微波信道、卫星信道等。 二十三、通信设备:其作用是为计算机转发数据,具体有交换机、集线器、路由器、调制解调器等。 二十四、中国教育科研网(CERNET )中国公用信息网(ChinaNET )中国科学技术网(CSTNET )中国金桥信息网(CHINAGBN) 1.阐述系统软件和应用软件的分类和作用。 系统软件:操作系统、程序设计语言、语言处理程序、诊断程序、数据库管理系统。 应用软件:用于科学计算方面的数学计算软件包、统计软件包;文字处理软件包;图像处理软件包;各种财务管理、税务管理、工业控制等行业软件。

存储器扩展实验

存储器扩展实验 1.实验目的 1. 了解存储器的扩展方法及其对存储器的读/写。 2. 掌握CPU对8/16位存储器的访问方法。 2.实验设备 PC机一台,TD-PITC实验箱。 3.实验内容 编写程序,往扩展存储器中传送有规律的数据(如5555H、AAAAH或顺序递增的数据等,以便于观察写入是否正确),然后通过Tdpit软件中的“扩展存储区数据显示窗口”查看该存储空间,检测写入数据是否正确。 1)循环传送16位规则字到扩展存储器(共32768个字); 2)循环传送16位非规则字到扩展存储器(共32768个字); 3)循环传送字节数据到扩展存储器(共32768个字节)。 关于规则字和非规则字的含义见以下16位存储器操作的说明。 4.实验原理 1)SRAM 62256介绍 SRAM(静态RAM)的基本存储元是由MOS管组成的触发器电路构成,每个触发器可以存放1位信息。只要不掉电,所储存的信息就不会丢失。目前较常用的SRAM有6116(2K×8),6264(8K×8)和62256(32K×8)。TD-PITC实验箱内使用了2片62256构成32K×16的扩展存储器模块。62256的引脚如图1所示。 图1 62256引脚图 2)16位总线的存储器接口 TD-PITC实验箱中的16位系统总线提供了XA1~XA20、#BHE、#BLE、MY0等信号用于扩展存储器的读写操作。MY0是系统为扩展存储器提供的片选信号,其地址空间为D8000H~DFFFFH,XA1~XA20提供了16位(2字节)存储单元的地址,#BHE和#BLE用来确定访问16位存储单元中的低8位还是高8位,#BLE有效时允许访问低8位(D7-D0),#BHE有效时允许访问高8位(D15-D8)。其对应关系如表1所示。

静态存储器扩展实验报告

静态存储器扩展实验报告

深圳大学实验报告 实验报告提交时间:2014/5/26 教务部制

一.实验目的与要求: 1. 了解存储器扩展的方法和存储器的读 / 写 2. 掌握 CPU 对 16 位存储器的访问方法。 二.实验设备 PC 机一台, TD-PITE 实验装置或 TD-PITC 实验 装置 一套,示波器一台。 触发器电路,每个触发器可以存放 1 位信息 只要不掉电, 所储存的信息就不会丢失。 因此, 静态 RAM 工作稳定,不要外加刷新电路,使用 方便 但一般 SRAM 的 每一个触发器是由 6 个晶体管 组成, SRAM 芯片的集成度不会太高, 目前较常用的有 6116 (2K ×8 位), 图 4.1 62256 引脚图 6264(8K ×8 位)和 62256(32K ×8 位)。本实 验平台上选 用的是 62256,两片组成 32K ×16 位的形式, 共 64K 字节。 62256 的外部引脚图如图 4.1 所示。 三.实验原理 存储器是用来存储信息的 部件,是计算机的重要组成部 分,静态 RAM 是由 MOS 管组成的 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 D0 D1 D2 GND 1 28 2 27 3 26 4 2 5 5 24 6 23 78 62256 2221 9 20 10 19 11 18 12 17 13 16 14 15 VCC WE A13 A8 A9 A11 OE A10 CS D7 D6 D5 D4 D3

DATA D15:D0

CS# WR# DATA D15:D8 D7:D0 DATA D15:D8 D7:D0 写规则字(左)和非规则字(右)简图4.2 单时序图

RAM-ROM-EEPROM存储器工作原理

RAM-ROM-EEPROM存储器工作原理

一.基本工作原理 1、存储器构造 存储器就是用来存放数据的地方。它是利用电平的高低来存放数据的,也就是说,它存放的实际上是电平的高、低,而不是我们所习惯认为的1234这样的数字,这样,我们的一个谜团就解开了,计算机也没什么神秘的吗。 图1 图2 让我们看图1。这是一个存储器的示意图:

一个存储器就像一个个的小抽屉,一个小抽屉里有八个小格子,每个小格子就是用来存放“电荷”的,电荷通过与它相连的电线传进来或释放掉,至于电荷在小格子里是怎样存的,就不用我们操心了,你可以把电线想象成水管,小格子里的电荷就像是水,那就好理解了。存储器中的每个小抽屉就是一个放数据的地方,我们称之为一个“单元”。 有了这么一个构造,我们就可以开始存放数据了,想要放进一个数据12,也就是00001100,我们只要把第二号和第三号小格子里存满电荷,而其它小格子里的电荷给放掉就行了(看图2)。可是问题出来了,看图1,一个存储器有好多单元,线是并联的,在放入电荷的时候,会将电荷放入所有的单元中,而释放电荷的时候,会把每个单元中的电荷都放掉,这样的话,不管存储器有多少个单元,都只能放同一个数,这当然不是我们所希望的,因此,要在结构上稍作变化,看图1,在每个单元上有个控制线,我想要把数据放进哪个单元,就给一个信号这个单元的控制线,这个控制线就把开关打开,这样电荷就可以自由流动了,而其它单元控制线上没有信号,所

以开关不打开,不会受到影响,这样,只要控制不同单元的控制线,就可以向各单元写入不同的数据了,同样,如果要某个单元中取数据,也只要打开相应的控制开关就行了。 2、存储器译码 那么,我们怎样来控制各个单元的控制线呢?这个还不简单,把每个单元的控制线都引到集成电路的外面不就行了吗?事情可没那么简单,一片27512存储器中有65536个单元,把每根线都引出来,这个集成电路就得有6万多个脚?不行,怎么办?要想法减少线的数量。我们有一种方法称这为译码,简单介绍一下:一根线可以代表2种状态,2根线可以代表4种状态,3根线可以代表几种,256种状态又需要几根线代表?8种,8根线,所以65536种状态我们只需要16根线就可以代表了。 3、存储器的选片及总线的概念 至此,译码的问题解决了,让我们再来关注另外一个问题。送入每个单元的八根线是用从什么地方来的呢?它就是从计算机上接过来的,一般地,这八根线除了接一个存储器之外,还要接其它的器件。这样问题就出来了,这八根线既然

单片机实验 数据存储器和程序存储器扩展

实验四数据存储器和程序存储器扩展 一、实验目的 1、学习片外存储器扩展方法 2、学习数据存储器不同的读写方法 3、学习片外程序存储器的读方法 二、实验说明 本次实验使用1片6264SRAM,作为片外扩展的数据存储器,对其进行读写。先向6264中写入整数1~200,然后将其逆向复制到地址0x0100处。注意单片机ALE引脚与74LS373的LE引脚的连接,直至锁存由单片机的ALE控制,另外还要注意单片机读/写控制引脚、与6264的连接。RD WR 三、实验线路图 四、实验步骤 1、先建立文件夹“ex4”,然后建立“ex4”工程项目,最后建立源程序文件“ex4.c”,输入如下源程序; /*用6264扩展内存*/ //说明:先向6264中写入整数1~200,然后将其逆序复制到0x0100处 #include

for(i=0;i<200;i++) { XBYTE[i]=i+1; } //将6264中的1~200逆向拷贝到0x0100地址开始处 for(i=0;i<200;i++) { XBYTE[i+0x0100]=XBYTE[199-i]; } //扩展内存数据处理完成后LED点亮 LED=0; while(1); } 2、用Proteus软件仿真 经过Keil软件编译通过后,可利用Proteus软件仿真。在Proteus ISIS编辑环境中绘制仿真电路图。打开配套实验3仿真原理图文件“ex4.DSN”,将编译好的“ex4.hex”文件载入 A T89C51,启动仿真。 五、思考题 实验仅使用了一片6264SRAM对数据内存进行扩展,要求在电路中使用EPROM27512(64KB)对程序内存进行扩展,将HEX文件移到27512中执行,注意将EA接地。 /*用6264扩展内存*/ //说明:先向6264中写入整数1~200,然后将其逆序复制到0x0100处 #include

静态MOS存储器工作原理

静态MOS存储器 1.基本存储元 (1)六管静态MOS存储元 A、电路图: 由两个MOS反相器交叉耦合而成的双稳态触发器。 B、存储元的工作原理: 假设:T0管导通,T1管截止:存0; T0管截至,T1管导通:存1; 说明:MOS管有三极,如果栅极为高电平,则源极和漏极导通。如果栅极为低电平,则源极和漏极截至。 ①写操作。在字线上加一个正电压的字脉冲,使T2、T3管导通。若要写“0”,无论该位存储元电路原存何种状态,只需使写“0”的位线BS0电压降为地电位(加负电压的位脉冲),经导通的T2管,迫使节点A的电位等于地电位,就能使T1管截止而T0管导通。 写入1,只需使写1的位线BS1降为地电位,经导通的T3管传给节点B,迫使T0管截止而T1管导通。 写入过程是字线上的字脉冲和位线上的位脉冲相重合的操作过程。 ②读操作。只需字线上加高电位的字脉冲,使T2、T3管导通,把节点A、B分别连到位线。若该位存储电路原存“0”,节点A是低电位,经一外加负载而接在位线BS0上的外加电

源,就会产生一个流入BS0 线的小电流(流向节点A经T0 导通管入地)。“0”位线上BS0 就从平时的高电位V下降一个很小的电压,经差动放大器检测出“0”信号。 若该位原存“1”,就会在“1”位线BS1 中流入电流,在BS1 位线上产生电压降,经差动放大器检测出读“1”信号。 读出过程中,位线变成了读出线。读取信息不影响触发器原来状态,故读出是非破坏性的读出。 ③若字线不加正脉冲,说明此存储元没有选中,T2 ,T3 管截止,A、B结点与位/读出线隔离,存储元存储并保存原存信息。 (2)8管静态MOS存储元 A 、 目的:地址的双重译码选择,字线分为X选择线与Y选择线 B 、 实现:需要在6管MOS存储元的A、B节点与位线上再加一对地址选择控制管T7 、T8 ,形成了8管MO BS1 读/写”0” 读/写”1” 位/ 6管MOS 存储电路

存储器实验

南京晓庄学院 信息工程学院 计算机组成原理课程 实 验 报 告 实验名称:存储器实验 年级专业班级:14级计算机科学与技术专业14计算机转本1 班级学号:14131504 姓名:康志勇 时间:2016 年 11月26 日 一、实验目的、要求:

EXD0EXD1EXD2EXD3EXD4EXD5EXD6EXD7 A010A19A28A37A46A55A64A73A825A924A1021A1123A122CS 1 20 CS 226WE 27OE 22D0 11D112D213D315D416D517D618D7 19 U52 6264 G ND V CC AD0AD1AD2AD3AD4AD5AD6AD7 CE` P 1.2P 1.1 图3-5 D13 Q1 2 D24Q2 5 D37Q3 6 D48Q4 9 D513Q5 12 D614Q6 15 D717Q7 16 D818 Q819 CLK 11CLR 1 U3774LS 273 V CC A02A13A24A35A46A57A68A79 B0 18 B1 17 B2 16 B3 15 B4 14 B5 13 B6 12 B7 11 E 19 DIR 1 U5174LS 245 S WB`V CC G ND KD6KD5KD4KD3KD0 KD2KD7KD1输入数据 L Z D 0-L Z D 7 UN2A 74LS 08 LDAR T 32 13 L D 0-L D 7L A D 0-L A D 7 45 6T 3WE UN2B 74001、掌握静态随机存取存储器RAM 工作特性及数据的读写方法。 二、实验仪器设备、器件及环境: 仪器设备名称 规格型号 编号 备注 模型机运算器 DVCC-C8JH 20112034 三、实验方法、原理: 图1.1.1 主存储器单元电路主要用于存放实验机的机器指令,如图1.1.1所示,它的数据总线挂在 外部数据总线EXD0~EXD7上;它的地址总线由地址寄存器单元电路中的地址寄存器74LS273(U37)给出,地址值由8个LED 灯LAD0~LAD7显示,高电平亮,低电平灭;在手动方式下,输入数据由8位数据开关KD0~KD7提供,并经一三态门74LS245(U51)连至外部数据总线EXD0~EXD7,实验时将外部数据总线EXD0~EXD7用8芯排线连到内

存储器读写实验

实验一存储器读写实验 一、实验目的 1. 熟悉静态RAM 的使用方法,掌握8088 微机系统扩展RAM 的方法; 2. 掌握静态RAM 读写数据编程方法。 二、实验内容 对指定地址区间的RAM(4000H~43FFH)先进行写数据55AAH,然后将其内容读出再写到5000H~53FFH 中。 三、实验接线图(系统中已连接好) 四、实验步骤 1. 在PC 机和实验系统联机状态下,编辑源程序。 2. 从存储器窗口检查和记录4000H~43FFH 中的内容和5000~53FFH 中的内容。 3. 对源程序进行编译和装载,生成可执行文件。 4. 对可执行文件进行调试,调试方法有:单步,宏单步,自动单步,自动宏单步,注意这些方法之间的区别。 5. 连续运行实验程序。 6. 从存储器窗口检查和记录4000H~43FFH 中的内容和5000~53FFH 中的内容,比较程序运行前、后存储器内容的变化情况。 五、实验程序清单 CODE SEGMENT ;RAM.ASM ASSUME CS:CODE PA EQU 0FF20H ;字位口 PB EQU 0FF21H ;字形口 PC EQU 0FF22H ;键入口 ORG 1850h

START: JMP START0 BUF DB ?,?,?,?,?,? data1: db0c0h,0f9h,0a4h,0b0h,99h,92h,82h,0f8h,80h,90h,88h,83h,0 c6h,0a1h db 86h,8eh,0ffh,0ch,89h,0deh,0c7h,8ch,0f3h,0bfh,8FH START0: MOV AX,0H MOV DS,AX ;写数据段地址 MOV BX,4000H ;内存首址 MOV AX,55AAH ;要写入的字 MOV CX,0200H ;数据长度 RAMW1: MOV DS:[BX],AX ;写数据 ADD BX,0002H ;下一个单元 LOOP RAMW1 ;循环写 MOV AX,4000H ;首址 MOV SI,AX ;SI置源首址 MOV AX,5000H MOV DI,AX ;DI置目首址 MOV CX,0400H ;数据长度 CLD ;增址 REP MOVSB ;串传送 call buf1 ;写”62256-” mov cx,0ffh con1: push cx call disp ;显示 pop cx loop con1 call buf2 ;写”--good” con2: call disp ;显示 jmp con2 DISP: MOV AL,0FFH ;显示子程序 ,5ms MOV DX,PA OUT DX,AL MOV CL,0DFH ;20H ;显示子程序 ,5ms MOV BX,OFFSET BUF DIS1: MOV AL,[BX] MOV AH,00H PUSH BX MOV BX,OFFSET DATA1 ADD BX,AX MOV AL,[BX] POP BX MOV DX,PB OUT DX,AL

静态存储器扩展实验报告记录

静态存储器扩展实验报告记录

————————————————————————————————作者:————————————————————————————————日期:

深圳大学实验报告 课程名称:微机原理与接口技术 实验项目名称:静态存储器扩展实验 学院:信息工程学院 专业:电子信息工程 指导教师:周建华 报告人:洪燕学号:2012130334 班级:电子3班 实验时间:2014/5/21 实验报告提交时间:2014/5/26 教务部制

一.实验目的与要求: 1. 了解存储器扩展的方法和存储器的读/写。 2. 掌握CPU 对16位存储器的访问方法。 二.实验设备 PC 机一台,TD-PITE 实验装置或TD-PITC 实验装置一套,示波器一台。 三.实验原理 存储器是用来存储信息的部件,是计算机的重要组成部分,静态RAM 是由MOS 管组成的触发器电路,每个触发器可以存放1位信息。只要不掉电,所储存的信息就不会丢失。因此,静态RAM 工作稳定,不要外加刷新电路,使用方便。 但一般SRAM 的每一个触发器是由6个晶体管组成,SRAM 芯片的集成度不会太高,目前较常用的有6116(2K ×8位), 图4.1 62256引脚图 6264(8K ×8位)和62256(32K ×8位)。本实验平台上选 用的是62256,两片组成32K ×16位的形式,共64K 字节。 62256的外部引脚图如图4.1所示。 本系统采用准32位CPU ,具有16位外部数据总线,即D0、D1、…、D15,地址总线为BHE #(#表示该信号低电平有效)、BLE #、A1、A2、…、A20。存储器分为奇体和偶体,分别由字节允许线BHE #和BLE #选通。 存储器中,从偶地址开始存放的字称为规则字,从奇地址开始存放的字称为非规则字。处理器访问规则字只需要一个时钟周期,BHE #和BLE #同时有效,从而同时选通存储器奇体和偶体。处理器访问非规则字却需要两个时钟周期,第一个时钟周期BHE #有效,访问奇字节;第二个时钟周期BLE #有效,访问偶字节。处理器访问字节只需要一个时钟周期,视其存放单元为奇或偶,而BHE #或BLE #有效,从而选通奇体或偶体。写规则字和非规则字的简单时序图如图4.2所示。 D15:D0 CS#WR#DATA D15:D8 D7:D0 CS#WR#DATA 图4.2 写规则字(左)和非规则字(右)简单时序图 A14A12A7A6A5A4A3A2A1A0D0D1D2GND 1234567891011121314 2827262524232221201918171615 VCC WE A13A8A9A11OE A10CS D7D6D5D4D3 62256

计算机组成原理存储器(1)(1)说课讲解

计算机组成原理存储 器(1)(1)

1.存储器 一、单选题(题数 54,共7 ) 1 在下述存储器中,允许随机访问的存储器是()。(1.2分) A、磁带 B 、磁盘 C 、磁鼓D 、半导体存储器 正确答案 D 2 若存储周期250ns,每次读出16位,则该存储器的数据传送率为()。(1.2分) A、4×10^6字节/秒 B、4M字节/秒 C、8×10^6字节/秒 D、8M字节/秒 正确答案 C 3 下列有关RAM和ROM得叙述中正确的是()。 IRAM是易失性存储器,ROM是非易失性存储器 IIRAM和ROM都是采用随机存取方式进行信息访问 IIIRAM和ROM都可用做Cache IVRAM和ROM都需要进行刷新 (1.2分) A、仅I和II B、仅I和III C、仅I,II,III D、仅II,III,IV 正确答案 A 4 静态RAM利用()。(1.2分) A、电容存储信息 B、触发器存储信息 C、门电路存储信息 D、读电流存储信息 正确答案 B 5 关于计算机中存储容量单位的叙述,其中错误的是()。(1.2分) A、最小的计量单位为位(bit),表示一位“0”或“1” B、最基本的计量单位是字节(Byte),一个字节等于8b C、一台计算机的编址单位、指令字长和数据字长都一样,且是字节的整数倍 D、主存容量为1KB,其含义是主存中能存放1024个字节的二进制信息 正确答案 C 6

若CPU的地址线为16根,则能够直接访问的存储区最大容量为()。(1.2分) A、1M B、640K C、64K D、384K 正确答案 C 7 由2K×4的芯片组成容量为4KB的存储器需要()片这样的存储芯片。(1.2分) A、2 B、4 C、8 D、16 正确答案 B 8 下面什么存储器是目前已被淘汰的存储器。(1.2分) A、半导体存储器 B、磁表面存储器 C、磁芯存储器 D、光盘存储器 正确答案 C 9 下列几种存储器中,()是易失性存储器。(1.2分) A、cache B、EPROM C、FlashMemory D 、 C D-ROM 正确答案 A 10 下面关于半导体存储器组织叙述中,错误的是什么。 (1.2分) A、存储器的核心部分是存储体,由若干存储单元构成 B、存储单元由若干存放0和1的存储元件构成 C、一个存储单元有一个编号,就是存储单元地址 D、同一个存储器中,每个存储单元的宽度可以不同 正确答案 D 11 在主存和CPU之间增加Cache的目的是什么。(1.2分) A、扩大主存的容量 B、增加CPU中通用寄存器的数量 C、解决CPU和主存之间的速度匹配 D、代替CPU中的寄存器工作 正确答案 C

存储器实验报告

存储器扩展实验报告 班级姓名学号日期 一、相关知识: 1.教学机配置了6个存储器芯片插座,其中4个28芯插座可插只读存储器,2个24 芯插座可插静态随机存储器6116。 2.在教学机中,已经放置了2片8K×8位的ROM和2片2K×8位的RAM,基本存 储器(指的是允许监控程序所必需的存储器)同时使用这两组。另设置了两个28芯插座用于进行存储器容量的扩展。 3.芯片ROMH、ROML用来存放监控程序,芯RAMH、RAML用来存放用户程序和 数据以及监控程序临时数据和堆栈。 4.内存地址译码器在教学机中由1片DC5 74LS138实现,对A15~A13产生8个译码 信号,分别对应内存地址从0000H~1FFFH到E000H~FFFFH。其中0000H~1FFFH 的译码信号作为ROMH的片选信号,地址为2000H~3FFFH的译码信号作为RAM 的片选信号,其它6个译码信号通过圆孔针引出。 5.6116只有2K空间,但是在设计时为其分配的内存空间为8K,即范围在2000H~ 27FFH、2800H~2FFFH、3000H~3FFFH的内存地址都是对6116同一存储单元的访问。 6.28C64芯片组地址空间为:0000H~1FFFH;6116芯片组地址空间为:2000H~3FFFH 58C65芯片组地址空间为:4000H-5FFFH;或者可以连接为5000H~6FFFH; 7000H~8FFFH;9000H~AFFFH;B000H~CFFFH;D000H~EFFFH 012 A 815 二、实验目的: ?通过看懂教学计算机中已经使用的几个存储器芯片的逻辑连接关系和用于完成存储器容量扩展的几个存储器芯片的布线安排,在教学计算机上设计、实现并调试出存储器容