xilinx ise13.4安装步骤

Xilinx ISE13.4安装步骤

安装程序是官网上下载,需要注册账号,填相关信息才可以下载。。Xilinx_ISE_DS_Win_13.4_O.87xd.3.0 共5.67G,用官网的download manager下载速度还可以。

解压后,点击xsetup图标后按照以下安装即可。

同时还需要在网上下载一个破解文件。

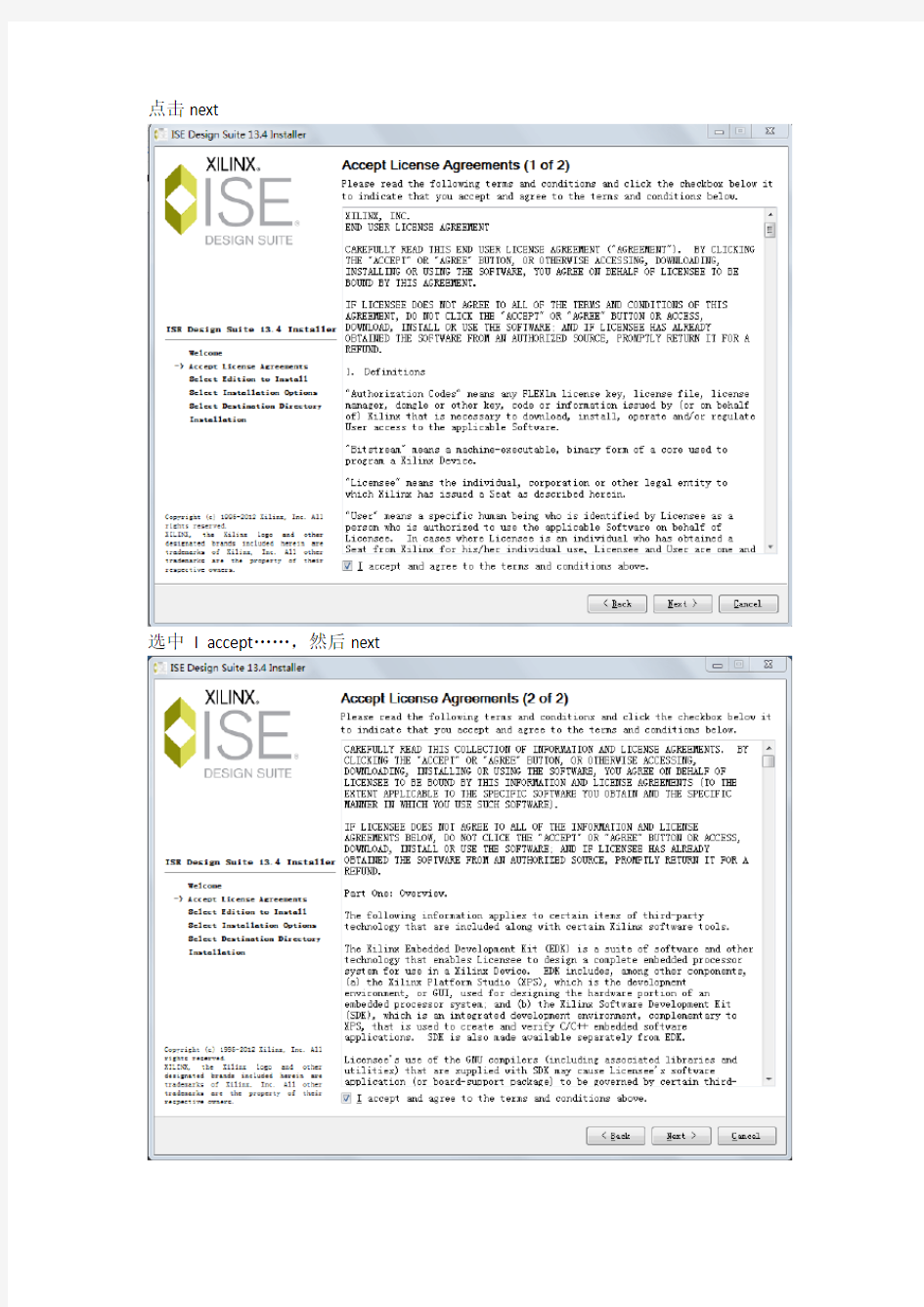

显示如下界面:

点击next

选中I accept……,然后next

选中I accept……next,显示如下:

选择需要安装的部分,一般按默认的装

点击next

可以修改默认的目录,然后点击next

直接点击install即可,进入等待当中,可以出去喝个茶,时间比较久,大约一个小时

90%时弹出如下界面

Next

点击Install后

过了一会弹出一个安全框,我点击了安装

之后又弹出一个,同样安装

之后弹出一个有关matlab,我的是2008a,好像不支持,我选择了choose later。

随后显示完成对话框,可以直接点击完成。

同时弹出激活框

选择locate existing license,选择网上下载的license即可。

安装完的启动界面如下:

最后可以打开看看,点击help-manage license……,license管理界面,使用期限。

至此大功告成。

虚拟演播室方案

虚拟演播室是视频技术于计算机技术结合的产物,把计算机图形图像处理技术与传统的色键技术集合起来形成的。是一种新颖的独特的电视节目制作技术。 虚拟演播室技术原理:虚拟演播室技术与色键技术十分相像,他是由前景主持人为主的画面和背景画面,采用色键的方法构成一个整体,产生人物置身于背景中的组合画面。 虚拟演播室工作原理 虚拟演播室装修的总体要求: 建立一个功能完善的虚拟演播室,需要做到如下基本要求: 1、要求演播室的拾音空间首先具有较好的语言清晰度、可懂度,其次是要有良好的声音丰满度, 2、要求演播室内各处要有合适的响度和均匀度,具有相应的满足拾音要求的混响频率特性。 3、抑制影响听、拾音音质的声缺陷,防止出现声聚焦、驻波、颤动回声、低频嗡声等。 4、演播室内墙面的声学装饰考虑在装饰大方美观、造型新颖的基础上对于高中低各频段的声学处理方式,特别是低频段的声学处理方式方法。 演播室的建声指标:混响时间≤0.6S±0.05S;噪声评价曲线NR-30---NR-35。 设计的隔声门隔声量大于35dB并具有好的密封性。 5、演播室声学建声装饰所选用的材料符合国家相应的强制消防要求,要求采用达到B1、B2级标准的材料。 6、演播室声学建声装饰所选用的材料符合国家相应的强制环保要求,特别是要求甲醛的释放量为<0。1mg/m3。墙面装饰层内禁止使用不安全和危害性较高的吸声材料。 7、装饰踢脚线兼做视音频线槽并做屏蔽处理。 8、演播室配置录制指示灯和紧急逃生指示灯。 9、装饰层内的综合布线按要求做穿管处理。 10、演播室现有的位置南边部分为玻璃幕墙,不利于演播室的隔声,所以要对原幕墙部分进行隔断,制作隔声封闭处理,在保证整体装饰的美观性和隔声性的同时,还应保证演播室正常的通风换气。 11、导控室地面用防静电地板,装修过程中做好设备布线(强电,弱电),做好防雷,接地各类设施的设计施工。 12、装修预留好空调位置,并配合本台做好空调,配电等设备的安装施工。

虚拟演播室系统方案

VS-VSCENE 虚拟演播室系统方案建议书北京华视恒通系统技术有限公司

北京华视恒通系统技术有限公司 目栩 公司简介................................................................................................................................................................... 3.. . 惊)前悅........................................................................................................................................................................................ 4.. . . 二)系统方案设计.................................................................................................................................................. 4.. . 1、设计原则........................................................................................................................................... 4.. . 2、设计方案........................................................................................................................................... 5.. . 3、系统结构原枞图............................................................................................................................. 7.. . 4、系统功能特点 ................................................................................................................................ 1..0. 5、TOPACK-C抠K 像卡................................................................................................................ 1..2 6、TOPACK-CG/AUD旓IO幕混愃卡 ................................................................................ 1..3 三)软件系统功能................................................................................................................................................. 1..5. 1、系统参数设敢 ................................................................................................................................ 1..5. 2、抠像参数设敢 ................................................................................................................................ 1..7. 3、场景编排.......................................................................................................................................... 1..8. 4、实时控敥.......................................................................................................................................... 2..0. 5、远程旓幕客户端............................................................................................................................ 2..2. 四)设备悪本及效果图........................................................................................................................................ 2..3. 五)系统配敢........................................................................................................................................................................................ 2..4 . 售后服务措施及承诺 ............................................................................................................................................. 2..6.

Xilinx spartan3e FPGA掉电配置及应用程序引导

Xilinx spartan3e FPGA掉电配置及应用程序引导 Xilinx公司的spartan3e开发板上面有丰富的外围器件,就存储器来说有一个16M并行flash,一个4Mbits串行flash,还又一个64M的DDR,在嵌入式开发中,一般我们可能会在FPGA中嵌入cpu软核,让C语言程序在里面运行。这就涉及到FPGA配置文件的引导,如果C语言程序太大,需要在DDR里面运行的话也涉及到应用程序的引导的问题。我刚接触到xinlinx的spartan3e开发板时,只会将FPGA配置文件(.bit)直接通过JTAG口下载到芯片里。后来编写的程序大了,如果将程序直接放到内部的RAM里面就装不下了,这时就只有将程序放到DDR里面运行,如果仅仅是调试应用程序不需要重启开发板后程序也可以运行,那么可以直接用EDK里面的XDM工具通过dow命令直接下载到DDR里面,然后就可以执行了。但是但我们的应用程序和硬件配置调试通过,达到了我们的要求以后我们就想到可不可以将让程序在板子上电时就可以自动运行呢。因为FPGA是掉电要丢失的,重新上电就必须重新配置。我们通过查找相关资料,找到了解决烧写问题的解决办法。首先是配置文件的烧写。spartan3e提供了3个掉电不丢失的外部存储器,就是上面提到的并行flash,串行flash和Flash PROM。配置文件都可以烧写到其中任何一个储存器里面。但是,在我看来,一般的配置问件都是烧写到Flash PROM里面。烧写方法有很多,可以用Xilinx公司的专门的烧写.mcs文件的工程烧写,也可以用iMPACT烧写。一般用iMPACT工具烧写,烧写过程如下: 打开iMPACT,弹出新建工程时选择Cancle,然后双击窗口左边的

Xilinx_FPGA中文教程

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

虚拟演播室灯光技术说明

虚拟演播室技术说明 由于虚拟演播室系统不同于传统演播室的抠像,它允许几台摄象机在不同的角度分做推、拉、摇、移等动作。为了保证摄象机在蓝箱中拍摄的人物与计算机制作的虚拟场景通过色键组合成系统准确合成,要求虚拟演播室系统中人物的活动空间(蓝箱)要有非常均匀和柔和的照明,不能有硬的影子出现,所以首先应用柔光灯把蓝箱铺满打匀,形成一个基本光。 根据贵台的实际情况,设计方案如下: 1.篮箱立面墙的布光:在灯具的选择上,虽然近年来国内一些灯 光企业相继推出了虚拟演播室专用灯光设备,但是由于大多数 电视台虚拟演播室是在原有传统演播室中设置的,所以虚拟演 播室的布光可利用传统演播室的灯具进行布光。布光时,我们 首先考虑选用冷光源——4×55W三基色柔光灯9台,由于它是 散射型光源,布光面积大,容易将墙体的光布匀。 2.篮箱地面布光:在虚拟演播室节目制作时,画面如果出人物的 全景,出现虚拟的地面时,这时不但主持人身后和两侧的蓝墙 要有均匀的布光,而且蓝箱的地面也要有非常均匀的照明。本 方案我们采用4×55W三基色柔光灯6台,作为地面布光,使 篮箱地面光线均匀; 3.人物布光:虚拟演播室人物的布光基本方法和对光比的要求, 仍采用传统演播室的三点式布光和对光比的要求,但同时要考 虑到虚拟演播室的特点。灯光人员在布光前要使人物的主光方

向与虚拟场景中的主光方向一致,同时使光的强弱、硬柔、色彩也都要与虚拟场景中的主光方向一致。使人和景在画面上融为一体,看起来真实。方案采用冷热光源混合式布光,用2台6×55W三基色柔光灯作为侧光,4×55W、6×55W三基色柔光灯各2台,1KW透射式聚光灯2台,作为人物的主面光和辅助面光,使拍摄人物更加丰满圆润; 4.吊挂系统采用格珊架式悬挂,充分利用室内空间高度,避免拍 摄全景时发生“穿帮”现象; 5.整个虚拟演播室采用冷热混合光源布光,总功率为9KW、色温 3200k、中心照度900Lux,满足贵台的虚拟演播室拍摄需求。

虚拟演播室方案

SUNUR-VS三维虚拟演播室系统集成方案 一、系统综述 如何在有限的时间内,不用花费大量的精力和财力,就能轻松地搭建出富有创意的演播室,制作出精彩新颖又充满无限魅力的节目?如何在现有的标清环境下选择面向未来的高清系统而不浪费投资?福州索普电子科技有限公司推出的面向未来创新虚拟演播室系统——SUNUR-VS,一个先进的、实用的、高度集成的、真三维、全场景的虚拟演播室完整解决方案,可以轻而易举地让您的梦想成真。 SUNUR VS三维虚拟场景解决方案使虚拟演播室系统去除了烦琐的硬件配置和大规模的数据运算,凭借简单的设置和直观的用户界面,使之成为一套功能强大的广播电视节目制作工具。只要利用摄影棚中的一小部分空间搭配绿色或蓝色背景,加上摄影灯光,把人物拍下,通过系统集成的色键器,对摄像机获得的信号与虚拟演播室系统信号进行处理,即可实现演播主体与虚拟场景的合成。从此,不再受狭小空间和景物的限制,使用SUNUR VS三维虚拟演播室系统,充分发挥您的想象力和创造力,便可满足任何电视节目现场直播、后期制作及应用的需要。并且,SUNUR VS 无三维虚拟演播室系统具有颠覆传统的业界最优的性价比。通过极快速的启动时间和极低的成本,SUNUR VS三维虚拟演播室系统能为新闻电视广播、体育、财经、现场访谈、气象、远程教育、娱乐节目、广告、游戏秀以及许多其他应用领域提供理想的硬件和软件解决方案。 二、系统方案设计原则 随着电视业和计算机技术的极速发展,高清制作和播出的要求也离我们越来越

近,虚拟演播室的更新步伐不断加快,大家对节目的制作水平和信号质量要求不断提高,SUNUR VS三维虚拟演播室系统本着"简捷至上"的设计宗旨,充分体现系统的技术先进性、功能完整性、经济实用性、运行可靠性、操作灵活性及系统扩展性,不仅能满足现阶段的需要,同时确保系统在今后相当长一段时间内具有先进性并留有扩展余地。在设计方案的过程中,首先考虑到系统要满足演播室现行技术要求,及其应用领域,同时又符合当今虚拟化的趋势,我们遵循以下几个原则: 1、技术的先进性 SUNUR VS三维虚拟演播室系统是福州索普公司在国外虚拟现实软件的基础上开发而来的真三维虚拟演播室系统,该系统是针对市场反馈,专为广电和电教系统应用量身定做和特别优化设计。 SUNUR VS三维虚拟演播室系统,采用革命性的独特设计,无需传感器,采用独有的虚拟摄像机结构,使得产品的安装、初始调试、使用极其方便,省却了繁琐的安装调试过程,真正作到随架随用,一开就用,迅速快捷。一人即可实现多机位的节目演播操作工作,并且真实人像与实时渲染的三维虚拟背景同步运行。如果用户习惯使用传感器系统时可通过增加传感器实现传统虚拟演播室功能。 SUNUR VS三维虚拟演播室系统一开始设计就采用HDSDI高清输入,并能兼容标清输入。在用户预算可能的情况下可以直接使用高清设备,并实现高清、标清、N制、P制混合输入。并在此基础上开发出基于模拟及HDMI接口输入的配套产品,以满足不同经济条件的用户的不同个性化需求。 2、功能完整性 SUNUR VS三维虚拟演播室系统功能完善。 系统集成了色键器、切换台等多种功能。 您无需使用昂贵的摄像机动作传感器,系统采用独有的虚拟摄像机结构。能够轻松的在3D场景中设置和改变8个不同的虚拟摄像机位置(模拟配置),还可方便地编辑3D场景中摄像机的运动速度和运动轨迹。通过与3D虚拟场景进行实时地无缝结合,可进行多重虚拟摄像机的显示与切换。 在系统配置的动作设计模块中,可以生成实时的镜像反射效果,增强了场景的真实感。

Xilinx ISE软件使用过程新(含PROM下载)

Xilinx ISE 13.4软件使用方法 本章将以实现一个如图所示的4为加法器为例,来介绍Xilinx ISE13.4开发流程,并且最终下载到实验板BASYS2中运行。 1 A 1 1.建立工程 运行Xilinx ISE Design Suite 13.4,初始界面如图F2所示 F1软件初始状态表 选择File->New Project ,该对话框显示用向导新建工程所需的步骤。 在Name 栏中输入工程名称(注意:以下所有不能含有中文字符或空格),如“test”。在Location 栏中选择想要存放的工程位置,如“E:\code\Xilinx\test”。顶层语言选项栏中选择“HDL”语言。设置向导最终设置效果如图F2所示 F2路径信息设置表

点击“Next”,进入芯片型号选择界面。在本界面中,根据BASYS2实验板上的芯片型号进行相关设置,设置效果如图F3所示。 F3芯片信息选择表 点击“Next”,出现如图F4所示工程信息汇总表格。 F4工程信息汇总表 点击“Finish”完成设置。

2新建Verilog文件 在F5所示界面中,如图所示的区域内右击鼠标,选择“New Source”,出现F6对话框。 F5 在File name栏中键入verilog文件的名称,如“test”。 F6 点击“Next”,在本界面中将设置加法器的输入输出引脚数量,如图F1所示的加法器共有A、B、C0、S和C1,5组引脚,其中A、B和S为4位总线形式,因此设置结果如图F7所示。

F7 点击“Next”,出现Verilog 新建信息汇总表。 F8 点击“Finish”,完成Verilog 新建工作。 3逻辑设计 输入代码

xilinx的prom配置经验

复位和上电复位 1 在上电时,这器件要求VCCINT在精确的上升时间内,单调的上升到标准工作电压值。 2 如果电压没满足要求,这器件就不能执行合适的上电复位。 3 上电运行的顺序:先PROM的OE/RESET保持低电平,在配置开始以前要求电源能达到它们各自的POR(上 电复位电压)门限,OE/RESET被定时释放后对稳定电源的应用有更多的余地。 4 在系统利用慢上升电源时,另外增加一个电源监控电路能被用做延时配置直到系统电源达到最小的操作 电源在OE/RESET一直为低电平。 5 当OE/RESET被释放,INIT就被上拉为高电平,允许FPGA有次序的配置。 6 如果电压低于POR门限时,PROM复位,OE/RESET再为低,直到达到POR 门限。 7 对于PROM电压正常时,只要OE/RESET=0或CE=1,复位就开始,当地址计数器复位时,CEO输出高电平,其 它的数据输出脚为高阻态。 8 XCFXXS PROM 只要求OE/RESET被释放以前,VCCINT上升到POR门限就行了。 9 XFCXXP PROM 在OE/RESET被释放以前,不但要求VCCINT上升到POR 门限,而且还要求VCCO达到被推荐的 正常工作电压。 配置 1 当JTAG配置指令在PROM里被更新时,PROM暂时给CF一个低电平,接着就给CF一个高电平。结合CF脚在外 部加了上拉电阻,此时在CF脚输出一个‘高-低-高’的脉冲个FPGA的PROGRAM 脚。此次FPGA就依次的开始 配置。 2 在CF脚外部必须加个上拉电阻,防止CF脚产生一个浮动到低电平的值而引起复位。 3 当XCFXXP的PROM存有多重设计文件时,CF脚必须连接到FPGA的PROGRAM_B脚去保证重新安放那些被选中 的设计文件(配置有效)。 4 对于XCFXXS的PROM,CF脚只是个输出,如果没有由于的功能的话,可以

VR虚拟演播室系统方案

VR虚拟演播室系统建设方案Make your dream magic ,make your life magic

目录 1.建设背景 (3) 2.设计原则 (4) 3.需求分析 (8) 4.VR情景互动虚拟演播室系统 (10) 方案概述 (10) 系统拓扑图 (11) 核心设备及功能 (11) VStage情景互动虚拟演播室系统 (11) 摄像采集设备 (25) 快速编辑模块 (25) 5.方案优势 (30) 6.售后服务与技术支持 (33) VR虚拟演播室系统建设方案

1.建设背景 虚拟演播室系统(The Virtual Studio System,简称VSS)是近年发展起来的一种独特的电视节目制作技术。它的实质是将计算机制作的虚拟三维场景与摄像机现场拍摄的人物活动图像进行数字化的实时合成,使人物与虚拟背景能够同步变化,从而实现两者天衣无缝的融合,以获得完美的合成画面。采用虚拟演播室技术,可以制作出任何想象中的布景和道具。无论是静态的,还是动态的,无论是现实存在的,还是虚拟的。这只依赖于设计者的想象力和三维软件设计者的水平。许多真实演播室无法实现的效果,对于虚拟演播室来说,却是“小菜一碟”。 从跟踪方式的区分,虚拟演播室分为有轨虚拟演播室和无轨虚拟演播室。有轨跟踪虚拟演播室系统应用摄像机跟踪技术,获得真实摄像机数据,并与计算机生成的背景结合在一起,背景成像依据的是真实的摄像机拍摄所得到的镜头参数,因而和主持人的三维透视关系完全一致,避免了不真实、不自然的感觉。虚拟演播室的跟踪技术有4种方式可以实现,网格跟踪技术、传感器跟踪技术、红外跟踪技术、超声波跟踪技术,其基本原理都是采用图形或者机械的方法,获得摄像机的参数,包括摄像机的X、Y、Z、(位置参数)Pan、Till、(云台参数)Zoom、Focus(镜头参数)由于每一帧虚拟背景只有20ms的绘制时间,所以要求图形工作站实时渲染能力非常强大,对摄像机的运动没有更多的限制,一般适合专业电视台,对节目制作要求较高的用户使用。但调试非常复杂,耗时长,需要专业人士才能操控。无轨虚拟演播室相对比较简单,它是预生成三维背景,即首先要制作好背景的三维模型,然后预先定义好虚拟摄像机的机位和镜头参数,根据这些数据生成每台虚拟摄像机的视图画面,最

FPGA常用的配置模式

FPGA配置电路模式有主模式、从模式和JTAG模式。 【1】主模式 在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射。主模式根据比特流的位宽又可以分为:串行模式( 单比特流) 和并行模式( 字节宽度比特流) 两大类。如:主串行模式、主SPI Flash 串行模式、内部主SPI Flash串行模式、主BPI 并行模式以及主并行模式,如下图: 【2】从模式 在从模式下,FPGA 作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。从模式也根据比特流的位宽不同分为串、并模式两类,具体包括:从串行模式、JTAG模式和从并行模式三大类。(此处的JTAG模式与下面要说的JTAG模式有所不同)如下图:

【3】JTAG模式 在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。 主串模式是最常用的配置模式 在FPGA主串配置模式下,会发现两种不同的连接方式: 一种是FPGA在前,PROM在后。即JTAG接口的DTI连接至FPGA的DTI,FPGA的DTO连接至PROM的DTI,PROM的DTO连接至JTAG接口的DTO。 另一种是PROM在前,FPGA在后。即JTAG接口的DTI连接至PROM的DTI,PROM的DTO 连接至FPGA的DTI,FPGA的DTO连接至JTAG接口的DTO。 这两种连接方式都是正确的,都可以。但是,由于PC机配置JTAG链的时候需要和第一级JTAG 设备同步,如果FPGA放在第一级,那么其配置速度较高,导致对PROM配置可能会不稳定,所以推荐的配置是将PROM作为JTAG链的第一级JTAG设备,即上述第二种方式。在Xilinx 的PROM芯片XCF01/2/4S手册中给出的主串模式下(Configuring in Master Serial Mode)的连接图也是第二种方式,如下图:

SUNUR-VS虚拟演播室操作说明

SUNUR-VS虚拟演播室界面说明导入场景 1、点击导入场景按钮,选择D盘下所要应用的场景; 2、场景载入。

场景管理 视频:点击视频,显示select live and mic操作界面,选择视频decklink video capture(2),选择音频decklink audio capture(2),选择select完成,选择1280*720 50帧(与来自摄像机信号相匹配),出现来自摄像机信号。

文件:点击文件,选择来自计算机的视频文件,导入完成。 物体:物体是对视频活文件的一个赋予(可以将文件或视频赋予给大屏或主持人) 物体控制:点击此按钮,可对主持人、LOGO或物体,对其进行大小、位置进行改变。 隐藏:对当前选中的对象进行隐藏和显示操作。(一般当前操作的对象会在下方显示) 定向、跟随:在被选对象的旋转操作时,进行定向或跟随操作(建议一般在旋转场景时不要使用跟随)。 16:9:点击按钮,进行4:3和16:9的切换。 抠像设置 应用抠像:对当前对象进行抠像操作应用。

取消抠像:对当前对象取消抠像操作应用。 网格背景:对当前所选对象进行网格背景和黑色背景的切换。黑色背景:对当前所选对象进行网格背景和黑色背景的切换。ALPHA:对所选视频进行alpha通道的抠像。(使要被保留的对象全部变成白色,要去掉的对象全部变成黑色。即黑透白不透)COLOR:对所选视频进行彩色通道的抠像。 黑色通道:对所选视频进行黑色通道抠像的参数调整(不要的对象如背景通过此按钮全部调成黑色) 白色通道:对所选视频进行白色通道抠像的参数调整(要保留的对象如主持人通过此按钮全部调成白色) 边缘色溢:对所选视频进行色溢参数调整(其实是对住要扣的对象进行实际色彩的调整,类似于条白平衡)。 色阀调节:对所选视频进行色阀参数调整(可以理解为对一开始的取色进行色彩饱和度的调整)。另外通过此按钮和白色通道的调整可对要抠对象的边缘进行更加完美的调整。 上边裁边:对所选视频进行上裁边操作。 下边裁边:对所选视频进行下裁边操作。 左边裁边:对所选视频进行左裁边操作。 右边裁边:对所选视频进行右裁边操作。 人物反射:对人物在地面上的反射进行参数调整。 地面反射:对虚拟背景进行在地面上反射参数的调整。

漫谈xilinx FPGA 配置电路

漫谈xilinx FPGA 配置电路 这里要谈的时xilinx的spartan-3系列FPGA的配置电路。当然了,其它系列的FPGA配置电路都是大同小异的,读者可以类推,重点参考官方提供的datasheet,毕竟那才是最权威的资料。这里特权同学只是结合自己的理解,用通俗的语言作一点描述。 所谓典型,这里要列出一个市面上最常见的spartan-3的xc3s400的配置电路。所有spartan-3的FPGA配置电路的链接方式都是一样的。Xc3s400是40万门FPGA,它的Configuration Bitstream虽然只有1.699136Mbit,但是它还是需要2Mbit的配置芯片XCF02S,不能想当然的以为我的设计简单,最多用到1Mbit,那么我选XCF01S(1Mbit)就可以了。事实并非如此,即使你只是用xc3s400做一个流水灯的设计,那么你下载到ROM(XCF02S)里的数据也是1.699136Mbit的,所以对于FPGA的配置ROM的选择宜大不宜小。 配置电路无非有下面五种:主串,从串,主并,从并,JTAG。前四种是相对于下载到PROM而言的(串并是相对于不同配置芯片是串口和时并口协议和FPGA 通讯区分的),只有JTAG是相对于调试是将配置下载到FPGA的RAM而言的(掉电后丢失)。FPGA和CPLD相比,CPLD是基于ROM型的,就是在数据下载到CPLD 上,掉电后不丢失。而FPGA则是基于RAM的,如果没有外部ROM存储配置数据,那么掉电后就丢失数据。所以FPGA都需要外接有配置芯片(当然现在也有基于FLASH的FPGA出现)。那么我们就来看一下主串模式下FPGA的配置电路的连接。 官方的硬件连接如下:

【配置知识】Virtex-5 FPGA 的配置

【配置知识】Virtex-5 FPGA的配置 配置方案 Xilinx 为终端用户提供了配置Virtex-5 FPGA 所需的灵活性。Virtex-5 FPGA 支持以下方案: 串行 最简单的配置方案,串行吞吐量。 主串行 Xilinx FPGA 驱动Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。 从串行 Xilinx PROM 的内部振荡器驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

从串行 外部时钟驱动Xilinx PROM CLK,Xilinx PROM 驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xil inx FPGA 提供了串行(x1)配置数据。 返回页首 从串行 外部时钟驱动Xilinx FPGA CLK 和Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

主SPI Virtex-5 FPGA 驱动SPI PROM 时钟,因为SPI PROM 为Virtex-5 FPGA 提供了串行(x1)配置数据。 并行 并行配置,可以实现最快速的吞吐量 主并(Master-SelectMap) Xilinx FPGA 驱动Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了字节宽的(x8)配置数据。

返回页首 从并(slave-SelectMAP) Xilinx PROM 的内部振荡器驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xilinx FPGA 提供了字节宽的(x8)配置数据。 从并(slave-SelectMAP) 外部时钟驱动Xilinx PROM CLK,Xilinx PROM 驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xil inx FPGA 提供了字节宽的(x8)配置数据。

Xilinx_FPGA下载烧写教程

Step1 学习下载配置Xilinx 之FPGA 配合Mars-EDA 的Spartan2 核心板,用图文方式向大家详细讲述如何下载配置Xilinx 的FPGA。 FPGA 下载模式说明 S1 为 FPGA 下载模式选择跳线,M0,M1,M2 默认状态为通过 4.7K 电阻上拉到 3.3V,当用跳线帽短接 S1 的PIN3 和PIN6 将置 M0 为0,同理,短接 PIN2 和PIN5,PIN3 和PIN4 将置 M1,M2 为0。M0,M1,M2 的电平和 FPGA 下载之间的关系参见下图:(Boundary-scan mode)是调试最常用的 JTAG 模式。当采用板载 PROM 时,采用的跳线模式是 Master Serial Mode –短路 PIN1 和PIN6,PIN2 和PIN5 J2 为Slave Serial Mode 的接口。下载模式跳线 S1 短接PIN1 和PIN6,PIN2 和PIN5 即可。 J3 为 JTAG Mode 的接口。下载模式跳线短接 PIN1 和 PIN6 即可。

S2 跳线说明 1.通过 JTAG 方式烧录 FPGA:短接 PIN1 和PIN3。 2.通过 JTAG 方式烧录 PROM:短接 PIN3 和PIN5,PIN2 和PIN4. 3.通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和PIN5,PIN4 和PIN6. 下面我们利用 Spartan2 核心板介绍一下通过 JTAG 菊花链方式下载 FPGA 和烧录 PROM. 硬件跳线选择: 1.跳线 S1: 此时要求 M0 M1 M2 = 100, 设置 FPGA 的下载方式为 Boundary-scan mode, 此时将 M1 和M2 的跳线安上。 跳线 S2 : 通过菊花链下载 FPGA 和烧录 PROM:短接 PIN3 和 PIN5,PIN4 和 PIN6. 2.将 Xilinx 下载线和核心板上 JTAG mode 接口 J3 相连,连接到计算机并口。核心板上电。

Xilinx FPGA 中文手册-《Platform Flash In-System Programmable Configuration PROMs》中文版

《Platform Flash In-System Programmable Configuration PROMs》中文版IO引脚1.8V~3.3V兼容,3.3V供电,20Pin。XCF08/16/32P芯片1.8V供电,48Pin。XCF04S有4Mb,Vccint3.3V,Vcco1.8~3.3V,Vccj2.5~3.3V。通过JTAG 片上编程,只有串行配置。内部结构: 图3 XCFxxS Platform Flash PROM内部结构 FPGA为主串行模式时输出CCLK驱动PROM,nCF为高且nCE和OE使能后经过一个短暂的有效延迟,与FPGA的DIN相连的PROM的DO引脚即发送数据。新数据位在每个CCLK上升沿后经过一个短暂的有效延迟可用,FPGA 生成合适的时钟脉冲个数以完成配置。当FPGA为从串行模式时PROM和FPGA 都被外部时钟驱动,对于XCFxxP系列PROM可用提供时钟驱动FPGA。 XCFxxP的设计版本提供“Master SelectMAP, Slave SelectMAP, Slave Parallel”配置模式。当工作在Master SelectMAP模式时FPGA产生配置时钟,工作在Slave SelectMAP模式时外部时钟或者PROM时钟工作。nCE和OE使能后,如果BUSY 为低且nCF为高,PROM的数据(D0~7)上的数据可用。新数据位在每个CCLK 上升沿后经过一个短暂的有效延迟可用,并在下一个上升沿载入FPGA。外部晶振可以是“free-running”晶振。 片上烧写过程中,nCEO被拉高。 在一个指令扫描序列期间,TDI和TDO通过Instruction Register(IR)连接,IR被并行载入固定的指令帧。指令帧被移位至TDO(低位先出),同时一个指令被移位进TDI。XCFxxS指令寄存器为8位宽, Platform Flash PROM的Test Access Port(TAP)测试接口特性 单端4线TAP:TCK、TMS、TDI、TDO。 初始化FPGA配置 有三种方式启动初始化:1.上电自动初始化;2.外部高-低-高脉冲驱动FPGA 的nPROGRAM引脚;3.JTAG配置指令控制PROM。 FPGA上电完成或者nPROGRAM引脚被使能后,FPGA的配置存储单元被清除,配置模式被选定,并做好了接收新配置比特流的准备。nPROGRAM引脚引脚可以由外部信号或PROM的nCF引脚控制,通过JTAG执行配置指令会拉低nCF引脚300~500ns复位FPGA并且初始化配置。iMPACT软件能够保证通过执行“装载FPGA”操作实现JTAG配置FPGA。

虚拟演播室使用说明

虚拟演播室管理制度 为规范虚拟演播室管理,保证灯光、音响及拍摄系统的正常使用,充分发挥虚拟演播室的作用,特制定本制度。 一、虚拟演播室的使用程序 1、进机房后,先打开配电柜,按从左到右的顺序依次打开第一排和第二排的开关。将调光台总输出推到9的位置,再将分输出推到3的位置,预热1到2分钟后在将分输出推到10的位置。 2、虚拟演播室操作人员先打开主控设备后,摄像人员打开摄像机,通过麦克联系,调节场景,操作人员不得擅自挪动灯位,避免妨碍他人使用。调节时,摄像人员先将摄像机拉至远景,虚拟演播室操作人员激活场景后,摄像人员按摄像机架黑盒上的红钮,使场景与摄像机同步,不得擅自挪动机位。 3、灯光调节结束后,虚拟演播室操作人员再调节场景的位置,并进行抠像。主持人试音,录制人员调节调音台。 4、录制结束后,摄像人员先将调光台总输出缓慢拉到3,关闭摄像机,把摄像机用布盖好后,再将调光台总输出拉到0。关闭配电柜中第二排开关,再按照从右至左的顺序关闭第一排开关并锁好门。虚拟演播室人员退出程序,关闭所有设备的开关。 5、因操作失误或不规范造成灯光、蓝箱、提字器、摄像机等机房设备损坏,处罚金100元以上。 二、虚拟演播室卫生 保持清洁的环境。拍摄结束后打扫卫生,恢复演播室内设施,将杂物

带离演播室。人员在蓝箱中要注意安全区域,不可踩踏蓝箱的连接部分,以免损坏蓝箱。 三、虚拟演播室防火 演播室内存在易燃材料,严谨吸烟,发现吸烟现象,将予以重罚。由于吸烟引起的火灾将,肇事人应负法律责任。 四、虚拟演播室的所有节目录制和技术保障由总编室技术人员负责,遇到技术故障请及时报知总编室进行排除。

Xilinx FPGA下载烧写教程(超详细)

Step by step 学习下载配置Xilinx之FPGA 配合Mars-EDA的Spartan2核心板,用图文方式向大家详细讲述如何下载配置Xilinx 的FPGA。 FPGA下载模式说明 S1为FPGA下载模式选择跳线,M0,M1,M2默认状态为通过4.7K电阻上拉到3.3V,当用跳线帽短接S1的PIN3和PIN6将置M0为0,同理,短接PIN2和PIN5,PIN3和PIN4将置M1,M2为0。M0,M1,M2的电平和FPGA下载之间的关系参见下图:(Boundary-scan mode)是调试最常用的JTAG模式。当采用板载PROM时,采用的跳线模式是Master Serial Mode –短路PIN1和PIN6,PIN2和PIN5 J2为Slave Serial Mode的接口。下载模式跳线S1短接PIN1和PIN6,PIN2和PIN5即可。 J3为JTAG Mode的接口。下载模式跳线短接PIN1和PIN6即可。

S2跳线说明 1.通过JTAG方式烧录FPGA:短接PIN1和PIN3。 2.通过JTAG方式烧录PROM:短接PIN3和PIN5,PIN2和PIN4. 3.通过菊花链下载FPGA和烧录PROM:短接PIN3和PIN5,PIN4和PIN6. 下面我们利用Spartan2核心板介绍一下通过JTAG菊花链方式下载FPGA和烧录PROM. 硬件跳线选择: 1. 跳线S1: 此时要求M0 M1 M2 = 100, 设置FPGA的下载方式为Boundary-scan mode,此时将M1和M2的跳线安上。 跳线S2 : 通过菊花链下载FPGA和烧录PROM:短接PIN3和PIN5,PIN4和PIN6. 2. 将Xilinx下载线和核心板上JTAG mode接口J3相连,连接到计算机并口。核心板上电。