计算机电路基础复习题.docx

1、对于某一支路电流的参考方向

A. 可以任意设定

B.

C. 要根据其它电流参考方向设定

。

必须与电流实际方向一致

D. 只能按顺时针方向设定

2、如图,已知E=5V,R=10 Ω,I=1A,则电压U= ()V。

A 、15B、5C、— 5D、 10

3、稳压二极管是利用PN结的特性,来实现稳定电压作用的。

A. 正向导通

B. 反向截止

C. 反向击穿

D. 温度特性

4、三极管当发射结和集电结都正偏时工作于()状态。

A. 放大

B.截止

C.饱和

D.无法确定

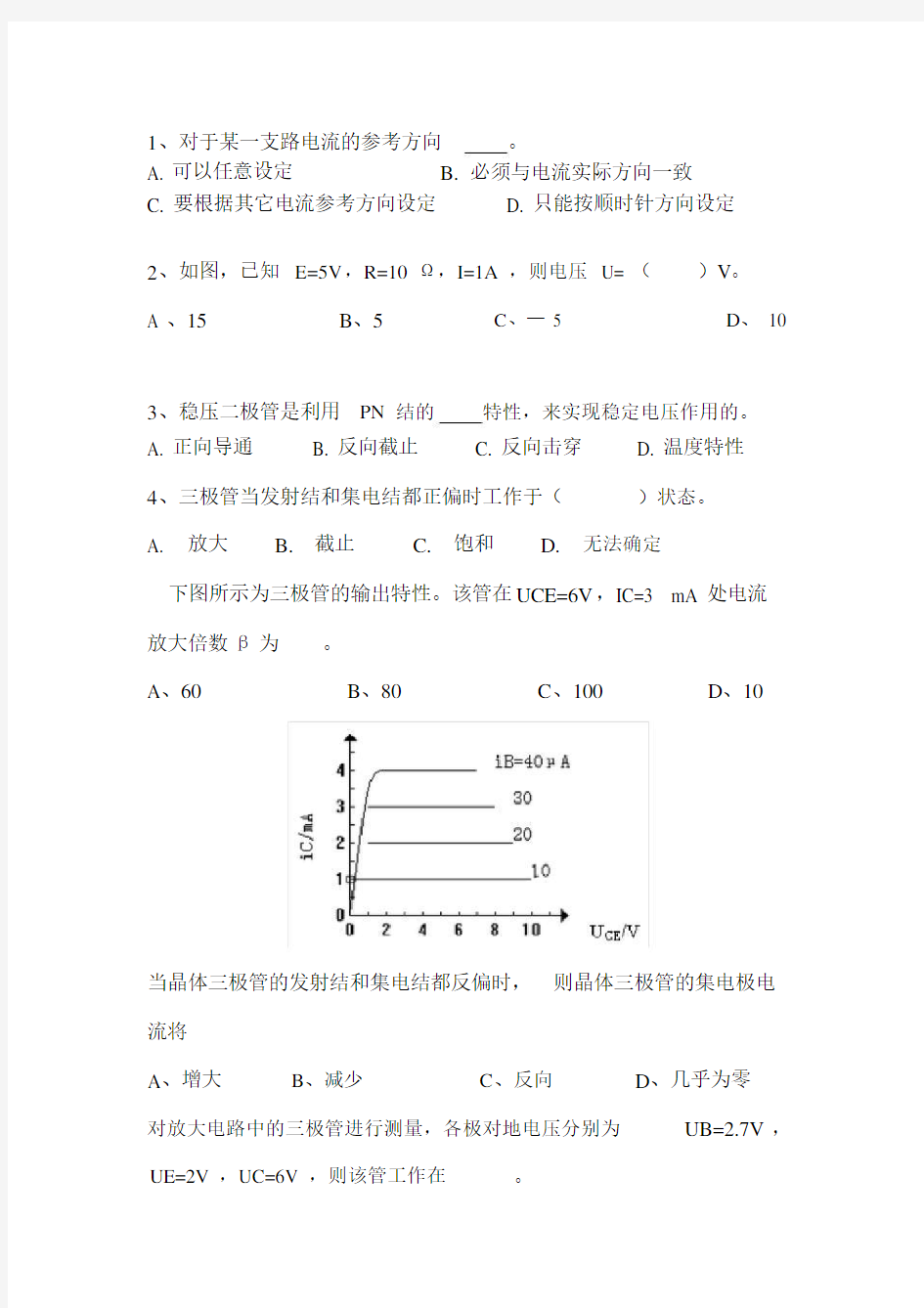

下图所示为三极管的输出特性。该管在UCE=6V,IC=3 mA 处电流

放大倍数β为。

A、60

B、80

C、100

D、10

当晶体三极管的发射结和集电结都反偏时,则晶体三极管的集电极电流将

A、增大

B、减少

C、反向

D、几乎为零

对放大电路中的三极管进行测量,各极对地电压分别为UB=2.7V,UE=2V ,UC=6V ,则该管工作在。

A、放大区

B、饱和区

C、截止区

D、无法确定

某单管共射放大电路在处于放大状态时,三个电极A、B、C 对地的电位分别是 UA=2.3V ,UB=3V ,UC=0V ,则此三极管一定是

A、PNP 硅管

B、NPN 硅管

C、PNP 锗管

D、NPN 锗管

电路如图所示,该管工作在。

A、放大区

B、饱和区

C、截止区

D、无法确定

测得三极管 IB=30 μA 时, IC = 2.4mA;IB=40μA时,IC = 1mA,则该管的交流电流放大系数为。

A、80

B、60

C、75

D、 100

用直流电压表测得放大电路中某晶体管电极1、 2、3的电位各为V1=2V ,V2=6V ,V3=2.7V ,则。

A、1 为 e 2 为 b 3 为 c

B、1 为 e 3 为 b 2为 c

C、2 为 e 1 为 b 3 为 c

D、3 为 e 1 为 b 2为 c

晶体管共发射极输出特性常用一族曲线表示,其中每一条曲线对应一

个特定的。

A、iC

B、uCE

C、 iB

D、iE

16、(2-1,低 )某晶体管的发射极电流等于 1 mA ,基极电流等于20

μA,则它的集电极电流等于

A、 0.98 mA

B、 1.02 mA

C、0.8 mA

D、1.2 mA

三极管各个极的电位如下,处于放大状态的三极管是。

A、VB = 0.7 V ,VE = 0 V,VC = 0.3 V

B、VB=-6.7V ,VE=-7.4V ,VC=-4 V

C、VB=-3V ,VE=0V,VC=6V

D、VB=2.7V,VE=2V,VC=2V

某放大器由三级组成,已知每级电压放大倍数为KV,则总放大倍数为。

A、 3KV

B、( KV) 3

C、( KV)3/3

D、KV

一个三级放大器,各级放大电路的输入阻抗分别为Ri1=1M Ω,Ri2=100K Ω,Ri3=200K Ω,则此多级放大电路的输入阻抗为。

A、 1M Ω

B、 100K Ω

C、 200K Ω

D、1.3KΩ

选用差分放大电路的原因是。

A、克服温漂

B、提高输入电阻

C、稳定放大倍数

D、提高放大倍数

差动放大器抑制零点漂移的效果取决于。

A、两个晶体管的静态工作点

B、两个晶体管的对称程

度 C、各个晶体管的零点漂移D、两个晶体管的放大倍数

38 差动放大电路的作用是。

A、放大差模

B、放大共模

C、抑制共模

D、抑制共模,又放大差模

差动放大电路中当UI1=300mV ,UI2=-200mV ,分解为共模输入信号 UIC= d mV ,差模输入信号 UID= a mV 。

A、500

B、100

C、250

D、50

多级放大器前级输出电阻,可看成后级的。

A、信号源阻

B、输入电阻

C、电压负载

D、电流负载

在输入量不变的情况下,若引入的是负反馈 ,则以下说确的是

。A、输入电阻增大B、输出量增大

C、净输入量增大

D、净输入量减小

48、(2-3,低 )为了实现稳定静态工作点的目的,应采用。

A 、交流正反馈

B 、交流负反馈C、直流正反馈D、直流负反馈

关于理想运算放大器的错误叙述是()。

A.输入阻抗为零,输出阻抗也为零; B.输入信号为零时,输出处于零电位; C.频带宽度从零到无穷大; D.开环电压放大倍数无穷大

在差动电路中,若单端输入的差模输入电压为20V,则其共模输入电

压为()。

A. 40V

B. 20V

C. 10V

D. 5V

1、理想运放的两个重要结论是()

A 虚断 VI+=VI- ,虚短 i I+=iI-

B 虚断 VI+=VI-=0

C 虚断 VI+=VI-=0,虚短i I+=iI-

D 虚断 i I+=iI-=0

2、对于运算关系为V0=10VI 的运算放大电路是(, i I+=iI-=0

,虚短 VI+=VI-

)

A 反相比例运算电路

B 同相比例运算电路

C 电压跟随器

D 加法运算电路

3、电压跟随器,其输出电压为V0=1 ,则输入电压为

()A VI B -VI C1 D -1

同相输入电路, R1=10K,Rf=100K ,输入电压 VI 为 10mv ,输出电压V0为()

A-100mv B100mv C10 mv D-10 mv

5、加法器, R1= Rf=R2=R3=10K, 输入电压 V1=10 mv,V2=20 mv , V3=30 mv ,则输出电压为()

A60mv B100mv C10 mv D-60 mv

6、反相输入电路, R1=10K,Rf=100K ,则放大倍数 AVf 为()A10B100C -10 D -100

电流并联负反馈可以使输入电阻()输出电阻()

A增大,减小 B 增大,增大

C 减小,减小D减小,增大

如图1-2所示的电路中, A 点电位为多少?

(A)6V(B)0V(C)3V(D)-6V

试回答在下列几种情况下,应分别采用哪种类型的滤波电路?

1.有用信号频率为10Hz。()

2.有用信号频率低于1000Hz 。()

3.希望抑制 50Hz 交流电源的干扰。()

4.希望抑制 2kHz 以下的信号。()

(从 a.低通 ,b.高通 ,c.带通 ,d.带阻四种滤波电路名称中选择一种填写

在各小题后的括号中)

1.使用差动放大电路的目的是为了提高()。 A 输

入电阻 B电压放大倍数 C抑制零点漂移能力 D 电流放大倍数

2.差动放大器抑制零点漂移的效果取决于()。

A 两个晶体管的静态工作点

B 两个晶体管的对称程度

C 各个晶体管的零点漂移

D 两个晶体管的放大倍数3.差模输入信号是两个输入信号的(),共模输入信号是两个输入信号的()。

A和 B差 C比值 D 4.电路的差模放大倍数越大表示(有用信号的放大倍数越大A 平均值

),共模抑制比越大表示()。

B 共模信号的放大倍数越

大

C抑制共模信号和温漂的能力越强

5.差动放大电路的作用是()。

A 放大差模

B 放大共模

C 抑制共模

D 抑制共模,又放大差模

6.差动放大电路由双端输入变为单端输入,差模电压增益是(

A 增加一倍

B 为双端输入的1/2

C 不变

D 不定

)。

7.差动放大电路中当 UI1=300mV ,UI2=-200mV入信号 UIC= ()mV ,差模输入信号 UID= (,分解为共模输)mV 。

A500B100C250D50

8.在相同条件下,阻容耦合放大电路的零点漂移(A 比直接耦合电路大 B 比直接耦合电路小

)。

C 与直接耦合电

路相同

9.差动放大电路由双端输出改为单端输出,共模抑制比KCMRR 减小的原因是()。

A AUD 不变, AUC 增大

B AUD 减小, AU

C 不变

C AU

D 减小, AUC 增大 D 1.直流放大器中的级间耦合通常采用((A)阻容耦合(B)变压器耦合AUD 增大, AUC

C)

(C)直接耦合

减小

(D)

电感抽头耦合

2.差分放大电路的作用是( A )

(A)放大差模信号,抑制共模信号(B)放大共模信号,抑制差模信号(C)放大差模信号和共模信号 (D) 差模信号和

共模信号都不放大

3.集成运放输入级一般采用的电路是(A)

(A)差分放大电路(B)射极输出电路(C)共基极电路(D)电流串联负反馈电路

4.典型差动放大电路的射极电阻Re 对()有抑制作用。

(A)差模信号(B)共模信号(C)差模信号与共模信号(D)差模信号与共模信号都没有

5.集成运放有(C)。

(A)一个输入端、一个输出端(B)一个输入端、二个输出端(C)二个输入端、一个输出端(D)二个输入端、二个输出端6.电路如图所示,这是一个(C)差动放大电路。

(A)双端输入、双端输出(B)双端输入、单端输出(C)单端输入、双端输出(D)单端输入、单端输出

1、十进制数1000对应二进制数为,对应十六进制数为。A:①1111101010②1111101000③1111101100④1111101110 B:① 3C8

② 3D8

③ 3E8

④ 3F8

2、十进制小数为 0.96875 对应的二进制数为,对应的十六进制数为。

A:① 0.11111 ② 0.111101 ③ 0.111111 ④ 0.1111111 B:

① 0.FC ② 0.F8 ③ 0.F2 ④ 0.F1

3、二进制的 1000001 相当十进制的,二进制的100.001可以表示为。

A:①62②63③64 ④65

B:① 23+2 –3② 22+2 –2③ 23+2 –2④ 22+2 –3

4、十进制的 100 相当于二进制。

①1000000

②1100000

③1100100

④1101000

5、八进制的 100 化为十进制为,十六进制的100 化为十进制为。

A:①80②72③64 ④56

B:① 160 ② ③ 230 ④ 256

6、在答案群所给出的关系式中正确的为,在给出的等式中不正确的为。

A:①0.1112<0.7510 ② 0.78>0.C16 ③ 0.610>0.AB16 ④ 0.1012<0.A

16

B:

①0.87510=0.E16 ② 0.748=0.937510 ③ 0.1012=0.A16 ④ 0.3116

=0.1418

7、十六进制数FFF.CH相当十进制数。

A:①4096.3②4096.25③4096.75④4095.75

8、2005 年可以表示为 ______年;而 37308 年是指 ______年。

A:① 7C5H ② 6C5H ③ 7D5H ④ 5D5H

B:① 200010 ② 200210 ③ 200610 ④ 200810

9、二进制数10000.00001可以表示为;将其转换成八进制数为;将其转换成十六进制数为。

A:① 25+2 –5② 24+2 –4③ 25+2 –4④ 24+2 –5

B:① 20.02 ② 02.01 ③ 01.01 ④ 02.02

C:① 10.10 ② 01.01 ③ 01.04 ④ 10.08

10、对于不同数制之间关系的描述,正确的描述为。

① 任意的二进制有限小数,必定也是十进制有限小数。② 任意的八

进制有限小数,未必也是二进制有限小数。③ 任意的十六进制有限小数,不一定是十进制有限小数。④ 任意的十进制有限小数,必然也是八进制有限小数。

11、二进制整数 1111111111 0.111111 转换成十进制数为A:① 1021 ② 1023 ③ 1024

转换为十进制数为

。

④ 1027

,二进制小数

B:① 0.9375 ② 0.96875 ③ 0.984375 ④ 0.9921875

12、十进制的160.5相当十六进制的,十六进制的10.8 相当十进制的。将二进制的0.100111001表示为十六进制为,将十六进制的100.001表示为二进制为。

A:① 100.5 ② 10.5 ③ 10.8 ④ A0.8

B:① 16.8 ② 10.5 ③ 16.5 ④ 16.4

C:① 0. ② 0.9C1 ③ 0.9C4 ④ 0.9C8

D:① 28+2 –8 ② 28+2 –9 ③ 28+2 –10 ④ 28+2 –12

一、选择题(每题 5 分,共 10 题,总分 50 分)

1、组合逻辑电路产生竞争冒险的可能情况是

A.2 个信号同时由 0→1

B. 2 个信号同时由 1→0

C. 1 个信号为 0,另 1 个由 0→1

D. 1 个信号为 0→1,另 1 个由 1→0

2、若在编码器中有50 个编码对象,则要求输出二进制代码位数为

A. 5B、6C、10D、50

3、一个16 选一的数据选择器,其地址输入(选择控制输入)端有

()个。 A.1B.2C.4D.16

4、一个 8 选一数据选择器的数据输入端有()个

A、8

B、2

C、3

D、4

5、在下列逻辑电路中,不是组合逻辑电路的有()。A、译码器B、编码器 C、全加器 D、寄存器

6、101 键盘的编码器输出()位二进制代码

A. B. 6C. 7D. 8

7、以下电路中,加以适当辅助门电路,()适于实现单输出组合逻辑电路

A.二进制译码器 B、加法器 C、数值比较器 D、七段显示译码器

8、组合逻辑电路在电路结构上的特点下列不正确的是()

A、在结构上只能由各种门电路组成

B、电路中不包含记忆(存储)元件<

C、有输入到输出的通路

D、有输出到输入的反馈回路

9、n 个变量可以构成()个最小项。

A、n

B、2

C、2^nD 、2^n-1

10、标准与或式是由()构成的逻辑表达式。

A、与项相或

B、最小项相或

C、最大项相与

D、或项相与

1.下列表达式中不存在竞争冒险的有。

A.Y= B +AB

B.Y=AB+ B C

C.Y=AB C +AB

D.Y=(A+ B )A D

2.若在编码器中有 50 个编码对象,则要求输出二进制代

码位数为位。

A.5

B.6

C.10

D.50

3.一个 16 选一的数据选择器,其地址输入(选择控制输

入)端有个。

A.1

B.2

C.4

D.16

4.下列各函数等式中无冒险现象的函数式有。

A.F BC AC AB

B.F AC

BC

AB C.F AC BC AB AB

D.F BC AC AB BC AB AC

E.F BC AC AB AB 5.函数F AC

冒险现象。

AB BC,当变量的取值为时,将出现

A.B=C=1

B.B=C=0

C.A=1,C=0

D.A=0,B=0

6.四选一数据选择器的数据输出 Y与数据输入

址码 Ai 之间的逻辑表达式为 Y=。

Xi和地

A.A1A0X0A1A0X1A1A0X2A1A0X3

B.A1A0X0

C.A1A0X1

D.A1A0X3

7.一个8选一数据选择器的数据输入端有个。

A.1

B.2

C.3

D.4

E.8

8.在下列逻辑电路中,不是组合逻辑电路的有

A.译码器

B.编码器

C.全加器

寄存器

9.八路数据分配器,其地址输入端有个。D.

。

A.1

B.2

C.3

D.4

E.8

10.组合逻辑电路消除竞争冒险的方法有。

A. 修改逻辑设计

B.在输出端接入滤波电容

C.后级加缓冲电路

D.屏蔽输入信号的尖峰干扰11.101键盘的编码器输出位二进制代码。

A.2

B.6

C.7

D.8

12.用三线-八线译码器 74LS138实现原码输出的8路数

据分配器,应。

A. ST A =1 ,ST B =D ,ST C =0

B.ST A=1, ST B=D, ST C=D

C. ST A =1 ,ST B =0 ,ST C =D

D.ST A=D, ST B=0, ST C=0 13.以下电路中,加以适当辅助门电路,适于实现

单输出组合逻辑电路。

A.二进制译码器

B.数据选择器

C.数值比较器

D.七段显示译码器

14.用四选一数据选择器实现函数 Y= A1A0A1A0,应使。

A.D 0=D 2=0 ,D1=D 3=1

B.D 0=D 2=1,D1=D 3=0

C.D 0=D 1=0 ,D2=D 3=1

D.D 0=D 1=1 ,D2=D 3=0 15.用三线-八线译码器 74LS138和辅助门电路实现逻辑函数 Y= A2A2A1,应。

A. 用与非门, Y= Y0Y1Y4Y5Y6Y7

B.用与门, Y= Y2Y3

C.用或门,Y= Y2Y3

D.用或门,

Y= Y0Y1Y4Y5 Y6Y7

1.N 个触发器可以构成能寄存位二进制数码

的寄存器。

A.N-1

B.N

C.N+1

D.2 N 2.在下列触发器中,没有约束条件的是。

A.主从 JK

B.主从 D

C.同步 RS

D.边沿 D

3.一个触发器可记录一位二进制代码,它有个稳态。

A.0

B.1

C.2

D.3

4.存储 8 位二进制信息要个触发器。

A.2

B.3

C.4

D.8

5 .对于 T 触发器,若原态 Q n =0 ,欲使新态 Q n + 1 =1 ,应使输入 T=。

A.0

B.1

C.Q

D. Q

6 .对于 T 触发器,若原态 Q n =1 ,欲使新态 Q n + 1 =1 ,应使输入 T=。

A.0

B.1

C.Q

D. Q

7 .对于 D 触发器,欲使 Q n + 1 =Q n,应使输入 D=。

A.0

B.1

C.Q

D. Q

8.对于 JK 触发器,若 J=K,则可完成触发器的逻辑功能。

A.RS

B.D

C.T

D.T ˊ

9 .欲使 JK 触发器按 Q n + 1 =Q n工作,可使 JK 触发器的输端。

A.J=K=0

B.J=Q,K=Q

C.J= Q,K=Q

D.J=Q,K=0

10 .欲使 JK 触发器按 Q n + 1 = Q n工作,可使 JK 触发器的

输端。

A.J=K=1

B.J=Q,K=Q

C.J= Q,K=Q

D.J=Q,K=1

11 .欲使 JK 触发器按 Q n + 1 =0 工作,可使 JK 触发器的输入端。

A.J=K=1

B.J=Q,K=Q

C.J=Q,K=1

D.J=0,K=1

12 .欲使 JK 触发器按 Q n + 1 =1 工作,可使 JK 触发器的输入端。

A.J=K=1

B.J=1,K=0

C.J=K=Q

D.J=K=0

13 .欲使 D 触发器按 Q n + 1 = Q n工作,应使输入 D=。

A.0

B.1

C.Q

D. Q

14.下列触发器中,克服了空翻现象的有。

A.边沿 D 触发器

B.主从 RS 触发器

C.同步 RS 触

发器

D.主从 JK触发器

15.下列触发器中,没有约束条件的是。

A.基本 RS触发器

B.主从 RS触发器

C.同步 RS 触

发器

D.边沿 D触发器

16.描述触发器的逻辑功能的方法有。

A.状态转换真值表

B.特性方程

C.状态转换图

D.状态转换卡诺图

17.为实现将 JK触发器转换为 D 触发器,应

使。

A.J=D,K=D

B. K=D,J=D

C.J=K=D

D.J=K=D

18. 边沿式 D 触发器是一种稳态电路。

A.无

B.单

C.双

D.多

1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高

B.触发器利用率高

C.电路简单

D.不受时钟 CP控

制。

2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4

B.5

C.9

D.20

3.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器

B.加法器

C.数码寄存器

D.数据选择器

4. N 个触发器可以构成最大计数长度(进制数)为的计数器。

2N

5. N 个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1

B.N

C.N+1

D.2N

6.五个 D 触发器构成环形计数器,其计数长度为。

A.5

B.10

C.25

D.32

7.同步时序电路和异步时序电路比较,其差异在于后者

。

A.没有触发器

B.没有统一的时钟脉冲控制

C.没有稳定状态

D.输出只与部状态有关

8.一位 8421BCD 码计数器至少需要个触发器。

A.3

B.4

C.5

D.10

9.欲设计 0,1,2,3,4,5,6,7 这几个数的计数器,如果设计合

理,采用同步二进制计数器,最少应使用级触发器。

A.2

B.3

C.4

D.8

10.8 位移位寄存器,串行输入时经个脉冲后, 8 位数码全部移入寄存器中。

A.1

B.2

C.4

D.8

11.用二进制异步计数器从 0 做加法,计到十进制数178,则最少需要个触发器。

A.2

B.6

C.7

D.8

E.10

12.某电视机水平 - 垂直扫描发生器需要一个分频器将31500H Z的脉冲转换为 60H Z的脉冲,欲构成此分频器至少需要个触发器。

A.10

B.60

C.525

D.31500

13.某移位寄存器的时钟脉冲频率为100KH ,欲将存放在该寄存器

Z

中的数左移 8 位,完成该操作需要时间。

A.10μS

B.80μS

C.100μS

D.800ms

14.若用 JK 触发器来实现特性方程为Q n 1AQ n AB,则JK端的方程为。

A.J=AB ,K= A B

B.J=AB ,K= AB

C.J= A B,K=AB

D.J= AB, K=AB

15.要产生 10 个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要片。

A.3

B.4

C.5

D.10

16.若要设计一个脉冲序列为1101001110 的序列脉冲发生器,应选

用个触发器。

A.2

B.3

C.4

D.10

10 .组合逻辑电路中的冒险是由于引起的。

A.电路未达到最简B.电路有多个输出

C.电路中的时延D.逻辑门类型不同

11 .用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?

A.在输出级加正取样脉冲B.在输入级加正取样脉冲

C.在输出级加负取样脉冲D.在输入级加负取样脉冲

12 .当二输入与非门输入为变化时,输出可能有竞争冒险。

A . 01 →10B. 00 →10C. 10 →11 D.11→01

13 .译码器74HC138的使能端E1E2E3取值为时,处于允许译码状态。

A.011B.100C.101D.

14 .数据分配器和A.加法器

有着相同的基本电路结构形式。

B.编码器 C.数据选择器D.译

码器

15 .在二进制译码器中,若输入有 4 位代码,则输出有个信号。

A.2B.4C.8D.16

16 .比较两位二进制数A=A 1A0和 B=B1B0,当 A>B 时输出 F=1,

则 F 表达式是

。

A.F A1B1B.F A1A0B1 B0

C.F A1B1A1B1A0B0D.F A1B1A0B0

17 .集成 4 位数值比较器 74LS85 级联输入I A<B、I A=B、I A>B分别接

001 ,当输入二个相等的 4 位数据时,输出F A<B、F A=B、F A>B分别为。

A.B.001C.100D.011

18 .实现两个四位二进制数相乘的组合电路,应有个输出函数。

A. 8B.9C.10D.11

19.设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要个异或门。

A.2B.3C.4D.5

20 .在图 T3.20 中,能实现函数F AB BC 的电路为。

+5V74LS138

Y 0 141312111098C A 0Y 0

A≥ 1B A 1Y 1

&&A A 2Y 2&

≥ 1Y 3

1

F F

&&B Y 4

≥ 1 C 1 E 1Y 5

12345670 E 2Y 6

Y 7 0 E 3Y 7

A C

B F

(a)(b )(c)

图 T3.20

A.电路(a)B.电路(b )C.电路(c)D.都不是

1.DRAM2164 (64K×1)外部引脚有()。

A.16 条地址线、 2条数据线

B.8 条地址线、 1 条数据线

C.16 条地址线、 1条数据线

D.8 条地址线、 2 条数据线

分析:从芯片容量(64K×1B)来看,有64K 个编址单元,应有16

条地址线( 216 =64K )。但 DRAM 芯片集成度高、容量大、引脚数量

不够,一般输入地址线采用分时复用锁存方式,即将地址信号分成二组、共用一组线,分两次送入片。而2164 却有二条数据线,一条作为

输入,一条作为输出。答案: D

2.8086 能寻址存贮器的最大地址围为()。

A.64KB

B.512KB

C.1MB

D.16KB

分析:8086 有 20 条地址总线 A0 ~A19,它可以表示

220=1M 个不同

的状态。答案: C

3.若用 1K×4 的芯片组成 2K×8 的 RAM ,需要()片。

A.2 片

B.16 片

C.4 片

D.8 片

分析: 2 片(1K×4)一组构成 1K×8 的 RAM ,所以需要 4 片。答案:

C

4.某计算机的字长是32 位,它的存储容量是64K 字节,若按字编址,它的寻址围是()。

A.16K

B.16KB

C.32K

D.64K

分析:因字长是32 位, 4 个字节才能构成一字单元,若按字编址,

则 64KB÷4B=16K 答案: A

5.采用虚拟存储器的目的是()。

A.提高主存的速度

B. 扩大外存的存储空间

C.扩大存储器的寻址空

间 D.提高外存的速度

分析:虚拟存储器的作用是使编程人员在写程序时不用考虑机器的实

际存容量,可以写出比实际配置的物理存储器容量大很多的程序。答案:C

6.RAM 存储器中的信息是()。

A.可以读 / 写的

B.不会变动的

C.可永久保留的

D.便于携带的

分析:RAM 是一种随机读 / 写存储器,一但掉电其存储的信息就会丢

失。答案: A

7.用 2164DRAM 芯片构成 8086 的存储系统至少要()片。

A.16

B.32

C.64

D.8

分析: 8086 的存储系统必须有两存储体,偶存储体和奇存储体,才

能进行字操作。而 2164 的容量为 64K×1,需要 8 片才能构字节单元,

即一个存储体至少要 8 片 2164 。答案: A

8.8086 在进行存储器写操作时,引脚信号和 DT/ 应该是()。

A.00

B.01

C.10

D.11

分析:当 8086CPU 访问存时, =1 ,进行写操作时DT/=1 。答案: D