并行计算机体系结构

第一章并行计算机体系结构

在介绍并行算法及其软件设计之前,必须先介绍一下并行计算机与分布式并行的一些基本知识。目前国内这方面的资料不是很完善,为此,本章将阐述一下并行计算机体系结构的一些基本知识。

1.1并行计算机定义

简单地讲,并行计算机就是由多个处理单元(以下也称为处理器,或简称为CPU)组成的计算机系统,这些处理单元相互通信和协作能快速、高效的求解大型复杂问题。

定义中涉及的问题:

a)并行计算机的规模:, 例如处理单元有多少,这就涉及到系统是小规模的(十个或几

十个)、中规模的(上百个)和大规模的(成千上万个)的问题;

b)处理单元的功能:处理单元的功能有多强,这就涉及到系统的组织策略是平行对称

的“蚁军法”(Army of Ants)或是一种主从的形式“象群法”(Hert of Elephants) 的问题;

c)处理单元之间怎样连接,这就涉及到系统是按照什么样的拓朴结构彼此互连起来的

问题;

d)处理单元的数据是如何传递的,这就涉及到通信是按照共享变量方式的或消息传递

方式的问题。

e)各处理单元彼此相互协作共同求解大型复杂问题,则涉及到的问题更多,例如如何

保证多处理单元操作的顺序性,这就涉及到同步互斥问题;如何确保共享数据的完整性问题,这就涉及到不同存储层次中的数据的一致性问题。

f)此外,还有求解具体问题的并行程序的编写、调试、运行和性能分析等方面的问题。

1.2并行机的由来

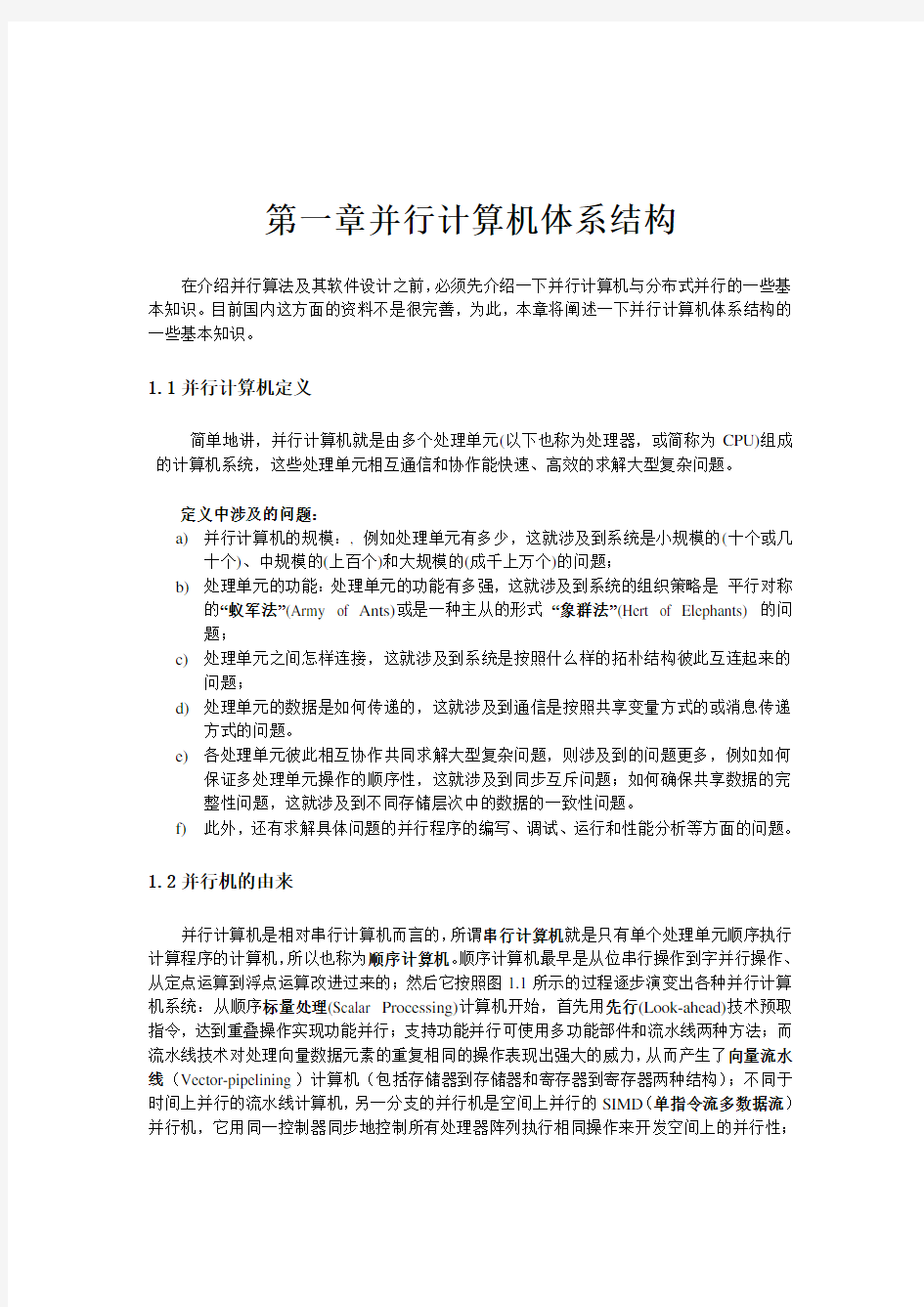

并行计算机是相对串行计算机而言的,所谓串行计算机就是只有单个处理单元顺序执行计算程序的计算机,所以也称为顺序计算机。顺序计算机最早是从位串行操作到字并行操作、从定点运算到浮点运算改进过来的;然后它按照图1.1所示的过程逐步演变出各种并行计算机系统:从顺序标量处理(Scalar Processing)计算机开始,首先用先行(Look-ahead)技术预取指令,达到重叠操作实现功能并行;支持功能并行可使用多功能部件和流水线两种方法;而流水线技术对处理向量数据元素的重复相同的操作表现出强大的威力,从而产生了向量流水线(Vector-pipelining)计算机(包括存储器到存储器和寄存器到寄存器两种结构);不同于时间上并行的流水线计算机,另一分支的并行机是空间上并行的SIMD(单指令流多数据流)并行机,它用同一控制器同步地控制所有处理器阵列执行相同操作来开发空间上的并行性;

如果用不同的控制器异步地控制相应的处理单元执行各自的操作,则就派生出另一类非常主要的MIMD(多指令流多数据流)并行机;其中,如果各处理单元通过公用存储器中的共享变量实现相互通信,则就称为多处理机(Multiprossors);如果处理单元之间使用消息传递的方式来实现相互通信,则就称为多计算机(Multicomputers),它也是当今最流行的并行计算机,也是本书讨论的重点。

大规模并行处理机(MPP)

图1.1从标量到向量和并行计算机的演变

1.3当代并行机系统

自20世纪70年代初到现在,并行计算机的发展已有20多年的历史.在此期间,出现了各种不同类型的并行机,包括历史上曾经风行一时的并行向量机PVP(Parallel Vector Processor)和SIMD 计算机,但它们现在均已衰落了下来,而MIMD类型的并行机却占了主导地位。当代的主流并行机是可扩放的并行计算机(Scalable-Parallel Computer),包括共享存储的对称多处理机SMP(Symmetric Multiprocessor),分布存储的大规模并行机MPP(Massively Parallel Processor),分布式共享存储DSM(Distributed Shared Memory)多处理机和工作站机群COW(Cluster of Workstations)以及刚刚兴起的跨地域性的、用高速网络将异构性计算节点连接起来满足用户分布式计算要求的所谓网格计算环境GCE(Grid Computational Environment)。本课程将重点讨论前4种当代可扩放的主流并行计算机。

1.4高性能计算机

顺便讲一下并行计算机与高性能计算机的关系。其实,高性能计算机并无明确严格的定义。因为性能可定义为求解问题所花费的时间的倒数,即求解问题的速度,所以按此意义,只要那些速度非常快的计算机都可认为是高性能计算机。当然,能高速求解问题的计算机,可以包括大型计算机(Mainframe),如早期的IBM370系列;超级计算机(Supercomputer),如Cray-1向量计算机以及各种并行计算机。因为为了达到高性能,仅靠改进电路工艺,提高单

机器件速度是有限的,所以使用并行计算机的方法则更为普通和有效,于是并行计算机也就渐渐地变成了高性能计算机的同义词了,这种说法虽不严格,但已被普遍认可。

1.5并行计算机发展背景

90年代,并行计算机已成为计算机技术中的关键部分,预计下20年它对计算机的发

展冲击会更大。并行计算机虽然有着漫长的历史,但其突飞猛进的发展却是得益于高度集成的微处理器芯片和快速大容量存储器芯片。历史上看,从60年代中期开始,小型计算机(Minicomputer)和大型计算机(Mainframe)便迅速发展起来;从70年代初期起,超级计算机(Supercomputer)则得以蓬勃发展;但到了80年代中期,微处理器的性能(速度)每年改进50%,而大型计算机和超级计算机的性能,每年只改进25%。高度集成的、单片CMOS 微处理器的性能稳定地压倒了那些较大的和较昂贵的其它处理器芯片,这样使用小型的、便宜的、低功耗的和批量生产的处理器作为基本模块来构筑计算机系统就变得非常直观的事了。到了90年代后期,单片微处理器占据着计算的各个方面,而并行计算也撑管了主流计算的很多领域。在微处理器出现之前,为了获得高性能,人们主要是通过特殊的电路工艺和机器组织,而现今大家普遍意识到使用多个处理器构成并行机和编写并行程序才是更为有效的途径。

以上是并行机发展的基本硬件背景。下面我们将深入讨论,是什么力量和趋势促进了并行计算机的发展,包括应用和技术进展以及并行计算机体系结构发展趋势。

1.6应用需求

从计算机的市场上看,一般的计算机用户都是使用低端计算机(PC机和工作站等),而那些富有挑战性的应用问题都需要使用高端计算机(超级计算机和并行计算机)。这些挑战的应用问题大都来自复杂科学计算,大型工程应用以及大存储容量和高RAS(Reliability ,Availability ,Serviceability)的商务处理,而且市场统计表明,科学和工程计算方面的应用只占并行机市场的小头,而大头却在众多的商业事务处理上。

1.6.1科学和工程计算

主流的科学计算主要有物理、化学、材料科学、生物学、天文学和地球科学等等;典型的工程应用主要有能源勘探、油藏模拟、药物分析、燃烧效率分析、汽车碰撞模拟、飞行器气流分析等等。这些当代科学与工程问题对计算机的应用需求,典型地反映在美国HPCC 计划和美国ASCI计划中。

(1)美国HPCC计划:美国为了保持在高性能计算机和通信领域中的世界领先地位,美国科学、工程、技术联邦协调理事会于1993年向国会提交了题为“重大挑战项目:高性能计算和通信”(High Performance Computing and Communication)的报告,简称为HPCC计划,

表1.1美国HPCC 计划公布的重大挑战性应用课题一览表

HPCC 计划所提出的某些重大挑战性课题的计算需求如图1.3所示。它列出了支持科学模拟、先进计算机辅助设计和大型数据库与信息检索操作的实时处理等所需要的处理速度和存储器容量的量级。

HPCC 计划中的重大挑战课题对计算机提出了3T 要求:即1Tflops 的计算能力、1TB 的主存容量和1TB/s 的I/O 带宽。在HPCC 计划提出的当时,性能最好的计算机与3T 要求也相差甚远:速度慢100~1000倍,而存储容量太小,I/O 带宽过窄。这就刺激了高性能并行计算机的研制。事隔3年之后,世界上第一台峰值速度超过1Tflops 的高性能并行计算机才由Intel 公司于1996年12月研制成功。

(2)美国ASCI 计划:全面禁止核试验条约签订后,核武器的研究代之以实验室数值模拟。因此禁试后数值模拟成了唯一可能进行的全系统(虚拟)试验。这样,1996年6月由美国能源部联合美国三大核武器实验室(Lawrence Livermore 国家实验室、Los Alamos 国家实验室和Sandia 国家实验室)共同提出了 “加速战略计算创新”(Accelerated Strategic

全球气候变化

统速度

存储器容量

1000G B

100G B

10G B

1G B 100M B 10M B

人类基因

图1.2 HPCC 方面重大挑战性课题的需求

Computing Initiative ,简称为ASCI)项目计划。提出通过数值模拟,评估核武器的性能、安全性、可靠性、更新等。要求数值模拟达到高分辨率、高逼真度、三维、全物理、全系统的规模和能力。该计划被认为是与当年曼哈顿计划等同的一个巨大的挑战,不仅需要科学界的参与,也需要计算机工业界合作,提供保障ASCI 应用所需的计算机平台。为此,三大核武器实验室分别向美国三大公司(Intel 、IBM 和SGI/CRAY )预定了峰值速度超过1Tflops 的并行计算机。美国能源部计划在2003年要使用运算速度为100Tflops 、内存容量为50TB 的并行机(见表1.2)。目前ASCI 计划正把各项应用需求与计算平台推进到万亿级规模的体

系中去(即每秒可执行万亿次浮点运算、万亿个字节的RAM、数十万亿个字节的磁盘、千万亿个字节的档案存储器、数百亿个字节的网络带宽)。

表1.2美国ASCI计划中的并行机性能一览表

1.6.2 商务应用

统计数据表明,科学和工程计算方面的应用只占并行机销售市场的少部分,大部分应用却在商业事务处理中。它们在计算能力方面可能不像科学和工程计算要求那么强大,但它们却需求大的存储和磁盘容量以及高的I/O传输率,同时对可靠性、有效性和服务性(即RAS 要求)也要求很高。典型的商务应用有数据库管理和查询、在线事务处理、数据仓库、数据开采和决策支持系统等。评价这些应用时,可将计算机系统的速度、容量直接换算成每分钟事务处理数tpm(Transccctions Per Minute)。TPC(Transaction Processing Performance Council)所观察的数据表明:商务中使用并行机是很流行的,几乎所有数据库硬件或软件的供货商都提供多处理机系统,其性能优于单处理机产品;这些并行系统不仅包含了大规模并行系统,而且也有中规模(几十个处理器)甚至小规模(2~4个处理器)的并行系统。

1.6.3 国计民生的需求

这方面的要求与国计民生直接休戚相关,包括医疗保健、教育和培养、能源管理、环境保护、文化娱乐和国防安全等。这些方面的应用大都涉及到高性能并行机的使用。将传统的科学和工程计算转为娱乐业的一个很有趣的例子就是,1995年世界上第一部全计算机动画片“玩具总动员”(Toy Story)就是在由上百台Sun工作站组成的并行计算机上制作成的。

1.6.4 网络计算应用

高性能并行计算最近的一种应用趋势是以网络为中心的某些应用,这些应用均运行在通过网络连接的多台计算机上,其中网络可以是LAN或W AN。这些应用主要要求有效的通信、协同和互动操作、良好的安全性等。有代表性的应用实例包括WWW服务、多媒体处理、视频点播、电子商务、数字图书馆、远程学习和医疗诊断等。网络计算的一个典型例子是1994年4月26日,美国宣布破译了世界上最长的RSA129密码。它在Internet上,使用1600台计算机,用600多个人工作了8个月,成功地破译了这个由129位数字组成的密码。

1.7 高性能计算机软硬件技术进展

已如前述,并行机的进展主要得益于高集成度的微处理器芯片和大容量的存储器芯片;而并行机真正与普通商品工艺技术相结合才产生了根本的变化。本小节将简述一下硬件技术

和软件技术方面的进展对并行机发展的影响。 1.7.1 硬件进展

硬件方面的进展包括(微)处理器芯、存储器芯片、磁盘和磁带以及通信网络等。 (1)处理器:以 Intel80x86微处理器系列为例,参照图1.4,在过去的17年(1978-1995),

110

100

1000

19788086

198280286

198580386

198980486

1993Pentium

1995

Pentium Pro

改进因子

图1.3 Intel 微处理器性能进展

片上的晶体管数增加几乎200倍,时钟频率增加近31倍,而峰值速度达900倍;相应地平均年增长率依次为36%,22%和49%。上述这种性能改进的现象,其实早就由Intel 公 司的共同创始人Moore 于1979年所观察到。现在已成为普遍认可的Moore 定律了,它有3种表述方法:①微片上晶体管的数目大约每18~24个月番一番(假定芯片的价格保持不变);②微处理器的速度大约每18~24个月番一番(假定处理器的价格保持不变);③微片的价格大约每18~24个月下跌48%(假定处理器速度或片上存储容量相同)。

按照上述的工艺技术改进的趋势,估计在2000年前夕,单片上可集成100万个晶体管,这样就有可能在单片上制造包括内存和I/O 支持的较强功能的计算机系统,即片上计算机系统(Computer System on Chip );或者在单片上放置多个处理器,即单片并行结构(Parallel Architecture into Single Chip )。

(2)存储系统:存储器也是机器硬件的主要组成部分,不幸的是,存储器工艺的进展远跟不上处理器工艺进展的步伐。例如,以IBMPC 系列为例,如图1.5所示,Pentium Pro PC 的速度比PC/XT 的速度改善多于900倍,而主存容量才增加64倍、硬盘容量增加85倍,

110

100

1000

1982PC/XT(8088)

1984

PC/AT(80286)

198880386 PC

199080486 PC

1993Pentium PC

1995

Pentium Pro PC

改进因子

图1.4 IBMPC 性能进展

但是存储器访问仅改进不到10倍。处理器和存储器性能改进的悬殊差异,迫使在近代并行

机中使用多级存储器组织,而且多级高速缓存总是提供的。

由于存储器系由半导体芯片组成,而辅存(外存)是由磁盘、磁带组成且总涉及到机械运动,所以辅存速度远远慢于主存,因而常成为系统的瓶颈。现今主存的访问速度和带宽比磁盘高2~3个数量级、比磁带高3~7个数量级,而且RAM 速度的改进速率快于磁盘和磁带。

(3)通信的网络:以Intel MPP 为例,如图1.6所示,从1985年-1996年其处理器速度、

110

100

1000

10000

1985iPSC/1

1987iPSC/2

1989iPSC/860

1992Paragon

1996TFLOP

改进因子

图1.5 Intel MPP 系统计算和通信性能进展

带宽和延迟性能的改进三者均呈指数增长,其中通信性能(包括带宽和延迟)的改进远远慢于处理器速度的改进,而带宽的改进却快于启动延迟的改进。10年期间,Intel MPP 的处理器速度增加5000倍,带宽增加760倍,而启动延迟仅改进86倍。表1.3汇总了Cray 超级计算机和Intel MPP 系列硬件性能参数的演变情况。

表1.3 Cray 超级计算机和Intel MPP 系列硬件性能参数演变一览表

1.7.2 软件进展

比起串行软件来,并行软件的发展是非常缓慢的,这是因为并行软件一是复杂,二是有赖于并行机结构,三是缺乏公共标准和提供给用户的满意的软件工具环境。随着当代并行计算机朝着DSM 、MPP 和机群方向发展,使得并行软件的危机更加尖锐。然而,多年来人们通过实践也逐步地对并行软件有了较深刻的认识和取得了一些进展:①现在人们已经比较清楚地知道了并行软件的要求和关键问题是什么,而且也开始出现了一些有效地解决方案;②对开发可移植和可扩展的与体系结构无关的软件已经达到了共识,甚至牺牲某些性能也应维

持与结构无关的基本原理;③应该开发那些公共使用的、开放式的、标准的工具,如用于多线程的Open MP 、数据并行的HPF 和消息传递的PVM 、MPI 等;④对于绝大多数应用,一个普遍的方法是使用串行Fortran 或C ,再加上某些用于进程通信、管理和相互作用的库函数或编译制导(Compiler Directives);⑤系统和应用软件商都正在开发各自产品的并行软件版本,如所有主要的数据库销售商(IBM 、Oracle 、Sybase 、Informix 等)都正提供并行数据库。

1.8 处理器结构发展趋势

开发并行度和提高性能是研究并行计算机体系结构的根本出发点。本节先讨论(微)处理器级如何开发并行度;接着讨论为了提高性能,并行机体系结构的发展变化;最后比较一下CISC 与RISC 结构。 1.8.1处理器级并行度的开发

图1.7不但反映了过去25年处理器芯片上晶体管数的增长基本服从Moore 定律,同时 也反映了第四代计算机(即VLSI )所使用的处理器芯片其并行度增加的情况。

(1)位级并行(1970-1986):直到大约1986年之前,处理器芯片上位并行占主导地位,在此期间,4位微处理器芯片不断由8位和16位微处理器芯片所代替。到80年代中期32位的微处理器已出现,但此后趋势变慢,10年之后才出现部分采用64位操作的芯片。进一步增加字长主要为了改进浮点表示和增大地址空间,但地址长度每年增加不到一位,将来使用128位似乎就够了。

1,000

10,000

100,000

1,000,000

10,000,000

100,000,000

1970

1975

1980

1985

1990

1995

2000

2005

晶体管

数

位级并行

指令级并行

线程级(?)

图1.6处理器芯片上的晶体管数及其并行度级别

(2)指令级并行(80年代中期-90年代中期):并发地执行好几条机器指令的部分叫做指令级并行。全字长操作意味着指令执行的基本步(指令译码、整数运算、地址计算)可在单周期内完成。RISC 方法展示了平均几乎每个周期可执行一条指令。RISC 微处理器性能的

进展,开拓了指令级并行度。流水线指令很适合于现代的工艺,编译技术的进展使得指令流水线更为有效。超标量(Superscalar )方法是使每个时钟周期内启动多条指令,并能由多条流水线在单周期内产生多个运算结果,它主要是用来开拓指令级并行的。为了满足增多的指令和数据带宽要求,越来越多的高速缓存均置于处理器芯片上。将微处理器和高速缓存放在同一芯片上,其间通路可作得非常宽,以满足增多的指令和数据带宽要求。但是每个周期内发送更多的指令,高速缓存的缺失会更加严重,为此提出了很多避免高速缓存缺失所造成的流水线延迟以及指令动态调度的方法。

(3)线程级并行(2000年以后):单控制线程内的指令级并行度是有限的,研究表明[3],如图1.8所示,每个周期发射2-4条指令能得到较好的加速,再多则效果不明显,即使具有无

0.511.52

2.530

5

10

15

20

每周期发射的指令

加

速

图1.7理想标量执行时多射指令的加速

限的机器资源和完美的分枝预测以及理想的重命名(Renaming ),在90%的周期内所发射的指令不会多于4条。最近的研究的经验证据是,为了获得可观的并行度,必须同时施行多控制线程[4]。所谓线程(Thread )就是控制流线(Thread of Control )的简称,系指被执行的一个指令序列;而多线程(Multithread )就是一台处理机有多个控制线程,能同时执行多条指令序列。多线程控制为大型多处理机隐藏掉较长的时延提供了一种有效机制。 1.8.2 并行结构的发展变化

(1)并行机的萌芽阶段(1964-1975):晶体管代替了电子管,缩小了计算机的体积;相对便宜的存储技术出现,扩大了计算机的存储容量,从此计算机体系结构渐渐 “定居”下来,而且逐渐形成 “家族”。60年代初期,著名的CDC6600提供了非对称的共享存储结构,其中央处理器连接了多个外部处理器,同时也采用了双CPU 。60年代后期,显赫的发明是在处理器中使用流水线和重复功能单元以获得比简单增加时钟频率更广范围的性能增加。尽管1967年Amdahl 定律[5],对增加处理器达到加速提出质疑,但在1972年,由Illinois 大学和Burroughs 公司却承担联合研制基于早期Solomon 工作的64台处理器的Illiac-Ⅳ SIMD 计算机的任务。该计划雄心勃勃,包括研究基本硬件技术、结构、I/O 设备,操作系统、程序设计语言和应用,并终于在1975年完成了世界上著名的一个16台处理器的Illiac-IV 系统。

(2)向量机的发展和鼎盛阶段(1976-1990):1976年,Cray 公司推出了第一台向量计算机Cray-1,它使用向量指令和向量寄存器以及CPU 和快速主存紧密耦合,其性能比当时的标量系统高出一个数量级。在随后的10年,人们不断地推出新的向量计算机,包括CDC 的Cyber205、Fujitsu 的VP1000/VP2000、NEC 的SX1/SX2以及我国的YH-1等。向量计算机以其高的性能几乎成了超级计算机的代名词,它的发展呈两大趋势,即提高单处理器的速度和

研制多处理器系统(如Cray X-MP )。到了80年代后期,Cray 2/Cray 3相继推出,随着标准Unix 操作系统和向量编译器的出现,越来越多的软件商可以将他们的应用程序移植到Cray 系统中,使得Cray 系列向量机几乎在很多应用领域获得了成功。但到了90年代初,向量机终因受物理器件速度的限制,Cray-3一直难产,直至Cray 公司被SGI 公司兼并,从此向量计算机就不再成为主流并行机了。

(3)MPP 出现和蓬勃发展阶段(1990-1995):90年代开始,MPP 系统逐渐地显示出代替和超越向量计算多处理机系统的趋势,早期的MPP 有TC2000(1989)、Touchstone Delta 、Intel/ Paragon (1992)、KSR-1、CrayT3D(1993)、IBMSP2(1994)和我国的曙光1000(1995)等,它们都是分布存储的MIMD 计算机。MPP 的高端机器是1996年Intel 公司的ASCI Red 和1997年SGI Cray 公司的T3E900,它们都是万亿次高性能并行计算机。90年代的中期,在中、低档市场上,SMP 以其更优的性能价格比代替了MPP ,而机群系统概念的提出也是从这一点出发的。图1.9示出了。

319

10673

50

100150200250

30035011/93

11/9411/9511/96

系统数

图1.8世界前500台最快计算机系统中PVP 、SMP 和MPP 数量分布

(4)各种体系结构(PVP 、MPP 、SMP 、DSM 、COW )并存阶段(1995年)后:从1995年以后,MPP 系统在世界前500台最快的计算机中占有量继续稳固上升;而其性能也得到了进一步的完善,如ASCI Red 的理论峰值速度已达到1Tflops ;与此同时向量计算机厂商推出的SX-4和VPP700其理论峰值速度都达到了1Tflops ;从1994年开始,SMP 由于其体系结构的发展相对成熟和卓越的性能价格比,受到了工业界用户产的普遍欢迎,如SGI Power Challenge 和我国的曙光1号。1998年以后,出现了SMP 系统和MPP 系统相结合的趋势,将SMP 系统作为单个构件块彼此连接起来形成新的机群系统,如Origin 2000,有人也将它视为DSM 系统,当然Stanford 的 DASH 才是世界上第一个真正含意下的DSM 系统。随着工作站性能的迅速提高和价格的日益下降以及高速网络产品陆续问世,一种新型的并行机体系结构便应运而生。这种系统将一群工作站或高档微机用某种结构的互连网络互连起来,充分利用各工作站的资源,统一调度、协调处理以实现高效并行计算,它就是近期甚为流行的工作站机群COW 。

1.9的并行计算机的分类

所谓并行,就是指有多个事件或过程在同一时间段或同一时刻内并发发生。并行算法的意义非常广泛,本节将围绕本论文所涉及的范围,重点讨论分布式并行算法。

1963年2月,美国Westing House 宇航实验室的工程师们利用9个CPU 部件组成了世界上第一台并行计算机。经过短短的二十几年的发展,并行机在计算效率和制造成本上都发生了巨大的变化,形式也多种多样。但是许多年以来人们一直使用了Flynn 分类法来为高性能计算机进行分类。这种分类方法的基础是根据高性能计算机中指令流和数据流的处理方式

的不同进行分类(单个或多个指令流/数据流)。一般来说高性能计算机可以分成如下四类:单指令流单数据流系统(SISD, Single Instruction Stream & Single Data Stream),它是包含一个中央处理器的常用系统,如Workstation和单个计算服务器,它并不是一个并行系统。

图1.9 SISD模型

单指令流多数据流系统(SIMD, Single Instruction Stream & Multiple Data Stream).它是多个简单的处理元件在相应的步骤里对不同的数据执行相同的指令,如Thingking Machines 的Connection Machine CM-2 和MasPar等,这类结构目前已经很少见,向量处理机通常被认为是这一系统,如Cray Y-MP C90、J916和T90系列、Convex C系列、Fujitsu VP系列、NEC SX、Connection Machine CM-2 、Maspar MP-1, MP-2系列。

图1.10 SIMD模型

多指令流单数据流系统(MISD, Multiple Instruction Stream & Single Data Stream).这类结构的大规模并行计算机国内外尚没有见到。MISD 是一种不太实际的计算机,但也有的学者把超标量机和脉动(Systolic)阵列机归属于此类。

多指令流多数据流系统(MIMD,Multiple Instruction Stream & Multiple Data Stream)。在多指令流单数据流系统中,各个处理器对各自的数据独立地执行不同的指令流,处理器之间有效地配合,当不同的处理器一起同时执行同一个作业时,就发生了并行的处理。如Cray C 90、Cray 2 、NEC SX-3、Fujitsu VP 2000 、Convex C-2 、Intel Paragon 、CM 5 、KSR-1 、IBM SP1 、IBM SP2 和Dawning 2000等。

图1.11 MIMD模型

1.10 MIMD并行计算机根据内存组织方式分类

另外,并行计算机也可以根据内存组织方式将MIMD系统划分为共享内存(Shared

Memory)MIMD系统和分布式内存(Distributed Memory)MIMD系统。

共享内存MIMD系统

在共享内存MIMD系统中,所有的处理器都独立进行操作,但是共享同一个公共的内存空间;通过控制各个处理器之间对内存的同步读写操作来实现并行。它的优点是使用者容易提高它的效率;在共享内存系统中的主要问题是处理器与存储器之间的连接,当增加处理器的数量时,存储器与处理器的连接的总的带宽不是同处理器的数目P线性地增加,而是需要)

O个连接,所以完全连接的代价很高。于是人们采用不同的方式连接网络,如用mesh P

(2

连接网络需要2P个连接,用 形网络需要P

log个连接,其它的还有网孔连接、树连接、

P

2

树网连接、金字塔连接和超立方连接。由于受互连网络容量或造价的限制,共享内存的计算机的处理器的数量无法达到很大。同时要求使用者来处理各个处理器之间的同步问题,并行编程的难度大大提高。这样的并行机有Cray Y-MP 、Convex C-2 和Cray C-90。

图1.12 共享内存系统

分布式MIMD系统

分布式MIMD系统是由多个处理器节点组成,每个处理器节点都有自己的内存,它们通过内部的网络或外部的网络来连接,每个处理器节点实际上就是一台完整的计算机,它运行时独立于其它的节点处理器节点之间只能通过网络通信来传递消息,即进行通信。使用者在编制并行程序时,需要考虑各个节点之间的同步和负载均衡问题。由于分布式MIMD系统与本论文密切相关,因此将给予重点介绍。

分布式MIMD系统的最大的优点是它的可扩展性,计算机的能力、内存容量和带宽会随着处理器节点的增加而增加;并行环境具有良好的可移植性,甚至由一些Workstation机群或PC机群就可以很容易地组合成一个高效的并行环境;另外,就单个的处理器节点而言,它可以迅速有效地对它的内存进行处理而不需要外界的任何干预。用户在设计并行程序时,只需要设计好各个节点之间的通信同步问题和通信问题就可以了。它的缺点是用户很难将现存的数据结构很好地组织并投影到各个节点上的地址空间中;各个节点之间的通信需要一些固定的延迟的开销,这在每次通信量较小同时各个节点之间比较频繁的时候表现的比较突出,有些时候通信的延迟甚至超过了数据拷贝的时间开销,因此对并行程序的设计提出了很高的要求。这类机型目前在国际上占据了主流的位置,如nCUBE Hypercube 、Intel Hypercube 、TMC CM-5 、IBM SP1, SP2 、Intel Paragon。1999年11月11日最新公布的全世界前500台高性能计算机的座次统计来看,分布式MIMD系统已经占了绝大部分,前50台超级计算机中,基本上都是采用了这一体系结构。

图1.13 分布式内存系统

混合内存系统:

尽管共享内存系统与分布式内存系统似乎有明显的区别。但许多并行系统都使用一种混合型内存组织。在共享内存系统中,每个处理器可能有一个大型超高速缓存存储器,它可以看作一个局部内存.一些系统有两级组织:处理器以共享内存模块组织成组、并通过通信网络来连接不同的处理器组.最后,分布式内存系统可以包含取得其它处理器内存中数据的软硬件支持,并使之对用户透明化.根据这种支持的具体形式,它们分别称为,‘分布共享内存”,“全局共享内存”,“全局虚内存”,等等.内存等级和性能 在向量处理器和高级RISC 处理器中,处理器运算速度都比主存储器的数据读写快得多.向量处理器中的向量寄存器和RISC 处理器中的大型高速缓存存储器置处理器与主存储器之间.这些速度非常高的存储模块用于维持处理器不间断地计算而不需要繁地访问主存储器.向量寄存器,高速缓存,局部存储器和/或全局(共享)内存一起形成内存等级。对一定的应用程序来说,它能达到的性能决定性地依赖于内存等级中“较高级”的存储器中的数据的(再)利用.因此,为了取得高性能,算法对数据的访问在(地址)空间上和时间上都应该有局部性.

1.10.11 分布式MIMD 系统的通信网络的拓扑结构

在分布式MIMD 系统中,通信网络的拓扑结构是非常重要的。一般来说,一个好的网络通信寻径的算法应该至少满足以下三个条件:

1. 完备性好,对任意情况或多数情况,只要路径存在就一定能够找到;

2. 效率高,找出的路径总是或常常是最短的;

3. 通信的开销小,信件中附加的信息少,判断方便简洁。 一些系统使用了二维或三维网格结构,其基本原因是这种网络的拓扑结构对于大部分的科学计算的算法已经足够了,而使用更高级的互连网络结构的代价很难获得实质的补偿。另外一些系统使用多级网格,如Ω形网络,多级网络的优点是二等分通信带宽与处理器的数目成线性关系,同时保证每个处理器的通信连线的数目的固定。

近些年以来,超立方体(HyperCube )系结构成了松散偶合大规模分布式并行处理系统的主流产品。SuperComputer’94会议上的典型产品是nCUBE 公司的nCUBE 2s 系列,还有IBM 公司的SP2系列。N 维超立方结构又称为Boolean 超立方体分布式网络结构。一个三维的立方体就是一个通常的立方体,它的48个节点作为立方体的8个顶点。立方体的每一条边将两台计算机节点相连,每个节点都与另外3个节点直接相邻。一般来说,包含n N 2=个节点的网络可以构成一个在每一维含有2个节点的N 维超立方体)log (2N n H n =。每个顶点与N 个节点相邻。根据Anderson 和Jensen 的分类,超立方体互连结构是采用间接传输策略和分散控制寻找路径、传输路径专用的方法。

图1.14 IBM SP2的内部网络连接

第一代分布式内存DM-MIMD 系统是基于简单、便宜的微处理器,网络技术不十分完善,这些机器的峰值性能低于典型的向量处理器和共享内存超级计算机的性能。现在,分布式内存计算机的性能经常超过传统的超级计算机,这是因为分布式内存系统所采用的RISC

处理器的性能的快速提高和网络技术的大大改进,加上分布式并行软件平台的大大改进。此外,许多分布式并行系统现在装有允许快速并行磁盘输入/输出(即并行I/O系统)的高级硬件和软件。因此分布式内存处理系统在侧重于计算速度的领域如空气动力学中已经逐渐占有了十分重要的地位。

分布式并行系统近年来得以迅速推广的另一个重要的原因是目前科研机构现有的网络或工作站机群可以很容易地当作廉价的分布式内存并行计算机来使用。一些科研单位利用现有的硬件基础,可以很容易地构筑自己的“超级并行机”。在软件平台方面,PVM和MPI 两个自由软件由于它的良好的可移植和可扩展性使之在科研领域得以快速的推广。这些都为并行计算在科研和教学领域的推广和发展创造了十分有利的条件。本论文就是基于以上的考虑,结合目前的实际情况,采用了基于MPI平台的分布式并行编程环境。

还有一个十分重要的问题需要在介绍分布式并行系统时提到,就是分布式并行系统的各个节点的连接方式和通信效率直接影响到了并行机的峰值性能。当前各个节点之间主要通过Ethernet(或者全通过快速FDDI互连)连接在一起,连接的通信性能很低。一些并行机厂商提供了节点之间的内部互连高性能开关来达到高速通信(如Digital和SP2).

1.11当代并行计算机体系结构

本节首先研究从当今具体不同的并行计算机系统中,抽象出具有普通意义的并行计算机体系结构模型,包括并行计算机结构模型和并行计算机的访存模型;然后简要介绍一下并行计算机的存储层次结构及其一致性问题。

1.11.1并行计算机结构模型

已如上述,大型并行机系统结构一般可分为6类:

单指令多数据流机SIMD(Single-Instruction Multiple-Data);

并行向量处理机PVP(Parallel Vector Processor);

对称多处理机SMP(Symmetric Multiprocessor);

大规模并行处理机MPP(Massively Parallel Processor);

工作站机群COW(Cluster of Workstation)

分布式共享存储DSM(Distributed Shared Memory)多处理机。

SIMD 计算机多为专用,其余的5种均属于多指令多数据流MIMD(Multiple-Instruction Multiple-Data)计算机。5种MIMD并行机的结构模型示于图1.15。其中B(Bridge)是存储总线和I/O总线间的接口,DIR(Cache Directory)是高速缓存目录,IOB(I/O Bus)是I/O总线,LD(Local Disk)是本地磁盘,MB(Memory Bus)是存储器总线,NIC(Network Interface Circuitry)是网络接口电路,P/C(Microprocessor and Cache)是微处理器和高速缓存,SM(Shared Memory)是共享存储器。目前绝大多数近代并行机均用商品硬件构成,而PVP计算机的部件很多都是定制(Custom -Made)的。

(c )M P P

(a )P V P

(b )S M P

(d )D S M

(e )C O W

图1.15 5种并行机结构模型

并行向量处理机(PVP )

典型的并行向量处理机的结构示于图1.15(a)。Cray C-90、Cray T-90、NEC SX-4和我国的银河1号等都是PVP 。这样的系统中包含了少量的高性能专门设计定制的向量处理器VP ,每个至少具有1Gflops 的处理能力。系统中使用了专门设计的高带宽的交叉开关网络将VP 连向共享存储模块,存储器可以每秒兆字节的速度向处理器提供数据。这样的机器通常不使用高速缓存,而是使用大量的向量寄存器和指令缓冲器。 对称多处理机(SMP )

对称多处理机的结构示于图1.15(b )。IBM R50、SGI Power Challenge 、 DEC Alpha 服务器8400和我国曙光1号等都是这种类型的机器;

SMP 系统使用商品微处理器(具有片上或外置高速缓存),它们经由高速总线(或交叉开关)连向共享存储器;

这种机器主要应用于商务,例如数据库、在线事务处理系统和数据仓库等;

重要的是系统是对称的,每个处理器可等同的访问共享存储器、I/O 设备和操作系统服务;

正是对称,才能开拓较高的并行度;

也正是共享存储,也限制了系统中的处理器不能太多(一般少于64个); 同时总线和交叉开关互连一旦作成也难于扩展。 大规模并行处理机(MPP )

大规模并行处理机的结构示于图1.15(c)。Intel Paragon 、IBM SP2、Intel TFLOPS 和我国的曙光-1000等都是这种类型的机器;

MPP一般是指超大型(Very Large-Scale)计算机系统,它具有如下特性:

①处理节点采用商品微处理器;

②系统中有物理上的分布存储器;

③采用高通信带宽和低延迟的互连网络(专门设计和定制的);

④能扩放至成百上千个处理器;

⑤它是一种异步的MIMD机器,程序系由多个进程组成,每个都有其私有地址空间,进程间采用传递消息相互作用。

MPP的主要应用是科学计算、工程模拟和信号处理等以计算为主的领域。

分布共享存储多处理机(DSM)

分布式共享存储多处理机的结构示于图1.15(d)。Stanford DASH、Cray T3D 和SGI/Gray Origin2000 等属于此类结构。

高速缓存目录DIR用以支持分布高速缓存的一致性;

DSM和SMP的主要差别是,DSM在物理上有分布在各节点中的局存从而形成了一个共享的存储器;

对用户而言,系统硬件和软件提供了一个单地址的编程空间;

DSM相对于MPP的优越性是编程较容易。

工作站机群(COW)

工作站机群结构示于图1.15(e)。Berkeley NOW、Alpha Farm、Digital Trucluster等都是COW结构。在有些情况下,机群往往是低成本的变形的MPP,COW的重要界线和特征是:①COW的每个节点都是一个完整的工作站(不包括监视器,键盘,鼠标等),这样的节点有时叫作“无源工作站”,一个节点也可以是一台PC或SMP;

②各节点通过一种低成本的商品网络(如以太网、FDDI和ATM开关等)互连(有的商用机群也使用定做的网络);

③各节点内总是有本地磁盘,而MPP节点内却没有;

④节点内的网络接口是松耦合到I/O总线上的,而MPP内的网络接口是连到处理节点的存储总线上的,因而可谓是紧耦合式的;

⑤一个完整的操作系统驻留在每个节点中,而MPP中通常只是个微核,COW的操作系统是工作站UNIX,加上一个附加的软件层以支持单一系统映像、并行度、通信和负载平衡等。

现今,MPP和COW之间的界线越来越模糊。例如,IBM SP2 它虽视为MPP,但它却有一个机群结构。机群相对于MPP有性能/价格比高的优势,所以在发展可扩放并行计算机方面呼声很高。

表1.6汇总了上述5种结构的特性比较。

表1.6 5种结构特性一览表

1.11.2并行计算机体系合一结构

90年代以后上述各种并行机体系结构呈现渐趋一致的趋势。促使体系结构渐趋一致而最终合一的主要因素是:所有的体系结构要求快速、高质量的互连网络;都希望尽量避免或降低延迟;都希望能尽量隐藏掉通信代价;都必须支持不同的同步形式等。

由于硬件和软件的发展演变,使得共享存储与消息传递的界限越来越模糊。

①在通信操作上:首先,传统的消息传递操作(发/收)在绝大多数共享存储的机器上

均可通过共享的缓冲存储器支持之:发方将写数据送入缓冲区,而收方从共享存

储器中读取这些数据,可以使用标记或锁等来控制缓冲区的访问。其次,在消息

传递机器中,用户进程可以构成全局地址空间,访问这样的全局地址,可以软件

方式用显式消息处理实现之。逻辑读可用发送请求给包含目标和接收响应的进程

实现之。绝大多数消息传递库,允许一个进程接收任何别的进程的消息,所以每

个进程均可服务于别的进程数据请求。再者,共享虚拟地址空间可以建立在消息

传递机器的页面级上。一组进程有其共享地址区域,但只有属于它的本地页面的

进程才可访问。

②在机器组织上:SMP、MPP和COW等并行结构渐趋一致,DSM是SMP和MPP

的自然结合,MPP和COW的界线逐渐不清,它们最终的结构趋向一致,形成

当代并行机的公用结构(图1.16)。在这机样的系统结构中,大量的节点可通过

高速网络互连起来。节点通常遵循着一个Shell结构(Shell Architecture),其中

一个专门设计定制的电路(叫作Shell)将商品微处理器P和其余的节点,包括

板级高速缓存C、局存M、NIC和磁盘D连接起来。在一个节点内可有不止一

个处理器。这种Shell结构的优点是,当处理器芯片更新换代时系统的其他部分

无需改变。图1.15中示了三种不同的共享结构,其中将无共享结构图(a)中节

点内的磁盘(D)移出来就形成了共享磁盘的结构图(b),再把主存(M)移出

来就变成了共享存储结构图(c)。

③在互连网络方面:很多诸如快速Ethernet、ATM、光纤等先进网络的出现,可使

用它们将节点(或系统)连成机群结构,构成一个可扩放的SMP机器。

(a)无共享

(b)共享磁盘

(c)共享存储

图1.16可扩放并行机公用结构

1.12 并行计算机访存模型

下面从系统访问存储器的模式讨论多处理机和多计算机系统的访存模型,它和上节所讨论的结构模型,是实际并行计算机系统结构的两个方面。

1.1

2.1均匀存储访问模型(UMA)

UMA(Uniform Memory Access)模型是均匀存储访问模型的简称。图1.17示出了UMA 多处理机模型,其特点是:

①物理存储器被所有处理器均匀共享;

②所有处理器访问任何存储字取相同的时间(此即均匀存储访问名称的由来);

③每台处理器可带私有高速缓存;

④外围设备也可以一定形式共享。

这种系统由于高度共享资源而称为紧耦合系统(Tightly Coupled System)。当所有的处理器都能等同地访问所有I/O设备、能同样地运行执行程序(如操作系统内核和I/O服务程序等)时称为对称多处理机SMP(Symmetric Multiprocessor);如果只有一台或一组处理器(称为主处理器),它能执行操作系统并能操纵I/O,而其余的处理器无I/O能力(称为从处理器),只在主处理器的监控之下执行用户代码,这时称为非对称多处理机。一般而言,UMA 结构适于通用或分时应用。

共享存储器

处理器

图1.17 UMA多处理机模型

1.1

2.2非均匀存储访问模型(NUMA )

NUMA(Nonuniform Memory Access)模型是非均匀存储访问模型的简称。图1.18示出了NUMA 多处理机模型,其中(a )为共享本地存储器的NUMA ;(b )为层次式机群NUMA ,NUMA 的特点是:

① 被共享的存储器在物理上是分布在所有的处理器中的,其所有本地存储器的集

合就组成了全局地址空间;

② 处理器访问存储器的时间是不一样的;访问本地存储器LM 或群内共享存储器

CSM 较快,而访问外地的存储器或全局共享存储器GSM 较慢(此即非均匀存储访问名称的由来);

③ 每台处理器照例可带私有高速缓存,且外设也可以某种形式共享。

(a)共享本地存储模型

(b)层次式机群模型

图1.18 NUMA 多处理机模型

1.1

2.3全高速缓存访问模型(COMA)

COMA(Cache-Only Memory Access)模型是全高速缓存存储访问的简称。图1.19示出了COMA 多处理机模型,它是NUMA 的一种特例。其特点是:

① 各处理器节点中没有存储层次结构,全部高速缓存组成了全局地址空间; ② 利用分布的高速缓存目录D 进行远程高速缓存的访问; ③ COMA 中的高速缓存容量一般都大于2 级高速缓存容量;

④ 使用COMA 时,数据开始时可任意分配,因为在运行时它最终会被迁移到要用到

它们的地方。

这种结构的机器实例有瑞典计算机科学研究所的DDM 和Kendall Square Research 公司的KSR-1等。

图1.19 COMA多处理机模型

1.1

2.4高速缓存一致性非均匀存储访问模型(CC-NUMA)

CC-NUMA(Coherent-Cache Nonuniform Memory Access)模型是高速缓存一致性非均匀存储访问模型的简称。图1.20示出了CC-NUMA多处理机模型,它实际上是将一些SMP 机器作为一个单节点而彼此连接起来所形成的一个较大的系统。其特点是:

①绝大多数商用CC-NUMA多处理机系统都使用基于目录的高速缓存一致性协议;

②它在保留SMP结构易于编程的优点的同时,也改善了常规SMP的可扩放性问题;

③CC-NUMA实际上是一个分布共享存储的DSM多处理机系统;

④它最显著的优点是程序员无需明确地在节点上分配数据,系统的硬件和软件开始时

自动在各节点分配数据,在运行期间,高速缓存一致性硬件会自动地将数据迁移至

要用到它的地方。

总之,CC-NUMA所发明的一些技术在开拓数据局部性和增强系统的可扩性方面很有效。不少商业应用,大多数数据访问都可限制在本地节点内,网络上的主要通信不是传输数据,而是为高速缓存的无效性(Invalidation)所用。

图1.20 CC-NUMA结构模型(RC:远程高速缓存)

1.1

2.5 非远程存储访问模型(NORMA)

NORMA(No-Remote Memory Access)模型是非远程存储访问模型的简称。在一个分布存储的多处理机系统中,如果所有的存储器都是私有的,仅能由其自己的处理器所访问时就称为NORMA。图1.21示出了基于消息传递的多计算机一般模型,系统由多个计算节点通过消息传递互连网络连接而成,每个节点都是一台由处理器、本地存储器和/或I/O外设组成的自治计算机。NORMA的特点是:

①所有存储器是私有的;

②绝大数NUMA都不支持远程存储器的访问;

③在DSM中,NORMA就消失了。

计算机体系结构期末复习

计算机体系结构期末复习资料 1.并行性:是指在同一时刻或者是同一时间间隔内完成两种或两种以上性质相同或不同的工作。 2.CPI:每条指令执行时所花费的平均时钟周期。 3.体系结构:即计算机的属性,即概念性结构与功能特性。 4.Amdahl定理:加快某部件执行速度所获得的系统性能加速比,受限于该部件在系统中所占的重要性。 5.信息存储的整数边界:信息在主存中存放的起始地址必须是该信息(字节数)的整数倍。 6.指令系统的正交性:指在指令中各个不同含义的字段,在编码时应互不相关,相互独立。 7.流水线技术:是指将一个重复的时序过程,分解成为若干子过程,而每个过程都可有效在其专用功能段上与其他子过程同时执行。 8.定向技术:在某条指令产生一个结果之前,其他指令并不直接需要该计算结果,如果能将该计算结果从其他产生的地方直接送到其他指令需要它的地方,那么就可以避免暂停的技术就叫定向技术。 9.相关:衡量两个随机变量之间相关程度的指标。 10.向量流水处理机:是指处理机具有向量数据表示并通过向量指令对向量的各元素进行处理。、

11.定向:将计算结果从其产生的地方直接送到其他指令需要它的地方,或所有需要它的功能单元,避免暂停。 12.指令集的并行:当指令之间不存在相关时,它们在流水线中是可以重叠起来并行执行。 13.记分牌技术:流出和读操作数。在没有结构冲突时,尽可能早地执行没有数据冲突的指令,实现每个时钟周期执行一条指令。如果某条指令被暂停,而后面的指令与流水线中正在执行或被暂停的指令都不相关,是这些指令可以跨越它,继续流出和执行下去。 14.Tomasulo算法:寄存器换名是通过保留站和流出逻辑来共同完成,当指令流出时,如果其操作数还没有计算出来,则该指令中相应的寄存器换名将产生这个操作数的保留站的标识。因此,指令流出到保留站后,其操作数寄存器或者换成了数据本身,或换成了保留站的标识,和寄存器无关。后面指令对该寄存器的写入操作就不会产生WAR冲突。 15.替换算法:由于主存中的块比Cache中的块多,所以当要从主存中调一个块到Cache中时,会出现该块所映象到的一组(或一个)Cache块已全部被占用的情况。这时,需要被迫腾出其中的某一块,以接纳新调入的块。

计算机组成与设计答案

计算机组成与设计答案——节选 9. 设计算机A有60条指令,指令操作码为6位固定长度编码,从000000到111011。其后继产品B需要增加32条指令,并与A保持兼容, (1) 试为计算机B设计指令操作码。(2) 计算操作码平均长度。答::(1)6位操作码中保留了111100到111111四个码字,如果不再保留码字可增加3位扩展码,这样增加的32条指令的操作码为111100,000到111111,111中的一个。(2)如果每条指令的使用概率相等,则平均指令长度为: (6×60 + 9×32)/(60+32) = 7.04 注意:B计算机与A计算机保持兼容意味着B计算机原封不动地采纳A计算机的指令,可增加新的指令,但A计算机中已有的指令不能做任何改动。 10. 某计算机的指令系统字长定长为16位,采用扩展操作码,操作数地址需要4位。该指令系统已有三地址指令M条,二地址指令N 条,没有零地址指令,问系统最多还有多少条一地址指令? 答:三种指令的操作码长度分别为4位、8位和12位。设系统最多有L条一地址指令,则有 L=((24-M) ?24-N) ?24 13. 在一个单地址指令的计算机系统中有一个累加器,给定以下存储

器数值: 单元20中的内容是40 单元30中的内容是50 单元40中的内容是60 单元50中的内容是70 求以下指令分别将什么数值装入到累加器中?(1) load #20 (2) load 20 (3) load (20) (4) load #30 (5) load 30 (6) load (30) 答:(1) 20 (2) 40 (3) 60 (4) 30 (5) 50 (6) 70 15. 一条双字长的指令存储在地址为W的存储器中。指令的地址字段位于地址为W+1处,用Y表示。在指令执行中使用的操作数存储在地址为Z的位置。在一个变址寄存器中包含X的值。试叙述Z是怎样根据其他地址计算得到的,假定寻址方式为 (1) 直接寻址(2) 间接寻址(3) 相对寻址(4) 变址寻址 答:根据题意画出如下示意图: WW+1变址寄存器XZ存储器?OP(操作码)Y(地址码)?A (1) 在直接寻址方式下,指令中存放的就是操作数的地址。即操作数的地址Z在地址为W+1处,Z从指令中得到,所以有Z=Y。(2) 在存储器间接寻址方式下,操作数的地址在某一个存储单元中,其地址在指令中。Z根据Y访存后得到,所以有Z = (Y)。 (3) 在相对寻址方式下,操作数的地址为PC的值(取完指令后PC的值为W+2)加上Y得到。所以有Z=W+Y+2。 (4) 在变址寻址方式下,操作数的地址为变址寄存器的值加上Y得到。所以有Z=X+Y

自考计算机系统结构考前复习资料

第一章计算机系统结构的基本概念 从处理数据的角度看,并行级别有位串字串,位并字串,位片串字并,全并行。位串字串和位并字串基本上构成了SIMD。位片串字并的例子有:相联处理机STARAN,MPP。全并行的例子有:阵列处理机ILLIAC IV。 从加工信息的角度看,并行级别有存储器操作并行,处理器操作步骤并行,处理器操作并行,指令、任务、作业并行。 存储器操作并行是指可以在一个存储周期内并行读出多个CPU字的,采用单体多字、多体单字或多体多字的交叉访问主存系统,进而采用按内容访问方式,位片串字并或全并行方式,在一个主存周期内实现对存储器中大量字的高速并行操作。例子有并行存储器系统,以相联存储器为核心构成的相联处理机。 处理器操作步骤并行是指在并行性概念中引入时间因素,让多个处理过程在时间上错开,轮流重复地执行使用同一套设备的各个部分,加快硬件周转来赢得速度。例子有流水线处理机。 处理器操作并行是指一个指令部件同时控制多个处理单元,实现一条指令对多个数据的操作。擅长对向量、数组进行处理。例子有阵列处理机。 指令、任务、作业并行是指多个独立的处理机分别执行各自的指令、任务、作业。例子有多处理机,计算机网络,分布处理系统。 并行性的开发途径有时间重叠(Time Interleaving),资源重复(Resource Replication),资源共享(Resource Sharing)。 时间重叠是指在并行性概念中引入时间因素,让多个处理过程在时间上错开,轮流重复地执行使用同一套设备的各个部分,加快硬件周转来赢得速度。例子有流水线处理机。 资源重复是指一个指令部件同时控制多个处理单元,实现一条指令对多个数据的操作。例子有阵列处理机,相联处理机。 资源共享是指用软件方法让多个用户按一定时间顺序轮流使用同一套资源以提高资源的利用率,从而提高系统性能。例子有多处理机,计算机网络,分布处理系统。 SISD:一个指令部件控制一个操作部件,实现一条指令对一个数据的操作。例子有传统的单处理机 SIMD:一个指令部件同时控制多个处理单元,实现一条指令对多个数据的操作。例子有阵列处理机,相联处理机。 MIMD:多个独立的处理机分别执行各自的指令、任务、作业,实现指令、任务、作业并行的多机系统,是多个SISD的集合,也称多倍SISD系统(MSISD)。例子有多处理机,计算机网络,分布处理系统。 exercises: 1.有一台经解释实现的计算机,可以按功能划分成4级,每一级为了执行一条指令,需要下一级的N条指令来解释。如果执行第1级的一条指令要Kns时间,那么执行第2、第3和第4级的一条指令各需要用多少时间? 解答:执行第2、第3和第4级的一条指令各需要KNns、KN^2ns、KN^3ns的时间。 1.有一个计算机系统可按功能分成4级,每级的指令互不相同,每一级的指令都比其下一级的指令在效能上强M倍,即第i级的一条指令能完成第i-1级的M条指令的计算量。现若需第i级的N条指令解释第i+1级的一条指令,而有一段第1级的程序需要运行Ks,问在第2、3和4级上一段等效程序各需要运行多长时间? 答:第2级上等效程序需运行:(N/M)*Ks。第3级上等效程序需运行:(N/M)*(N/M)*Ks。第4级上等效程序需运行:(N/M)*(N/M)*(N/M)*Ks。 note: 由题意可知:第i级的一条指令能完成第i-1级的M条指令的计算量。而现在第i 级有N条指令解释第i+1级的一条指令,那么,我们就可以用N/M来表示N/M 表示第i+1级

ARM处理器体系架构详细说明

ARM处理器体系架构详细说明 ARM 体系结构是构建每个 ARM 处理器的基础。ARM 体系结构随着时间的推移不断发展,其中包含的体系结构功能可满足不断增长的新功能、高性能需求以及新兴市场的需要。 ARM 体系结构支持跨跃多个性能点的实现,并已在许多细分市场中成为主导的体系结构。ARM 体系结构支持非常广泛的性能点,因而可以利用最新的微体系结构技术获得极小的 ARM 处理器实现和极有效的高级设计实现。实现规模、性能和低功耗是 ARM 体系结构的关键特性。 已经开发了体系结构扩展,从而为 Java 加速 (Jazelle)、安全性 (TrustZone)、SIMD 和高级 SIMD (NEON) 技术提供支持。A RMv8-A 体系结构增加了密码扩展作为可选功能。 ARM 体系结构通常描述为精简指令集计算机 (RISC) 体系结构,因为它包含以下典型 RISC 体系结构特征: ?统一寄存器文件加载/存储体系结构,其中的数据处理操作只针对寄存器内容,并不直接针对内存内容。 ?简单寻址模式,所有加载/存储地址只通过寄存器内容和指令字段确定。 对基本 RISC 体系结构的增强使 ARM 处理器可以实现较高性能、较小代码大小、较低功耗和较小硅面积的良好平衡。 ARMv8 体系结构 ARMv8-A 将 64 位体系结构支持引入 ARM 体系结构中,其中包括: ?64 位通用寄存器、SP(堆栈指针)和 PC(程序计数器) ?64 位数据处理和扩展的虚拟寻址 ?两种主要执行状态: ?AArch64 - 64 位执行状态,包括该状态的异常模型、内存模型、程序员模型和指令集支持

?AArch32 - 32 位执行状态,包括该状态的异常模型、内存模型、程序员模型和指令集支持 这些执行状态支持三个主要指令集: ?A32(或 ARM):32 位固定长度指令集,通过不同体系结构变体增强部分 32 位体系结构执行环境现在称为 AArch 32 ?T32 (Thumb),以 16 位固定长度指令集的形式引入,随后在引入 Thumb-2 技术时增强为 16 位和 32 位混合长度指令集。部分 32 位体系结构执行环境现在称为 AArch32 ?A64:提供与 ARM 和 Thumb 指令集类似功能的 32 位固定长度指令集。随 ARMv8-A 一起引入,它是一种 AArch64 指令集。 ARM ISA 不断改进,以满足前沿应用程序开发人员日益增长的要求,同时保留了必要的向后兼容性,以保护软件开发投资。在ARMv8-A 中,对 A32 和 T32 进行了一些增补,以保持与 A64 指令集一致。 A32(ARM) ARM(通常称为 A32)是一种固定长度(32 位)的指令集。它是 ARMv4T、ARMv5TEJ 和 ARMv6 体系结构中使用的基础 32 位ISA。在这些体系结构中,该指令集用于需要高性能的应用领域,或用于处理硬件异常,如中断和处理器启动。 对于性能关键应用和旧代码,Cortex 体系结构的 Cortex-A 和 Cortex-R 配置文件也支持 ARM ISA。其多数功能都包括在与Thumb-2 技术一起引入的 Thumb 指令集中。Thumb (T32) 从改进的代码密度中获益。 ARM 指令的长度为 32 位,需要 4 字节边界对齐。 可以对大多数 ARM 指令进行“条件化”,使其仅在以前的指令设置了特定条件代码时执行。这意味着,如果应用程序状态寄存器中的 N、Z、C 和 V 标志满足指令中指定的条件,则指令仅对程序员的模型操作、内存和协处理器发挥其正常作用。如果这些标记不满足此条件,则指令会用作 NOP,即执行过程正常进入下一指令(包括将对异常进行任意相关检查),但不发挥任何其他作用。此条件化指令允许对 if 和 while 语句的一小部分进行编码,而无需使用跳转指令。 条件代码包括: T32(Thumb)

系统结构期末考试试题及答案

得分 评分人 填空题: (20分,每题2 分) 单选题:(10分,每题1分) A.任何虚页都可装入主存中任何实页的位置 B. 一个虚页只装进固定的主存实页位置 《计算机系统结构》期末考试试卷(A ) 得分 注:1、共100分,考试时间120分钟。 2、此试卷适用于计算机科学与技术本科专业。 1、."启动I/O"指令是主要的输入输出指令,是属于( A. 目态指令 B.管态指令 C.目态、管态都能用的指令 D.编译程序只能用的指令 2、 输入输出系统硬件的功能对 (B )是透明的 A.操作系统程序员 B.应用程序员 C.系统结构设计人员 D.机器语言程序设计员 3、 全相联地址映象是指(A ) C. 组之间固定,组内任何虚页可装入任何实页位置 D.组间可任意装入,组内是固定装入 4、( C ) 属于MIMD 系统结构 A.各处理单元同时受一个控制单元的管理 B.各处理单元同时受同个控制单元送来的指令 C.松耦合多处理机和多计算机系统 D. 阵列处理机 5、多处理机上两个程序段之间若有先写后读的数据相关,则( B ) A.可以并行执行 B.不可能并行 C.任何情况均可交换串行 D.必须并行执行 6、 计算机使用的语言是(B ) A.专属软件范畴,与计算机体系结构无关 B.分属于计算机系统各个层次 C.属于用以建立一个用户的应用环境 D. 属于符号化的机器指令 7、 指令执行结果出现异常引起的中断是( C ) A.输入/输出中断 B.机器校验中断 C.程序性中断 D.外部中断 &块冲突概率最高的 Cache 地址映象方式是(A ) A.直接 B .组相联 C .段相联 D .全相联 9、 组相联映象、LRU 替换的Cache 存储器,不影响 Cache 命中率的是(B ) A.增大块的大小 B .增大主存容量 C .增大组的大小 D .增加Cache 中的块数 10、 流水处理机对全局性相关的处理不 包括(C ) A.猜测法 B.提前形成条件码 C.加快短循环程序的执行 D.设置相关专用通路

计算机组成与设计 硬件 软件接口-第四版-课后题答案 第二章

2 Solutions Solution 2.1 2.1.1 a.add f, g, h add f, f, i add f, f, j b.addi f, h, 5 addi f, f, g 2.1.2 a.3 b.2 2.1.3 a.14 b.10 2.1.4 a. f = g + h b. f = g + h 2.1.5 a.5 b.5 Solution 2.2 2.2.1 a.add f, f, f add f, f, i b.addi f, j, 2 add f, f, g

S20 Chapter Solutions 2 2.2.2 a.2 b.2 2.2.3 a.6 b.5 2.2.4 a. f += h; b. f = 1–f; 2.2.5 a.4 b.0 Solution 2.3 2.3.1 a.add f, f, g add f, f, h add f, f, i add f, f, j addi f, f, 2 b.addi f, f, 5 sub f, g, f 2.3.2 a.5 b.2 2.3.3 a.17 b.–4

Chapter 2 Solutions S21 2.3.4 a. f = h – g; b. f = g – f – 1; 2.3.5 a.1 b.0 Solution 2.4 2.4.1 a.lw $s0, 16($s7) add $s0, $s0, $s1 add $s0, $s0, $s2 b.lw $t0, 16($s7) lw $s0, 0($t0) sub $s0, $s1, $s0 2.4.2 a.3 b.3 2.4.3 a.4 b.4 2.4.4 a. f += g + h + i + j; b. f = A[1];

计算机系统结构-第二章自考练习题答案

计算机系统结构- 第二章自考练习题答 案 第二章数据表示与指令系统 历年真题精选 1. 计算机中优先使用的操作码编码方法是(C )。 A. BCD码 B. ASCII码 C.扩展操作码 D.哈夫曼 编码2.浮点数尾数基值r m=16 ,除尾符之外的尾数机器位数为8 位时,可表示的规格化最大尾数值为(D )。 A. 1/2 B. 15/16 C. 1/256 D. 255/256

3. 自定义数据表示包括(标志符)数据表示和(数据描述符)两类。 4. 引入数据表示的两条基本原则是:一看系统的效率是否有提 高;二看数据表示的(通用)性和(利用)率是否高。 5. 简述设计RISC的一般原则。 6. 简述程序的动态再定位的思想。 7. 浮点数表示, 阶码用二进制表示,除阶符之外 的阶码位数p=3, 尾数基值用十进制表示,除尾符外的尾数二进制位数m=8计算非负阶、规格化、正尾数时, (1 )可表示的最小尾数值;(2)可表示 的最大值;3)可表示的尾数个数。

8. ( 1)要将浮点数尾数下溢处理成K —1 位结 果,则ROM表的单元数和字长各是多少?并简述ROM表各单元所填的内容与其地址之间的规则。 (2) 若3 位数,其最低位为下溢处理前的附加位,现将其下溢 处理成2 位结果,设计使下溢处理平均误差接近于零的 ROK表,以表明地址单元与其内容的关系。 同步强化练习 一. 单项选择题。 1. 程序员编写程序时使用的地址是 ( D ) 。 A ?主存地址 B . 有效地址 C. 辅存实 地址D . 逻辑地址

2. 在尾数下溢处理方法中,平均误差最大的是 )。 A .舍入法 B .截断法C.恒置“ 1 ”法 D . ROM查表法 3. 数据表示指的是(C )。 A.应用中要用到的数据元素之间的结构关系 B . 软件要处理的信息单元之间的结构关系 C. 机器硬件能识别和引用的数据类型 D ?高级语言中的数据类型说明语句 4. 标志符数据表示中的标志建立由(A )。 A . 编译程序完成 B . 操作系统完成 C . 高级语言编程时完成

计算机系统结构期末考试题目

第一章: 1.计算机系统结构的定义 答:由程序设计者看到的一个计算机系统的属性,即概念性结构和功能特性。 2.透明性概念 答:在计算机技术中,一种本来是存在的事物或属性,但从某种角度看似乎不存在,称为透明性现象。 3.兼容性向后兼容 兼容性:同一个软件可以不加修改地运行于系统结构相同的各档机器,可获得相同的结果,差别只在于不同的运行时间。 向后兼容:按某个时期投入市场的某种型号机器编制的程序,不加修改就能运行于在它之后投入市场的机器。 4.Amdahl定律 答:系统中某一部件由于采用某种更快的执行方式后整个系统性能的提高与这种执行方式的使用频率或占总执行时间的比例有关。 5.CPI 答:每条指令的平均时钟周期数。 6.MIPS 答:每秒百万条指令数!MIPS=时钟频率/(CPI*10^6) 7.MFLOPS 答:每秒百万次浮点操作次数。MFLOPS=程序中的浮点操作次数/(执行时间*10^6) 8.命中率的概念 答: 9.Flynn分类法是按指令流和数据流的多倍性特征进行计算机系统结构的划分 答:①单指令流单数据流SISD ②单指令流多数据流SIMD ③多指令流单数据流MISD(实际不存在)④多指令流多数据流MIMD 10.计算机系统设计的定量原理(四个) 答:①加快经常性事件的速度②Amdahl定律③CPU性能公式④访问的局部性原理11.CPI和加速比的计算 答:CPI=CPU时钟周期数/IC CPU时间=CPU时钟周期数/频率 CPU时间=CPU时钟周期*时钟周期长 加速比=(采用改进措施后的性能)/(没有采用改进措施前的性能) =(没有采用改进措施前执行某任务的时间)/(采用改进措施后执行某任务的时间) 12.软硬件实现的特点 硬件实现:速度快、成本高;灵活性差、占用内存少 软件实现:速度低、复制费用低;灵活性好、占用内存多 13.系统评价的标准 ①运算速度②存储器系统③其他性能④成本标准

计算机组成与设计第五版答案

解决方案4第4章解决方案S-34.1 4.1.1信号值如下:RegWrite MemReadALUMux MemWrite aloop RegMux Branch 0 0 1(Imm)1 ADD X 0 ALUMux是控制ALU输入处Mux 的控制信号,0(Reg)选择寄存器文件的输出,1(Imm)从指令字中选择立即数作为第二个输入。铝合金是控制Mux输入寄存器文件的控制信号,0(ALU)选择ALU的输出,1(Mem)选择存储器的输出。X值表示“不关心”(不管信号是0还是1)4.1.2除了未使用的寄存器4.1.3分支添加单元和写入端口:分支添加,寄存器写入端口没有输出:无(所有单元都生成输出)4.2 4.2.1第四条指令使用指令存储器、两个寄存器读取端口、添加Rd和Rs的ALU,寄存器中的数据存储器和写入端口。4.2.2无。此指令可以使用现有的块来实现。4.2.3无。此指令可以在不添加新的控制信号的情况下实现。它只需要改变控制逻辑。4.3 4.3.1时钟周期时间由关键路径决定。对于给定的延迟,它正好得到加载指令的数据值:I-Mem(读取指令)、Regs(长于控制时间)、Mux(选择ALU)输入)、ALU、数据存储器和Mux(从内存中选择要写入寄存器的值)。这个路径的延迟是400ps 吗?200秒?30秒?120秒?350马力?30秒?1130马力。1430马力(1130马力?300

ps,ALU在关键路径上)。4.3.2第4.3.2节加速度来自于时钟周期时间和程序所需时钟周期数的变化:程序要求的周期数减少了5%,但循环时间是1430而不是1130,所以我们的加速比是(1/0.95)*(1130/1430)?0.83,这意味着我们实际上在减速。S-4第4章解决方案4.3.3成本始终是所有组件(不仅仅是关键路径上的组件)的总成本,因此原处理器的成本是I-Mem、Regs、Control、ALU、D-Mem、2个Add单元和3个Mux单元,总成本是1000?200?500?100?2000年?2*30?3*10?3890我们将计算与基线相关的成本。相对于此基线的性能是我们先前计算的加速,相对于基线的成本/性能如下:新成本:3890?600?4490相对成本:4490/3890?1.15性价比:1.15/0.83?1.39条。我们必须付出更高的代价来换取更差的性能;成本/性能比未经修改的处理器差得多。4.2.2的单位是4.2倍,所以指令选择4.2倍的时间,而不是4.2倍的时间?4注意,通过另一个加法单元的路径较短,因为I-Mem的延迟比加法单元的延迟长。我们有:200秒?15磅?10磅?70秒?20秒?315 ps4.4.3条件分支和无条件分支具有相同的长延迟路径来计算分支地址。此外,它们还有一个长延迟路径,通过寄存器、Mux和ALU计算PCSrc

计算机体系结构自考

全国 2004年 7月高等教育自学考试 计算机系统结构试卷 课程代码:02325 一、单项选择题( 在每小题的四个备选答案中,选出一个正确答案,并将正确答案的 序号填在题干的括号内。每小题2分,共20 分) 1.软件和固件的功能在逻辑上是 ( )的。 A.固件优于软件 B.不等价 C.等价 D.软件优于固件 2.( )编写者看到的逻辑结构和功能能力就是计算机的外部特性。 A.操作系统 B.汇编语言程序 C.Windows NT D.微程序 3.RISC 计算机的指令系统集类型是 ( )。 A. 堆栈型 B.累加器型 C.寄存器—寄存器型 D.寄存器-存储器型 4.主存储器的 ( )要求属于外特性。 A. 容量大小 B.速度 C.页面组织 D.带宽 5.在采用延迟转移技术时,在以下几种调度方法中,效果最好的是哪一种方法 ?( ) A.将转移指令前的那条指令调度到延迟槽中 B.将转移目标处的那条指令调度到延迟槽中 C.将转移不发生时该执行的那条指令调度到延迟槽中 D.在延迟槽中填入 NOP 空操作指令 6.设 8个处理器编号分别为 0,1,2?,7用 Cube2互联函数时,第 5号处理机与第 ( 处理机相联。 A.1 B.3 C.4 D.6 7.大型计算机和小型计算机的主要区别在于 ( )。 A.大型机运行速度比小型机快得多 B.大型机能够控制大量的外设 C.大型机具有图型终端和图形处理能力 D.大型机的外存经管能力超过小型机 8.在以下总线规范中,哪一种总线具有与设备和主机无关的高级命令系统 ?( ) A.IDE B.AT C.SCSI D.PCI )号)。 1 / 5

2020.4《计算机体系结构》期末试卷A含答案

《计算机体系结构》期末考试A卷 (总分:100分,时间:100分钟) 姓名:周元华 专业:计算机科学与技术 学号: 18260070164016 学习中心:上海弘成 一、填空题(每空1分,共14分) 1.高速缓冲存储器的地址映象方式有三种,它们分别是:全向量方式,直接相联方式,组相连方式。 2.虚拟存储器的三种管理方式是段式管理,页式管理和 段页式管理。 3.从主存的角度来看,“Cache—主存”层次的目的是为了提高速度,而“主存—辅存”层次的目的是为了扩大容量 4.根据指令间的对同一寄存器读和写操作的先后次序关系,数据相关冲突可分为读与写(RAM)、写与读(WAR)和写与写(WAW)三种类型。 5.当代计算机体系结构的概念包括指令集结构、计算机组成和计算机实现三个方面的内容 二、名词解释(每题2分,共16分) 计算机体系结构: 计算机体系结构是指根据属性和功能不同而划分的计算机理论组成部分及计算机基本工作原理、理论的总称。其中计算机理论组成部分并不单与某一个实际硬件相挂钩,如存储部分就包括寄存器、内存、硬盘等。 兼容机: 兼容机,就是由不同公司厂家生产的具有相同系统结构的计算机。简单点说,就是非厂家原装,而改由个体装配而成的机器,其中的元件可以是同一厂家出品,但更多的是整合各家之长的 计算机。 写直达法: 写直达法一般指全写法。全写法(write-through):又称写直达法、写穿法,透写法,Cache使 用方式之一。 高速缓冲存储器: 高速缓冲存储器(Cache)其原始意义是指存取速度比一般随机存取记忆体(RAM)来得快 的一种RAM,一般而言它不像系统主记忆体那样使用DRAM技术,而使用昂贵但较快速的SRAM 技术,也有快取记忆体的名称。 高速缓冲存储器是存在于主存与CPU之间的一级存储器,由静态存储芯片(SRAM)组成, 容量比较小但速度比主存高得多,接近于CPU的速度。在计算机存储系统的层次结构中,是介 于中央处理器和主存储器之间的高速小容量存储器。它和主存储器一起构成一级的存储器。高速 缓冲存储器和主存储器之间信息的调度和传送是由硬件自动进行的。 高速缓冲存储器最重要的技术指标是它的命中率。 延迟转移技术: 在转移指令之后插入一条或几条有效的指令。当程序执行时,要等这些插入的指令执行完成 之后,才执行转移指令,因此,转移指令好像被延迟执行了,这种技术称为延迟转移技术。 线性流水线: 线性流水线就是由一整套工艺串联而成的生产线。 流水线又称为装配线,一种工业上的生产方式,指每一个生产单位只专注处理某一个片段的工 作,以提高工作效率及产量;按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、 倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。 输送线的传输方式有同步传输的/(强制式),也可以是非同步传输/(柔性式),根据配置的 选择,可以实现装配和输送的要求。输送线在企业的批量生产中不可或缺。 流水线的吞吐率: 流水线的吞吐率是单位时间内流水线处理的任务数。 并行性: 并行性是指计算机系统具有可以同时进行运算或操作的特性,在同一时间完成两种或两种以 上工作。它包括同时性与并发性两种含义。同时性指两个或两个以上事件在同一时刻发生。并发 性指两个或两个以上事件在同一时间间隔发生。 三、简答题(每题5分,共30分) 1.如有一个经解释实现的计算机,可以按功能划分成4级。每一 级为了执行一条指令需要下一级的N条指令解释。若执行第一 级的一条指令需K(ns)时间,那么执行第2、3、4级的一条指 令各需要用多少时间(ns)? 答:第1级:1条1级指令 K ns 第2级:1条2级指令N条1级指令 1*N*K ns = NK ns 第3级:1条3级指令N条2级指令 1*N*NK ns =N2K ns 第4级:1条4级指令N条3级指令 1*N*NNK ns =N3K ns 2.根据Amdahl定律,系统加速比由哪两个因素决定? 答:系统加速比依赖于两个因素: (1)可改进比例:可改进部分在原系统计算时间中所占的比例 (2)部件加速比:可改进部分改进以后的性能提高 3.简述组相联映象规则。 答:(1)主存与缓存分成相同大小的数据块。(2)主存和Cache 按同样大小划分成组。(3)主存容量 是缓存容量的整数倍,将主存空间按缓冲区的大小分成区,主存中每一区的组数与缓存的组数相同 4.引起Cache与主存内容不一致的原因是什么?为了保持Cache 的一致性,在单计算机系统中一般采取哪些措施? 答:不一致的原因:(1)由于CPU写Cache,没有立即写主存 (2)由于I/O处理机或I/O设备写主存 采取措施: (1)全写法,亦称写直达法(WT法-Write through) 方法:在对Cache进行写操作的同时,也对主存该内容进行写入 (2)写回法(WB法-Write back) 方法:在CPU执行写操作时,只写入Cache,不写入主存。 5.按照同一时间内各段之间的连接方式来分,流水线可分为哪两 类? 答:(1)静态流水线:在同一时间内,流水线的各段只能按同一种功能的连接方式工作。 (2)动态流水线:在同一时间内,当某些段正在实现某种运算时,另一些段却在实现另一种运算。 6.Flynn分类法是根据什么对计算机进行分类的?将计算机分 成哪几类? 答:Flynn分类法,根据计算机中指令和数据的并行状况把计算机分成: (1)单指令流单数据流(SISD.; (2)单指令流多数据流(SIMD.; (3)多指令流单数据流(MISD.; (4)多指令流多数据流(MIMD.。 四、问答与计算题(第1题10分,第2、3题每题15分共40分) 1.一个有快表和慢表的页式虚拟存储器,最多有64个用户,每 个用户最多要用1024个页面,每页4K字节,主存容量8M字节。 (1)写出多用户虚地址的格式,并标出各字段的长度。 (2)写出主存地址的格式,并标出各字段的长度。

计算机体系结构期末试卷及答案

课程测试试题( A 卷) ----------------------以下为教师填写-------------------- I、命题院(部):信息科学与工程学院 II、课程名称:计算机体系结构 III、测试学期:2014-2015学年度第2学期 IV、测试对象:信息学院计算机、网络专业 2012 级班 V、问卷页数(A4): 3 页 VI、答卷页数(A4): 4 页 VII、考试方式:闭卷(开卷、闭卷或课程小论文,请填写清楚) VIII、问卷内容: 一、填空题(共30分,20空,每空分) 1、现代计算机系统是由()和()组成的十分复杂的系统。 2、计算机系统应能支持软件可移植,实现可移植性的常用方法有3种,即(),(), 统一高级语言。 3、可以将当前大多数通用寄存器型指令集结构进一步细分为3种类型,即()、() 和存储器-存储器型指令集结构。 4、MIPS指令DADDIU R14,R5,#6属于()类型的指令格式;MIPS指令 SD R4,300(R5)属于()类型的指令格式。 5、描述流水线的工作,常采用时空图的方法。在时空图中,横坐标表示(),纵坐 标代表()。 6、在MIPS指令实现的简单数据通路中,在WB周期中,有两大类指令执行操作:() 和()指令。 7、存储器的层次结构中,“Cache-主存”层次是为了弥补主存()的不足,“主 存-辅存”层次是为了弥补主存()的不足。 8、Cache实现的映像规则有全相联映像、()和()三种。 9、反映存储外设可靠性能的参数有可靠性、()和()。 10、根据系统中处理器个数的多少,可把现有的MIMD计算机分为两类,每一类代表 了一种存储器的结构和互连策略。第一类机器称为()结构,第二类机器具有()。 二、判断题(每小题1分,共10分) 1、从计算机语言的角度,系统结构把计算机系统按功能划分成多级层次结构,其中, 第2级是操作系统虚拟机,第3级是汇编语言虚拟机。() 2、计算机系统中提高并行性的3种途径中,资源重复是在并行性概念中引入时间因 素,加快硬件周转而赢得时间。() 3、指令集结构中采用多种寻址方式可能会增加实现的复杂度和使用这些寻址方式的 指令的CPI。() 4、指令条数多,通常超过200条,是设计RISC的原则之一。() 5、根据流水线中各功能段之间是否有反馈回路,可把流水线分为线性流水线和非线 性流水线。() 6、在多级存储体系中,“cache——主存”层次的存储管理实现主要由软件件实现。

计算机组成与设计第五版答案

计算机组成与设计(2010年机械工业出版社出版的图书): 《计算机组成与设计》是2010年机械工业出版社出版的图书,作者是帕特森(DavidA.Patterson)。该书讲述的是采用了一个MIPS 处理器来展示计算机硬件技术、流水线、存储器的层次结构以及I/O 等基本功能。此外,该书还包括一些关于x86架构的介绍。 内容简介: 这本最畅销的计算机组成书籍经过全面更新,关注现今发生在计算机体系结构领域的革命性变革:从单处理器发展到多核微处理器。此外,出版这本书的ARM版是为了强调嵌入式系统对于全亚洲计算行业的重要性,并采用ARM处理器来讨论实际计算机的指令集和算术运算。因为ARM是用于嵌入式设备的最流行的指令集架构,而全世界每年约销售40亿个嵌入式设备。 采用ARMv6(ARM 11系列)为主要架构来展示指令系统和计算机算术运算的基本功能。 覆盖从串行计算到并行计算的革命性变革,新增了关于并行化的一章,并且每章中还有一些强调并行硬件和软件主题的小节。 新增一个由NVIDIA的首席科学家和架构主管撰写的附录,介绍了现代GPU的出现和重要性,首次详细描述了这个针对可视计算进行了优化的高度并行化、多线程、多核的处理器。 描述一种度量多核性能的独特方法——“Roofline model”,自带benchmark测试和分析AMD Opteron X4、Intel Xeo 5000、Sun Ultra SPARC T2和IBM Cell的性能。

涵盖了一些关于闪存和虚拟机的新内容。提供了大量富有启发性的练习题,内容达200多页。 将AMD Opteron X4和Intel Nehalem作为贯穿《计算机组成与设计:硬件/软件接口(英文版·第4版·ARM版)》的实例。 用SPEC CPU2006组件更新了所有处理器性能实例。 作者简介: David A.Patterson,加州大学伯克利分校计算机科学系教授。美国国家工程研究院院士。IEEE和ACM会士。曾因成功的启发式教育方法被IEEE授予James H.Mulligan,Jr教育奖章。他因为对RISC 技术的贡献而荣获1 995年IEEE技术成就奖,而在RAID技术方面的成就为他赢得了1999年IEEE Reynold Johnson信息存储奖。2000年他~13John L.Hennessy分享了John von Neumann奖。 John L.Hennessy,斯坦福大学校长,IEEE和ACM会士。美国国家工程研究院院士及美国科学艺术研究院院士。Hennessy教授因为在RISC技术方面做出了突出贡献而荣获2001年的Eckert-Mauchly奖章.他也是2001年Seymour Cray计算机工程奖得主。并且和David A.Patterson分享了2000年John von Neumann奖。

自考计算机系统结构试题-小炒

一、选择题 1、对汇编语言程序员,下列(A )不是透明的。 A: 中断字寄存器 B: 乘法器 C: 移位器 D: 指令缓冲器 2、假设对A机器指令系统的每条指令的解释执行可直接由B机 器的一段微程序解释执行,则A称为(D )。 A: 仿真机 B: 宿主机 C: 虚拟机 D: 目标机 3、 1. 查看下面三条指令:V3←A;V2←V0+V1;V4←V2*V3;假 设向量长度小于64,且前后其他的指令均没有相关性,数据进入和 流出每个功能部件,包括访问存储器都需要一拍的时间,假设向 量的长度为N。三条指令全部采用串行的方法,那么执行的时间是:A: 3N+20 B: 3N+21 C: 3N+22 D: 3N+23 4、某向量处理机有16个向量寄存器,其中V0-V5种分别存放有 向量A,B,C,D,E,F,向量的长度是8,向量各元素均为浮点数;处理 部件采用两个单功能流水线,加法功能部件时间为2拍,乘法功 能部件时间为3拍。采用类似CRAY-1的链接技术,先计算(A+B)*C, 在流水线不停的情况下,接着计算(D+E)*F。求此链接流水线的通 过时间是多少拍?(设寄存器出入各需1拍) A: 8 B: 9 C: 17 D: 18 5、设有一个4个处理器的MIMD系统,假设在系统中访存取指和 取数的时间可以忽略不计;加法与乘法分别需要2拍和4拍;在 MIMD系统中处理器(机)之间每进行一次数据传送的时间为1拍; 在MIMD系统中,每个PE都可以和其它PE有直接的的通路。 求利用此系统计算表达式所需 的节拍数。 A: 23 B: 12 C: 11 D: 10 6、以下哪些是周期窃取方式的特点? A : 硬件结构简单 B : 硬件结构复杂 C : 数据输入或输出过程中占用了CPU时间 D : 数据输入或输出过程中不占用CPU时间 7、从下列有关Cache的描述中,选出应填入空格中的正确答案: (1)今有甲、乙两台计算机,甲计算机的Cache存取时间为50ns, 主存储器为2us;乙计算机的Cache存储时间为100ns,主存储器 为1.2us。设Cache的命中率均为95%,则甲计算机的平均存取 时间为__A_ns;乙计算机的平均存取时间为__B_ns。 (2)在Cache中,经常采用直接映象或组相联映象两种方式,在 Cache容量相等的情况下,前者比后者的命中率__C__。 选项 A : 147.5 153.5 155 180 选项 B : 147.5 153.5 155 180 选项 C : 高低相等 8、有研究人员指出,如果在采用通用寄存器指令集结构的计算 机里加入寄存器—存储器寻址方式可能提高计算机效率,做法就 是用指令ADD R2,0(Rb)代替指令序列LOAD R1,0(Rb) ADD R2,R2,R1假定使用新的指令能使时钟周期增加10%,并且假定只 对时钟产生影响,而不影响CPI那么采用新指令,要达到与原来 同样的性能需要去掉的LOAD操作所占的百分比?(提示:去掉的 是与ADD指令连用的LOAD指令,假定未采用新指令前LOAD指令 占总指令的22.8%)A: 39% B: 36% C: 40% D: 39.8% 9、下述的几个需要解决的问题中,那个是向量处理机所最需要 关心的? A: 计算机指令的优化技术 B: 设计满足运算器带宽要求的存储器 C: 如何提高存储器的利用率,增加存储器系统的容量 D: 纵横处理方式的划分问题 10、一台单处理机可以以标量方式运行,也可以以向量方式运行。 在向量方式情况下,计算可比标量方式快18倍。设某基准程序在 此计算机上运行的时间是T。另外,已知T的25%用于向量方式, 其余机器时间则以标量方式运行。那么在上述条件下与完全不用 向量方式的条件下相比的加速比是: A: 3 B: 3.43 C: 3.33 D: 以上均不正确 11、给定1个采用完全混洗互连网络,并有256个PE的SIMD机 器,加入执行混洗互连函数10次,则原来在PE123中的数据将被 送往何处? A: PE237 B: PE222 C: PE111 D: PE175 12、 设计一种采用加、乘和数据寻径操作的算法,计算表达式 。假设加法和乘法分别需要2个和4个 单位时间,从存储器取指令、取数据、译码的时间忽略不计,所 有的指令和数据已经装入有关的PE。现有一台串行计算机,有一 个加法器,一个乘法器,问最短多少单位时间计算出s? A: 192ns B: 130ns C: 128ns D: 以上结果都不对 13、下列功能,那些一般由硬件实现? A : 第一次关CPU中断 B : 返回中断点 C : 第一次开CPU中断 D : 保存中断点 14、星形网络的网络直径和链路数分别为()和()。 选项 1 : N-1 N/2 2 N(N-1)/2 选项 2 : N-1 N/2 2 N(N-1)/2 16、在计算机系统结构来看,机器语言程序员看到的机器属性是 (D)。 A)计算机软件所要完成的功能B)计算机硬件的全部组 成 C)编程要用到的硬件知识D)计算机各部件的硬件 实现 17、在提高CPU性能的问题上,从系统结构角度,可以(D)。 A)提高时钟频率B) 减少程序指令条数 C)减少每条指令的时钟周期数D)减少程序 指令条数和减少每条指令的时钟周期数 18、计算机系统结构不包括(C )。 A)主存速度B)机器工作状态C)信息保护 D)数据表示 19、推出系列机的新机器,不能更改的是(A)。 A)原有指令的寻址方式和操作码B) 系统的总线的组成 C)数据通路宽度 D)存储芯片的集成度 20、在系统结构设计中,提高软件功能实现的比例会(C)。 A)提高解题速度 B)减少需要的存储容量 C)提高系统的灵活性 D)提高系统的性能价格比 21、重叠寄存器技术主要用于解决在RISC系统中因( C )而导 致的问题。 A)JMP指令影响流水线 B)CALL指令的现场保护 C)只有LOAD和STORE指令带来的访问存储器不便D) 存储器访问速度 22、不属于堆栈型替换算法的是(C )。 A)近期最少使用法B)近期最久未用法 C)先 进先出法D)页面失效频率法 23、与全相联映象相比,组相联映象的优点是(B)。 A)目录表小B)块冲突概率低C)命中率高 D)主存利用率高 24、最能确保提高虚拟存储器访主存的命中率的改进途径是(D)。 A)增大辅存容量 B)采用FIFO替换算法并增大页面 C)改用LRU替换算法并增大页面D)改用LRU 替换算法并增大页面数 25、"一次重叠"中消除"指令相关"最好的方法是( A )。 A)不准修改指令B)设相关专用通路C)推后分析下条指令 D)推后执行下条指令 26、在流水机器中,全局性相关是指(D)。 A)先写后读相关B)先读后写相关C)指令相关 D)由转移指令引起的相关 27、下列说法不正确的是(D)。 A)线性流水线是单功能流水线B) 动态流水线是多功能流水线 C)静态流水线是多功能流水线D) 动态流水线只能是单功能流水线 28、16个处理器编号为0、1、…、15,采用单级Cube3互连网络 互连,与13号处理器相连的处理器号是()。 A)2 B)3 C)4 D)5 29、经多级网络串联来实现全排列网络,只能用(C)。 A)多级立方体网络B)多级PM2I网络C)多级混洗 交换网络D)上述任何网络 30、经3级立方体网络对0-7八个端子(0 1 2 3 4 5 6 7)排列, 进行模8移4变换,得到的这八个端子新的排列应当是()。 A)(2 3 4 5 6 7 0 1)B) (4 5 6 7 0 1 2 3) C)(1 2 3 0 5 6 7 4)D) (1 0 3 2 5 4 7 6) 31、虫蚀寻径以流水方式在各寻径器是顺序传送的是(C)。 A)消息B)包C)片 D)字节 32、能实现指令、程序、任务级并行的计算机系统属于(D )。