完整的寄存器介绍

A VR单片机寄存器介绍

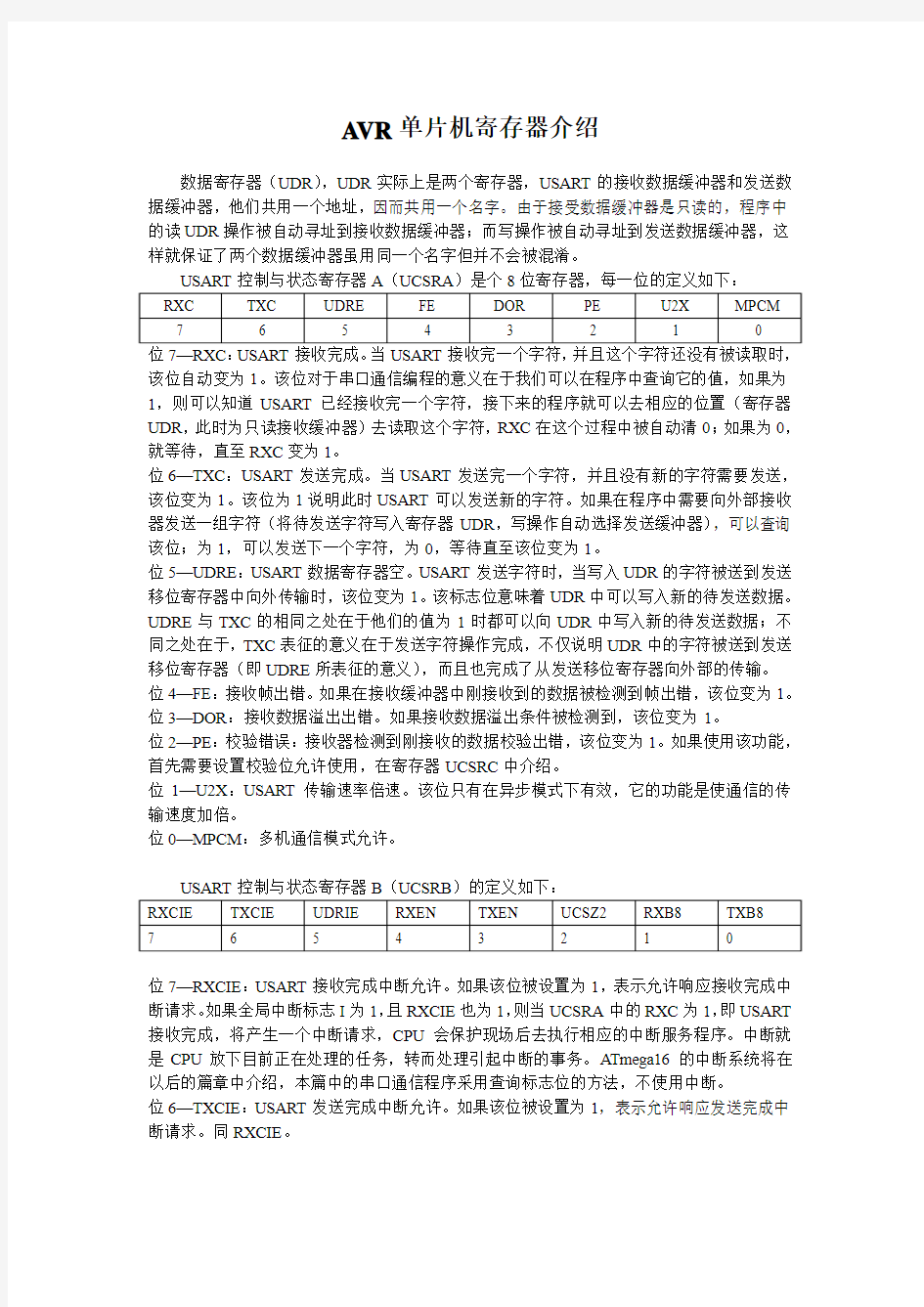

数据寄存器(UDR),UDR实际上是两个寄存器,USART的接收数据缓冲器和发送数据缓冲器,他们共用一个地址,因而共用一个名字。由于接受数据缓冲器是只读的,程序中的读UDR操作被自动寻址到接收数据缓冲器;而写操作被自动寻址到发送数据缓冲器,这样就保证了两个数据缓冲器虽用同一个名字但并不会被混淆。

该位自动变为1。该位对于串口通信编程的意义在于我们可以在程序中查询它的值,如果为1,则可以知道USART已经接收完一个字符,接下来的程序就可以去相应的位置(寄存器UDR,此时为只读接收缓冲器)去读取这个字符,RXC在这个过程中被自动清0;如果为0,就等待,直至RXC变为1。

位6—TXC:USART发送完成。当USART发送完一个字符,并且没有新的字符需要发送,该位变为1。该位为1说明此时USART可以发送新的字符。如果在程序中需要向外部接收器发送一组字符(将待发送字符写入寄存器UDR,写操作自动选择发送缓冲器),可以查询该位;为1,可以发送下一个字符,为0,等待直至该位变为1。

位5—UDRE:USART数据寄存器空。USART发送字符时,当写入UDR的字符被送到发送移位寄存器中向外传输时,该位变为1。该标志位意味着UDR中可以写入新的待发送数据。UDRE与TXC的相同之处在于他们的值为1时都可以向UDR中写入新的待发送数据;不同之处在于,TXC表征的意义在于发送字符操作完成,不仅说明UDR中的字符被送到发送移位寄存器(即UDRE所表征的意义),而且也完成了从发送移位寄存器向外部的传输。

位4—FE:接收帧出错。如果在接收缓冲器中刚接收到的数据被检测到帧出错,该位变为1。位3—DOR:接收数据溢出出错。如果接收数据溢出条件被检测到,该位变为1。

位2—PE:校验错误:接收器检测到刚接收的数据校验出错,该位变为1。如果使用该功能,首先需要设置校验位允许使用,在寄存器UCSRC中介绍。

位1—U2X:USART传输速率倍速。该位只有在异步模式下有效,它的功能是使通信的传输速度加倍。

位0—MPCM:多机通信模式允许。

位7—RXCIE:USART接收完成中断允许。如果该位被设置为1,表示允许响应接收完成中断请求。如果全局中断标志I为1,且RXCIE也为1,则当UCSRA中的RXC为1,即USART 接收完成,将产生一个中断请求,CPU会保护现场后去执行相应的中断服务程序。中断就是CPU放下目前正在处理的任务,转而处理引起中断的事务。ATmega16的中断系统将在以后的篇章中介绍,本篇中的串口通信程序采用查询标志位的方法,不使用中断。

位6—TXCIE:USART发送完成中断允许。如果该位被设置为1,表示允许响应发送完成中断请求。同RXCIE。

位5—UDRIE :USART 数据寄存器空中断允许。当该位被设置为1 时,表示允许响应发送数据寄存器UDR 空中断请求。同RXCIE 。

位4—RXEN :USART 接收数据允许。当该位被设置为1时,允许USART 接收数据。也就是说如果你准备用串口接收数据,那么首先需要将此位设置为1。此时管脚PD0(RXD )由通用I/O 口转变为第二功能RXD 。

位3—TXEN :USART 发送数据允许。当该位被设置为1时,允许USART 发送数据。 位2—UCSZ2:USART 数据位设定。该位协同UCSRC 寄存器中的UCSZ1,UCSZ0位设定

位1—RXB8:接收字符的第8位。当设定的通信字符位长为9时,该位用来表示接收数据的最高位,即第8位。

位0—TXB8:发送字符的第8位。同RXB8。

位7

—URSEL :寄存器选择。该位用于选择要操作的寄存器是UCSRC 或者是UBRRH 。读取UCSRC 时,该位读出值为1;写UCSRC 寄存器时,必须将该位写入1才能够正常写入UCSRC 寄存器。

位6—UMSEL :工作状态选择。该位为写入0时为异步模式;写入1为同步模式。 位5,位4—校验方式选择。选择串行数据通信采用何种校验

方式。如表格所示。

位3—USBS :停止位选择。为0时,数据帧中包含1位停止位;

为1时,数据帧中包含2位停止位。

位0—UCPOL :时钟极性选择。该位只在同步模式下使用。在

异步通信模式中应将此位写0。

波特率寄存器(UBRRH ,UBRRL ):UBRRL 与UBRRH 的低4位构成一个12位寄存器,用来设置串行通信的速率。需要注意一点的是在写UBRRH 寄存器时,最高位(第7位)必须写入0。来看一下波特率如何计算。

116xBAUD

fosc

BARR -=

其中,BARR 即所需要求得的UBRR 寄存器的值;fosc 为晶体频率;BAUD 即通信波特率。

比如准备以9600的波特率进行通信,晶体为14.7456MHZ,可得到BARR=95。当然,波特率也可以通过查表来获得。

单片机各寄存器汇总

符号 地址功能介绍 B F0H B寄存器 ACC E0H 累加器 PSW D0H 程序状态字 IP B8H 中断优先级控制寄存器 P3 B0H P3口锁存器 IE A8H 中断允许控制寄存器 P2 A0H P2口锁存器 SBUF 99H 串行口锁存器 SCON 98H 串行口控制寄存器 P1 90H P1口锁存器 TH1 8DH 定时器/计数器1(高8位)TH0 8CH 定时器/计数器1(低8位)TL1 8BH 定时器/计数器0(高8位)TL0 8AH 定时器/计数器0(低8位) TMOD 89H 定时器/计数器方式控制寄存器 TCON 88H 定时器/计数器控制寄存器 DPTR 82H 83H 83H数据地址指针(高8位) PC SP 81H 堆栈指针 P0 80H P0口锁存器 PCON 87H 电源控制寄存器 、PSW-----程序状态字。 D7D6D5D4D3D2D1D0 CY AC F0 RS1 RS0 OV P 下面我们逐一介绍各位的用途 CY:进位标志。 AC:辅助进、借位(高半字节与低半字节间的进、借位)。 F0:用户标志位,由用户(编程人员)决定什么时候用,什么时候不用。 RS1、RS0:工作寄存器组选择位。这个我们已知了。 0V:溢出标志位。运算结果按补码运算理解。有溢出,OV=1;无溢出,OV=0。什么是溢出我们后面的章节会讲到。

P :奇偶校验位:它用来表示ALU 运算结果中二进制数位“1”的个数的奇偶性。若为奇数,则P=1,否则为0。 运算结果有奇数个1,P =1;运算结果有偶数个1,P =0。 例:某运算结果是78H (01111000),显然1的个数为偶数,所以P=0。 定时/计数器寄存器 1.工作方式寄存器TMOD(P134) TMOD 为T0.T1的工作方式寄存器,其各位的格式如下:TMOD D7 D6 D 5 D4 D3 D2 D1 D0 GATE C/-T M1 M0 GATE C/-T M1 M0 定时器1 定时器0 位7 GATE ——T1的门控位。 当GATE=0时,只要控制TR1置1,即可启动定时器T1开始工作; 当GATE=1时,除需要将TR1置1外,还要使INT1引脚为高电平,才能启动相应的定时器开始工作。 位6 C/—T ——T1的功能选择位。 当C/—T=0时,T1为定时器方式; 当C/—T=0时,T1为计数器方式; 位5和位4 M1和M0——T1的方式选择位。 由这两位的组合可以定义T1的3种工作方式 定时器T1工作方式选择表 如右表: 位3 GATE ——T0的门控位。 当GATE=0时,只要控制TR0置1,即可启动定时器T0开始工作; 当GATE=1时,除需要将TR0置1外,还要使INT0引脚为高电平,才能启动相应的定时器开始工作。 位2 C/T ——T1的功能选择位。 当C/—T=0时,T0为定时器方式; 当C/—T=0时,T0为计数器方式; 位1和位0 M1和M0—T0的方式选择位。 由这两位的组合可以定义T1的3种工作方式 定时器T0工作方式选择表 TMOD 不能进行位寻址,只能用字节传送指令设置定时器工作方式,低半节定义定时器0,高半字节定义定时器1。复位时,TMOD 所有位均为0,定时器处于停止工作状态。 定时/计数器控制寄存器中断请求标志寄存器TCON(P183) TCON 的作用是控制定时器的启/停,标志定时器的溢出和中断情况。定时器控制寄存器TCON 各位格式如下:TCON(88H) 8FH 8EH 8DH 8CH 8BH 8AH 89H 88H TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 当有中断源发出请求时,有硬件将相应的中断标志位置 1.在中断请求被响应前,相应中断标志位被锁存在特殊功能寄存器TCON 或SCON 中。 TCON 为定时器T0和T1的控制寄存器,同时也锁住T0和T1的溢出中断标志及外部中断——INT0和— M1 M0 工作方式 功能描述 0 0 方式0 13位计数器 0 1 方式1 16位计数器 1 0 方式 2 自动再装入8位计数器 1 1 方式3 定时器1:停止计数 M1 M0 工作方式 功能描述 0 0 方式0 13位计数器 0 1 方式1 16位计数器 1 0 方式 2 自动再装入8位计数器 1 1 方式3 定时器0:分成2个8位计数器

寄存器(register)

寄存器 Scope of register: 寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器是中央处理器内的组成部份。寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和位址。在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。 1、寄存器- 特点及原理 寄存器又分为内部寄存器与外部寄存器,所谓内部寄存器,其实也是一些小的存储单元,也能存储数据。但同存储器相比,寄存器又有自己独有的特点: ①寄存器位于CPU内部,数量很少,仅十四个; ②寄存器所能存储的数据不一定是8bit,有一些寄存器可以存储16bit数据,对于386/486处理器中的一些寄存器则能存储32bit数据; ③每个内部寄存器都有一个名字,而没有类似存储器的地址编号。 寄存器的功能十分重要,CPU对存储器中的数据进行处理时,往往先把数据取到内部寄存器中,而后再作处理。外部寄存器是计算机中其它一些部件上用于暂存数据的寄存器,它与CPU之间通过“端口”交换数据,外部寄存器具有寄存器和内存储器双重特点。有些时候我们常把外部寄存器就称为“端口”,这种说法不太严格,但经常这样说。 外部寄存器虽然也用于存放数据,但是它保存的数据具有特殊的用途。某些寄存器中各个位的0、1状态反映了外部设备的工作状态或方式;还有一些寄存器中的各个位可对外部设备进行控制;也有一些端口作为CPU同外部设备交换数据的通路。所以说,端口是CPU和外设间的联系桥梁。CPU对端口(Ports)的访问也是依据端口的“编号”(地址),这一点又和访问存储器一样。不过考虑到机器所联接的外设数量并不多,所以在设计机器的时候仅安排了1024个端口

移位寄存器及其应用(精)

移位寄存器及其应用 一、实验目的 1、掌握中规模4位双向移位寄存器逻辑功能及使用方法。 2、熟悉移位寄存器的应用—实现数据的串行、并行转换和构成环形计数器。 二、原理说明 1、移位寄存器是一个具有移位功能的寄存器,是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。按代码的移位方向可分为左移、右移和可逆移位寄存器,只需要改变左、右移的控制信号便可实现双向移位要求。根据移位寄存器存取信息的方式不同又可分为:串入串出、串入并出、并入串出、并入并出四种形式。 本实验选用的4位双向通用移位寄存器,型号为CC40194或74LS194,两者功能相同,可互换使用,其逻辑符号及引脚排列如图8-3-3-1所示。 其中 D0、D1、D2、D3为并行输入端;Q0、Q1、Q2、Q3为并行输出端;S R为右移串行输入 C为直接无条件清零端; 端,S L为左移串行输入端;S1、S0为操作模式控制端;R CP为时钟脉冲输入端。 CC40194有5种不同操作模式:即并行送数寄存,右移(方向由Q0→Q3),左移(方向由Q3→Q0),保持及清零。 S1、S0和R C端的控制作用如表8-3-3-1。 图8-3-3-1 CC40194的逻辑符号及引脚功能 表8-3-3-1 CC40194功能表

2、移位寄存器应用很广,可构成移位寄存器型计数器;顺序脉冲发生器;串行累加器;可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和数据的串、并行转换。 (1)环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位, 如图8-3-3-2所示,把输出端 Q3和右移串行输入端S R 相连接,设初始状态Q0Q1Q2Q3=1000,则在时钟脉冲作用下Q0Q1Q2Q3将依次变为0100→0010→0001→1000→……,如表10-2所示,可见它是一个具有四个有效状态的计数器,这种类型的计数器通常称为环形计数器。图8-3-3-2 电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。其状态表如表8-3-3-2所示。 表8-3-3-2 环形计数器状态表 图 8-3-3-2 环形计数器 如果将输出Q O与左移串行输入端S L相连接,即可达左移循环移位。 (2)实现数据串、并行转换 ①串行/并行转换器 串行/并行转换是指串行输入的数码,经转换电路之后变换成并行输出。 图8-3-3-3是用二片CC40194(74LS194)四位双向移位寄存器组成的七位串/并行数据转换电路。

寄存器简单理解

GPIOB_BASE是一个地址,这个地址是GPIOB一系列寄存器的首地址,后面地址依次是GPIOB 的寄存器,将这个地址转换为结构体形式,并将后面寄存器按顺序定义在结构体里面,这样访问寄存器就可以通过引用结构体的形式了而不必书写寄存器的地址来访问寄存器。 寄存器用途: 1.可将寄存器内的数据执行算术及逻辑运算; 2.存于寄存器内的地址可用来指向内存的某个位置,即寻址; 3.可以用来读写数据到电脑的周边设备。 AX 累加器,得名原因是最初常使用ADD AX,n这样的指令 CX 计数器,得名原因是最常使用CX的值作为重复操作的次数 BX 常用作地址寄存器,如MOV AX,[BX],把BX所指地址中的数取到AX中去 DX 通用寄存器 所讲的寄存器都是以x86为基础的,那么这种CPU内,寄存器可分为以下几种: 1.EAX、EBX、ECX、EDX等通用寄存器——从通用上来讲,它所存储的东西,只要它的容积所容许的话,什么都是可以存储的; 2.CS、SS、ES等段寄存器——它所存储的只能是地址,它的作用是从寻址上可以体现出来; 3.EIP,也称为指令指针 4.EFLAGS寄存器,俗称为标志寄存器——所存储的是与CPU的每一个执行的指令有关。是关系到CPU每一个指令的执行相关内容与特殊的关联,即CPU所执行的指令是否违规,它的指令是否有进位,它的指令是否有溢出,都是在标志寄存器中能表现与表达出来; 5.浮点单元,这里面之所以只浮点单元,是因为在它里面还有一些小的寄存分类,主要是数学上的浮点上的计算 6.MMX指令使用的8个64位寄存器 7.单指令、多数据操作(SIMD,single-instruction,multiple-data)使用的8个128位XMM寄存器

移位寄存器 第三章答案

第三章习题参考答案 1.画出以1)(2 4 6 +++=x x x x f 为联接多项式的线性移位寄存器逻辑框图,及其对应的状态图。 解:由1)(2 46+++=x x x x f ,得反馈函数为531621),,,(x x x x x x f ++=Λ,故 (1)逻辑框图: (2)状态图: 状态圈-1: 状态圈-2: 状态圈-3: 状态圈-4: 状态圈-5: 状态圈-6: 状态圈-7: 状态圈-8:

状态圈-9: 状态圈-10: 状态圈-11: 状态圈-12: 2.已知图3-2所示的7级线性反馈移位寄存器: 图3-2 (1)绘出该移位寄存器的线性递推式,联接多项式及特征多项式。 (2)给出状态转移矩阵。 (3)设初态为(1 1 1 1 1 1 1),给出输出序列a 。 解:(1)由逻辑框图得,递推式为: k k k k a a a a ++=+++357 ()0≥k 。 联接多项式为:7 4 2 1)(x x x x f +++=。 特征多项式为:7531)(~ x x x x f +++=

(2)状态转移矩阵:? ? ???? ? ?? ? ? ??0100000 101000000010001000100 000001000000011000000。 (3)输出序列:)111111111(ΛΛ=- a 。 3.设5级线性反馈移位寄存器的联接多项式为1)(2 5 ++=x x x f ,初态为(10101)。求输出序列a 。 解:由联接多项式得,反馈函数为:41521),,,(x x x x x f +=Λ。故以)10101(为初态的状态转移图为: 10101 01010001010001000001100000100000100100100100110100110100110100110100111100111100111101111101111001110001110001110000110010110110111110101110101110101110101→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→→ 由此可得,输出序列为:=a 44444443444444421一个周期 0110100100000011111001010111011…。 4.证明:n 级线性反馈移位寄存器的状态转移变换是n 维线性空间n F 2上的线性变换。 证明:设f T 为n 级线性移位寄存器的状态转移变换,对n F 2,∈?βα,令),,,(110-=n a a a Λα, ),,,(110-=n b b b Λβ,有: ),,,(),,,()(121110∑=--==n i i n i n f f a c a a a a a T T ΛΛα, ),,,(),,,()(1 21110∑=--==n i i n i n f f b c b b b b b T T ΛΛβ。 ) ()() ,,,(),,,() )(,,,() ,,,()(1 211 2112211111100βαβαf f i n n i i i n n i i n i i n i n i n n f f T T b c b b a c a a b a c b a b a b a b a b a T T +=+=+++=+++=+-=-==----∑∑∑ΛΛΛΛ 对 2F k ∈?, ))((),,,(),,,()(1 21110ααf i n n i i n f f T k a c k ka ka ka ka ka T k T ===-=-∑ΛΛ。 故n 级线性反馈移位寄存器的状态转移变换是n 为线性空间n F 2上的线性变换。

msp430状态寄存器介绍概括

寄存器实在太多了。。我有个文档给你看看吧、、 MSP430寄存器中文注释---P1/2口(带中断功能) /************************************************************ * DIGITAL I/O Port1/2 寄存器定义有中断功能 ************************************************************/ #define P1IN_ 0x0020 /* P1 输入寄存器*/ const sfrb P1IN = P1IN_; #define P1OUT_ 0x0021 /* P1 输出寄存器*/ sfrb P1OUT = P1OUT_; #define P1DIR_ 0x0022 /* P1 方向选择寄存器*/ sfrb P1DIR = P1DIR_; #define P1IFG_ 0x0023 /* P1 中断标志寄存器*/ sfrb P1IFG = P1IFG_; #define P1IES_ 0x0024 /* P1 中断边沿选择寄存器*/ sfrb P1IES = P1IES_; #define P1IE_ 0x0025 /* P1 中断使能寄存器*/ sfrb P1IE = P1IE_; #define P1SEL_ 0x0026 /* P1 功能选择寄存器*/ sfrb P1SEL = P1SEL_; #define P2IN_ 0x0028 /* P2 输入寄存器*/ const sfrb P2IN = P2IN_; #define P2OUT_ 0x0029 /* P2 输出寄存器*/ sfrb P2OUT = P2OUT_; #define P2DIR_ 0x002A /* P2 方向选择寄存器*/ sfrb P2DIR = P2DIR_; #define P2IFG_ 0x002B /* P2 中断标志寄存器*/ sfrb P2IFG = P2IFG_; #define P2IES_ 0x002C /* P2 中断边沿选择寄存器*/ sfrb P2IES = P2IES_; #define P2IE_ 0x002D /* P2 中断使能寄存器*/ sfrb P2IE = P2IE_; #define P2SEL_ 0x002E /* P2 功能选择寄存器*/ sfrb P2SEL = P2SEL_; MSP430寄存器中文注释---P3/4口(无中断功能) /************************************************************ * DIGITAL I/O Port3/4寄存器定义无中断功能 ************************************************************/ #define P3IN_ 0x0018 /* P3 输入寄存器*/

UART寄存器介绍

UART寄存器介绍 UARTn_BR: UART波特率寄存器 UARTn_BR[15:0]: 由定时器的装入寄存器定时装入相应内容。 UARTn_CR.Run=0可以装入直到UARTn_CR.Run=1才写入无效 UARTn_TxBUFR:UART传输寄存器 UARTn_TxBUFR[8]: 传输数据第八位或者奇偶校验位或者唤醒位或者未定义的位有相应操作模式决定 1.如果是001模式则此位写0 2.如果是8+校验111模式则此位由UART自己处理写入软件操作无效 UARTn_TxBUFR[7]: 传输数据第七位或者奇偶校验位 1.如果是7+校验011模式同样此位由UART自己处理写入软件操作无效 UARTn_TxBUFR[6:0]:数据位 UARTn_RxBuffer: UART接收寄存器 RX[9]:桢错误标志1表示此桢有问题 RX[8]:接收数据位8,或者奇偶校验位或者唤醒位

RX[7]:接收数据位7,或者奇偶校验位 RX[6:0]:数据位 UARTn_CR:UART控制寄存器 CR[15-11]保留都是0 CR[10]FifoEnble队列模式0关闭表示TxFIFO认为是包含了16位数据才是满栈 1是开启表示TxFIFO认为当前就是才是满栈直接置TxFULL位 CR[9]SCENBLE 智能卡关闭还是开启不使用则置0 CR[8]RxEnble 接收功能关闭开启由下降沿来触发RXD脚初始化 CR[7]Run=0波特率无用=1则有用 CR[6]LoopBack=0标准的接收和发送模式=1是特殊模式。此位只由UART无效被改变 CR[5]ParityOdd选择奇偶校验=0则为偶校验=1为奇校验CR[43]StopBits 00 0.5停止位01是1个停止位10是1.5个11是2个 CR[2:0] MODE 5种模式 UARTn_IER UART的中断允许寄存器 15-9保留位为0 8 RxHalfFullIE 接收存储器超过8位则置

14、芯片与寄存器的介绍

理解芯片控制的原理 如果要说做单片机很难吗?其实并不难,用3句话就可以讲明白: 第1句话:芯片管脚不是输入,就是输出。 我们所有的程序,用单片机控制的产品,以及外设,无非就是控制芯片的各个管脚输入或者输出两个状态;例如,芯片发送数据就是输出;芯片驱动一个产品,也是输出;芯片接收数据就是输入;单片机对一个存储芯片写输入,可以理解为单片机与存储芯片连接的管脚输出状态,输出数据到存储芯片的管脚上,而存储芯片此时它的芯片对应管脚被配置成输入,将数据写入到芯片内部。 所以说,芯片管脚不是输入,就是输出,当然,如果你不使用这个管脚,也可以将它配置成某一种中间状态,免得干扰了外界,影响了PCB板上的其他元器件状态。 第2句话:芯片管脚不是高电平,就是低电平。 无论管脚是输入还是输出,它的目的是传输数据,传输信息,所以要么是高电平,要么低电平,通过010101这样的数据来传输它想传输的内容;这个就是所谓的二进制。 第3句话:传输协议。 什么是传输协议,比如与串口芯片通信,那么就要是串口协议的;如果是I2C 协议的EERPOM,那么就是I2C协议;还有其他一些比如485协议,CAN协议,USB协议,SD卡的SDIO协议…….等等数不胜数。 而这些协议,无非就是按照预先规定的表达方式进行通信,比如举个例子,我约定先连续发4个1,,然后再发4个0,就表示芯片A要开始发数据给芯片B 了,即芯片A通过它的芯片管脚发‘11110000’给到芯片B的时候,那么芯片B 就知道芯片A要给它真正的数据,它就要做好准备工作,准备好之后,芯片B 就会给芯片A一个回应,当芯片A收到芯片B的回应,就正式开始发数据。 这样通信双方之间的协商规定,就构成了协议,经过这么多年,就形成了我们所常见到的串口协议,CAN协议,USB协议(像USB协议又分为USB1.0协议,USB2.0协议,USB3.0协议,版本越高,速度就越快,协议进行优化后,通信效率也变高了)。 不知道大家理解了没有呢?所以总结下来,一个芯片最简单的外设莫过于 I/O口的高低电平控制,我们这里将详细讲解一下如何用一个I/O口去控制一个LED灯的亮灭。

段寄存器的工作原理

一、段寄存器的产生 段寄存器的产生源于Intel 8086 CPU体系结构中数据总线与地址总线的宽度不一致。 数据总线的宽度,也即是ALU(算数逻辑单元)的宽度,平常说一个CPU是“16位”或者“32位”指的就是这个。8086CPU的数据总线是16位。 地址总线的宽度不一定要与ALU的宽度相同。因为ALU的宽度是固定的,它受限于当时的工艺水平,当时只能制造出16位的ALU;但地址总线不一样,它可以设计得更宽。地址总线的宽度如果与ALU相同当然是不错的办法,这样CPU的结构比较均衡,寻址可以在单个指令周期内完成,效率最高;而且从软件的解决来看,一个变量地址的长度可以用整型或者长整型来表示会比较方便。 但是,地址总线的宽度还要受制于需求,因为地址总线的宽度决定了系统可寻址的范围,即可以支持多少内存。如果地址总线太窄的话,可寻址范围会很小。如果地址总线设计为16位的话,可寻址空间是2^16=64KB,这在当时被认为是不够的;Intel最终决定要让8086的地址空间为1M,也就是20位地址总线。 地址总线宽度大于数据总线会带来一些麻烦,ALU无法在单个指令周期里完成对地址数据的运算。有一些容易想到的可行的办法,比如定义一个新的寄存器专门用于存放地址的高4位,但这样增加了计算的复杂性,程序员要增加成倍的汇编代码来操作地址数据而且无法保持兼容性。 Intel想到了一个折中的办法:把内存分段,并设计了4个段寄存器,CS,DS,ES和SS,分别用于指令、数据、其它和堆栈。把内存分为很多段,每一段有一个段基址,当然段基址也是一个20位的内存地址。不过段寄存器仍然是16位的,它的内容代表了段基址的高16位,这个16位的地址后面再加上4个0就构成20位的段基址。而原来的16位地址只是段内的偏移量。这样,一个完整的物理内存地址就由两部分组成,高16位的段基址和低16位的段内偏移量,当然它们有12位是重叠的,它们两部分相加在一起,才构成完整的物理地址。 Base b15 ~ b12 b11 ~ b0 Offset o15 ~ o4 o3 ~ o0 Address a19 ~ a0 这种寻址模式也就是“实地址模式”。在8086中,段寄存器还只是一个单纯的16位寄存器,而且操作寄存器的指令也不是特权指令。通过设置段寄存器和段内偏移,程序就可以访问整个

AD9833详细原理解析(附内部寄存器说明)

基于AD9833的高精度可编程波形发生器系统设计 来源:国外电子元器件 1 引言 频率合成器在通信、雷达和导航等设备中既是发射机的激励信号源,又是接收机的本地振荡器;在电子对抗设备中可作为干扰信号发生器;在测试设备中则作为标准信号源。因此频率合成器被称为许多电子系统的“心脏”。而设计高精度,易于操作的频率合成器则是核心,因此,这里提出了一种基于DDS AD9833的高精度波形发生器系统解决方案。用户可直接编辑设置所需的波形频率和峰峰值等信息,利用串口将配置信息发送到电路板,实时控制波形。该系统设计已成功应用于某型雷达测速仪测试设备。 2 AD9833简介 AD9833是ADI公司的一款低功耗、DDS器件,能够输出正弦波、三角波、方波。AD9833无需外接元件,输出频率和相位可通过软件编程设置,易于调节。其频率寄存器为28位,主频时钟为25 MHz时,其精度为0.1 Hz;主频时钟为l MHz时.精度可达0.004 Hzt2。 AD9833内部有5个可编程寄存器:1个16位控制寄存器,用于设置器件_T 作模式;2个28位频率寄存器和2个12位相位寄存器,分别用于设置器件输出正弦波的频率和相位。AD9833有3根串行接口线,可与SPI,QSPI,MICRO-WIRE 和DSP接口标准相兼容。在串口时钟SCLK的作用下,数据是以16位方式加载至设备。 AD9833的内部电路主要有数控振荡器(NCO)、频率和相位调节器、SineROM、D/A转换器、电压调整器。AD9833的核心是28位的相位累加器,它由加法器和相位寄存器组成,而相位寄存器是按每个时钟增加步长,相位寄存器的输出与相位控制字相加后输入到正弦查询表地址中。正弦查询表包含1个周期正弦波的数字幅值信息,每个地址对应正弦波中O。~360°内的1个相位点。查询表把输入的地址相位信息映射成正弦波幅值的数字量信号,驱动D/A转换器输出模拟量。 输出正弦波频率为: 式中:FREQREG为频率控制字,由频率寄存器FREQOREG或FREQlREG的值给定,其范围为0≤M<228一1。fMCLK为参考时钟频率。 输出正弦波的相位为2π/4 096xPHASEREG,其中PHASEREG是所选相位寄存器的值。输出正弦波的峰峰值固定.约600 mV,且正弦波不是标准正弦波,即波谷是0 V,而不是负电压。因此,输出正弦波为: 式中:K约600 mV,与器件内部参考电压有关。

ARM寄存器简介

ARM寄存器简介 ARM处理器含有37个寄存器,这些寄存器包括以下两类寄存器。 (1)31个通用寄存器:包括程序计数器PC等,这些寄存器都是32位寄存器。 (2)6个状态寄存器:状态寄存器也是32位的寄存器,但是只使用了其中的12位。 1.通用寄存器 在ARM处理器的7种模式下都有一组对应的寄存器组。在任意时刻,可见的寄存器组包括15个通用寄存器R0~R14、一个或两个状态寄存器和PC。在所有的寄存器中,有些是各种模式下共用的同一个物理寄存器,有些是各种模式自己独立拥有的物理寄存器。详细如表1-3所示。 表1-3 ARM物理寄存器 用户模式系统模 式特权模式中止模式未定义指令 模 外部中断模快速中断模 R0 R0 R0 R0 R0 R0 R0 R1 R1 R1 R1 R1 R1 R1 R2 R2 R2 R2 R2 R2 R2 R3 R3 R3 R3 R3 R3 R3 R4 R4 R4 R4 R4 R4 R4 R5 R5 R5 R5 R5 R5 R5 R6 R6 R6 R6 R6 R6 R6 R7 R7 R7 R7 R7 R7 R7 R8 R8 R8 R8 R8 R8 R8_fiq R9 R9 R9 R9 R9 R9 R9_fiq R10 R10 R10 R10 R10 R10 R10_fiq R11 R11 R11 R11 R11 R11 R11_fiq R12 R12 R12 R12 R12 R12 R12_fiq R13 R13 R13_svc R13_abt R13_und R13_irq R13_fiq R14 R14 R14_svc R14_abt R14_und R14_irq R14_fiq PC PC PC PC PC PC PC CPSR CPSR CPSR CPSR CPSR CPSR CPSR SPSR_svc S PSR_abt SPSR_und SPSR_irq SPSR_fiq 通用寄存器通常又可以分为下面3类。 n 未备份寄存器:包括R0~R7。 n 备份寄存器:包括R8~R14。

SDHC部分寄存器介绍

11.3.2 K60的SD模块存储器映像与寄存器定义 K60的SDHC模块主要使用到表11-6中寄存器,其他寄存器详细信息可参见网络光盘中的本章阅读材料。 表11-6 SDHC模块部分寄存器列表 1.块属性寄存器(Block Attributes Register,SDHC_BLKATTR) 这个寄存器是用来配置数据块数和每块的字节数。 图52-4 SDHC_BLKATTR D31~D16—BLKCNT位,当前传输的块数。当XFERTYP[BCEN]被置1时,该寄存器有用,仅用于多块间传输。主驱动应设定该寄存器为从1到最大块数(最大为65535块)之间的一个值,每块传输并停止后,该域自减1,直到块数为0。设定块数为0将导致没有数据块传输。当XFERTYP [MSBDEL]位被清零时,只能单块传输,BLKCNT的读值总为1。当为0时,表示停止计数;为1时,表示1块;为0xFFFF时,表示65535块。 D15~D13—保留。 D12~D0—BLKSIZE位,传输块的大小。该寄存器为块数据传输时,每块数据大小,其值可被设定为1字节到最大缓冲值(最大为4096字节)之间的数。该域在SDHC空闲时,修改才有效。传输期间的读操作可能发回一个无效值,且修改无效。当为0时,表示无数据传输;为1时,表示1字节;为0x1000时,表示4096块。 2.命令参数寄存器(Command Argument Register,SDHC_CMDARG) 该寄存器用于写入SD/MMC操作命令参数。 D31~D0—CMDARG位,命令内容。在SD或MMC的协议中,SD/MMC命令内容被

指定在命令格式的39-8位。当PRSSTAT[CDIGBO]为1,该寄存器被写保护。 3.传输类型寄存器(Transfer Type Register,SDHC_XFERTYP) D31~D30—保留。 D29~D24—CMDINX位,命令索引。在SD储存卡物理层协议和SDIO卡协议中,这些位的命令应设为命令格式的45-40位。 D23~D22—CMDTYP位,命令类型。一共可以设置四种命令类型,执行普通命令时,该域为0。3种特殊类型命令:暂停,重新开始,和中止命令。暂停命令:如果暂停命令成功,SDHC模块认为总线已经释放,并有可能使用DAT通道发出下一个命令;重新开始命令:主驱动通过在发送暂停命令之前,恢复寄存器储存值重新开始数据传输,并发送重新开始命令;中止命令:如果当执行读传输时发送该命令,SDHC将停止读入缓冲。如果当执行写传输时发送该命令,SDHC将停止DAT通道。终止命令发放后,主机驱动器发送一个软件复位命令。 D21—DPSEL位,传输时的数据选择。当该域为1时,表明数据需要发送并且通过DAT 通道传输。当该域为0时,表明命令仅通过CMD通道或没有数据传输的命令,但使用繁忙信号通道DAT[0]。 D20—CICEN位,命令索引检测使能。如果该位置1,SDHC将检测响应值是否与命令索引相等。如果不等,将报告命令索引错误;如果该位置0,则不检测响应。 D19—CCCEN位,命令CRC检测使能。如果该位置1,SDHC将检测响应的CRC字段。如果检测到错误则报告命令CRC错误。如果该位置0,不检测CRC段,这些位由CRC 字段值根据响应长度的变化检测。 D18—保留。 D17~D16—RSPTYP位,响应类型。00b:无响应;01b:响应长度136;10b:响应长度48;11b:响应长度48,响应后检测忙碌状态。 D15~D6—保留。 D5—MSBSEL位,多/单块选择。该位控制多块DAT通道数据传输,对其他命令,该位应置为0。如果该位为1,就不必设定块计数寄存器。 D4—DTDSEL位,数据传输方向选择。该位定义了DAT通道数据发送的方向。当主驱动从SD卡发送数据到SDHC时该位置1,其他命令时则置0。 D3—保留。 D2—AC12EN位,自动CMD12使能。存储器的多块传输需要CMD12停止事务。当该位为1,在最后块传输完成后,SDHC将自动发出一个CMD12。主驱动发出的命令不需

(整理)2移位寄存器及其应用.

实验七移位寄存器及其应用 一、实验目的 1.移位寄存器74LS194的逻辑功能及使用方法; 2.熟悉4位移位寄存器的应用。 二、实验预习要求 1.了解74LS194的逻辑功能; 2.用4位移位寄存器构成8位移位寄存器; 3.了解移位寄存器构成环形计数器的方法。 三、实验原理 1. 移位寄存器是指寄存器中所存的代码能够在移位脉冲的作用下依次左移或右移。74 LS194是一个4位双向移位寄存器,最高时钟脉冲为36MHz,其逻辑符号及引脚排列如图实验7.1所示。 图实验7.1 74 LS194逻辑符号及引脚排列 其中:D0~D1为并行输入端;Q0~Q3为并行输出端;SR-右移串引输入端;SL-左移串引输入端;S1、S0-操作模式控制端;/CR-为直接无条件清零端;CP-为时钟脉冲输入端。74LS194模式控制及状态输出如表实验7.1所示。 2. 用74LS194构成8位移位寄存器 电路如图实验7.2所示,将芯片(1)的Q3接至芯片(2)的SR,将芯片(2)的Q4接至芯片(1)的SL,即可构成8位的移位寄存器。注意:/CR端必须正确连接。3. 74LS194构成环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图实验7.3所示。设初态为Q3Q2Q1Q0=1000,则在CP作用下,模式设为右移,输出状态依次为: 表实验7.1 74LS194工作状态表

2. 用74LS194构成8位移位寄存器 电路如图实验7.2所示,将芯片(1)的Q3接至芯片(2)的SR,将芯片(2)的Q4接至芯片(1)的SL,即可构成8位的移位寄存器。注意:/CR端必须正确连接。 图实验7.2 8位移位寄存器 3. 74LS194构成环形计数器 把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图实验7.3所示。设初态为Q3Q2Q1Q0=1000,则在CP作用下,模式设为右移,输出状态依次为:

单片机寄存器名称

【转】【51单片机特殊功能寄存器功能一览表】 Posted on 2011-03-26 15:07 香格里拉\(^o^)/阅读(688) 评论(0)编辑收藏 【转】【51单片机寄存器功能一览表】 21个特殊功能寄存器(52系列是26个)不连续地分布在128个字节的SF R存储空间中,地址空间为80H-FFH,在这片SF R空间中,包含有128个位地址空间,地址也是80H-FFH,但只有83个有效位地址,可对11个特殊功能寄存器的某些位作位寻址操作(这里介绍一个技巧:其地址能被8整除的都可以位寻址)。 在51单片机内部有一个CPU用来运算、控制,有四个并行I/O口,分别是P0、P1、P2、P3,有R OM,用来存放程序,有R AM,用来存放中间结果,此外还有定时/计数器,串行I/O口,中断系统,以及一个内部的时钟电路。在单片机中有一些独立的存储单元是用来控制这些器件的,被称之为特殊功能 寄存器(SF R)。这样的特殊功能寄存器51单片机共有21个并且都是可寻址的列表如下(其中带*号的为52系列所增加的特殊功能寄存器):

分别说明如下: 1、ACC---是累加器,通常用A表示 这是个什么东西,可不能从名字上理解,它是一个寄存器,而不是一个做加法的东西,为什么给它这么一个名字呢?或许是因为在运算器做运算时其中一个数一定是在ACC中的缘故吧。它的名字特殊,身份也特殊,稍后在中篇中我们将学到指令,可以发现,所有的运算类指令都离不开它。自身带有全零标志Z,若A=0则Z=1;若A≠0则z=0。该标志常用作程序分枝转移的判断条件。 2、B--一个寄存器 在做乘、除法时放乘数或除数,不做乘除法时,随你怎么用。 3、PSW-----程序状态字。 这是一个很重要的东西,里面放了CPU工作时的很多状态,借此,我们可以了解CPU的当前状态,并作出相应的处理。它的各位功能请看下表: 下面我们逐一介绍各位的用途 CY:进位标志。 8051中的运算器是一种8位的运算器,我们知道,8位运算器只能表示到0-255,如果做加法的话,两数相加可能会超过255,这样最高位就会丢失,造成运算的错误,怎么办?最高位就进到这里来。这样就没事了。有进、借位,CY=1;无进、借位,CY=0 例:78H+97H(01111000+10010111) AC:辅助进、借位(高半字节与低半字节间的进、借位)。

通用寄存器的作用

通用寄存器的作用 数据寄存器不讲,简单的说,段寄存器(ES,CS,SS,DS,FS,GS)和变址寄存器(SI,DI)是配合使用访问段数据的,指针寄存器(BP,SP)是用来操作堆栈的,BP指向栈的基址,SP则永远指向栈顶。 另外指令指针EIP存放的是要执行的下一条指令在代码段里的偏移量,在实方式下,每个段的最大范围都是64K,所以EIP的高16位都是0。 寄存器的分类寄存器主要用途 通用寄存器 数据 寄存器 AX 乘、除运算,字的输入输出,中间结果的缓存 AL 字节的乘、除运算,字节的输入输出,十进制算术运算 AH 字节的乘、除运算,存放中断的功能号 BX 存储器指针 CX 串操作、循环控制的计数器 CL 移位操作的计数器 DX 字的乘、除运算,间接的输入输出 变址 寄存器 SI 存储器指针、串指令中的源操作数指针 DI 存储器指针、串指令中的目的操作数指针 变址 寄存器 BP 存储器指针、存取堆栈的指针 SP 堆栈的栈顶指针 指令指针IP/EIP 标志位寄存器Flag/EFlag 32位CPU的段寄存器16位CPU的 段寄存器 ES 附加段寄存器 CS 代码段寄存器 SS 堆栈段寄存器 DS 数据段寄存器新增加的 段寄存器 FS 附加段寄存器 GS 附加段寄存器

--------------------------------- 1、数据寄存器 数据寄存器主要用来保存操作数和运算结果等信息,从而节省读取操作数所需占用总线和访问存储器的时间。 32位CPU有4个32位的通用寄存器EAX、EBX、ECX和EDX。对低16位数据的存取,不会影响高16位的数据。这些低16位寄存器分别命名为:AX、BX、CX和DX,它和先前的CPU中的寄存器相一致。 4个16位寄存器又可分割成8个独立的8位寄存器(AX:AH-AL、BX:BH-BL、CX:CH-CL、DX:DH-DL),每个寄存器都有自己的名称,可独立存取。程序员可利用数据寄存器的这种“可分可合”的特性,灵活地处理字/字节的信息。 寄存器AX和AL通常称为累加器(Accumulator),用累加器进行的操作可能需要更少时间。 累加器可用于乘、除、输入/输出等操作,它们的使用频率很高; 寄存器BX称为基地址寄存器(Base Register)。它可作为存储器指针来使用; 寄存器CX称为计数寄存器(Count Register)。在循环和字符串操作时,要用它来控制循环次 数;在位操作中,当移多位时,要用CL来指明移位的位数; 寄存器DX称为数据寄存器(Data Register)。在进行乘、除运算时,它可作为默认的操作数 参与运算,也可用于存放I/O的端口地址。 在16位CPU中,AX、BX、CX和DX不能作为基址和变址寄存器来存放存储单元的地址,但在32位CPU中,其32位寄存器EAX、EBX、ECX和EDX不仅可传送数据、暂存数据保存算术逻辑运算结果,而且也可作为指针寄存器,所以,这些32位寄存器更具有通用性。详细内容请见第3.8节——32位地址的寻址方式。 2、变址寄存器 32位CPU有2个32位通用寄存器ESI和EDI。其低16位对应先前CPU中的SI 和DI,对低16位数据的存取,不影响高16位的数据。 寄存器ESI、EDI、SI和DI称为变址寄存器(Index Register),它们主要用于存放存储单元在段内的偏移量,用它们可实现多种存储器操作数的寻址方式(在第3章有详细介绍),为以不同的地址形式访问存储单元提供方便。 变址寄存器不可分割成8位寄存器。作为通用寄存器,也可存储算术逻辑运算的操作数和运算结果。 它们可作一般的存储器指针使用。在字符串操作指令的执行过程中,对它们有特定的要求,而且还具有特殊的功能。具体描述请见第5.2.11节。 3、指针寄存器 32位CPU有2个32位通用寄存器EBP和ESP。其低16位对应先前CPU中的SBP 和SP,对低16位数据的存取,不影响高16位的数据。 寄存器EBP、ESP、BP和SP称为指针寄存器(Pointer Register),主要用于存放堆栈内存储单元的偏移量,用它们可实现多种存储器操作数的寻址方式(在第3章有详细介绍),为以不同的地址形式访问存储单元提供方便。

寄存器的赋值

C 编程之——寄存器赋值操作(转) 通过这段时间的工作和学习,我感觉在嵌入式硬件编程中,大多数情况下都是对相应硬件的功能寄存器进行设置和操作。 一, 寄存器的设置和操作特性 1,一个寄存器的每个位有其不同的意义,进行不同的设置会使硬件产生不同的效果和功能; 2,有些情况下需要对一个寄存器进行连续的不同的甚至完全相反的设置; 3,有些情况下需要对一个寄存器中的某一位或一位进行连续的不同的甚至完全相反的设置,而其余的位要保持不变; 4,有时,对一个寄存器进行设置时,对其不同的位进行先后顺序不同的设置,即对其各个位有先后设置的顺序的要求,使硬件产生的结果也不同; 5,有时,对于一个寄存器要求必须一次赋值,若对其某些位赋值先后顺序不同,便达不到预期的效果和功能。 二,寄存器的赋值操作方法 为说明方便,定义如下3个8位的寄存器: #define REG 0xFFFFFF10 1,对单个的位进行赋值

(1)将寄存器REG的第5位置“1” REG |= (1 << 5); (2)将寄存器REG的第5位清零 REG &= ~(1 << 5); (3)将寄存器REG的第3、5位置“1” REG |= (1 << 5) | (1 << 3); (4)将寄存器REG的第3、5位清零 REG &= ~( (1 << 5) | (1 << 3) ); 2,直接赋值 (1)将寄存器REG的0、1、2、3、5、7位置“1” REG = 0x5F; (即给寄存器REG1赋值为1010 1111,这种方法多在初始化中用)(2)分别将寄存器REG的1、3、5、7位置“1”,0、2位置“0” uint32 temp; tmep = REG; temp &= ~0x01; temp |= (1 << 1); temp &= ~(1 << 2); temp |= (1 << 3); temp |= (1 << 5); temp |= (1 << 7); REG = temp;