基于状态机的工程设计

2.6.4.2 基于状态机的工程设计方法

学习利用quartusII软件中的状态机编辑器设计一个1110010序列检测器。

1.建立工程文件

工程文件的建立主要包括指定工程文件名称、选择添加的文件和库及选择目标器件3个过程。

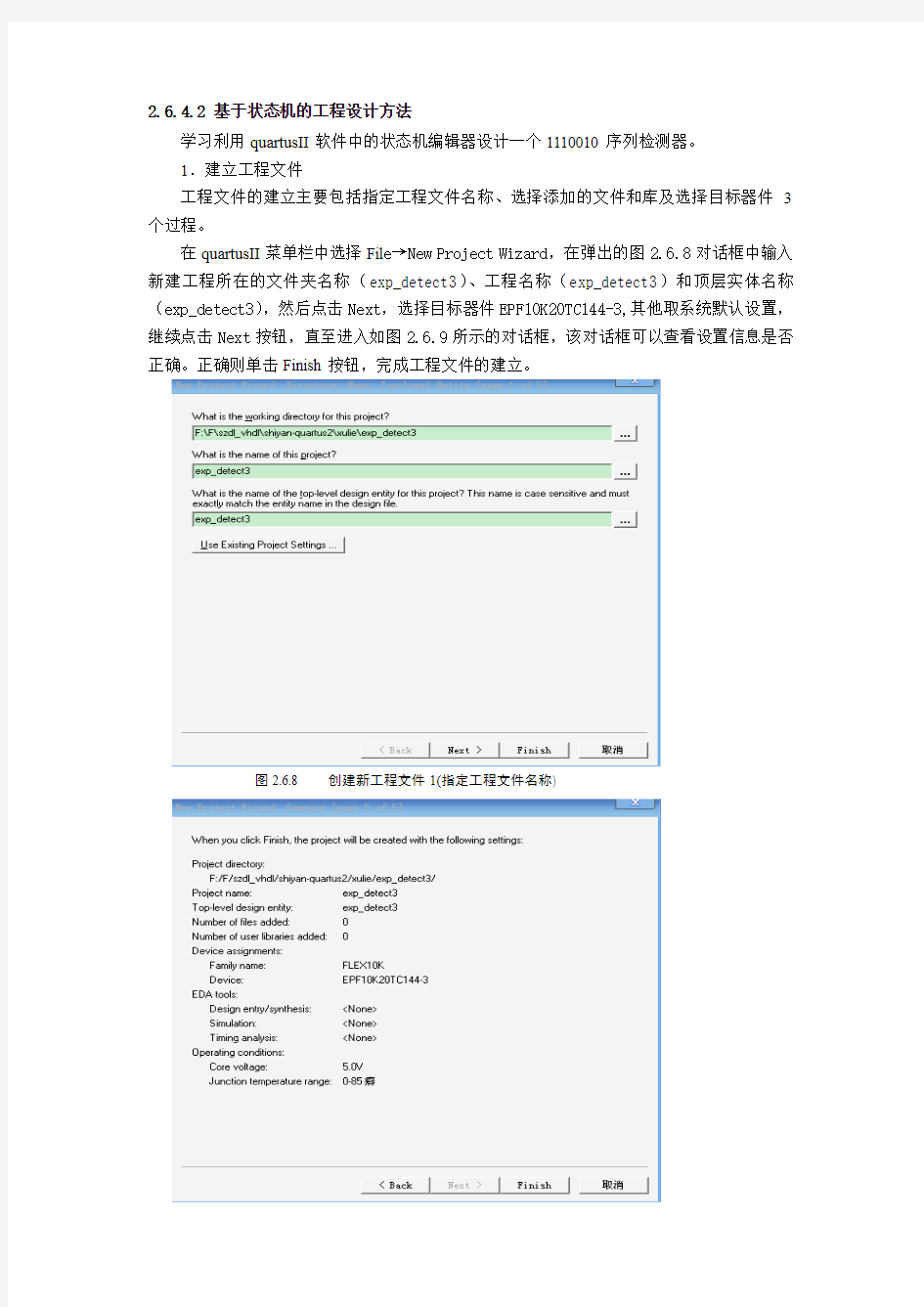

在quartusII菜单栏中选择Fil e→New Project Wizard,在弹出的图2.6.8对话框中输入新建工程所在的文件夹名称(exp_detect3)、工程名称(exp_detect3)和顶层实体名称(exp_detect3),然后点击Next,选择目标器件EPF10K20TC144-3,其他取系统默认设置,继续点击Next按钮,直至进入如图2.6.9所示的对话框,该对话框可以查看设置信息是否正确。正确则单击Finish按钮,完成工程文件的建立。

图2.6.8 创建新工程文件1(指定工程文件名称)

图2.6.9 工程创建结束对话框

2.输入状态机

⑴建立文件

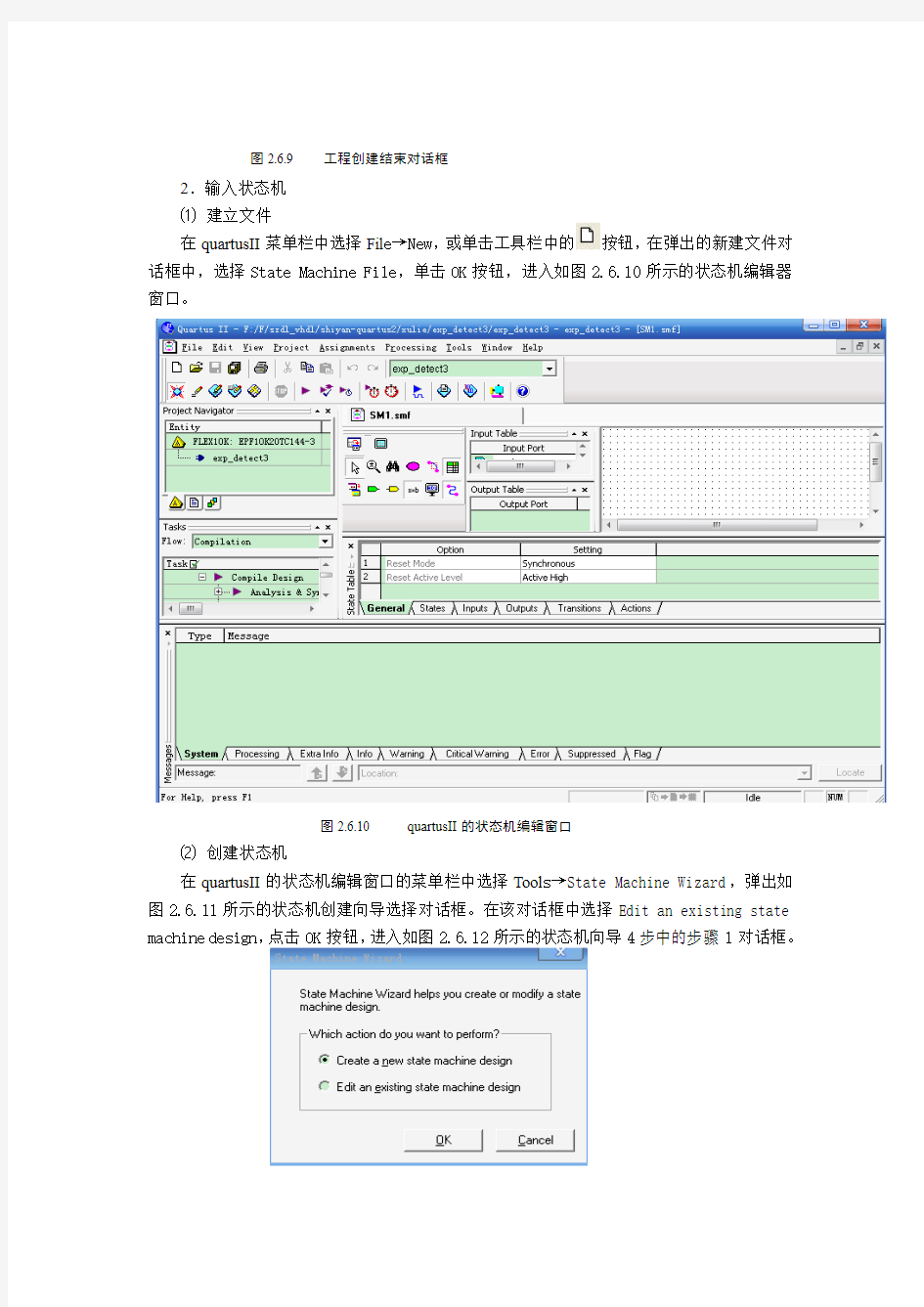

在quartusII菜单栏中选择Fil e→New,或单击工具栏中的按钮,在弹出的新建文件对话框中,选择State Machine File,单击OK按钮,进入如图2.6.10所示的状态机编辑器窗口。

图2.6.10 quartusII的状态机编辑窗口

⑵创建状态机

在quartusII的状态机编辑窗口的菜单栏中选择Tool s→State Machine Wizard,弹出如图2.6.11所示的状态机创建向导选择对话框。在该对话框中选择Edit an existing state machine design,点击OK按钮,进入如图2.6.12所示的状态机向导4步中的步骤1对话框。

图2.6.11 状态机创建向导选择对话框

①状态机向导步骤1:

在图 2.6.12对话框中,选择复位Reset信号模式:同步(Synchronous)或者异步(Asynchronous),该序列检测器设计选择异步复位;选中复位信号Reset高电平有效(Reset is active-high);选中输出端的输出方式为寄存器方式(Register the output ports),点击Next 按钮,进入状态机向导步骤2对话框如图2.6.13。

图2.6.12 状态机向导步骤1

②状态机向导步骤2:状态转换

在图2.6.13状态转换对话框中,在States栏中输入1110010序列检测器的状态名称s0、s1…s7,在Input ports栏中输入该检测器状态机的输入时钟信号clock、复位信号reset以及串行数据输入信号din。在State transitions栏中依据该序列检测器设计的状态图依次输入各种状态转换,设置完后点击Next,进入状态机向导步骤3的对话框,如图2.6.14

图2.6.13 状态机向导步骤2(状态转换)

③状态机向导步骤3:

在图2.6.14所示对话框中,在Output ports栏下的Output Port Name中输入该序列检测器设计的输出信号z,在Output State栏中选择Next clock cycle;在Action condition栏下的Output Port中输入该设计的输出信号z,在Output V alue栏以及INState栏中输入该设计的检测结果1极其状态s7。设置完后点击Next进入如图2.6.15所示的状态机向导步骤4。

图2.6.14 状态机向导步骤3

④状态机向导步骤4:

在图2.6.15所示对话框中显示出状态机的设置情况。点击Finish,关闭状态机向导,生成所需的状态机,将该状态机的各状态位置做适当调整,得到我们所需的状态图,如图2.6.16。

图2.6.15 状态机向导步骤4

图2.6.16 利用状态机向导完成的状态图

⑶保存文件

单击菜单栏中的按钮,在弹出的“另存为|”对话框中,默认该设计文件为exp_detect3.smf,选中Add file to current project,点击保存按钮,完成文件保存。

⑷生成对应的VHDL文件

选择Too l→Generate HDL File,在弹出的对话框2.6.17中选择产生程序代码HDL语言的种类,选择VHDL,点击OK按钮,则自动生成对应的余状态机文件名相同的VHDL文本文件exp_detect3.vhd,在文本编辑窗口中打开该状态机的VHDL代码。

图2.6.17 生成HDL文件对话框

基于状态机输入的1110010序列检测器的VHDL代码:exp_detect3.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY exp_detect3 IS

PORT

( clock : IN STD_LOGIC;

reset : IN STD_LOGIC := '0';

din : IN STD_LOGIC := '0';

z : OUT STD_LOGIC );

END exp_detect3;

ARCHITECTURE BEHAVIOR OF exp_detect3 IS

TYPE type_fstate IS (s0,s1,s2,s3,s4,s5,s6,s7);

SIGNAL fstate : type_fstate;

SIGNAL reg_fstate : type_fstate;

SIGNAL reg_z : STD_LOGIC := '0';

BEGIN

PROCESS (clock,reg_fstate)

BEGIN

IF (clock='1' AND clock'event) THEN

fstate <= reg_fstate;

END IF;

END PROCESS;

PROCESS (fstate,reset,din,reg_z)

BEGIN

IF (reset='1') THEN

reg_fstate <= s0;

reg_z <= '0';

z <= '0';

ELSE

reg_z <= '0';

z <= '0';

CASE fstate IS

WHEN s0 =>

IF ((din = '1')) THEN

reg_fstate <= s1;

ELSIF (NOT((din = '1'))) THEN

reg_fstate <= s0;

-- Inserting 'else' block to prevent latch inference

ELSE

reg_fstate <= s0;

END IF;

WHEN s1 =>

IF ((din = '1')) THEN

reg_fstate <= s2;

ELSIF (NOT((din = '1'))) THEN

reg_fstate <= s0;

-- Inserting 'else' block to prevent latch inference ELSE

reg_fstate <= s1;

END IF;

WHEN s2 =>

IF ((din = '1')) THEN

reg_fstate <= s3;

ELSIF (NOT((din = '1'))) THEN

reg_fstate <= s0;

-- Inserting 'else' block to prevent latch inference ELSE

reg_fstate <= s2;

END IF;

WHEN s3 =>

IF (NOT((din = '1'))) THEN

reg_fstate <= s4;

ELSIF ((din = '1')) THEN

reg_fstate <= s2;

-- Inserting 'else' block to prevent latch inference ELSE

reg_fstate <= s3;

END IF;

WHEN s4 =>

IF (NOT((din = '1'))) THEN

reg_fstate <= s5;

ELSIF ((din = '1')) THEN

reg_fstate <= s1;

-- Inserting 'else' block to prevent latch inference ELSE

reg_fstate <= s4;

END IF;

WHEN s5 =>

IF ((din = '1')) THEN

reg_fstate <= s6;

ELSIF (NOT((din = '1'))) THEN

reg_fstate <= s0;

-- Inserting 'else' block to prevent latch inference

ELSE

reg_fstate <= s5;

END IF;

WHEN s6 =>

IF (NOT((din = '1'))) THEN

reg_fstate <= s7;

ELSIF ((din = '1')) THEN

reg_fstate <= s2;

-- Inserting 'else' block to prevent latch inference

ELSE

reg_fstate <= s6;

END IF;

WHEN s7 =>

IF ((din = '1')) THEN

reg_fstate <= s1;

ELSIF (NOT((din = '1'))) THEN

reg_fstate <= s0;

-- Inserting 'else' block to prevent latch inference

ELSE

reg_fstate <= s7;

END IF;

reg_z <= '1';

WHEN OTHERS =>

reg_z <= 'X';

report "Reach undefined state";

END CASE;

z <= reg_z;

END IF;

END PROCESS;

END BEHAVIOR;

⑸综合出的RTL viewer

图2.6.18 exp_detect3的(rtl viewer)

⑹仿真验证图

用状态机输入法完成的1110010序列检测器设计的仿真验证结果如图26.19。

图2.6.19 用状态机输入法完成的1110010序列检测器设计的仿真结果图

⑺下载硬件验证,观察实验结果并记录实验数据

⑻实验数据记录

①波形图

②波形仿真参数设置

③波形说明