微机原理与单片机(部分知识点)

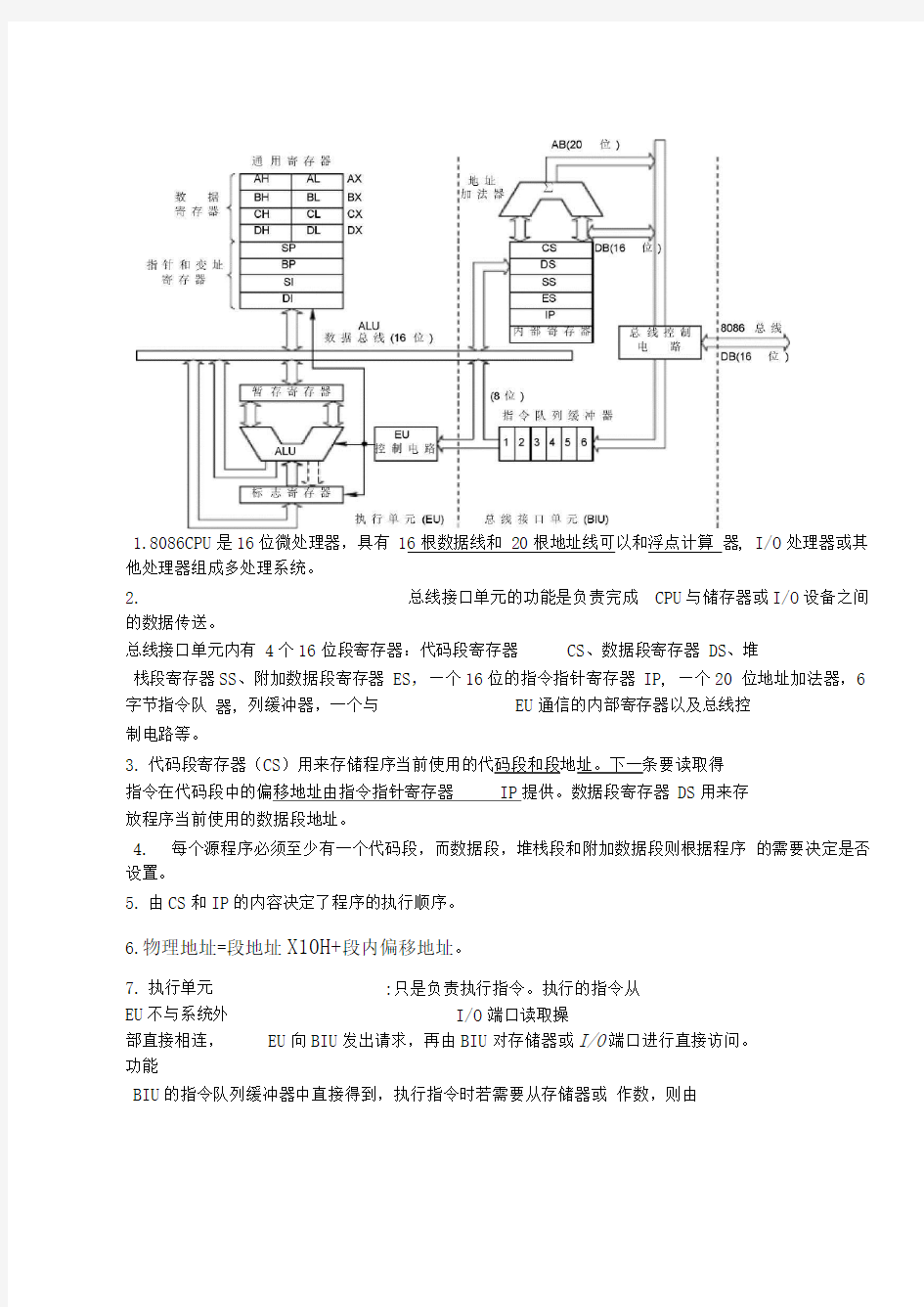

1.8086CPU 是16位微处理器,具有 16根数据线和 20根地址线可以和浮点计算 器, I/O 处理器或其

他处理器组成多处理系统。

2.

总线接口单元的功能是负责完成 CPU 与储存器或I/O 设备之间

的数据传送。

总线接口单元内有 4个16位段寄存器:代码段寄存器 CS 、数据段寄存器 DS 、堆

栈段寄存器SS 、附加数据段寄存器 ES ,—个16位的指令指针寄存器 IP , —个20 位地址加法器,6

字节指令队列缓冲器,一个与 EU 通信的内部寄存器以及总线控

制电路等。

3. 代码段寄存器(CS )用来存储程序当前使用的代码段和段地址。下一条要读取得

指令在代码段中的偏移地址由指令指针寄存器 IP 提供。数据段寄存器 DS 用来存

放程序当前使用的数据段地址。

4. 每个源程序必须至少有一个代码段,而数据段,堆栈段和附加数据段则根据程序 的需要决定是否

设置。

5. 由CS 和IP 的内容决定了程序的执行顺序。

6.物理地址=段地址X10H+段内偏移地址。

7. 执行单元EU 不与系统外

部直接相连,功能

BIU 的指令队列缓冲器中直接得到,执行指令时若需要从存储器或 作数,则由

器, :只是负责执行指令。执行的指令从

I/O 端口读取操

EU 向BIU 发出请求,再由BIU 对存储器或I/O 端口进行直接访问。

8. EU 组成:1)16位算数逻辑单元(ALU ),2)16位标志寄存器 FLAGS ,3)数据 暂存寄存器, 9.8086和8088的差异:1)外

部数据总线不同,

队列缓冲器大小不同, 脚的功能定义有所区别

4)通用寄存器,5)EU 控制电路 8086是16位,8088是8位,2)指令

8086可容纳6个字节,8088只能容纳4个字节,3)部分引

8086/8088CPU 中可供编程使用的有 14个16位寄存器,按其用途可分为

3类:通

用寄存器、段寄存器、控制寄存器。

10.通用寄存器(累加器 AX 、基址寄存器 BX 、计数器CX 、数据寄存器 DX )高8 位 AH 、BH 、CH 、DH ; 底 8 位 AL 、BL 、CL 、DL

11.标志寄存器FLAG : 16位寄存器,共9个标志,其中6个用作状态标志,3个用 作控制标志。 状态标志CF :进位标志,ZF :零标志位,SF :符号标志位,IF :中断允许标志位

12.8084A

位时钟发生器,8282为8位地址锁存器,8086为具有三态输出的 8位数 据总线收发器

13. INTA 引脚24,中断响应信号,作为输出;

ALE 引脚25,地址锁存允许信

号,作为输出;

14.8088与8086引脚不同:1)AD15 — A8的定位不同;2)引脚34的定义不同;引 脚28的有效电

平高低定义不同

15.8086/8088CPU 有20条地址线,可直接对

元放一个字节(8位)数据,一个“字”占两个字节即

一个20位的地址,这 1M 个存储单元对应的地址为

220

-1)

16.堆栈操作(1)存放指令操作数(2)保护断点和现场;每进行一次进站操作, SP 值减2,每进行一

次出栈操作,

SP 加2;栈底(先存),栈顶(先取)

17.存储器/IO 读时序:1)T1,M /IO 信号:从存储器读还是从

I/O 设备中读数

据;ALE :地址锁存信号,以使地址 /数据线分开。2)T2状态,RD 由高电平变

为低电平,开始进行读数据操作。

18.. 8086/8088有20条地址线,可直接对 1 M 个存储单元进行访问。每个存储单

元存放一个字节型数据(8位),一个字占两个字节即 16位,存放在两个相邻的存 储单元中,高字节存放在高地址单元,低字节存放在低地址单元。且每个存储单元 都有一个20位的地址,这 1 M 个存储单元对应的地址为 OOOOOH-FFFFFH

19.保护断点和现场。此为堆栈的主要功能。

1M 个存储单元进行访问。每个存储单

16位,每个存储单元都有 00000H — FFFFFH ( 0 —

(SS): (SP) 2000: 0000 2000: 0001 2000 2000 2000 2000 2000 2000 2000 2000 2000: 0100 X X

X X

X X XX X X X X X X X X

X X X X

00F8 00F9 .堆栈段

00FA 00FB 00FC 00FD 00FE 00FF (a)堆栈空 (S P)= 0100H

"栈底

(AX),

4AC7H

X X X X

X X XX

1FH 2BH

8FH A2H

C7H 4AH

栈顶

栈底

(SP): 00FAH

A 28X

)

^

2BX)^

XX 1

XX

XX

XX

1FH 2BH 8FH A2H C7H 4AH

栈底

(SP)= 00FEH

2Zh-^(CX)

栈顶

(CX)

厂①

(b)执行 PUSH AX

PUSH BX PUSH CX

指令后

(c)执行 POP BX

POP CX

指令后

状态输出

BH^输出

地址输出

,数据输入1

厂

I

ALE

⑨

RD DEN

AD 15 ?AD 0 BHE / S 7

A 19冷6 ?A

16

/S

3

I ②

I ⑥

;④ i _⑧ 『\BH ^输出y 1② !⑦

\ I

—I —

DT / R

总线读周期的时序

ALE WR

DT / R-

DEN

存储器I/O 写周期的时序

ALE 地址锁存信号。

20. CPU 中BIU 单元的地址加法器根据指令中给出的段地址和段内偏移地址,通

过将段地址乘以 10H(16),即左移4位,再与段内偏移量相加得到一个 20位的物

理地址,该20位的物理地址加载到 20位的地址总线上,即可实现对 8086/8088系 统1 M 个

存储单元的访问。

21.数据传送指令 MOV 。指令格式及操作:

MOV dst , src ; (dst) J (src) dst 表

示目的操作数,src 表示源操作数 指令格式及操作:

;(SP)J(SP)-2, ((SP)+1: (SP))J(src) 出栈指令POP 。指令格式及操作:

POP dest ; (dest)?((SP)+1: (SP)), (SP)J(SP)+2

ADD 加法,ADC 带进位位加,SUB 减,SBB 带进位位减,CMP 数据比较

22.过程调用指令 CALL(Call a procedure)

(1) 段内直接调用。指令格式及操作:

CALL near_proc ; (SP)?(SP)-2, ((SP)+1 : (SP))?(IP)

;(IP) J (IP)+disp

相对位移量disp 的范围为-32 768?+32 767,占2个字节,段内直接调用指令为 3

字节指令

(2) 段内间接调用。指令格式及操作:

7

[数据输入:

A 19

/S

6

!② !、 丄V 地-址输’出乂

AD 15 ?AD

指令格式中的 进

栈指令PUSH 。 PUSH src

CALL reg16/mem16 ; (SP)J (SP)-2 , ((SP)+1 : (SP))J (IP)

;(IP) J(reg16)/(mem16)

指令的操作数是一个 16位的寄存器或存储器,其中的内容是一个近过程的入口

地址。

(3) 段间直接调用。指令格式及操作:

CALL far_proc ; (SP)J (SP)-2, ((SP)+1 : (SP))J (CS)

;(CS) J SEG far_proc

;(SP)J (SP)-2, ((SP)+1: (SP))J (IP) ;(IP) J OFFSET far_proc

(4) 段间间接调用。指令格式及操作: CALL

mem32 ; (SP)J(SP)-2, ((SP)+1 : (SP)) J (CS) ;(CS) J (mem32+2)

;(SP)J (SP)-2, ((SP)+1: (SP))J (IP) ;(IP) J (mem32)

(IP)J((SP)+1 : (SP)), (SP(SP)+2 ;(IP) J ((SP)+1: (SP)), (SP 片(SP)+2

(SP) J (SP)+pop_value 2)从远过程返回:

RET ; (IP) J ((SP)+1: (SP)), ;(CS) J ((SP)+1:

RET pop_value ; (IP) J ((SP)+1:

;(CS) J ((SP)+1:

;(SP)J(SP)+pop_value RET 指令还允许带一个弹出值

(pop_value),这是一个范围为 0?64 K 的立即数,通 常是偶数。弹出值表示返回时从堆栈

中舍弃的字节数。

23.过程返回指令 RET

指令格式及操作:

1)从近过程返回: RET

RET po p_value

(SP (SP )+2 (SP (SP)+2 (SP (SP)+2

(SP (SP)+2

(SP)), (SP)),

24. DB 字节型,每个元素占一个存储单元

DW 字型,每个元素占两个存储单元

25. 段定义伪指令

27. 中断源

1)中断向量,

向量地址=向量表的首地址+中断类型码X 4

对于8086CPU 中断类型号有 256,中断向量表占用 256X 4=1KB

字节

字节数

地址

低字节 1 IP 高字节 1 低字节 1 CS

高字节 1

(1) 外部硬件中断

外部硬件中断是指中断源是外部硬电路,通过 提出中断请求

可屏蔽中断INTR ,受CPU 内标志寄存器中IF 位的屏蔽。 非屏蔽中断NMI ,不受IF 位的屏蔽,CPU 必须响应。

CPU 每执行完一条指令,就会检测

NMI 和INTR 引脚上有无中断请求。

(2) 内部异常中断

内部异常中断是指 CPU 内部正在执行的过程中发生异常情况,如除法操作时结果太 大。

(3) 中断优先顺序 ①

除法出错中断,溢出中断,INT n ,?…②NM ③INTR ④单步中断

段名SEGMENT 段名ENDS

ASSUME

段寄存器名:段名

功能:定义一个逻辑段 功能:明确段与段寄存器的关系

CPU 的NMI 弓I 脚或INTR 弓I 脚向CPU

26.随机存取存储器RAM 。只读存储器ROM 。

I/O 接口的基本结构