8选1数据选择器74LS151

创作编号:

GB8878185555334563BT9125XW

创作者:凤呜大王*

8选1数据选择器74LS151

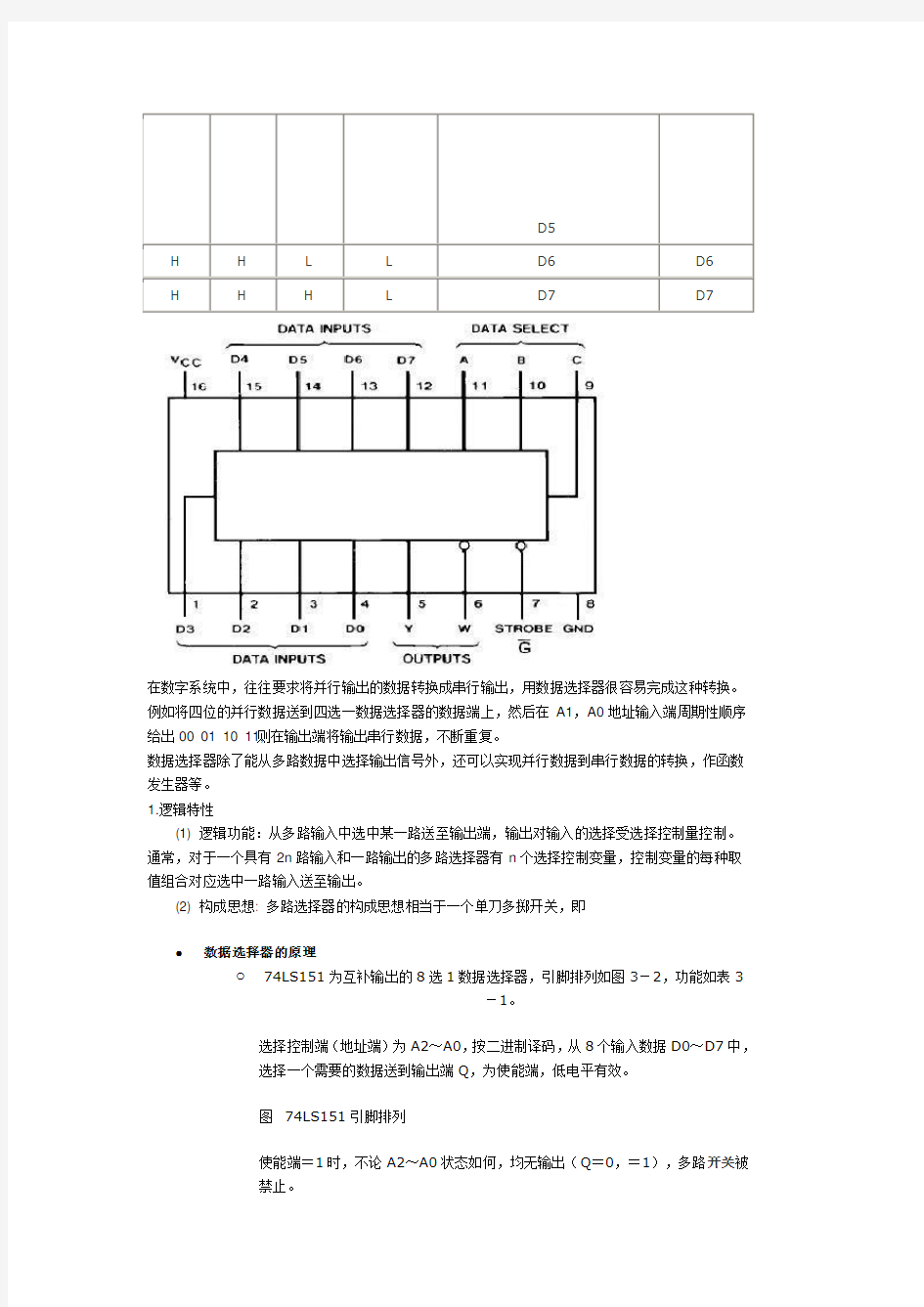

74LS151为互补输出的8选1数据选择器,引脚排列如图所示,功能见表。

选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。

(1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。838电子

(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。

如:CBA=000,则选择D0数据到输出端,即Y=D0。新艺图库

如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。工作原理ab126计算公式大全74LS151功能表:

D5

H H L L D6 D6

H H H L D7 D7

在数字系统中,往往要求将并行输出的数据转换成串行输出,用数据选择器很容易完成这种转换。例如将四位的并行数据送到四选一数据选择器的数据端上,然后在A1,A0地址输入端周期性顺序给出00 01 10 11,则在输出端将输出串行数据,不断重复。

数据选择器除了能从多路数据中选择输出信号外,还可以实现并行数据到串行数据的转换,作函数发生器等。

1.逻辑特性

(1) 逻辑功能:从多路输入中选中某一路送至输出端,输出对输入的选择受选择控制量控制。通常,对于一个具有2n路输入和一路输出的多路选择器有n个选择控制变量,控制变量的每种取值组合对应选中一路输入送至输出。

(2) 构成思想: 多路选择器的构成思想相当于一个单刀多掷开关,即

?数据选择器的原理

o74LS151为互补输出的8选1数据选择器,引脚排列如图3-2,功能如表3

-1。

选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,

选择一个需要的数据送到输出端Q,为使能端,低电平有效。

图74LS151引脚排列

使能端=1时,不论A2~A0状态如何,均无输出(Q=0,=1),多路开关被

禁止。

1)使能端=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择

D0~D7中某一个通道的数据输送到输出端Q。

如:A2A1A0=000,则选择D0数据到输出端,即Q=D0。

如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推。

数据选择器的定义及功能

数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。实现数据选择功能的逻辑电路称为数据选择器。它的作用相当于多个输入的单刀多掷开关,其示意图如下所示。

下面以4选1数据选择器为例,说明工作原理及基本功能。其逻辑图为:

功能表为:

为了对4个数据源进行选择,使用两位地址码BA产生4个地址信号。由BA等于00、01、10、11分别控制四个与门的开闭。显然,任何时候BA只有一种可能的取值,所以只有一个与门打开,使对应的那一路数据通过,送达Y端。输入使能端G是低电平有效,当G=1时,所有与门都被封锁,无论地址码是什么,Y总是等于0;当G=0时

,封锁解除,由地址码决定哪一个与门打开。

同样原理,可以构成更多输入通道的数据选择器。被选数据源越多,所需地址码的位数也越多,若地址输入端为N,可选输入通道数为2n。

二、集成电路数据选择器

1.74LS151集成电路数据选择器的功能

74LS151是一种典型的集成电路数据选择器,它有3个地址输入端CBA,可选择D0~D7 8个数据源,具有两个互补输出端,同相输出端Y和反相输出端W。其逻辑图和引脚图分别如下所示:由逻辑图可知,该逻辑电路的基本结构为“与一或一非”形式。输入使能G为低电平有效。输出Y的表达式为: 式中

。Mi为CBA的最小项。例如,当CBA=010时,根据最小项性质,只有M2为1,其余各项为0,故得Y=D2,即只有D2传送到输出端。

上面所讨论的是1位数据选择器,如需要选择多位数据时,可由几个1位数据选择器并联组成,即将它们的使能端连在一起,相应的选择输入端连在一起。2位8选1数据选择器的连接方法如下图所示

。当需要进一步扩充位数时,只需相应地增加器件的数目。

可以把数据选择器的使能端作为地址选择输入,将两片74LS151连接成一个16选1的数据选择器,其连接方式如下图所示。16选16选1的数据选择器的地址选择输入有4为4位,其最高位D与一个8选1数据选择器的使能端连接,经过一反相器反相后与零一另一个数据选择器的使能端连接。低3位地址选择输入端CBA由两片74LS151的地址选择输入端相对应连接而成。

2.数据选择器的应用

数据选择器除实现有选择的传送数据外,还有其他用途,下面介绍几种典型应用。

(1)逻辑函数产生器

从74LS151得逻辑图可以看出,当使能端G=0时,Y是C、B、A和输入数据D0~D7的与或函数,它的表达式可以写成

式中mi是C、B、A构成的最小项。显然。当Di=1时,其对应的最小项mi在与或表达式中出现,当Di=0时,对应的最小项就不出现。利用这一点,不难实现组合逻辑函数。

已知逻辑函数,利用数据选择器构成函数产生器的过程是,将函数变换成最小项表达式,根据最小项表达式确定各数据输入端的二元常量。将数据选择器的地址信号C、B、A作为函数的输入

变量,数据输入D0~D7,作为控制信号,控制各最小项在输出逻辑函数中是否出现,使能端G始终保持低电平,这样8选1数据选择器就成为一个3变量的函数产生器。

例1 试用8选1数据选择器74LS151产生逻辑函数

解:把式变换成最小项表达式:

显然D3、D5、D6、D7,都应该等于1,而式中没有出现的最小项m0,m1,m2,m4的控制变量D0、D1、D2、D4都应该等于0,由此可画出该逻辑函数产生器的逻辑图:、例2 试用与上例相同的8选1数据选择器产生

解:根据表达式列出真值表如下:

从表中可以看出,凡使L值为1的那些最小项,其控制变量应该等于1,即D1、D2、D4、D7等于1(对应XYZ:001、010、100、111),其他控制变量均等于0。由此可得逻辑函数产生器:通过上面两例可以看出,与用各种逻辑门设计组合逻辑电路相比

,使用数据选择器的好处是无需对函数化简。

(2)实现并行数据到串行数据的转换

上图是实现并/串行转换的电路框图和输出信号时序图。

电路由8选1数据选择器和1个3位二进制计数器构成。计数器的作用是累计时钟脉冲的个数,当时钟脉冲CP一个接一个送入时,计数器的输出端Q2Q1Q0从000→001→010→…→111依次变化。由于Q2Q1Q0与选择器的地址输入端C、B、A相连,因此C、B、A就随时钟脉冲的逐个输入从000到111变化,选择器的输出Y随之接通D0、D1、D2

、…Dn。当选择器的数据输入端D0~D7与一个并行8位数01001101相连时,输出端得到的就是一串随时钟节拍变化的数据0-1-0-0

-1-1-0-1,这种数称为串行数据。为了简单起见,图中时序图的时钟脉冲CP画成了尖窄脉冲。

创作编号:

GB8878185555334563BT9125XW

创作者:凤呜大王*