完整word版,Quartus下载程序到fpga开发板的教程(张显编)

Quartus下载程序到fpga开发板的教程

——————笔者:张显

第一篇

一.建quartus软件工程

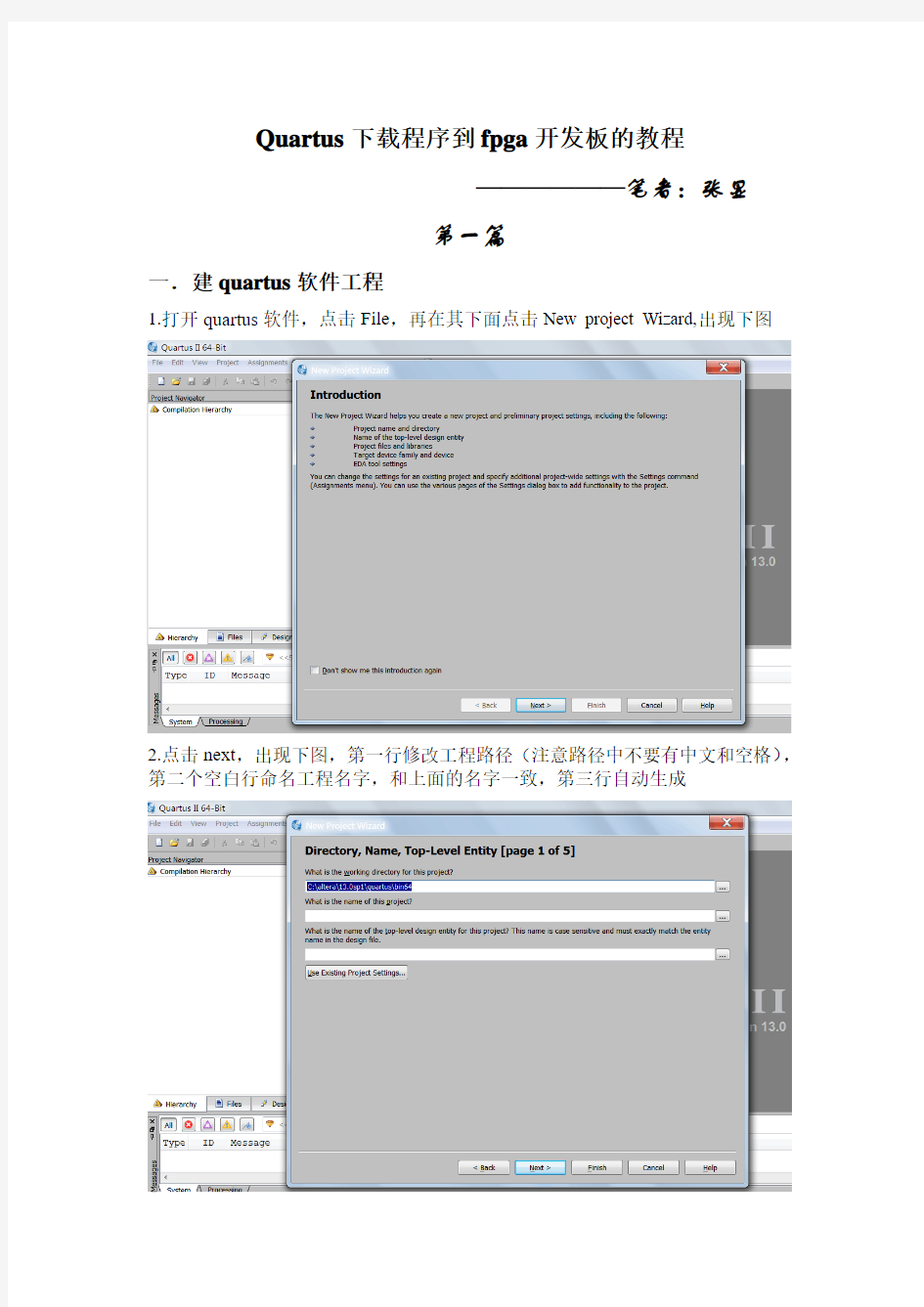

1.打开quartus软件,点击File,再在其下面点击New project Wizard,出现下图

2.点击next,出现下图,第一行修改工程路径(注意路径中不要有中文和空格),第二个空白行命名工程名字,和上面的名字一致,第三行自动生成

3.点击next,出现下图,不做改动

4.继续点next就行,有

选择device family系列,再选择芯片类型5.点next,有下图

6.再点击next则有

7.点击finish即完成工程的建立

二.在存在原代码的情况下,将原代码加入工程

1.按照刚才的路径查看所建的工程有:

2.打开原代码所在地(个体情况不一样,看自己的在哪)有以下

里面有2个文件夹很重要,就是source和tcl,source里面就是我们程序的源代码

3.将sourece 和tcl拷贝到刚才建立的那个工程文件夹下,结果如下

4.回到quartus软件中,点击project,在其下点击add files in project ,有

5.选中图中的3个.v文件,并点击打开,立即有

6.点击applay、再点OK即可

7.回到quartus软件中,点击红色file处,可以看到刚才添加的3个文件

8.选择顶层文件,根据所编代码模块,自行选择之一,上图中选择了mix模块,右键单击,并点击set as top level entity,之后就有,Hierarchy中显示的是mix模

块,说明顶层模块设置成功

1.点击红色处,之后单击Device,有

2.点击上图红色处Device and pin options,则有

3.点击configuration,按照下图红色处配置修改(EPCS64根据自身情况选择)

4.选择unused pins,如下

5.选择voltage,FPGA的I/O口是3.3v的TTL电平,选择它,有下:

6.把dual_purpose pin进行设置,双功能引脚都设置为普通的I/O口即可

1.进行编译,点击图中红色处,一个三角

2.编译后的结果,显示编译成功,同时会生成一个编译报告

上图编译报告会显示一些所用FPGA的资源

3.点击pin planner,则生成以下画面

4.进行引脚分配,在红色处逐一进行选择,双击原来空白处并下拉,关闭,在进行编译即可

五.下载程序

1.编译过后,点击红色处图标显示programmer,进入下载界面如下:

2.添加文件,编译后有2中文件,sof、pof文件2种,JTAG下载时用sof文件、AS下载使用pof文件,用JTAG下载时,存在RAM里,一旦掉电程序会丢失,上电后要重新下载,用AS下载的话,则是固化了,掉电也不会丢失,一般编译

后,文件会自动加载,如没有,就点击下图红色处寻找,进行添加即可:

https://www.360docs.net/doc/e59812872.html,B下载器连上,电源线通上,按下开关,点击旁侧的start,进行下载

看到右上方显示绿色进度条为100%,说明下载成功4.实验现象以及开发板图

5.

第二篇(简洁版)

1.在某个路径下创建一个文件,做为工程文件的路径,命名

2.在Quartus中先创建一个文件File,把file另存为上面那个工程文件路径下,在新建的verilog HDL文件中编写好所需程序,然后保存,注意文件名要和module后的文件名一致,如果不一致就会导致出错这时会跳出一个对话框,问要不要为这个文件创建工程,点击是的,

3.开始工程的创建,关于工程创建,参考上一篇第一部分

4.之后进行第三部分,工程的其余设置,参考上篇

5.编译,,分配引脚,下载程序,参考上篇

AS下载,请参照《FPGA-AS_下载使用说明书》这个文档,一定要

注意,软件配置好以后,硬件的接口一定也变成AS下载接口!!

Quartus2原理图输入法

Quartus2原理图输入法(上机实训) 一、实验目的 1.熟悉Quartus2的使用方法。 2.熟悉Quartus2原理图输入法的全过程。 二 、实验设备: 1. 计算机 2. Quartus Ⅱ软件 三、实验原理 1位全加器可以用两个半加器及一个或门连接而成,半加器原理图的设计方 法很多,我们用一个与门、一个非门和同或门(xnor 为同或符合,相同为1,不 同为0)来实现。先设计底层文件:半加器,再设计顶层文件全加器。 (1) 半加器的设计: 半加器表达式:进位:co=a and b 和:so=a xnor ( not b ) 半加器原理图如下: (2) 全加器的设计: 全加器原理图如下: 四、实验内容 1.用逻辑门设计实现一个半加器,仿真验证其功能,并生成新的半加器图形模块单元。 2.用实验内容1中生成的半加器模块和逻辑门设计实现一个全加器,仿真验证其功能。 3.用D 触发器设计一个四位可以自启动的环形计数器,仿真验证其功能。 五、实验步骤参考 1、设计思路和过程 I113ain cout cout ain bin sum cin bin sum cin f_adder or2a f e d u3 u2 u1 b a c co so B co so B h_adder A h_adder A I113co a so b 1 0101 0110001 10 0co so b a not xnor2 and2

(1)半加器的设计:通过对半加器的逻辑功能的分析可以知道,半加器完成2进制加法并有进位功能,因此使用与门和异或门即可完成逻辑功能。 打开Quartus2并创建工程文件后,添加与门和异或门,2个输入端,2个输 出端,并连线,即完成半加器的电路设计。 (2)全加器的设计:通过对全加器的逻辑功能的分析可以知道,全加器完成带有后位进位的2进制加法并向前进位,因此用(1)中的2个半加器和一个或门 就可以完成该逻辑功能。即完成3个2进制数的相加,一个半加器的其中一 个输入端借另一个的S输出端,该半加器的S输出端即为全加器的S输出端。 2个半加器的CO进位端进行或运算后的输出即为全加器的CO输出。 (3)环形计数器的设计:通过对环形计数器的逻辑功能的分析可以知道,该环形计数器完成4位循环计数,并可以自启动。因此需要4个D触发器,4个D 触发器依次想连并且第一第二第三个D触发器的输出进行或非运算后接入第 一个D触发器的输入端,即可完成自启动的计数功能,CP时钟脉冲接入每 个触发器即完成电路设计。 2、实验原理图 半加器原理图 全加器原理图

Quartus简明操作指南修

Quartus II简明操作指南 在前面的实验里,我们所有的实验都是基于这样一个观点,即将一个数字系统划分成合适利用已有的中小规模数字集成电路的功能的模块,然后将这些集成电路通过外部引线连接起来。现在开始我们将研究用可编程逻辑器件(PLD/FPGA)来进行数字系统设计。 可编程逻辑器件是一种大规模的集成电路,其内部预置了大量易于实现各种逻辑函数的结构,同时还有一些用来保持信息或控制连接的特殊结构,这些保持的信息或连接确定了器件实现的实际逻辑功能,当改变这些信息或连接时器件的功能也将随之改变。可编程逻辑器件的设计过程和传统的中小规模数字电路设计也不一样,可编程数字系统,无论是CPLD 还是FPGA器件都需要利用软件工具来进行设计。可编程数字系统设计总体上一般可以分为设计输入、项目处理、设计校验和器件编程这四个主要过程。下面我们将一个简单的模60BCD计数器为例,说明可编程数字系统设计的基本流程、概念和方法,掌握Quartus II 软件的基本功能和操作,了解原理图输入方式的设计全过程。 一、设计项目输入 设计输入是设计者对系统要实现的逻辑功能进行描述的过程。设计输入有多种表达方式,本次我们主要学习图形输入法。 1.1 建立工程项目 1.打开Quartus II,在File菜单中选择New Project Wizard项,将出现工程项目建立向导对 话框。 2.点击“Next”,进入到相应的对话框,在最上面的文本输入框中输入项目所在的目录名(注 意:不能用中文名,下同),在中间的文本输入框中输入项目名称,在最下面的文本输入框中输入最顶层模块的名称。 3.点击“Next”,进入到设计文件选择对话框,由于在本例中还没有任何设计文件,所以不 选择任何文件。 4.点击“Next”,进入到器件选择对话框,在“Family”下拉菜单中选择“Cyclone”,在“Available Devices”列表栏中选择“EP1C6Q240C8”。 5.点击“Next”进入到第三方EDA工具选择对话框,在这个界面我们可以选择第三方的综 合工具、仿真工具和时延分析工具。由于在本例中我们的综合、仿真和时延分析都采用Quartus II内置的工具,所以在这个页面不作任何选择。 6.点击“Next”进入到“Summary”对话框,在这个窗口列出了前面所作设置的全部信息。 点击“Finish”完成工程项目建立过程,回到主窗口。 1.2 建立原理图输入文件 在Quartus II中我们可以利用Block Editor以原理图的形式进行设计输入和编辑。Block Editor 可以读取并编辑后缀名为”.bdf”的原理图设计文件以及在MAX+PLUS II 中建立的后缀为”.gdf”的原理图输入文件。 1.在File菜单中选择New项,将出现新建文件对话框。选择“Device Design File/Block

QuartusII原理图---输入篇

QuartusII的使用:原理图输入篇 QuartusII是MaxplusII的升级版,其功能比MaxplusII更加强大,主要是增加了与其它EDA工具(仿真、综合等工具)的接口,另外它具有更强大的时序分析、时序优化等功能。这里主要介绍QuartusII的基本功能与使用方法: 1.新建一个文件夹作为工程项目目录,注意此目录不能为根目录,不能用中文命名。 2.为设计建立项目及文件 (1)建立项目(或工程project)在file下选择new project wizard(左下图),在弹出的 窗口中第一个空格框内选择该项目存放的路径(即第1步所建立的项目目录的路 名称(右下图,注意项目名称 一定不能为中文,只能为英文, 比如可取名为myproject),完 成后点击finish。 (2)建立原理图文件 执行File—New,选择Block Diagram/Schematic File,执行File—Save as命令,给 文件取名,文件名同样用英文命名,文件名的后缀为.bdf,将Add file to current project选项选中,使得该文件添加到刚建立的工程中去。 3.建立原理图文件 (1)编辑输入原理图文件 在原理图编辑区的一个位置双击鼠标的左键,将弹出Symbol对话框,或单击鼠标右键在弹出的选择对话框中选择Insert—Symbol,也会弹出Symbol对话框。用单击的方法展开Liabraries栏中的元件库,其中Primitives为基本元件库,打开Logic子库,里面是常用 的与门、或门和非门等门电路。选中要用的元件,点击OK按钮,将该图样移动到编辑区合