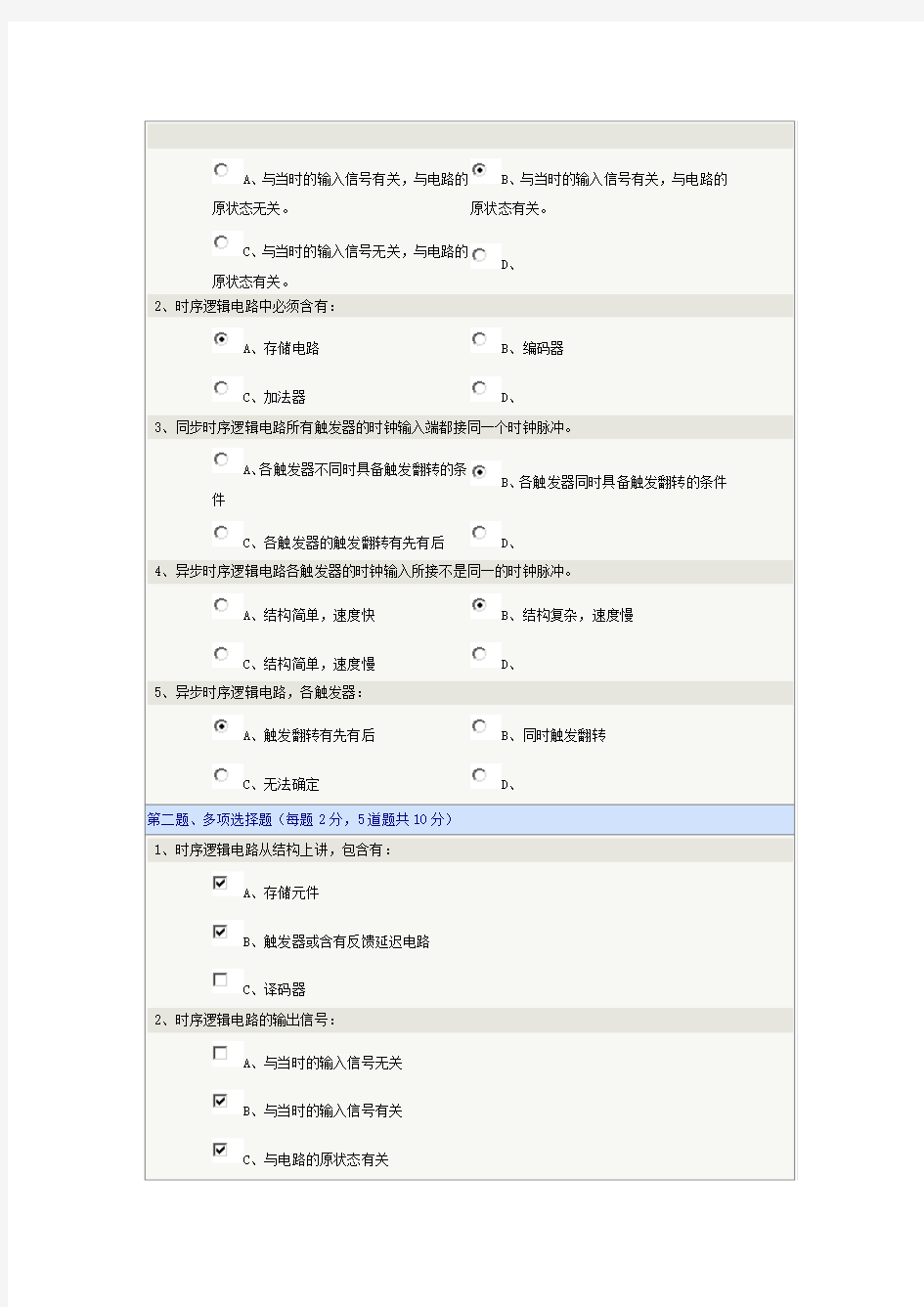

时序逻辑电路的分析

A、与当时的输入信号有关,与电路的原状态无关。

B、与当时的输入信号有关,与电路的原状态有关。

C、与当时的输入信号无关,与电路的

原状态有关。

D、

2、时序逻辑电路中必须含有:

A、存储电路

B、编码器

C、加法器

D、

3、同步时序逻辑电路所有触发器的时钟输入端都接同一个时钟脉冲。

A、各触发器不同时具备触发翻转的条

件

B、各触发器同时具备触发翻转的条件

C、各触发器的触发翻转有先有后

D、

4、异步时序逻辑电路各触发器的时钟输入所接不是同一的时钟脉冲。

A、结构简单,速度快

B、结构复杂,速度慢

C、结构简单,速度慢

D、

5、异步时序逻辑电路,各触发器:

A、触发翻转有先有后

B、同时触发翻转

C、无法确定

D、

第二题、多项选择题(每题2分,5道题共10分)

1、时序逻辑电路从结构上讲,包含有:

A、存储元件

B、触发器或含有反馈延迟电路

C、译码器

2、时序逻辑电路的输出信号:

A、与当时的输入信号无关

B、与当时的输入信号有关

C、与电路的原状态有关

D、与电路的原状态无关

3、同步时序逻辑电路:

A、所有触发器的时钟输入端都接同一个时钟脉冲

B、各触发器同时具备触发翻转的条件

C、速度快;结构简单

D、速度快;结构复杂

4、时序逻辑电路的逻辑功能可用()来描述。

A、状态方程

B、状态表

C、状态图

D、时序图

5、时序逻辑电路的分析是指已知逻辑图:

A、列写逻辑方程式

B、计算状态表

C、画电路的状态图

D、画电路的时序图

E、判定电路的功能

第三题、判断题(每题1分,5道题共5分)

1、时序逻辑电路中必须含有存储电路。

正确错误

2、时序逻辑电路中的存储电路只能用延迟元件组成,不能用触发器构成。

正确错误

3、同步时序逻辑电路各触发器同时具备触发翻转的条件。

正确错误

4、异步时序逻辑电路结构简单,速度慢。

正确错误

、时序逻辑电路的输出信号只与当时的输入信号有关,与电路的原状态无关。

正确错误

时序逻辑电路的分析方法

7.2 时序逻辑电路的分析方法 时序逻辑电路的分析:根据给定的电路,写出它的方程、列出状态转换真值表、画出状态转换图和时序图,而后得出它的功能。 7.2.1同步时序逻辑电路的分析方法 同步时序逻辑电路的主要特点:在同步时序逻辑电路中,由于所有触发器都由同一个时钟脉冲信号CP来触发,它只控制触发器的翻转时刻,而对触发器翻转到何种状态并无影响,所以,在分析同步时序逻辑电路时,可以不考虑时钟条件。 1、基本分析步骤 1)写方程式: 输出方程:时序逻辑电路的输出逻辑表达式,它通常为现态和输入信号的函数。 驱动方程:各触发器输入端的逻辑表达式。 状态方程:将驱动方程代入相应触发器的特性方程中,便得到该触发器的状态方程。 2)列状态转换真值表: 将电路现态的各种取值代入状态方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。如现态的起始值已给定时,则从给定值开始计算。如没有给定时,则可设定一个现态起始值依次进行计算。 3)逻辑功能的说明: 根据状态转换真值表来说明电路的逻辑功能。 4)画状态转换图和时序图: 状态转换图:是指电路由现态转换到次态的示意图。 时序图:是在时钟脉冲CP作用下,各触发器状态变化的波形图。 5)检验电路能否自启动 关于电路的自启动问题和检验方法,在下例中得到说明。

2、分析举例 例、试分析下图所示电路的逻辑功能,并画出状态转换图和时序图。 解:由上图所示电路可看出,时钟脉冲CP加在每个触发器的时钟脉冲输入端上。因此,它是一个同步时序逻辑电路,时钟方程可以不写。 ①写方程式: 输出方程: 驱动方程: 状态方程: ②列状态转换真值表: 状态转换真值表的作法是: 从第一个现态“000”开始,代入状态方程,得次态为“001”,代入输出方程,得输出为“0”。 把得出的次态“001”作为下一轮计算的“现态”,继续计算下一轮的次态值和输出值。

时序逻辑电路的组成及分析方法案例说明

时序逻辑电路的组成及分析方法案例说明 一、时序逻辑电路的组成 时序逻辑电路由组合逻辑电路和存储电路两部分组成,结构框图如图5-1所示。图中外部输入信号用X (x 1,x 2,… ,x n )表示;电路的输出信号用Y (y 1,y 2,… ,y m )表示;存储电路的输入信号用Z (z 1,z 2,… ,z k )表示;存储电路的输出信号和组合逻辑电路的内部输入信号用Q (q 1,q 2,… ,q j )表示。 x x y 1 y m 图8.38 时序逻辑电路的结构框图 可见,为了实现时序逻辑电路的逻辑功能,电路中必须包含存储电路,而且存储电路的输出还必须反馈到输入端,与外部输入信号一起决定电路的输出状态。存储电路通常由触发器组成。 2、时序逻辑电路逻辑功能的描述方法 用于描述触发器逻辑功能的各种方法,一般也适用于描述时序逻辑电路的逻辑功能,主要有以下几种。 (1)逻辑表达式 图8.3中的几种信号之间的逻辑关系可用下列逻辑表达式来描述: Y =F (X ,Q n ) Z =G (X ,Q n ) Q n +1=H (Z ,Q n ) 它们依次为输出方程、状态方程和存储电路的驱动方程。由逻辑表达式可见电路的输出Y 不仅与当时的输入X 有关,而且与存储电路的状态Q n 有关。 (2)状态转换真值表 状态转换真值表反映了时序逻辑电路的输出Y 、次态Q n +1与其输入X 、现态Q n 的对应关系,又称状态转换表。状态转换表可由逻辑表达式获得。 (3)状态转换图

状态转换图又称状态图,是状态转换表的图形表示,它反映了时序逻辑电路状态的转换与输入、输出取值的规律。 (4)波形图 波形图又称为时序图,是电路在时钟脉冲序列CP的作用下,电路的状态、输出随时间变化的波形。应用波形图,便于通过实验的方法检查时序逻辑电路的逻辑功能。 二、时序逻辑电路的分析方法 1.时序逻辑电路的分类 时序逻辑电路按存储电路中的触发器是否同时动作分为同步时序逻辑电路和异步时序逻辑电路两种。在同步时序逻辑电路中,所有的触发器都由同一个时钟脉冲CP控制,状态变化同时进行。而在异步时序逻辑电路中,各触发器没有统一的时钟脉冲信号,状态变化不是同时发生的,而是有先有后。 2.时序逻辑电路的分析步骤 分析时序逻辑电路就是找出给定时序逻辑电路的逻辑功能和工作特点。分析同步时序逻辑电路时可不考虑时钟,分析步骤如下: (1)根据给定电路写出其时钟方程、驱动方程、输出方程; (2)将各驱动方程代入相应触发器的特性方程,得出与电路相一致的状态方程。 (3)进行状态计算。把电路的输入和现态各种可能取值组合代入状态方程和输出方程进行计算,得到相应的次态和输出。 (4)列状态转换表。画状态图或时序图。 (5)用文字描述电路的逻辑功能。 3.案例分析 分析图8.39所示时序逻辑电路的逻辑功能。 图8.39 逻辑电路 解:该时序电路的存储电路由一个主从JK触发器和一个T触发器构成,受统一的时钟CP控制,为同步时序逻辑电路。T触发器T端悬空相当于置1。 (1)列逻辑表达式。 输出方程及触发器的驱动方程分别为

Moore型同步时序逻辑电路的设计与分析

实验九Moore型同步时序逻辑电路的分析与设计 22920132203686 薛清文周2下午实验 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.D,JK触发器的特性机器检测方法。 2.掌握时序逻辑电路的测试方法。 3.了解时序电路自启动设计方法。 4.了解同步时序电路状态编码对电路优化作用。 二.实验原理: 二、 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 实验十Moore型同步时序逻辑电路的分析与设计 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.掌握时序逻辑电路的测试方法。 二.实验原理: 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 (7)利用卡诺图如图2,求状态方程、驱动方程。 (8)自启动检验:将各无效状态代入状态方程,分析状态转换情况,画出完整的 状态转换图,如图3所示,检查是否能自启动。 时序逻辑电路的分析方法 时序逻辑电路的分析:根据给定的电路,写出它的方程、列出状态转换真值表、画出状态转换图和时序图,而后得出它的功能。 同步时序逻辑电路的分析方法 同步时序逻辑电路的主要特点:在同步时序逻辑电路中,由于所有触发器都由同一个时钟脉冲信号CP来触发,它只控制触发器的翻转时刻,而对触发器翻转到何种状态并无影响,所以,在分析同步时序逻辑电路时,可以不考虑时钟条件。 1、基本分析步骤 1)写方程式: 输出方程:时序逻辑电路的输出逻辑表达式,它通常为现态和输入信号的函数。 驱动方程:各触发器输入端的逻辑表达式。 状态方程:将驱动方程代入相应触发器的特性方程中,便得到该触发器的状态方程。 2)列状态转换真值表: 将电路现态的各种取值代入状态方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。如现态的起始值已给定时,则从给定值开始计算。如没有给定时,则可设定一个现态起始值依次进行计算。 3)逻辑功能的说明: 根据状态转换真值表来说明电路的逻辑功能。 4)画状态转换图和时序图: 状态转换图:是指电路由现态转换到次态的示意图。 时序图:是在时钟脉冲CP作用下,各触发器状态变化的波形图。 5)检验电路能否自启动 关于电路的自启动问题和检验方法,在下例中得到说明。 2、分析举例 例、试分析下图所示电路的逻辑功能,并画出状态转换图和时序图。 解:由上图所示电路可看出,时钟脉冲CP加在每个触发器的时钟脉冲输入端上。因此,它是一个同步时序逻辑电路,时钟方程可以不写。 ①写方程式: 输出方程: 驱动方程: 状态方程: ②列状态转换真值表: 状态转换真值表的作法是: 从第一个现态“000”开始,代入状态方程,得次态为“001”,代入输出方程,得输出为“0”。 《时序逻辑电路》练习题及答案 []分析图P6-1 时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 图P6-1 [解] 驱动方程:3 1 1 Q K J= =,状态方程:n n n n n n n Q Q Q Q Q Q Q 1 3 1 3 1 3 1 1 ⊕ = + = + ; 1 2 2 Q K J= =,n n n n n n n Q Q Q Q Q Q Q 1 2 2 1 2 1 1 2 ⊕ = + = + ; # 3 3 2 1 3 Q K Q Q J= =,,n n n n Q Q Q Q 1 2 3 1 3 = + ; 输出方程:3 Q Y= 由状态方程可得状态转换表,如表6-1所示;由状态转换表可得状态转换图,如图A6-1所示。电路可以自启动。 表6-1 n n n Q Q Q 1 2 3 Y Q Q Q n n n1 1 1 2 1 3 + + +n n n Q Q Q 1 2 3 , Y Q Q Q n n n1 1 1 2 1 3 + + + 000 001 010 011 0010 0100 0110 — 1000 100 101 110 111 0001 0111 0101 ; 0011 图A6-1 电路的逻辑功能:是一个五进制计数器,计数顺序是从0到4循环。 []试分析图P6-2时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。A为输入逻辑变量。 # 图P6-2 [解] 驱动方程:2 1 Q A D=, 2 1 2 Q Q A D= 状态方程: n n Q A Q 2 1 1 = + , ) ( 1 2 2 1 1 2 n n n n n Q Q A Q Q A Q+ = = + 输出方程:2 1 Q Q A Y=表6-2 @ 由状态方程可得状态转换表,如表6-2所示;由状态转换表 可得状态转换图,如图A6-2所示。 电路的逻辑功能是:判断A是否连续输入四个和四个以上 “1”信号,是则Y=1,否则Y=0。 图A6-2 []试分析图P6-3时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,检查电路能否自启动。 、 图P6-3 [解] 3 2 1 Q Q J=,1 1 = K; 1 2 Q J=, 3 1 2 Q Q K=; 2 3 2 1 3 Q K Q Q J= =, = +1 1 n Q 3 2 Q Q· 1 Q; 2 1 1 2 Q Q Q n= + +2 3 1 Q Q Q; 3 2 3 2 1 1 3 Q Q Q Q Q Q n+ = + Y = 3 2 Q Q 电路的状态转换图如图A6-3所示,电路能够自启动。 ' 图A6-3 n n Q AQ 1 2 Y Q Q n n1 1 1 2 + + 000 < 001 010 011 100 111 110 101 010 $ 100 110 001 111 100 010 000 第六章 时序逻辑电路 【题 】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 Y 图P6.3 【解】驱动方程: 11323131233 J =K =Q J =K =Q J =Q Q ;K =Q ?? ??? 输出方程:3Y Q = 将驱动方程带入JK 触发器的特性方程后得到 状态方程为: n+11313131n 1 2121221n+1 3321 Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q +?=+=?=+=⊕??=?e 电路能自启动。状态转换图如图 【题 】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图。A 为输入逻辑变量。 图A6.3 Y 图P6.5 【解】 驱动方程: 12 21212() D AQ D AQ Q A Q Q ?=??==+?? 输出方程: 21Y AQ Q = 将驱动方程带入JK 触发器的特性方程后得到状态方程为: n+1 12 n+1 212() Q AQ Q A Q Q ?=??=+?? 电路的状态转换图如图 1 图A6.5 【题 】 分析图时序电路的逻辑功能,画出电路的状态转换图,检查电路能否自启动,说明电路能否自启动。说明电路实现的功能。A 为输入变量。 A Y 图P6.6 【解】驱动方程: 11221 1 J K J K A Q ==?? ==⊕? 输出方程: 1212Y AQ Q AQ Q =+ 将驱动方程带入JK 触发器的特性方程后得到状态方程为: n+111 n+1 2 12 Q Q Q A Q Q ?=??=⊕⊕?? 电路状态转换图如图。A =0时作二进制加法计数,A =1时作二进制减法计数。 01图A6.6 【题 】 分析图时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图,说明电路能否自启动。 A、与当时的输入信号有关,与电路的原状态无关。 B、与当时的输入信号有关,与电路的原状态有关。 C、与当时的输入信号无关,与电路的 原状态有关。 D、 2、时序逻辑电路中必须含有: A、存储电路 B、编码器 C、加法器 D、 3、同步时序逻辑电路所有触发器的时钟输入端都接同一个时钟脉冲。 A、各触发器不同时具备触发翻转的条 件 B、各触发器同时具备触发翻转的条件 C、各触发器的触发翻转有先有后 D、 4、异步时序逻辑电路各触发器的时钟输入所接不是同一的时钟脉冲。 A、结构简单,速度快 B、结构复杂,速度慢 C、结构简单,速度慢 D、 5、异步时序逻辑电路,各触发器: A、触发翻转有先有后 B、同时触发翻转 C、无法确定 D、 第二题、多项选择题(每题2分,5道题共10分) 1、时序逻辑电路从结构上讲,包含有: A、存储元件 B、触发器或含有反馈延迟电路 C、译码器 2、时序逻辑电路的输出信号: A、与当时的输入信号无关 B、与当时的输入信号有关 C、与电路的原状态有关 D、与电路的原状态无关 3、同步时序逻辑电路: A、所有触发器的时钟输入端都接同一个时钟脉冲 B、各触发器同时具备触发翻转的条件 C、速度快;结构简单 D、速度快;结构复杂 4、时序逻辑电路的逻辑功能可用()来描述。 A、状态方程 B、状态表 C、状态图 D、时序图 5、时序逻辑电路的分析是指已知逻辑图: A、列写逻辑方程式 B、计算状态表 C、画电路的状态图 D、画电路的时序图 E、判定电路的功能 第三题、判断题(每题1分,5道题共5分) 1、时序逻辑电路中必须含有存储电路。 正确错误 2、时序逻辑电路中的存储电路只能用延迟元件组成,不能用触发器构成。 正确错误 3、同步时序逻辑电路各触发器同时具备触发翻转的条件。 正确错误 4、异步时序逻辑电路结构简单,速度慢。 时序逻辑电路分析例题 1、分析下图时序逻辑电路。 解: 1、列出驱动方程:111==K J 1//122Q A AQ K J +== 2、列出状态方程: 将驱动方程代入JK 触发器的特性方程Q K JQ Q //*+=得: /1*1Q Q = 212/1//21//2/1*2Q AQ Q Q A Q Q A Q AQ Q +++= 3、列出输出方程: 21//2/1Q Q A Q AQ Y += 4、列出状态转换表: (1)当A=1时: 根据:/1*1Q Q =;21/2/1*2Q Q Q Q Q +=;/ 2 /1Q Q Y =得: (2)当A=0时: 根据:/1*1Q Q =;2/1/ 21*2Q Q Q Q Q +=;21Q Q Y =得: 5、画状态转换图: 6、说明电路实现的逻辑功能: 此电路是一个可逆4进制(二位二进制)计数器,CLK 是计数脉冲输入端,A 是加减控制端,Y 是进位和借位输出端。当控制输入端A 为低电平0时,对输入的脉冲进行加法计数,计满4个脉冲,Y 输出端输出一个高电平进位信号。当控制输入端A 为高电平1时,对输入的脉冲进行减法计数,计满4个脉冲,Y 输出端输出一个高电平借位信号。 2、如图所示时序逻辑电路,试写出驱动方程、状态方程,画出状态图,说明该电路的功能。 解:驱动方程 ?? ?=⊕=1010K Q X J n ???=⊕=11 1K Q X J n 状态方程 ()()n n n n n n n n n n n n n n Q XQ Q Q X Q Q X Q Q Q X Q Q X Q Q X Q 0 1010 1 10 01011011+=⊕=+=⊕=++ CP X Z实验十 Moore型同步时序逻辑电路的分析与设计

同步时序逻辑电路的分析方法

《时序逻辑电路》练习题及答案

时序逻辑电路课后答案

时序逻辑电路的分析

时序逻辑电路分析举例