FFT处理器寄生参数提取和静态时序分析(精)

FFT处理器寄生参数提取和静态时序分析

摘要:本文在简要介绍寄生参数提取工具Star-RCXT和静态时序分析工具PrimeTime的基础上,对已通过物理验证工具Calibre DRC和LVS的FFT处理器版图用Star-RCXT工具进行了基于CCI的寄生参数提取,得到内部互连网络的详细寄生电容和电阻值。最后,用 PrimeTime工具进行了精确的版图时序分析。

关键词:FFT处理器;Star_RCXT;寄生参数抽取;Primetime;静态时序分析

引言

对于应用0.18mm及以下工艺的设计而言,二维提取进行Sign-off静态时序分析就显得有些粗略,而且精度不够。这是因为对于0.18mm及以下工艺,毗邻金属连线所产生的耦合电容在设计中已经成为不得不考虑的寄生参数,于是先进的寄生参数提取工具就可以检测到相同层次之间产生耦合电容的影响。因此对0.18mm 及以下工艺的设计,通过物理验证,在进行流片之前,需要用专门的寄生参数抽取工具将每一个节点的RC网络信息写成文件传递给设计,即所谓的反标,再用静态时序分析工具做精确的版图时序分析。

Star-RCXT工具介绍

Star- RCXT以其高精度、友好的用户界面以及和其它工具良好的结合成为目前业界比较流行的一款寄生参数提取工具,是专门针对0.18mm及以下工艺的寄生参数提取所设计的。它采用了二点五维的几何提取技术,达到了三维的提取精度,但比三维的抽取工具速度快很多,能够快速准确地对上百万门的设计进行全局的寄生参数提取。

用Star-RCXT进行寄生参数提取的条件

应用Star-RCXT进行精细寄生参数提取,还需要两个与工艺参数有关的文件:mapping文件和ITF(Interconnect Technology Format)文件。ITF文件是由晶圆代工厂直接提供的,它包含的信息主要有:工艺采用的各个层次(包括电介质、过孔和金属导线等),各个层次在工艺流程中的厚度、宽度等物理尺寸,各个层次的电气参数(如介电常数、方块阻值等)。Star-RCXT不能直接使用ITF格

式的文件,它提供grdgenxo 命令将晶圆代工厂提供的ITF格式文件转换成

Star-RCXT所需要的.nxtgrd格式文件,Mapping文件用于实现这种转换过程,将目标.nxtgrd文件中各个层次名称与设计数据库中的层名称相对应起来。

Star-RCXT支持的格式

寄生参数提取工具Star-RCXT支持多种格式输入,主要有Milkyway、Lef/Def、Hercules和Calibre格式。也支持多种格式输出,如输出格式为IEEE 1481标

准的SPEF(Standard Parastic Exchange Format)格式;输出与PrimeTime静态时序分析工具最有效对接的SBPF(Synopsys Binary Parasitic Format)格式;

输出格式包含了每一个节点RC网络信息的DSPF (Detailed Standard

Parasitic Format)格式;还有STAR、NETNAME、MW、CONLY等格式。因为寄生电容值与其毗邻的金属连线有密切关系,版图上一个图形有可能会影响到其相邻模块中某一条连线的寄生参数提取,因此寄生参数提取是针对flat版图,提取出来的寄生参数信息是不带有层次的。也正是由于这个原因,寄生参数提取一般需要花费较长的时间,并占用较大的硬件资源。

Primetime工具介绍

PrimeTime 是Synopsys公司提供的一个针对复杂全芯片进行静态时序分析的工具。PrimeTime可以集成于逻辑综合和物理综合的流程,让设计者分析并解决复杂的时序问题,提高时序收敛的速度。它是一种穷尽分析方法,不依赖于激励,分析检查电路或设计对象中的所有时序路径,包括无效路径,能够保证100%的覆盖率。它运行速度快,占用内存少,完全克服了动态时序验证的缺陷,适用于超大规模芯片系统的电路验证。

PrimeTime分析原理

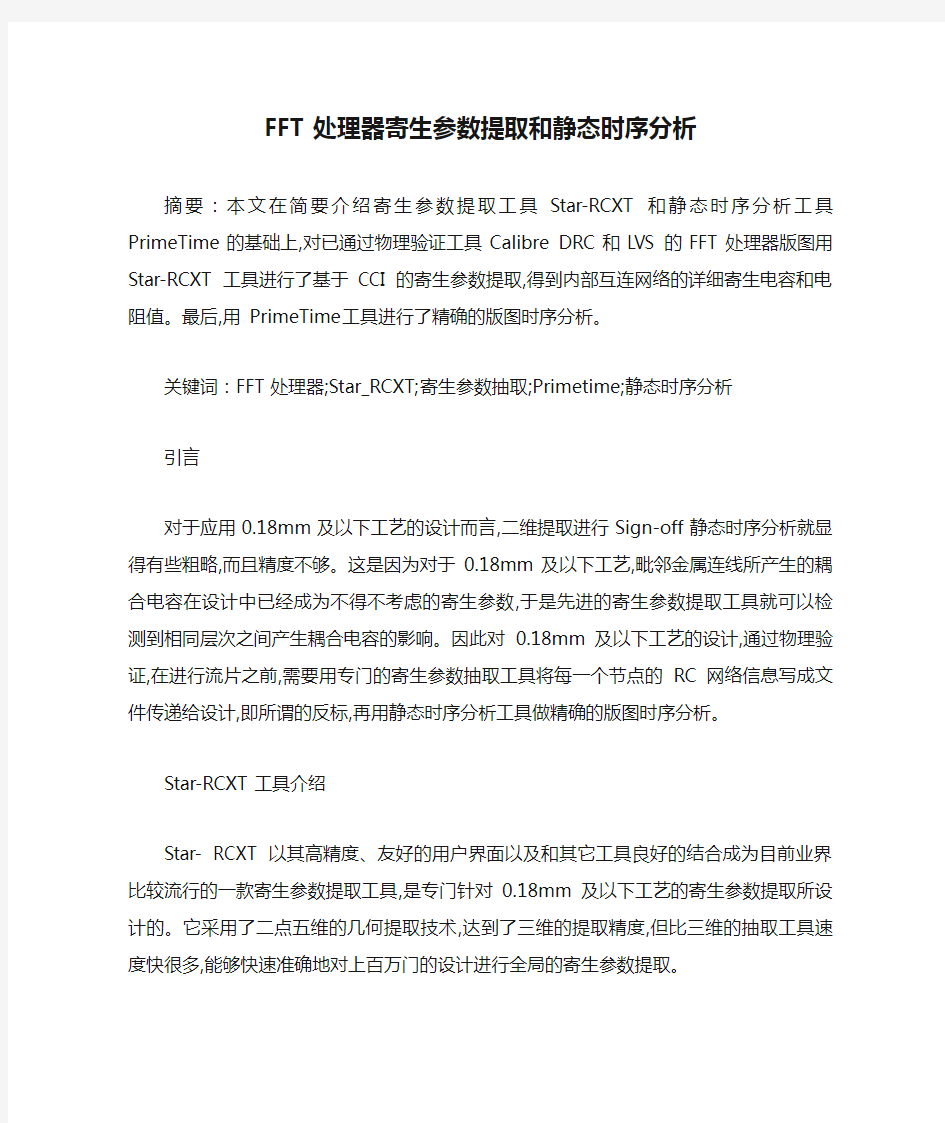

PrimeTime 进行静态时序分析时把整个芯片按照时钟分成许多时序路径。路径的起点是时序单元的输出引脚或是设计的输入端口,路径的终点是时序单元的输入引脚或是设计的输出端口。根据起点和终点的不同,可将逻辑电路分解为图1中用虚线表示的四种路径,分别代表了以下四种类型: 路径1起始于输入端口,终止于时序单元的数据输入端;路径2起始于时序单元的时钟引脚,终止于时序单元的数据输入端;路径3起始于时序单元的时钟引脚,终止于输出端口;路径4起始于输入端口,终止于输出端口。

图1 逻辑电路中的四种时序路径

PrimeTime 工具把设计打散成一系列时序路径之后,沿每条路径计算延时。路径的总延时是该路径中所有单元延时和连线延时的和。单元延时为路径中从逻辑门的输入到输出的延时量,若没有提供反标延时信息,PrimeTime会根据工艺库

中提供的此单元延迟表来计算单元延时。典型的单元延迟表是输入传输时间和输出负载电容的函数,基于二维表格来计算每个单元的延时。对于在表格中找不到对应点的情况,可通过内插或外推表格中的值来获得当前条件下的延时值。连线延时是时序路径中从一个单元的输出到下一个单元输入的延时总和。PrimeTime可读取由专门提取工具得到的详细内部互联网络的寄生电容和电阻值,并基于此精确地计算连线延时,以完成精确的版图时序分析。

PrimeTime分析要求

静态时序分析的目的是保证设计中的以上四种类型路径可以满足建立时间和保持时间的要求。即无论其起点是什么,信号都可以被及时地传递到该路径的终点,

并且在电路正常工作所必需的时间段内保持恒定。如果建立时间和保持时间不能得到满足,触发器就无法采样到正确的数据。

对FFT处理器进行寄生参数提取和静态时序分析

当 FFT处理器完成版图设计,通过Calibre DRC和LVS进行Sign-off的静态时序分析时,可用专门的寄生参数提取工具Star-RCXT将每一个节点的RC网络信息写成文件传递给设计,再用静态时序分析工具PrimeTime读取由Star-RCXT工具得到的详细内部互联网络的寄生电容和电阻值,并基于此精确地计算连线延迟,做精确的版图时序分析。

对FFT处理器进行寄生参数提取

由于FFT项目采用Mentor公司的 Calibre工具进行DRC和LVS,因此寄生参数提取工具Star-RCXT采用的输入格式为Calibre,基于CCI(Calibre

Connectiity Interface)的Star-RCXT寄生参数提取流程如图2所示。

图2 基于CCI的寄生参数提取流程

在 Calibre中采用flat方式对FFT处理器进行LVS,通过LVS后自动产生SVDB 目录,并将配置LVS运行时设置的内容保存为lvsset文件。然后编写

query.cmd文件,该文件指定基于CCI的Star-RCXT寄生参数提取所需文件的位置,如标注的GDSII版图、层映射信息、顶层端口信息、理想版图网表、网络名信息、交互表等。编写好query.cmd文件后,在calibredrv工具的命令行中执行命令:Calibre- query svdb < query.cmd,会生成Star-RCXT寄生参数提取所需的文件,如包含多边形和连通性信息的文件xtalkdetailDRCLVS.agf、元件交互参考信息的文件xtalkdetailDRC LVS.ixf、网络交互参考信息的文件xtalkdetailDRCLVS.nxf、理想版图网表文件xtalkdetailDRCLVS.nl和器件表文件xtalkdetailDRCLVS. devtab等。

本设计用运行Star-RCXT命令文件(star.cmd)来进行寄生参数提取,在编写star.cmd命令文件时要输入:模块名称xtalkdetailDRCLVS、层映射文件SmicVTMP_LO_SRAM _MR_MM_HV_LC_018.map、电源/地网络名称VDD和GND、加

工工艺文件smic018.nxtgrd、提取参数的输出格式SPEF、提取网络的范围、是否要将耦合电容折算成对地电容、配置LVS运行的设置文件lvsset和指定进行基于CCI寄生参数提取所需文件位置的文件 query.cmd等。然后在Star-RCXT 中运行StartXtract -clean star.cmd命令即可完成寄生参数提取,输出文件名为xtalkdetailDRCLVS.spef。

对FFT处理器进行静态时序分析

首先在PrimeTime的启动文件(.synopsys_pt.setup)中设置与库文件相关的信息,如用set_link_library { * smic18_ss.db smic18IO_line_ss.db}命令来

设置链接库,用set target_library {* smic18_ss.db smic18_IO_line_ss.db}

命令来设置目标库、用set_min_library命令来指定工艺库用于最大延迟和最小延迟分析等。然后用 primetime命令启动PrimeTime的图形用户界面,对FFT 处理器进行Sign-off的静态时序分析。具体流程包括:读入设计数据、约束时序、设定环境和分析条件、检查设计数据和分析设置参数,以及执行分析和检查结果5步。

读入设计数据

读入网表文件用read_verilog命令,读入由Star-RCXT提取输出的SPEF格式寄生网表用read_parasitics命令。若要分析建立时间则要读入最坏情况的寄生电容和电阻信息,若要分析保持时间则要读入最好情况的寄生电容和电阻信息。

约束时序

进行Sign-off静态时序分析时,由于现在的网表中已经包括了实际的时钟信息,用create_clock命令来定义一个时钟的基本信息,如周期、波形等,将该时钟信号在实际的时钟树中传播,进而得到实际的时钟延时和偏移。用

set_propagated_ clock命令可以根据时钟树,自动计算出时钟信号到达终点的延时和偏移。Sign-off静态时序分析可不设置时钟的确定性,但有时为了提高设计可靠性,用set_clock_uncertainty命令对建立时间和保持时间都设置一个很小时间值。根据设计规范要求用set_input_delay命令直接设置输入延时值,用set_output_delay命令直接设置输出延时值等。

设定环境和分析条件

PrimeTime 中set_operating_conditions命令用来根据工艺库指定工艺、温度和电压的工作条件。分析建立时间时工作条件应当在最坏情况进行,即

set_operating_conditions worst;分析保持时间时工作条件应当在最好情况进行,即set_operating_conditions best。用set_load命令设置输出端口的负载,用set_driving_cell命令指定输入端口的驱动单元等。另外可用

set_case_analysis命令在某个端口设置为固定逻辑常数或逻辑转换限制该信号在设计中传播,如果在时序分析时不考虑扫描链的影响,可执行

set_case_analysis 0 [get_ports scan_en_pad]命令。

检查设计数据和分析设置参数

在进行时序分析前要先检查设计数据,如层次、库、端口、单元等,以及分析设置参数,如时钟、输入延迟约束、输出延迟约束等是否已经设置或设置是否正确。如, 用check_timing命令来检查是否存在未定义的时钟、未定义的输入到达时间和未定义的输出约束等;用report_design命令输出当前设计的一系列属性,如分析类型、所选的工作条件、线负载模型和设计规则等;用report_port 命令显示端口名、引脚电容、线电容和输入输出延迟等端口信息。

执行分析和检查结果

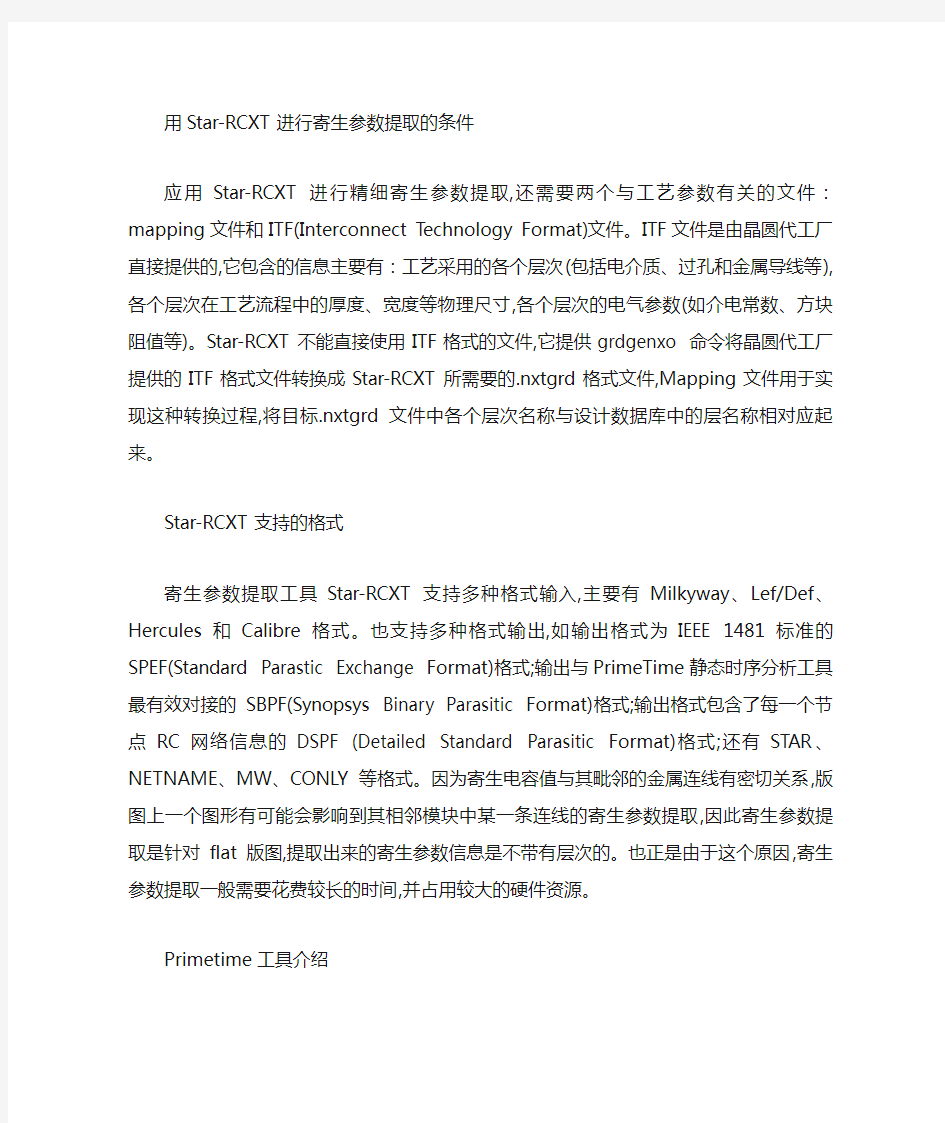

在设计数据和参数设置均正确的情况下进行时序分析,然后查看分析结果,获得设计具体的时间信息。如用report_timing命令产生一条最大时延路径的详细报告,包括路径信息(工作条件、线负载模型的模式、路径起点、路径终止点和路径类型等)、路径延时、路径延时要求和总结部分。用report_constraint-all_violator命令报告所有的建立时间时序违规。为了准确了解FFT处理器所有路径的建立时间情况,可执行菜单命令Timing→Histogram→Endpoint Slack…弹出Endpoint Slack对话框,在Delay type中选择max后按OK可得如图3所示的所有路径建立时间情况,从中可知建立时间最小值为0.13792,满足建立时间要求。再运行命令 report_analysis_coverage得PrimeTime分析的路径条数为45957,分析的覆盖率为100%,建立时间的违规率为0%。

图3 建立时间的分析结果

为了准确了解FFT处理器所有路径的保持时间情况,可进行与分析建立时间过程相同的步骤。

结语

静态时序分析已经成为数字集成电路设计必不可少的环节。本文应用寄生提取工具Star-RCXT基于CCI流程对FFT处理器进行寄生参数提取,再用静态时序分析工具PrimeTime读取由Star-RCXT抽取工具得到的内部互连网络的详细寄生电容和电阻值,进行精确的版图时序分析。它不需要输入测试向量就能覆盖所有的路径,且运行速度很快,占用内存较少,可以对芯片设计进行全面的时序验证。

集成电路验证与算法知识点总结

集成电路验证与算法知识点总结 黑盒:验证工程师不需了解设计的任何实现细节,所有的验证都必须通过接口完成,不能对内部状态进行直接访问,对内部的结构和实现不需过多了解,缺陷可观测性和可控性比较差。白盒:对待验证设计的内部结构和实现完全可见,也具有完全的可控性,优点在于能够快速的设置感兴趣的状态和输入组合,或者分离特定的功能,可以很容易的在验证过程中对结果进行观察并在输出与期望结果不一致时立即报错,但这种方法与特定的实现紧密相关,并且不能用于不同的实现或者将来的二次设计并且还需要验证工程师对设计实现的细节有相当的了解,以便正确生成有意义的条件以及合理地确定对什么结果进行观测白盒是黑盒的有益补充可以保证与实现有关的特性功能的正确性。 灰盒:介于黑盒和白盒之间的一种折中方案。黑盒可能不能验证设计的所有部分,而白盒不具备可移植性和独立性,与黑盒一样,灰盒通过最顶层接口对设计进行观测和控制,一般而已,灰盒最主要是验证与特定实现有关的重要特征。 遗传算法:5个参数的定义:Np是种群数量,Ng是每一代的数量No是产生子代的数量,Pi是通过反转产生2代的概率,Pu是通过变异产生子代的概率。基本思想:首先计算每一个个体的适应度Fitness Np(i)通过竞争选择出Ng个个体,然后根据适应度随机选择双亲,产生下一代,产生下一代的方式中Pi的概率是通过反转产生,Pu的概率通过变异产生,还有的是通过双亲交配产生,产生下一代的个体数量为No,由Ng和No选择出Np个以保持种群数量不变。一直遗传下来,直到种群的适应度足够高或不再提高为止。 验证计划:①明确的验证目标②验证策略③验证手段:基于行为级的模拟,静态时序分析还是形式化验证④结果检查手段:开发的验证环境是自检查,还是验证结果与参考模型的输出结果对比,还是验证结果直接和期望结果对比⑤建立验证环境的要求:内容有验证对象的抽象层次,验证模型的来源,包括行为模型,模拟模型等;验证环境的要素,包括结果检查,激励源等。⑥制定验证方案,即验证用例设计⑦验证结果的质量标准,内容包括验证向量数目,功能覆盖率和代码覆盖率⑧回归测试,什么时间进行回归测试,采用哪些激励进行回归测试⑨验证问题跟踪与管理,内容包括验证过程中发现的问题的记录和解决问题的情况,以及由此引发的代码更改记录⑩制定验证的进度安排和小组人员职责和分工⑾验证计划评审的节点和内容。 断言:监测设计中正确行为或错误行为的验证对象。断言将设计要求转换成了验证对象,从而可以用模拟器或形式化验证工具,评测设计要求是否被满足.断言分为3种:第一种为Assertion,用于描述设计所期望的正确行为;第二种为Constraint,用于描述设计所处环境的行为;第三种为Cover,用于描述设计及其所处环境应该会到达的状态。 SV A是SystemVerilog的断言,比较适合用Verilog编写的RTL代码,SV A是免费的,而PSL 需要购买。SV A的不太适合验证异步时钟接口。 PSL比较适合用VHDL编写的RTL代码。PSL的断言可以用于验证异步时钟接口。PSL的断言功能比SV A要强,例如,PSL支持具有Liveness功能的断言,但SV A不支持openspabc的功能验证(不包括时序和物理设计验证)①处理器体系结构设计验证②RTL设计模拟验证③DFT验证;系统级环境验证:固件操作系统和各类驱动; 使用工具:软模拟,加速器仿真,形式化验证;商业工具+定制工具 模拟:1适用于所有设计层次,2需要测试向量,3完整的模型,部分的验证,4输入驱动,施加激励,比较输出,5不完备的验证方法,只能证明设计有错而不能证明无错,6验证输入空间的点,一次检查一个输出点,7难点在于确定模拟激励是否足够。

TimeQuest快速入门

TimeQuest快速入门 简介 本教程介绍用TimeQuest Analyzer进行时序约束和静态时序分析的必要步骤。所用示例文件在\qdesigns\fir_filter文件夹下。 TimeQuest约束步骤 下面的步骤描述了用TimeQuest对设计进行时序约束的步骤,每一步操作包含GUI和Command-line的操作方法。 第1步:在QuartusII中打开&建立工程 启动QuartusII软件,在\qdesigns\fir_filter文件夹下打开工程compile_fir_filter.qpf。 第2步:设置TimeQuest Analyzer 默认状态下,QuartusII使用Classic Timing Analyzer作为默认的时序分析工具。需要在QuatusII中进行如下设置将TimeQuest Analyzer设为当前工程的时序分析器。 在【Assignment】菜单下单击【Settings】,在【Category】列表中展开【Timing Analysis Processing】,选择【Use TimeQuest Analyzer during compilation】,然后点击【OK】即可。 第3步:进行初始的编译 在将时序约束应用到设计之前,需要为TimeQuest创建初始的数据。初始数据是通过post-map结果产生的。步骤如下: 在【Processing】菜单栏下,选择【Start】/【Start Analysis&Synthesis】。 通过运行【Analysis&Synthesis】产生post-map数据。 还可以用post-fit网表来产生初始数据。但是创建post-map数据所用时间更少,而且post-map数据对本设计示例工程来说已经够用。 第4步:启动TimeQuest Analyzer 为了创建并验证时序约束,需要启动TimeQuest Analyzer。在【Tools】菜单下,单击【TimeQuest Analyzer】启动TimeQuest Analyzer。 第5步:创建Post-Map时序网表 在指定时序要求前,需要首先创建一个时序网表。可以从post-map或post-fit 数据中创建时序网表(见第3步)。利用post-map数据创建时序网表的方法为:在【netlist】菜单下,单击【Create Timing Netlist】,在弹出的对话框中,选择【Input netlist type】下的【Post-Map】,单击【OK】。 不能通过【Task】面板下的【Create Timing Netlist】命令来创建post-map网表。在默认情况下,【Create Timing Netlist】需要post-fit数据。

半导体激光器常用参数的测定

半导体激光器常用参数的测定 一 实验目的:掌握半导体激光器常用的电学参数及其测试方法 一 实验基本原理 1、 普通光源的发光——受激吸收和自发辐射 普通常见光源的发光(如电灯、火焰、太阳等地发光)是由于物质在受到外来能量(如光能、电能、热能等)作用时,原子中的电子就会吸收外来能量而从低能级跃迁到高能级,即原子被激发。激发的过程是一个“受激吸收”过程。处在高能级(E2)的电子寿命很短(一般为10-8~10-9秒),在没有外界作用下会自发地向低能级(E1)跃迁,跃迁时将产生光(电磁波)辐射。辐射光子能量为 12E E h -=ν 这种辐射称为自发辐射。原子的自发辐射过程完全是一种随机过程,各发光原子的发光过程各自独立,互不关联,即所辐射的光在发射方向上是无规则的射向四面八方,另外未位相、偏振状态也各不相同。由于激发能级有一个宽度,所以发射光的频率也不是单一的,而有一个范围。在通常热平衡条件下,处于高能级E2上的原子数密度N2,远比处于低能级的原子数密度低,这是因为处于能级E 的原子数密度N 的大小时随能级E 的增加而指数减小,即N ∝exp(-E/kT),这是著名的波耳兹曼分布规律。于是在上、下两个能级上的原子数密度比为 ]/)(ex p[/1212kT E E N N --∝ 式中k 为波耳兹曼常量,T 为绝对温度。因为E2>E1,所以N2《N1。例如,已知氢原子基态能量为E1=-13.6eV ,第一激发态能量为E2=-3.4eV ,在20℃时,kT≈0.025eV,则 0)400ex p(/12≈-∝N N 可见,在20℃时,全部氢原子几乎都处于基态,要使原子发光,必须外界提供能量使原子到达激发态,所以普通广义的发光是包含了受激吸收和自发辐射两个过程。一般说来,这种光源所辐射光的能量是不强的,加上向四面八方发射,更使能量分散了。 2、 受激辐射和光的放大 由量子理论知识知道,一个能级对应电子的一个能量状态。电子能量由主量子数n(n=1,2,…)决定。但是实际描写原子中电子运动状态,除能量外,还有轨道角动量L 和自旋角动量s ,它们都是量子化的,由相应的量子数来描述。对轨道角动量,波尔曾给出了量子化公式Ln =nh ,但这不严格,因这个式子还是在把电子运动看作轨道运动基础上得到的。严格的能量量子化以及角动量量子化都应该有量子力学理论来推导。 量子理论告诉我们,电子从高能态向低能态跃迁时只能发生在l (角动量量子数)量子数相差±1的两个状态之间,这就是一种选择规则。如果选择规则不满足,则跃迁的几率很小,甚至接近零。在原子中可能存在这样一些能级,一旦电子被激发到这种能级上时,由于不满足跃迁的选择规则,可使它在这种能级上的寿命很长,不易发生自发跃迁到低能级上。这种能级称为亚稳态能级。但是,在外加光的诱发和刺激下可以使其迅速跃迁到低能级,并放出光子。这种过程是被“激”出来的,故称受激辐射。受激辐射的概念世爱因斯坦于1917年在推导普朗克的黑体辐射公式时,第一个提出来的。他从理论上预言了原子发生受激辐射的可能性,这是激光的基础。 受激辐射的过程大致如下:原子开始处于高能级E2,当一个外来光子所带的能量hυ正好为某一对能级之差E2-E1,则这原子可以在此外来光子的诱发下从高能级E2向低能级E1跃迁。这种受激辐射的光子有显著的特点,就是原子可发出与诱发光子全同的光子,不仅频

MOS管寄生参数的影响和其驱动电路要点

MOS管寄生参数的影响和其驱动电路要点 我们在应用MOS管和设计MOS管驱动的时候,有很多寄生参数,其中最影响MOS管开关性能的是源边感抗。寄生的源边感抗主要有两种来源,第一个就是晶圆DIE和封装之间的Bonding 线的感抗,另外一个就是源边引脚到地的PCB走线的感抗(地是作为驱动电路的旁路电容和电源网络滤波网的返回路径)。在某些情况下,加入测量电流的小电阻也可能产生额外的感抗。 我们分析一下源边感抗带来的影响: 使得MOS管的开启延迟和关断延迟增加 由于存在源边电感,在开启和关段初期,电流的变化被拽了,使得充电和放电的时间变长了。同时源感抗和等效输入电容之间会发生谐振(这个谐振是由于驱动电压的快速变压形成的,也是我们在G端看到震荡尖峰的原因),我们加入的门电阻Rg和内部的栅极电阻Rm都会抑制这个震荡(震荡的Q值非常高)。 我们需要加入的优化电阻的值可以通过上述的公式选取,如果电阻过大则会引起G端电压的过冲(优点是加快了开启的过程),电阻过小则会使得开启过程变得很慢,加大了开启的时间(虽然G端电压会被抑制)。 源边感抗另外一个影响是阻碍Id的变化,当开启的时候,初始时di/dt偏大,因此在原感抗上产生了较大压降,从而使得源点点位抬高,使得Vg电压大部分加在电感上面,因此使得G 点的电压变化减小,进而形成了一种平衡(负反馈系统)。 另外一个重要的寄生参数是漏极的感抗,主要是有内部的封装电感以及连接的电感所组成。 在开启状态的时候Ld起到了很好的作用(Subber吸收的作用),开启的时候由于Ld的作用,有效的限制了di/dt/(同时减少了开启的功耗)。在关断的时候,由于Ld的作用,Vds电压形成明显的下冲(负压)并显著的增加了关断时候的功耗。下面谈一下驱动(直连或耦合的)的一些重要特性和典型环节:

IC后端流程初学必看样本

校外IC后端实践报告 本教程通过对synopsys公司给lab进行培训,从verilog代码到版图整个流程(固然只是基本流程,由于真正一种大型设计不是那么简朴就完毕),此教程目就是为了让人们尽快理解数字IC设计大概流程,为后来学习建立一种基本。此教程只是本人摸索实验成果,并不代表内容都是对的,只是为了阐明大概流程,里面一定尚有诸多未完善并且有错误地方,我在此后学习当中会对其逐个完善和修正。 此后端流程大体涉及一下内容: 1.逻辑综合(工具DC 逻辑综合是干吗就不用解释了把?) 2.设计形式验证(工具formality) 形式验证就是功能验证,重要验证流程中各个阶段代码功能与否一致,涉及综合前RTL代码和综合后网表验证,由于如今IC设计规模越来越大,如果对门级网表进行动态仿真话,会耗费较长时间(规模大话甚至要数星期),这对于一种对时间规定严格(设计周期短)asic 设计来说是不可容忍,而形式验证只用几小时即可完毕一种大型验证。此外,由于版图后做了时钟树综合,时钟树插入意味着进入布图工具本来网表已经被修改了,因此有必要验证与本来网表是逻辑等价。 3.静态时序分析(STA),某种限度上来说,STA是ASIC设计中最重要环节,使用primetime 对整个设计布图前静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。 (PR后也需作signoff时序分析) 4.使用cadence公司SOCencounter对综合后网表进行自动布局布线(APR) 5.自动布局后来得到详细延时信息(sdf文献,由寄生RC和互联RC所构成)反标注到网 表,再做静态时序分析,与综合类似,静态时序分析是一种迭代过程,它与芯片布局布线联系非常紧密,这个操作普通是需要执行许多次才干满足时序需求,如果没违规,则进入下一步。 6.APR后门级功能仿真(如果需要)

静态时序分析中建立时间和保持时间关系详解

建立时间和保持时间关系详解 图1 建立时间(setup time)是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器; 保持时间(hold time)是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被打入触发器。 如图1 。数据稳定传输必须满足建立和保持时间的要求,当然在一些情况下,建立时间和保持时间的值可以为零。PLD/FPGA开发软件可以自动计算两个相关输入的建立和保持时间。 个人理解: 1、建立时间(setup time)触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。 2、保持时间(hold time)触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。 关于建立时间保持时间的考虑 华为题目:时钟周期为T,触发器D1的建立时间最大为T1max,最小为T1min。组合逻辑电路最大延迟为T2max,最小为T2min。问:触发器D2的建立时间T3和保持时间T4应满足什么条件? 分析: Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为触发器的输出延时。 Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是题目中的组合逻辑延迟。 Tsetup:建立时间 Thold:保持时间 Tclk:时钟周期 建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。 保持时间容限:保持时间容限也要求大于等于0。

HeNe激光器模式分析

实验二 He-Ne 激光器的模式分析 一、实验目的 1. 用共焦球面扫描干涉仪测量He-Ne 激光器的相邻纵模间隔,判别高阶横模的阶次。 2. 了解激光的频谱结构,掌握扫描干涉仪的使用方法及测定其性能指标的实验技能。 3. 观察激光器的频率漂移及跳模现象,了解其影响因素;观察激光器的输出横向光场分布花样,体会谐振腔的调整对它的影响。 二 实验设备 He-Ne 激光器、激光电源、小孔光阑、共焦球面扫描干涉仪、锯齿波发生器、放大器、示波器等 三、实验原理 1.激光的频率特性 激光器的光学谐振腔内可存在一系列具有分立谐振频率的本征模式,但其中频率位于工作物质增益带宽范围内,并满足阈值条件的本征模才会振荡形成激光。 通常把激光光波场的空间分布,分解为沿传播方向(腔轴方向)的分布E(z)和垂直于传播方向在横截面内的分布E(x,y),即谐振腔模式可分为纵模和横模,用符号TEM mn 标志不同模式的模式分布。对激光束的模式进行频率分析,可以分辨出它的精细 结构。 由无源腔理论可知:共轴稳定球面谐振腔TEM mn 模的频率为 ??? ????????? ??-???? ??-+++=2111arccos )1(12R L R L n m q nL C v mnq π (2.1) 式中m 、n 为横模阶次,q 为纵模阶次,L 为腔长,R 1R 2是腔面两反射镜的曲率半径,n 是工作物质的折射率。 当m=n=0时为基横模,而m 或n ≠0时叫做高阶横模。对于不同的横模(m 、n 不同)有不同的横向光强分布,所以观察光斑图案或测量光强分布也能分析横模结构。但对于含有高阶横模的结构,则必须借助于频率分析才能分辨。由(2.1)式可知,q 一定时,不同的横模对应有不同的振荡频率,其频率间隔为

寄生参数提取-CalibrexRC培训班

寄生参数提取-Calibre xRC培训班 (1天) 课程描述: Mentor Graphics 的Calibre 是深亚微米物理验证的工业标准。本次课程将教会用户IC设计流程中有效的使用Calibre xRC进行寄生参数提取。更有相应的练习课程可加深对Calibre xRC概念和技术的理解,增加Calibre xRC的使用经验。 在这次课中可以学到: ●如何编写Calibre xRC所需的文件; ●如何使用Calibre xRC进行寄生参数提取,产生Lumped-C、Distributed RC和RCC网表等; ●如何分析Calibre xRC的报告和了解提取出来的网表结果等; ●了解Calibre xRC与其他EDA供应商的工具的接口。 适合的听众: ●IC设计工程师和版图工程师; ●需要编写rule files的工程师; ●CAD支持小组。 需要的知识: ●IC版图设计的知识; ●使用Calibre LVS的经验; ●了解电路仿真的基本知识; ●了解SPICE网表; ●熟悉UNIX; ●版图验证概念和工具的知识(非必需)。

附录1: Calibre xRC for Parasitic Extraction Training Course Schedule ●Morning ?Introduce Calibre xRC ?Foundational Flow Concepts ?Parasitic Elements and Netlists ?Transistor-Level Extraction ?Lab ●Morning ?Gate-Level Extraction ?Customizing Output Netlists ?Hierarchical Extraction ?Lab ?Q&A

时序分析基础与时钟约束实例1

时序分析基础与时钟约束实例(1) 文中实例配套SF-CY3开发套件。更多内容请参考《SF-CY3 FPGA套件开发指南》。 何谓静态时序分析(STA,Static Timing Analysis)? 首先,设计者应该对FPGA内部的工作方式有一些认识。FPGA的内部结构其实就好比一块PCB板,FPGA的逻辑阵列就好比PCB板上的一些分立元器件。PCB通过导线将具有相关电气特性的信号相连接,FPGA也需要通过内部连线将相关的逻辑节点导通。PCB板上的信号通过任何一个元器件都会产生一定的延时,FPGA的信号通过逻辑门传输也会产生延时。PCB的信号走线有延时,FPGA的信号走线也有延时。这就带来了一系列问题,一个信号从FPGA的一端输入,经过一定的逻辑处理后从FPGA的另一端输出,这期间会产生多大的延时呢?有多个总线信号从FPGA的一端输入,这条总线的各个信号经过逻辑处理后从FPGA 的另一端输出,这条总线的各个信号的延时一致吗?之所以关心这些问题,是因为过长的延时或者一条总线多个信号传输时间的不一致,不仅会影响FPGA本身的性能,而且也会给FPGA之外的电路或者系统带来诸多问题。 言归正传吧,之所以引进静态时序分析的理论也正是基于上述的一些思考。它可以简单的定义为:设计者提出一些特定的时序要求(或者说是添加特定的时序约束),套用特定的时序模型,针对特定的电路进行分析。分析的最终结果当然是要求系统时序满足设计者提出的要求。 下面举一个最简单的例子来说明时序分析的基本概念。假设信号需要从输入到输出在FPGA内部经过一些逻辑延时和路径延时。系统要求这个信号在FPGA内部的延时不能超过15ns,而开发工具在执行过程中找到了如图所示的一些可能的布局布线方式。那么,怎样的布局布线能够达到系统的要求呢?仔细分析一番,发现所有路径的延时可能为14ns、15ns、16ns、17ns、18ns,有两条路径能够满足要求,那么最后的布局布线就会选择满足要求的两条路径之一。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,即有约束才会有分析。若设计者不添加时序约束,那么时序分析就无从谈起。特权同学常常碰见一些初学者在遇到问题时不问青红皂白就认为是时序问题,实际上只有在添加了时序约束后,系统的时序问题才有可能暴露出来。 下面我们再来看一个例子,我们假设有4个输入信号,经过FPGA内部一些逻辑处理后输出。FPGA内部的布线资源有快有慢之分,好比国道和高速公路。通过高速通道所需要的路径延时假设为3ns-7ns,但只有两条可用;而通过慢速通道的路径延时则>10ns。

激光器的种类及性能参数总结

激光器的种类及性能参数总结 半导体激光器——用半导体材料作为工作物质的一类激光器 中文名称: 半导体激光器 英文名称: semiconductor laser 定义1: 用一定的半导体材料作为工作物质来产生激光的器件。 所属学科: 测绘学(一级学科);测绘仪器(二级学科) 定义2: 以半导体材料为工作物质的激光器。 所属学科: 机械工程(一级学科);光学仪器(二级学科);激光器件和激光设备-激光器名称(三级学科) 定义3: 一种利用半导体材料PN结制造的激光器。 所属学科: 通信科技(一级学科);光纤传输与接入(二级学科) 半导体激光器的常用参数可分为:波长、阈值电流Ith 、工作电流Iop 、垂直发散角θ⊥、水平发散角θ∥、监控电流Im 。 (1)波长:即激光管工作波长,目前可作光电开关用的激光管波长有635nm、650nm、670nm、激光二极管690nm、780nm、810nm、860nm、980nm等。 (2)阈值电流Ith :即激光管开始产生激光振荡的电流,对一般小功率激光管而言,其值约在数十毫安,具有应变多量子阱结构的激光管阈值电流可低至10mA以下。 (3)工作电流Iop :即激光管达到额定输出功率时的驱动电流,此值对于设计调试激光驱动电路较重要。 (4)垂直发散角θ⊥:激光二极管的发光带在垂直PN结方向张开的角度,一般在15?~40?左右。 (5)水平发散角θ∥:激光二极管的发光带在与PN结平行方向所张开的角度,一般在6?~ 10?左右。 (6)监控电流Im :即激光管在额定输出功率时,在PIN管上流过的电流。 工业激光设备上用的半导体激光器一般为1064nm、532nm、808nm,功率从几瓦到几千瓦不等。一般在激光打标机上使用的是1064nm的,而532nm的则是绿激光。 准分子激光器——以准分子为工作物质的一类气体激光器件。 中文名称: 准分子激光器 英文名称: excimer laser 定义:

静态时序分析报告中门延时计算

1引言 在集成电路设计过程中,模拟方法是应用最多的验证时序正确与否的手段,然而,模拟方法在微系统芯片(SoC)时代正面临严竣的挑战。传统的逻辑模拟方法虽然比较快,但需要输入向量作为激励,给使用带来很多不便;更为严重的是其精度不够高,不能处理SoC时代越来越严重的互连线的耦合电容、电感效应。电路模拟方法虽然能非常精确地计算SoC时代的各种效应,但其速度太慢,容量也太小。静态时序分析技术通过提取整个电路的所有时序路径,计算信号沿(上升沿或下降沿)在传播过程的延时,然后检查在最坏情况下电路中是否存在建立时间和保持时间不满足要求的器件,从而确认被验证的电路是否存在时序问题。它们又分别通过对最大路径延迟和最小路径延迟的分析得到。静态时序分析不需要输入向量、运行速度快、占用内存少,因而成为SoC时代最主要的时序验证手段。延时计算和最长/最短路径分析是静态时序分析的关键。由于互连线结构 [1]对门延时的影响非常大,必须在门延时模型中充分考虑这一因素才能确保静态分析结果的正确性。 广告插播信息 维库最新热卖芯片: XC9536-15PC44C SN74F244DWR IS62C1024L-70Q SS34HT162288E6050-RJJ AQY210E H KM68V257CJ-15MUR3020PT TL082CDR 本文提出新的Π模型方法,结合了门的等效电容[3]来计算门的延时,我们的方法结合门的互连线负载的拓扑结构和门负载三阶矩求解的方法,采用[4]中提出的等效电容的求解公式,求出门延时计算模型,相比上述两种方法,在静态时序分析中更为合理。 2新的门延时模型 2.1 新的门延时模型 在[4]中,作者提出了利用Π型的RC模型来近似门的互连线输出负载,同时考虑了负载的屏蔽效应。用该模型等价地计算出门输出驱动点导纳函数前三阶系数。 图1中Y(s)表示准确的RC树的驱动点导纳函数,在s=0的Taylor展开式表示如下: 将门的输出的RC树的互连线负载等效负载为Π模型,如图2。

FPGA静态时序分析模型——寄存器到寄存器

FPGA静态时序分析模型——寄存器到寄存器 1. 适用范围 本文档理论适用于Actel FPGA并且采用Libero软件进行静态时序分析(寄存器到寄存器)。 2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为FPGA设计的主要验证手段之一,不需要设计者编写测试向量,由软件自动完成分析,验证时间大大缩短,测试覆盖率可达100%。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。 进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。 3. 理论分析 3.1 静态时序分析的理论基础知识 在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的时序分析报告犹如天书。如图3.1所示,为libero软件给出的寄存器到寄存器模型的时序分析报告的截取,接下来我们会弄清楚每个栏目的数据变量的含义,以及计算方法。 图3.1 libero静态时序分析报告 3.1.1 固定参数launch edge、latch edge、Tsu、Th、Tco概念

1. launch edge 时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。 2. latch edge 时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。 3. Clock Setup Time (Tsu) 建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。如图3.2所示: 图3.2 建立时间图解 4. Clock Hold Time (Th) 保持时间(Th):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。保持时间示意图如图3.3所示: 图3.3 保持时间图解 5. Clock-to-Output Delay(tco) 数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间

《现代SOC设计技术》学习小结

《现代SOC设计技术》学习小结 目录 一、SOC的概念 二、前端设计和后端实现 三、可测性设计 四、软硬件协同技术 五、验证技术 六、低功耗技术 七、IP复用技术 一、SOC概念 SOC(System on Chip)中文翻译为片上系统、系统级芯片等,由超大规模集成电路发展而来。从狭义上理解,SOC即把系统关键部件集成的到一张芯片上;而从广义上理解,SOC本身就是一个小型系统。 SOC的发展由市场和技术共同推动。20世纪90年代,计算机、通信、电子产品以及军事等领域需要大量高集成度的集成电路,于是集成电路向集成系统转变。这种转变的表现,一方面,IC品种增加、规模扩大、性能提高、上市时间缩短,并且IC标准化形成;另一方面,微电子技术不断发展,计算机性能提高,EDA综合开发工具性能提高,硬件描述语言公布。相比于IC,SOC具有的优势有:功耗低、体积小、速度快、功能丰富、节省成本。 IP核是SOC设计的基本单元。IP核是已经设计好经过验证的具

有特定功能的电路模块。在设计SOC时可以直接使用IP核。IP核分为软核、硬核和固核。软核指RTL级描述的核,一般是HDL代码,也就是源代码。它不依赖工艺,灵活性好,价格很贵。硬核指电路版图形式的核,不能被修改。它需要预先布局,可靠性高,价格低。固核介于软核和硬核之间,属于门级网表形式,固核需要使用者布局布线,有一定的灵活性。 SOC设计是基于核的设计,也就是将系统按功能分为若干块,组合不同的IP核,集成为特定功能的芯片的过程。但是这不意味着,简单的组合IP核就够了,还需要IP核的测试复用和结构上的精心设计。通常利用IP模块可以简化系统设计,但是对开发者理解IP模块有了更高的要求,时序一致性的问题也会凸显。这个问题推动了IP 模块的标准化。代表性的SOC标准化组织是美国的VSIA。 SOC的技术的特征有:复杂的系统功能、软硬件结合、含有一个或多个芯核(微处理器MPU、微控制器MCU、数字信号处理器DSP等)、采用深亚微米或超深亚微米工艺实现。 随着计算机、通信、手持设备等对IC的需求不断增加。IC的发展由元件到单元,再到RTL,现在为IP核。集成电路会继续朝着SOC 发展。 我国的SOC产业从20世纪90年代开始逐步发展。现在基本分为三大产业:设计、制造和封装。封装测试业占的比重约70%。在我国SOC发展的重点有高端通用芯片、网络通信、数字家电、信息安全、工业控制、生物医疗、IP核。

后端流程(初学必看)(DOC)

基本后端流程(漂流&雪拧) ----- 2010/7/3---2010/7/8 本教程将通过一个8*8的乘法器来进行一个从verilog代码到版图的整个流程(当然只是基本流程,因为真正一个大型的设计不是那么简单就完成的),此教程的目的就是为了让大家尽快了解数字IC设计的大概流程,为以后学习建立一个基础。此教程只是本人探索实验的结果,并不代表内容都是正确的,只是为了说明大概的流程,里面一定还有很多未完善并且有错误的地方,我在今后的学习当中会对其逐一完善和修正。 此后端流程大致包括一下内容: 1.逻辑综合(逻辑综合是干吗的就不用解释了把?) 2.设计的形式验证(工具formality) 形式验证就是功能验证,主要验证流程中的各个阶段的代码功能是否一致,包括综合前RTL代码和综合后网表的验证,因为如今IC设计的规模越来越大,如果对门级网表进行动态仿真的话,会花费较长的时间(规模大的话甚至要数星期),这对于一个对时间要求严格的asic设计来说是不可容忍的,而形式验证只用几小时即可完成一个大型的验证。另外,因为版图后做了时钟树综合,时钟树的插入意味着进入布图工具的原来的网表已经被修改了,所以有必要验证与原来的网表是否逻辑等价。 3.静态时序分析(STA),某种程度上来说,STA是ASIC设计中最重要的步骤,使用primetime对整个设 计布图前的静态时序分析,没有时序违规,则进入下一步,否则重新进行综合。(PR后也需作signoff 的时序分析) 4.使用cadence公司的SOCencounter对综合后的网表进行自动布局布线(APR) 5.自动布局以后得到具体的延时信息(sdf文件,由寄生RC和互联RC所组成)反标注到网表,再做静 态时序分析,与综合类似,静态时序分析是一个迭代的过程,它与芯片布局布线的联系非常紧密,这个操作通常是需要执行许多次才能满足时序需求,如果没违规,则进入下一步。 6.APR后的门级功能仿真(如果需要) 7.进行DRC和LVS,如果通过,则进入下一步。 8.用abstract对此8*8乘法器进行抽取,产生一个lef文件,相当于一个hard macro。 9.将此macro作为一个模块在另外一个top设计中进行调用。 10.设计一个新的ASIC,第二次设计,我们需要添加PAD,因为没有PAD,就不是一个完整的芯片,具体 操作下面会说。 11.重复第4到7步

Actel FPGA静态时序分析

1. 适用范围 本文档理论适用于Actel FPGA并且采用Libero软件进行静态时序分析(寄存器到寄存器)。 2. 应用背景 静态时序分析简称STA,它是一种穷尽的分析方法,它按照同步电路设计的要求,根据电路网表的拓扑结构,计算并检查电路中每一个DFF(触发器)的建立和保持时间以及其他基于路径的时延要求是否满足。STA作为FPGA设计的主要验证手段之一,不需要设计者编写测试向量,由软件自动完成分析,验证时间大大缩短,测试覆盖率可达100%。 静态时序分析的前提就是设计者先提出要求,然后时序分析工具才会根据特定的时序模型进行分析,给出正确是时序报告。 进行静态时序分析,主要目的就是为了提高系统工作主频以及增加系统的稳定性。对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。 3. 理论分析 3.1 静态时序分析的理论基础知识 在进行正确的时序分析前,我们必须具备基本的静态时序的基本知识点,不然看着编译器给出的时序分析报告犹如天书。如图3.1所示,为libero软件给出的寄存器到寄存器模型的时序分析报告的截取,接下来我们会弄清楚每个栏目的数据变量的含义,以及计算方法。 图3.1 libero静态时序分析报告 3.1.1 固定参数launch edge、latch edge、Tsu、Th、Tco概念 1. launch edge 时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

2. latch edge 时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。 3. Clock Setup Time (Tsu) 建立时间(Tsu):是指在时钟沿到来之前数据从不稳定到稳定所需的时间,如果建立的时间不满足要求那么数据将不能在这个时钟上升沿被稳定的打入触发器。如图3.2所示: 图3.2 建立时间图解 4. Clock Hold Time (Th) 保持时间(Th):是指数据稳定后保持的时间,如果保持时间不满足要求那么数据同样也不能被稳定的打入触发器。保持时间示意图如图3.3所示: 图3.3 保持时间图解 5. Clock-to-Output Delay(tco) 数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。 3.1.2 Clock skew 时钟偏斜(clock skew):是指一个时钟源到达两个不同寄存器时钟端的时间偏移,如图3.4所示:

YLPM激光器使用说明

●更宽的频率调节范围(1.6kHz~1000kHz); ●更高的峰值功率; ●可广泛应用于塑胶按键及阳极铝打黑等项目上。 ●更快的开关光速度,打标速度更快。 在安装打标软件时,注意选择选择“YLPM型激光器”, 在控制界面,YLP-M比YLP-F多了一个打标参数:激光模式。共有8种激光模式可选。可直接把所需的模式填入。 8种模式都有标称频率,即RR值,如果设定的频率低于该值时,激光器会自动降低输出功率,以保护激光器。 其中,T1模式配160镜头可在阳极铝上打黑,其效果类似皮秒激光器; T2模式配254镜头也可在阳极铝上打黑,效果可与SPI激光器的3号波形的

效果媲美; 而打标参数与SPI 激光器3号波形下的参数大致相同。 另,T2模式可用在含激光粉的PC,ABS材料上打白。 6.1ns T2模式,RR=200kHz,上升时间:3.8ns,50%时的脉冲宽度:8.4ns,10%时的脉冲宽度: 15.4ns T3模式, RR=125kHz,上升时间:3.8ns,50%时的脉冲宽度:14.4ns,10%时的脉冲宽度:21.1n s T4模式, RR=105kHz,上升时间:3.8ns,50%时的脉冲宽度:14.9ns,10%时的脉冲宽度:26.3ns T5模式, RR=85kHz,上升时间:4.0ns,50%时的脉冲宽度:14.6ns,10%时的脉冲宽度:31.5ns

T6模式, RR=60kHz,上升时间:3.2ns,50%时的脉冲宽度:14.8ns,10%时的脉冲宽度:53.6ns T7模式, RR=40kHz,上升时间:3.3ns,50%时的脉冲宽度:24.5ns,10%时的脉冲宽度:100.3ns

MIPS程序设计报告

组成原理实验报告 姓名学号 陈宝可 07055004 刘睿 07055013 林建财 07055040 指导老师:姜欣宁 2010年4月22日

一、总体设计思想 1.1 CPU简介 CPU是计算机的核心,其重要性好比大脑对于人一样,它负责处理、运算计算机内部的所有数据。CPU的种类决定了操作系统和相应的软件。CPU主要由运算器、控制器、寄存器组和内部总线等构成,是PC的核心,再配上储存器、输入/输出接口和系统总线组成为完整的PC(个人电脑)。 单周期CPU 的特点是每条指令的执行只需要一个时钟周期,一条指令执行完再执行下一条指 令。再这一个周期中,完成更新地址,取指,解码,执行,内存操作以及寄存器操作。由于每个时钟上 升沿时更新地址,因此要在上升沿到来之前完成所有运算,而这所有的运算除可以利用一个下降沿外, 只能通过组合逻辑解决。这给寄存器和存储器RAM的制作带来了些许难度。且因为每个时钟周期的时 间长短必须统一,因此在确定时钟周期的时间长度时,要依照最长延迟的指令时间来定,这也限制了它 的执行效率。 下图是cpu设计的思路: 1.2系统主要框架 第一台电子计算机与1946年2月14日诞生至今,计算机的发展迅速,经历了电子管,晶体管管,集成电路,大规模集成电路,超大规模集成电路的时代,现在集成电路的设计已经接近极限,不过在发

展历程中,计算机的核心框架并没有太多的改变,仍然是由五大部件组成:存储器、运算器、控制器、I/O设备。设计过程中主要以CPU(运算器+控制器)为中心。 如图是计算机组成原理图: CPU 的功能: 设计的cpu主要是由ALU(运算器)和CU(控制器)两个核心部件构成,另外设计一些辅助器件。ALU处理整个计算机的计算,设计的ALU只能进行简单的算术运算,并不能够实现很强大的计算功能,CU是整个计算机的控制部分,它能够接收外界的响应,并控制计算机的其他部件完成特定的功能,CU 和ALU共同组成cpu的核心部件,处理整个计算机的事件。 CPU开发的进程: 设计初始时,成员讨论cpu所能实现的功能,cpu的组成部分,所需要的开发工具、语言、平台、参考资料等,明确了设计思想后,小组进行明确的分工,现在设计过程已经从最初的讨论进入初步的实践,小组成员正按照各自的分工进行cpu的设计开发。 设计成员的分工: 本小组由三名成员,林建财主要完成设计思路提出和最终的整合,陈宝可主要完成各个模块的设计,刘睿主要完成报告的编写以及提出相关的意见,设计过程中成员需要相互配合,相互支持分工没有明显的界限,成员可以扬长避短,各展所长。 CPU设计的工具: 现在存在很多的cpu开发语言,如VHDL硬件描述语言,V erilog HDL描述语言等等,它们都是非常优秀的开发工具,鉴于知识的局限性,这里只列出我们所学的工具。 Quartus® II design 是最高级和复杂的,用于system-on-a-programmable-chip (SOPC)的设计环境。QuartusII design 提供完善的timing closure 和LogicLock? 基于块的设计流程。QuartusII design是唯一一个包括以timing closure 和基于块的设计流为基本特征的programmable logic device

TimeQuest快速入门实例及时序查看

1.在quartus中对设计进行时序分析 2.1TimeQuest 工具 Quartus? II TimeQuest Timing Analyzer是一个功能强大的ASIC型时序分析工具,能够以工业标准方法论来约束,分析和报告用户设计中所有逻辑的时序性能。这个工具是一个严格的静态工具,使用时不需要搭建硬件环境及进行调试。本节将介绍如何使用Quartus II TimeQuest Timing Analyzer工具的图形化功能来约束,分析及报告设计中的时序结果。 使用这个工具,我们要指定初始时序信息,包括时钟,时序例外以及信号传输中的到达和要求的时间。我们通过后缀名为sdc(Synopsys Design Constraints)的文件来指定时序要求,然后The Quartus II Fitter将优化逻辑布局等来满足我们的时序要求。 在时序分析过程中,Quartus II TimeQuest Timing Analyzer分析设计中的每一条时序路径,计算每条路径的延迟,检查是否存在时序违例,并且报告时序结果。一旦发现时序违例,可以精确定位到违例路径的时序细节,然后用户约束它以纠正违例。如果时序分析没有报告违例,那么恭喜你,在这个器件中的逻辑行为将与你的设计意图一致。 使用TimeQuest分析设计时序的一般步骤为: 图使用TimeQuest分析设计时序的一般步骤第一次编译时我们需要得到没有设置约束的时序结果,有助于我们给设计添加约束。第二次编译的时序需要把包含指定时序要求的文件(后缀为sdc 的文件)添加到工程文件中执行编译,这样工具就能够按照我们的时序要求来进行映射了。 2.2timequest快速入门示例 下面我们按照altera公司所给的timequest快速入门教程示例来讲解该时序分析工具的大致用法。使用的工具是目前使用最广泛的quartusII9.1版本

逻辑设计心得

序 很早之前就想对这几个月工作经历写的东西,一是作为自己的总结,二是自己也很 想将自己这段时间的一些经历和大家分享一下,希望对初学者而言能使得他们能少走一 些弯路。只是公司里的事情很多,最近经常加班,所以一直拖到现在。 能来到这家公司应该是一种缘份--缘起NIOS。当初三月份altera来我们学校建立SO PC实验室的时候自己还不知道NIOS是什么东西,只是想在altera的FAE讲完NIOS后多问他几个时序约束的问题,然后拷一份PPT回去。但是想不到因为那一份NIOS的培训资料,我 认识了edacn上的cawan,他给我讲了很多NIOS的东西,之后是丁哥在SOC版帖了位NIOS大赛的通知,然后我和队友就去报了名,并去川大参加了NIOS的培训,认识了峻龙的FAE- ---也是我现在的boss。在这里要谢谢cawan、丁哥、和我一起参加NIOS竞赛的队友刘科 以及我的BOSS,是他们让我有了这一段的经历。 在公司里的几个月,做的项目其实不多,但是收获还是有一些,我觉得收获最大的是 设计理念的改变,这也是我这段时间最想总结的,我会在后面逐渐阐述。 时序是设计出来的 我的boss有在华为及峻龙工作的背景,自然就给我们讲了一些华为及altera做逻辑 的一些东西,而我们的项目规范,也基本上是按华为的那一套去做。在工作这几个月中 ,给我感触最深的是华为的那句话:时序是设计出来的,不是仿出来的,更不是湊出来 的。 在我们公司,每一个项目都有很严格的评审,只有评审通过了,才能做下一步的工 作。以做逻辑为例,并不是一上来就开始写代码,而是要先写总体设计方案和逻辑详细 设计方案,要等这些方案评审通过,认为可行了,才能进行编码,一般来说这部分工作 所占的时间要远大于编码的时间。 总体方案主要是涉及模块划分,一级模块和二级模块的接口信号和时序(我们要求 把接口信号的时序波形描述出来)以及将来如何测试设计。在这一级方案中,要保证在 今后的设计中时序要收敛到一级模块(最后是在二级模块中)。什么意思呢?我们在做 详细设计的时候,对于一些信号的时序肯定会做一些调整的,但是这种时序的调整最多 只能波及到本一级模块,而不能影响到整个设计。记得以前在学校做设计的时候,由于 不懂得设计时序,经常因为有一处信号的时序不满足,结果不得不将其它模块信号的时 序也改一下,搞得人很郁闷。 在逻辑详细设计方案这一级的时候,我们已经将各级模块的接口时序都设计出来了 ,各级模块内部是怎么实现的也基本上确定下来了。 由于做到这一点,在编码的时候自然就很快了,最重要的是这样做后可以让设计会 一直处于可控的状态,不会因为某一处的错误引起整个设计从头进行。 做逻辑的难点在于系统结构设计和仿真验证 刚去公司的时候BOSS就和我讲,做逻辑的难点不在于RTL级代码的设计,而在于系统 结构设计和仿真验证方面。目前国内对可综合的设计强调的比较多,而对系统结构设计