锁存器原理

锁存器原理

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。

简单锁存器定义:

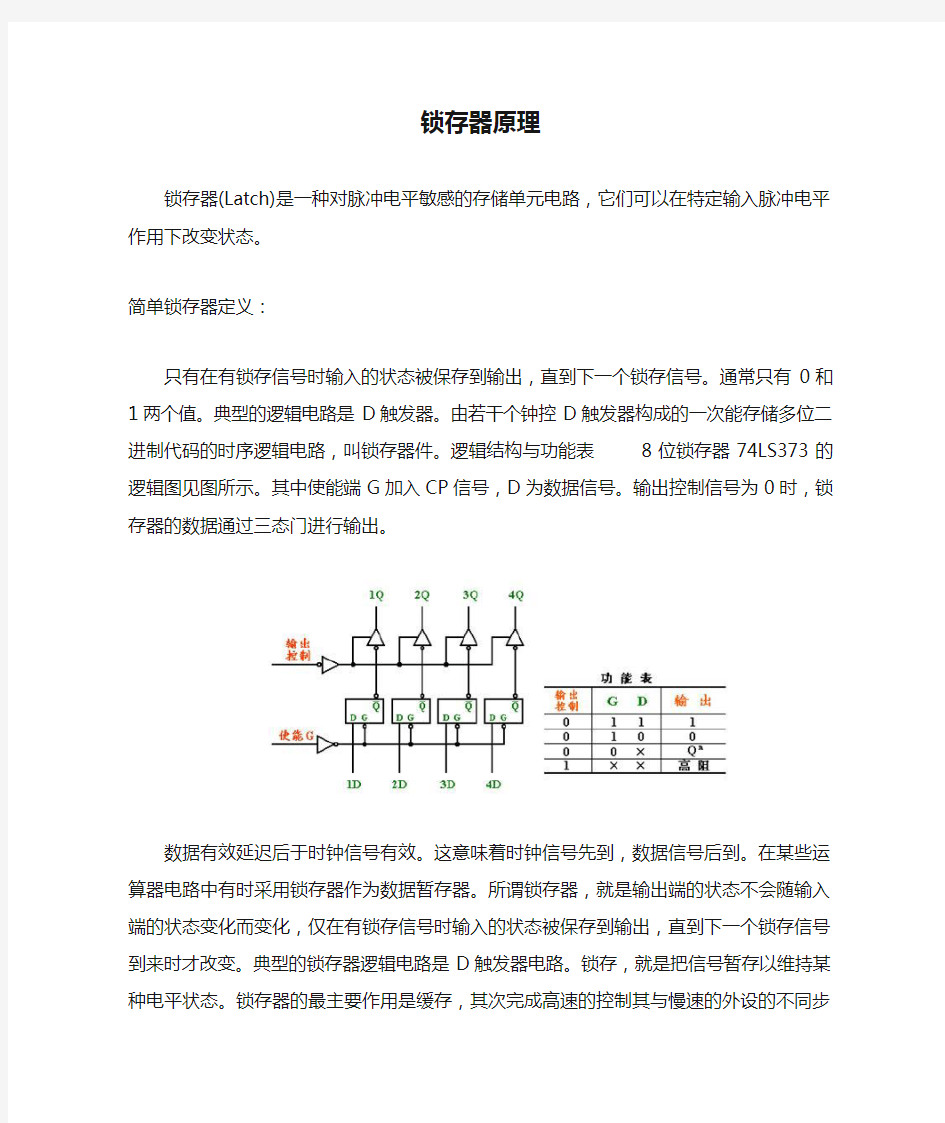

只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。通常只有0和1两个值。典型的逻辑电路是D触发器。由若干个钟控D触发器构成的一次能存储多位二进制代码的时序逻辑电路,叫锁存器件。逻辑结构与功能表8位锁存器74LS373的逻辑图见图所示。其中使能端G加入CP信号,D为数据信号。输出控制信号为0时,锁存器的数据通过三态门进行输出。

数据有效延迟后于时钟信号有效。这意味着时钟信号先到,数据信号后到。在某些运算器电路中有时采用锁存器作为数据暂存器。所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。典型的锁存器逻辑电路是D触发器电路。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制其与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O 口既能输出也能输入的问题。在某些应用中,单片机的I/O 口上需要外接锁存器。例如,当单片机连接片外存储器时,要接上锁存器,这是为了实现地址的复用。假设,MCU 端口其中的8 路的I/O 管脚既要用于地址信号又要用于数据信号,这时就可以用锁存器先将地址锁存起来。8051访问外部存储器时P0口和P2口共做地址总线,P0口常接锁存器再接存储器。以防止总线间的冲突。而P2口直接接存储器。因为单片机内部时序只能锁住P2口的地址,如果用P0口传输数据时不用锁存器的话,地址就改变了。看看8051单片机总线操作的时序图对我们很有帮助。由于数据总线、地址总线共用P0口,所以要分时复用。先送地址信息,由ALE使能锁存器将地址信息锁存在外设的地址端,然后送数据信息和读写使能信号,在指定的地址进行读写操作。使用锁存器来区分开单片机的地址和数据,8051系列的单片机用的比较多,也有一些单片机内部有地址锁存功能,如8279就不用锁存器了。

并不是一定要接锁存器,要看其地址线和数据线的安排,只有数据和地址线

合用的情况下才会需要锁存器,其目的是防止在传数据时,地址线被数据所影响!这是由单片机数据与地址总线复用造成的,接RAM 时加锁存器是为了锁存地址信号。如果单片机的总线接口只作一种用途,不需要接锁存器;如果单片机的总线接口要作两种用途,就要用两个锁存器。例如:一个口要控制两个LED,对第一个LED 送数据时,“打开”第一个锁存器而“锁住”第二个锁存器,使第二个LED 上的数据不变。对第二个LED 送数据时,“打开”第二个锁存器而“锁住”第一个锁存器,使第一个LED 上的数据不变。如果单片机的一个口要做三种用途,则可用三个锁存器,操作过程相似。然而在实际应用中,我们并不这样做,只用一个锁存器就可以了,并用一根I/O 口线作为对锁存器的控制之用(接74373 的LE,而OE可恒接地)。所以,就这一种用法而言,可以把锁存器视为单片机的I/O 口的扩展器。

摘要

随着电路工艺尺寸的精进,采用纳米级CMOS结构设计的电路对外部辐射现象越来越敏感,可能导致软错误的发生,因此对纳米级的电路设计中电路的软错误有严格要求。传统的容错方法在功耗、面积和性能方面耗费大量成本,因此存储单元的低功耗加固设计显得尤为重要。

本文采用纳米工艺设计了三个新型加固CMOS锁存器,拥有较低的功耗和较强的抗软错误率。并对面积和性能方面进行对比,采用hspice仿真结果,验证了设计的正确性,分析了该锁存器对电压、温度(PVT)的变化曲线

1、锁存器及抗辐射加固锁存器电路的原理(文献综述)

2、锁存器及其加固技术在国内外发展现状

3、现有锁存器的原理及分析

4、锁存器加固和抗辐射的原理和电路分析

5、三种新型的具有抗辐射加固锁存器的设计

6、电路设计,仿真结果及数据分析

7、结论