20152567-李莹-大数据实验报告1

《大数据技术原理与应用》实验报告

题目:安装Hadoop

班级:150409班

姓名:李莹

学号:20152567

日期:2018.5.18

实验1 安装Hadoop

一、实验环境

操作系统:Windows系统或者Ubuntu(或CentOS7)。

虚拟机软件:推荐使用的开源虚拟机软件为VirtualBox 。VirtualBox是一款功能强大的免费虚拟机软件,它不仅具有丰富的特色,而且性能也很优异,简单易用,可虚拟的系统包括Windows、Mac OS X、Linux、OpenBSD、Solaris、IBM OS2甚至Android 4.0

系统等操作系统。读者可以在Windows系统上安装VirtualBox软件,然后在VirtualBox上安装并且运行Linux操作系统。本次实验默认的Linux发行版为Ubuntu14.04。

二、实验内容

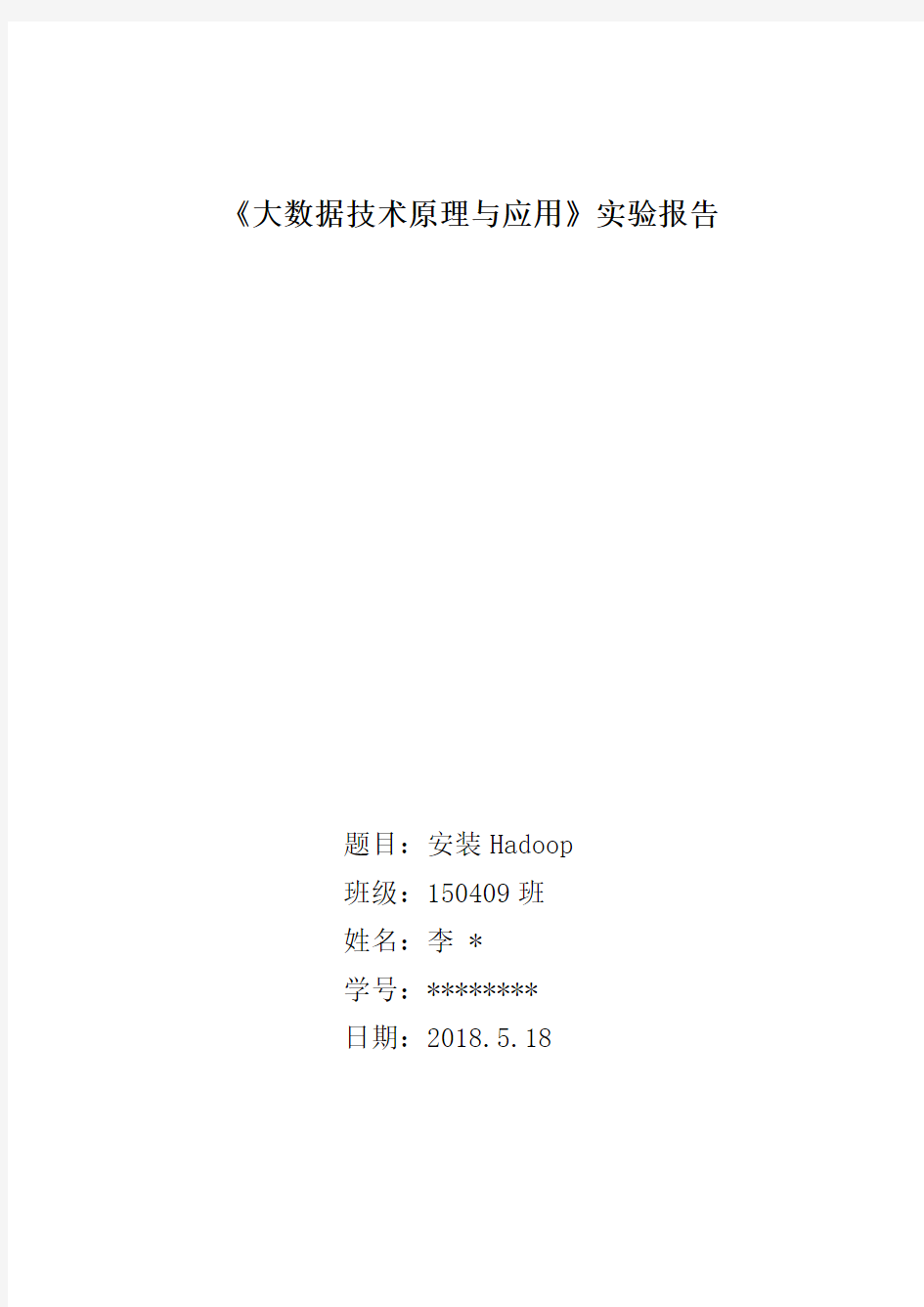

1.安装jdk

2.安装hadoop

四、实验结果

五、问题及解决方案

VirtualBox 对我的电脑并不适配,所以我用的是VMware Workstation 来实现实验。实验中为了实现虚拟机和Windows 连接,

安装VM Tools时遇到了一些问题,通过上网查询新教程使其成功实现。

基本运算器实验模板

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称计算机组成原理 项目名称基本运算器实验 班级 学号 姓名 同组人员无 实验日期 2016.5.17

一、实验目的与要求 (一) 实验目的: (1) 了解运算器的组成结构。 (2) 掌握运算器的工作原理。 (二) 实验要求: (1)实验之前,应认真准备,写出实验步骤和具体设计内容,否则实验效率会特别低,一次实验时间根本无法完成实验内容,即使基本作对了,也很难说懂得了些什么重要教学内容。 (2)应在实验前掌握所有控制信号的作用,写出实验预习报告并带入实验室。 (3)实验过程中,应认真进行实验操作,既不要因为粗心造成短路等事故而破坏设备,又要仔细思考实验有关内容,把自己想不明白的问题通过实验理解清楚。 二、实验逻辑原理图与分析 2.1 画实验逻辑原理图 xxxxxxxxxx xxxxxxxxxx 多路开关 判零 A=xx LOG=xx SHF=xx ART=xx 进位 B=xx & &

2.2 逻辑原理图分析 1)运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要 处理的数据存于暂存器A和暂存器B,三个部件同时接受来自A 和B 的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM)。 2)各部件对操作数进行何种运算由控制信号S3…S0和CN 来决定,任何时候, 多路选择开关只选择三部件中一个部件的结果作为ALU 的输出。如果是影响进位的运算,还将置进位标志FC,在运算结果输出前,置ALU 零标志。 ALU 中所有模块集成在一片CPLD 中。 三、数据通路图及分析 1、逻辑运算

20152567-李莹-实验报告4

《大数据技术原理与应用》实验报告 题目:MapReduce编程初级实践 姓名:李莹 日期:2018.6.22

实验四MapReduce编程初级实践 一、实验环境 操作系统:Linux 工具:Eclipse或者Intellij Idea等Java IDE 二、实验内容 1.安装Hbase 2.创建文件

3.上传文件夹 4.创建项目 5.编程 package org.apache.hadoop.examples; public class WordCount { public WordCount() { } public static void main(String[] args) throws Exception { Configuration conf = new Configuration(); String[] otherArgs = (new GenericOptionsParser(conf, args)).getRemainingArgs(); if(otherArgs.length < 2) {

System.err.println("Usage: wordcount

基本运算器实验定稿版

基本运算器实验 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称计算机组成原理 项目名称基本运算器实验 班级 学号 姓名 同组人员 实验日期 一、实验目的与要求 实验目的 (1)了解运算器的组成结构 (2)掌握运算器的工作原理 实验要求

(1)实验之前,应认真准备,写出实验步骤和具体设计内容,否则实验效率会很低,一次实验时间根本无法完成实验任务; (2)应在实验前掌握所以控制信号的作用,写出实验预习报告并带入实验室; (3)实验过程中,应认真进行实验操作,既不要因为粗心造成短路等事故而损坏设备,又要自习思考实验有关内容; (4)实验之后,应认真思考总结,写出实验报告,包括实验步骤和具体实验结果,遇到的问题和分析与解决思路。还应写出自己的心得体会,也可以对教学实验提出新的建议等。实验报告要上交老师。 二、实验逻辑原理图与分析 画实验逻辑原理图 逻辑原理图分析 上图为运算器原理图。如图所示运算器内部含有三个独立运算部件,分别为算术、逻辑和移位运算部件,要处理的数据存于暂存器A和暂存器B,三个部件同时接受来自A 和B的数据(有些处理器体系结构把移位运算器放于算术和逻辑运算部件之前,如ARM),各部件对操作数进行何种运算由控制信号S3…S0和CN来决定(三选一开关),任何时候,多路选择开关只选择三部件中一个部件的结果作为ALU的输出。如果是影响进位的运算,还将置进位标志FC,在运算结果输出前,置ALU零标志FZ。ALU中所有模块集成在一片CPLD中。

计算机组成原理实验-运算器组成实验报告

计算机组成原理课程实验报告 9.3 运算器组成实验 姓名:曾国江 学号: 系别:计算机工程学院 班级:网络工程1班 指导老师: 完成时间: 评语: 得分:

9.3运算器组成实验 一、实验目的 1.熟悉双端口通用寄存器堆的读写操作。 2.熟悉简单运算器的数据传送通路。 3.验证运算器74LS181的算术逻辑功能。 4.按给定数据,完成指定的算术、逻辑运算。 二、实验电路 ALU-BUS# DBUS7 DBUS0 Cn# C 三态门(244) 三态门(244)ALU(181) ALU(181) S3S2S1S0M A7A6A5A4F7F6F5F4 F3F2F1F0B3B2B1B0 Cn+4 Cn Cn Cn+4 LDDR2T2 T2 LDDR1LDRi T3 SW-BUS# DR1(273) DR2(273) 双端口通用寄存器堆RF (ispLSI1016) RD1RD0RS1RS0WR1WR0 数据开关(SW7-SW0)数据显示灯 A3A2A1A0B7B6B5B4 图3.1 运算器实验电路 LDRi T3A B 三态门 R S -B U S # 图3.1示出了本实验所用的运算器数据通路图。参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用寄存器堆RF 中。

RF(U30)由一个ispLSI1016实现,功能上相当于四个8位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从B端口(右端口)读出的通用寄存器,RD1、RD0用于选择从A端口(左端口)读出的通用寄存器。而WR1、WR0用于选择写入的通用寄存器。LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。RF的A、B端口分别与操作数暂存器DR1、DR2相连;另外,RF的B端口通过一个三态门连接到数据总线DBUS上,因而RF中的数据可以直接通过B端口送到DBUS 上。 DR1和DR2各由1片74LS273构成,用于暂存参与运算的数据。DR1接ALU的A输入端口,DR2接ALU的B输入端口。ALU由两片74LS181构成,ALU的输出通过一个三态门(74LS244)发送到数据总线DBUS上。 实验台上的八个发光二极管DBUS7-DBUS0显示灯接在DBUS上,可以显示输入数据或运算结果。另有一个指示灯C显示运算器进位标志信号状态。 图中尾巴上带粗短线标记的信号都是控制信号,其中S3、S2、S1、S0、M、Cn#、LDDR1、LDDR2、ALU_BUS#、SW_BUS#、LDRi、RS1、RS0、RD1、RD0、WR1、WR0都是电位信号,在本次实验中用拨动开关K0—K15来模拟;T2、T3为时序脉冲信号,印制板上已连接到实验台的时序电路。实验中进行单拍操作,每次只产生一组T1、T2、T3、T4时序脉冲,需将实验台上的DP、DB开关进行正确设置。将DP开关置1,DB开关置0,每按一次QD 按钮,则顺序产生T1、T2、T3、T4一组单脉冲。 三、实验设备 1.TEC-5计算机组成实验系统1台 2.逻辑测试笔一支(在TEC-5实验台上) 3.双踪示波器一台(公用) 4.万用表一只(公用) 四、实验任务 1、按图3.1所示,将运算器模块与实验台操作板上的线路进行连接。由于运 算器模块内部的连线已由印制板连好,故接线任务仅仅是完成数据开关、控制信号

计算机组成原理运算器实验—算术逻辑运算实验

实验报告 、实验名称 运算器实验—算术逻辑运算实验 、实验目的 1、了解运算器的组成原理。 2、掌握运算器的工作原理。 3、掌握简单运算器的数据传送通路。 4、验证运算功能发生器( 74LS181)的组合功能 三、实验设备 TDN-CM++ 计算机组成原理教学实验系统一套,导线若干四、实验原理 实验中所用的运算器数据通路如图1-1 所示。其中两片74LSl81以串行方式构成8 位字长的ALU,ALU 的输出经过一个三态门(74LS245)和数据总线相连。三态门由ALU-R 控制,控制运算器运算的结果能否送往总线,低电平有效。为实现双操作数的运算,ALU 的两个数据输入端分别由二个锁存器DR1、DR2 (由74LS273实现)锁存数据。要将数据总线上的数据锁存到DRl、DR2 中,锁存器的控制端LDDR1 和DDR2必须为高电平,同时由T4 脉冲到来。 数据开关“( INPUT DEVICE")用来给出参与运算的数据,经过三态 (74LS245) 后送入数据总线,三态门由SW—B控制,低电平有效。数据显示灯“( BUS UNIT") 已和数据总线相连,用来显示数据总线上的内容。 图中已将用户需要连接的控制信号用圆圈标明(其他实验相同,不再说明),其中除T4 为脉冲信号外,其它均为电平信号。由于实验电路中的时序信号均已连至“W/R UNIT ”的相应时序信号引出端,因此,在进行实验时,只需将“W /R UNIT"的T4接至“ STATE UNIT ”的微动开关KK2 的输入端,按动微动开关,即可获得实验所需的单脉冲。 ALU 运算所需的电平控制信号S3、S2、S1、S0 、Cn、M、LDDRl、 LDDR2 、ALU-B 、SW-B均由“ SWITCH UNIT ”中的二进制数据开关来模拟,其中Cn、ALU —B、SW 一 B 为低电平有效LDDR1 、LDDR2 为高电平有效。 对单总线数据通路,需要分时共享总线,每一时刻只能由一组数据送往总线。

运算器部件实验报告

实验一运算器部件实验报告 班级姓名学号日期 一、实验目的 ●熟悉与深入理解4位运算器芯片Am2901的功能和内部组成,运行中要求 使用的控制信号及其各自的控制作用。 ●熟悉与深入理解用4片4位的运算器芯片构成16位的运算器部件的具体方 案,各数据位信号、各控制位信号的连接关系。 ●熟悉与深入理解用2片GAL20v8芯片解决ALU最低位的进位输入信号和 最高、最低位的移位输入信号、实现4位的标志位寄存器的方案,理解为什么这些功能不能在运算器芯片之内实现而要到芯片之外另外处理。 ●明确教学计算机的运算器部件,使用总计24位的控制信号就完全确定了它 的全部运算与处理功能,脱机运算器实验中可以通过24位的微型开关提供这些控制信号。 二、实验说明 脱机运算器实验,是指让运算器从教学计算机整机中脱离出来,此时,它的全部控制与操作均需通过24位的微型开关来完成,通过开关、按键控制教学机的运算器完成指定的运算功能,并通过指示灯观察运算结果。 三、实验要求 1、实验之前认真预习,写出预习报告,包括操作步骤,实验过程所用数据和运行结果等 2、实验过程当中,要仔细进行,防止损坏设备,分析可能遇到的各种现象,判断结果是否正确,记录运行结果 3、实验之后,认真写出实验报告,包括对遇到的各种现象的分析,实验步骤和实验结果,自己在这次实验的心得体会与收获。 四、实验所使用到的控制信号 AM2901所用的控制信号

1、将教学机设置为单步、16位、脱机状态下,即把教学机左下方的5个控制开关置为1XX00。 2、按一下RESET按键,进行初始化。 3、按照指定功能给出控制信号和数据信息,观察各信号指示灯状态。 4、按压START键,给出脉冲信号,观察各信号灯状态。 六、实验内容 1、下表中所列操作在教学机上进行运算器脱机实验。并将结果填入表中。 运算器功能所用到的控制信号

大数据分析报告与挖掘实验报告材料

《数据挖掘》实验报告 目录 1.关联规则的基本概念和方法 (1) 1.1数据挖掘 (1) 1.1.1数据挖掘的概念 (1) 1.1.2数据挖掘的方法与技术 (1) 1.2关联规则 (2) 1.2.1关联规则的概念 (2) 1.2.2关联规则的实现——Apriori算法 (3) 2.用Matlab实现关联规则 (5) 2.1Matlab概述 (5) 2.2基于Matlab的Apriori算法 (6) 3.用java实现关联规则 (10) 3.1java界面描述 (10) 3.2java关键代码描述 (13) 4、实验总结 (18) 4.1实验的不足和改进 (18) 4.2实验心得 (19)

1.关联规则的基本概念和方法 1.1数据挖掘 1.1.1数据挖掘的概念 计算机技术和通信技术的迅猛发展将人类社会带入到了信息时代。在最近十几年里,数据库中存储的数据急剧增大。数据挖掘就是信息技术自然进化的结果。数据挖掘可以从大量的、不完全的、有噪声的、模糊的、随机的实际应用数据中,提取隐含在其中的,人们事先不知道的但又是潜在有用的信息和知识的过程。 许多人将数据挖掘视为另一个流行词汇数据中的知识发现(KDD)的同义词,而另一些人只是把数据挖掘视为知识发现过程的一个基本步骤。知识发现过程如下:·数据清理(消除噪声和删除不一致的数据) ·数据集成(多种数据源可以组合在一起) ·数据转换(从数据库中提取和分析任务相关的数据) ·数据变换(从汇总或聚集操作,把数据变换和统一成适合挖掘的形式) ·数据挖掘(基本步骤,使用智能方法提取数据模式) ·模式评估(根据某种兴趣度度量,识别代表知识的真正有趣的模式) ·知识表示(使用可视化和知识表示技术,向用户提供挖掘的知识)。 1.1.2数据挖掘的方法与技术 数据挖掘吸纳了诸如数据库和数据仓库技术、统计学、机器学习、高性能计算、模式识别、神经网络、数据可视化、信息检索、图像和信号处理以及空间数据分析技术的集成等许多应用领域的大量技术。数据挖掘主要包括以下方法。 神经网络方法:神经网络由于本身良好的鲁棒性、自组织自适应性、并行处理、分布存储和高度容错等特性非常适合解决数据挖掘的问题,因此近年来越来越受到人们的关注。典型的神经网络模型主要分3大类:以感知机、bp反向传播模型、函数型网络为代表的,用于分类、预测和模式识别的前馈式神经网络模型;以hopfield的离散模型和连续模型为代表的,分别用于联想记忆和优化计算的反馈式神经网络模型;以art模型、koholon模型为代表的,用于聚类的自组织映射方法。神经网络方法的缺点是"黑箱"性,人们难以理解网络的学习和决策过程。 遗传算法:遗传算法是一种基于生物自然选择与遗传机理的随机搜索算法,是一种仿生全局优化方法。遗传算法具有的隐含并行性、易于和其它模型结合等性质使得它在数据挖掘中被加以应用。sunil已成功地开发了一个基于遗传算法的数据挖掘工具,利用该工具对两个飞机失事的真实数据库进行了数据挖掘实验,结果表明遗传算法是进行数据挖掘的有效方法之一。遗传算法的应用还体现在与神经网络、粗糙集等技术的结合上。如利用遗传算法优化神经网络结构,在不增加错误率的前提下,删除多余的连接和隐层单元;用遗传算法和bp算法结合训练神经网络,然后从网络提取规则等。但遗传算法的算法较复杂,收敛于局部极小的较早收敛问题尚未解决。 决策树方法:决策树是一种常用于预测模型的算法,它通过将大量数据有目的分类,从

嵌入式--计算器--实验报告

计算器设计实验报告 一、实验设计主要分工 04009320 文斌:算法设计,LCD显示。 04** 张希:界面(按钮控件)设计,文件内容读取。 共同调试、完善设计。 二、程序设计实现功能效果 (1)支持整数、小数基本加减乘除运算; (2)有优先级的判别计算。优先级由高到低一次为括号运算、乘除运算、加减运算。(3)支持键盘输入和触摸屏输入; (4)能读取指定目录下文本内容(内容为计算表达式)并计算得出结果,将内容和结果显示在LCD上。 程序任务开始后,等待键盘或触摸屏的输入。输入键有0~9数字键、+-*/()运算符、del退格键、clear清屏键、read读指定目录文本内容并计算键、enter'='键、‘.’小数点键。 每当有字符输入时,触摸屏相应键显示“AAA”,100ms后恢复原相应按键符号,同时LCD 屏幕上显示相应字符。当输入'del'键时,屏幕显示去掉最后一位字符。当输入'='号后,得出计算结果,结果显示于表达式的下一行。若是除零错误,则结果显示为“/0ERROR!”。若有非法字符(触摸点不能识别为设计按键符则视为非法字符),则结果输出为“Syntax Error!!”。若表达式有运算符连续输入,则忽略前面的运算符,只取最后一位运算符计算,正常显示数字结果。当输入'clear'键时,情况显示区域。当输入'read'键时,从指定目录文本文件中读取表达式并计算。将表达式内容和计算结果显示在LCD上。 三、程序算法实现 1、计算算法 首先将输入的0~9数字、+-*/()运算符的内容存储于一个全局变量cal[number]中, 表达为中缀表达式。用void str2repol()函数,将输入字符串cal[number]转换成逆波 兰表达式并存于全局数组char repol[maxs]中。str2repol()函数中缀表达式转成逆波兰 后缀表达式算法如下: (1)首先构造一个运算符栈stack[maxs],此运算符在栈内遵循越往栈顶优先级越高的 原则。

计算机组成原理实验报告运算器组成存储器

计算机组成原理实验报告 一、实验1 Quartus H的使用 一.实验目的 掌握Quartus H的基本使用方法。 了解74 1 38(3:8)译码器、74244、74273的功能。 利用Quartus H 验证74138 (3: 8)译码器、74244、74273 的功能。 二.实验任务 熟悉Quartus H中的管理项目、输入原理图以及仿真的设计方法与流程。新建项目,利用原理编辑方式输入74138、74244、74273的功能特性,依照其功能表分别进行仿真,验证这三种期间的功能。 三.74138、74244、74273的原理图与仿真图 1.74138 的原理图与仿真图 74244的原理图与仿真图 1.

实验2运算器组成实验 一、 实验目的 1. 掌握算术逻辑运算单元(ALU 的工作原理。 2. 熟悉简单运算器的数据传送通路。 3. 验证4位运算器(74181)的组合功能。 4. 按给定数据,完成几种指定的算术和逻辑运算。 二、 实验电路 附录中的图示出了本实验所用的运算器数据通路图。 8位字长的ALU 由2 片74181构成。2片74273构成两个操作数寄存器 DR1和DR2用来保存参 与运算的数据。DR1接ALU 的A 数据输入端口,DR2接 ALU 的B 数据输入端 口,ALU 的数据输出通过三态门74244发送到数据总线BUS7-BUS 上。参与 运算的数据可通过一个三态门74244输入到数据总线上,并可送到DR1或 DR2 暂存。 图中尾巴上带粗短线标记的信号都是控制信号。除了 T4是脉冲信号外,其 4. 74273的原理图与仿真图、

他均为电位信号。nCO, nALU-BUS nSW-BU鈞为低电平有效。 三、实验任务按所示实验电路,输入原理图,建立.bdf 文件。 四. 实验原理图及仿真图 ,然后利用ALU的直通功能,检查DR1 DR2中是否保存了所置的数。 其实验原理图如下: 波形图如下: 实验 3 半导体存储器原理实验 (一)、实验目的 (1)熟悉静态随机存储器RAM和只读存储器ROM勺工作特性和使用方法; (2)熟悉半导体存储器存储和读出数据的过程; (3)了解使用半导体存储器电路时的定时要求。 (二)、实验要求 利用Quartus H器件库提供的参数化存储单元,设计一个由128X8 位的RAM和128X8位的ROM勾成的存储器系统。请设计有关逻辑电路,要求仿真通过,并设计波形文件,验证该存储器系统的存储与读出。 (三)、实验原理图与仿真图 ram内所存储的数据: rom 内所存储的数据: 仿真图如下: (四)心得体会 本次试验中,我们应该熟练掌握Quartus H软件的使用方法;熟悉静态随机存储器RAM和只读存储器RO啲工作特性和使用方法;熟悉半导体存储器存

大数据实验报告

学生实验报告册 (理工类) 课程名称:大型数据库技术专业班级:12计算机科学与技术(1)学生学号:学生姓名: 所属院部:计算机工程学院指导教师:陈爱萍

2014——20 15学年第2 学期 金陵科技学院教务处制

实验报告书写要求 实验报告原则上要求学生手写,要求书写工整。若因课程特点需打印的,要遵照以下字体、字号、间距等的具体要求。纸张一律采用A4的纸张。 实验报告书写说明 实验报告中一至四项内容为必填项,包括实验目的和要求;实验仪器和设备;实验内容与过程;实验结果与分析。各院部可根据学科特点和实验具体要求增加项目。 填写注意事项 (1)细致观察,及时、准确、如实记录。 (2)准确说明,层次清晰。 (3)尽量采用专用术语来说明事物。 (4)外文、符号、公式要准确,应使用统一规定的名词和符号。 (5)应独立完成实验报告的书写,严禁抄袭、复印,一经发现,以零分论处。 实验报告批改说明 实验报告的批改要及时、认真、仔细,一律用红色笔批改。实验报告的批改成绩采用百分制,具体评分标准由各院部自行制定。 实验报告装订要求 实验批改完毕后,任课老师将每门课程的每个实验项目的实验报告以自然班为单位、按学号升序排列,装订成册,并附上一份该门课程的实验大纲。

实验项目名称:Oracle数据库安装与配置实验学时: 1 同组学生姓名:实验地点:1316 实验日期:2015/3/27 实验成绩: 批改教师:陈爱萍批改时间:

实验1:Oracle数据库安装与配置 一、实验目的和要求 (1)掌握Oracle数据库服务器的安装与配置。 (2)了解如何检查安装后的数据库服务器产品,验证安装是否成功。 (3)掌握Oracle数据库服务器安装过程中出现的问题的解决方法。 (4)完成Oracle 11g数据库客户端网路服务名的配置。 (5)检查安装后的数据库服务器产品可用性。 (6)解决Oracle数据库服务器安装过程中出现的问题。 二、实验设备、环境 设备:奔腾Ⅳ或奔腾Ⅳ以上计算机 环境:WINDOWS 7、ORACLE 11g中文版 三、实验步骤 (1)从Oracle官方网站下载与操作系统匹配的Oracle 11g数据库服务器和客户机安装程序。 (2)解压Oracle 11g数据库服务器安装程序,进行数据库服务器软件的安装。

java计算器实验报告

Java计算器实验报告 计算机032 胡勇健 03095218 2005年5月5日

目录 1.设计名称与要求 2.各模块功能的介绍和实现3.系统的特色和不足4.参考书

一. 实验名称及其要求: A)名称: java计算器的设计 B)要求:1.实验目的:图形界面设计。 熟悉java.awt包中的组件,掌握图形界面设计方法,理解委托事件处理模型。 2.题意: 请设计并实现Windows系统中“计算器”的窗口及功能。 3.实验要求: (1)设计图形界面添加菜单:窗口上添加各种组件及菜单,并处理组件及菜单的事件监听程序。 (2)运算:实现多种运算,保证运算正确性。 二.各模块功能的介绍和实现: A)GUI图形界面的组件: a)所用到的Java类库包: java.awt.*; 基本的图形界面组件来源于awt包。 java.awt.event.*; 事件的属性处理来源于awt.event包。 javax.swing.*; swing组件增加了awt包中所不具备的各种优越功能。 java.awt.datatransfer.*; 用于计算器与外部的程序进行复制粘贴。 b)所用的各部分图形组件的定义: Frame mainFrame; //主框架 JTextField answerText; //显示计算结果 JTextField memoryState; //显示计算器内存的使用情况MenuBar menuGroup; //菜单栏 Menu editMenu,viewMenu,helpMenu; //编辑,查看,帮助菜单 MenuItem copyItem,pasteItem; //复制,粘贴 MenuItem standardModel; //标准型 CheckboxMenuItem numGroup; //数字分组 MenuItem aboutCal; //关于计算器 Button buttonBackSpace,buttonCE,buttonC; //退格,清除,清空按钮 Button buttonMC,buttonMR,buttonMS,buttonMADD; //内存操作按钮 Button buttonNum[]; //数字按钮 Button buttonAdd,buttonSub,buttonMul,buttonDiv; //+,-,*,/ Button buttonDot,buttonSign,buttonEqual; //. +/- =

计算机组成原理实验1-运算器

《计算机组成原理》 实验报告 实验一运算器实验

一、实验目的 1.掌握运算器的组成及工作原理; 2.了解4位函数发生器74LS181的组合功能,熟悉运算器执行算术操 作和逻辑操作的具体实现过程; 3.验证带进位控制的74LS181的功能。 二、实验环境 EL-JY-II型计算机组成原理实验系统一套,排线若干。 三、实验内容与实验过程及分析(写出详细的实验步骤,并分析实验结果) 实验步骤:开关控制操作方式实验 1、按图1-7接线图接线: 连线时应注意:为了使连线统一,对于横排座,应使排线插头上的箭头面向自己插在横排座上;对于竖排座,应使排线插头上的箭头面向左边插在竖排座上。 图1-1 实验一开关实验接线图 2、通过数据输入电路的拨开关开关向两个数据暂存器中置数: 1)拨动清零开关CLR,使其指示灯。再拨动CLR,使其指示灯亮。置ALU-G =1:关闭ALU的三态门;再置C-G=0:打开数据输入电路的三态门; 2)向数据暂存器LT1(U3、U4)中置数:

(1)设置数据输入电路的数据开关“D15……D0”为要输入的数值; (2)置LDR1=1:使数据暂存器LT1(U3、U4)的控制信号有效,置LDR2=0:使数据暂存器LT2(U5、U6)的控制信号无效; (3)按一下脉冲源及时序电路的【单脉冲】按钮,给暂存器LT1送时钟,上升沿有效,把数据存在LT1中。 3)向数据暂存器LT2(U5、U6)中置数: (1)设置数据输入电路的数据开关“D15……D0”为想要输入的数值; (2)置LDR1=0:数据暂存器LT1的控制信号无效;置LDR2=1:使数据暂存器LT2的控制信号有效。 (3)按一下脉冲源及时序电路的“单脉冲”按钮,给暂存器LT2送时钟,上升沿有效,把数据存在LT2中。 (4)置LDR1=0、LDR2=0,使数据暂存器LT1、LT2的控制信号无效。 4)检验两个数据暂存器LT1和LT2中的数据是否正确: (1)置C-G=1,关闭数据输入电路的三态门,然后再置ALU-G=0,打开ALU 的三态门; (2)置“S3S2S1S0M”为“F1”,数据总线显示灯显示数据暂存器LT1中的数,表示往暂存器LT1置数正确; (3)置“S3S2S1S0M”为“15”,数据总线显示灯显示数据暂存器LT2中的数,表示往暂存器LT2置数正确。 3、验证74LS181的算术和逻辑功能: 按实验步骤2往两个暂存器LT1和LT2分别存十六进制数“1234H”和“5678H”,在给定LT1=1234H、LT2=5678H的情况下,通过改变“S3S2S1S0MCn”的值来改变运算器的功能设置,通过数据总线指示灯显示来读出运算器的输出值F,填入上表中,参考表1-1的功能表,分析输出F值是否正确。分别将“AR”开关拨至“1”和“0”的状态,观察进位指示灯“CY”的变化并分析原因。 实验结果表为:

运算器实验报告模板

脱机运算器实验报告 理论课教师姓名:高金山实验指导教师:刘万成 组号:姓名:闫麟阁学号:12281212 实验目的: (1)了解脱机操作下AM2901运算器的功能与控制信号的使用,了解运算器AM2901的内部结构及工作时序,观察运算器运算的结果对状态标志的影响。 (2)深入了解AM2901运算器的功能与具体用法,掌握用AM2901完成各种运算操作时各控制信号的使用,观察指令执行的结果对状态标志的影响;了解4片AM2901的级联方式,深化运算器部件的组成、设计、控制与使用等诸项知识。 实验内容: 1.将教学机左下方的5个拨动开关置为1XXOO(单步、16位、脱机);先按一下“RESET”按键,再按一下“START”按键,进行初始化。 2.接下来,按下表所列的操作在机器上进行运算器脱机实验,将结果填入表中:其中D1取为0101H,D2取为1010H;通过两个12位的红色微型开关向运算器提供控制信号,通过16位数据开关向运算器提供数据,通过指示灯观察运算结果及状态标志。 运算器实验(1) 实验结果分析(每人选择2个操作运算进行控制信号取值和运算结果值的分析):

此式的功能是R0∨R1然后将值赋给R1,由于有两个值,所以A、B口均有对应地址输入,B 对应的是R0,所以B的地址为0001,A对应的是R1,所以A的地址为0000。因为最后的值存储到B口多对应的地址并输出,所以I8-I6所选值为011;该式实现的是并运算,所以I5-I3所选值为011;数据来源是A和B,所以I2-I0所选值为001。 该式接受ALU的标志位输出的值,所以SST所选值为001;该式执行的并(SUB),所以SSH SCI 所选值为000。 因为R0=0101,R1=1010,所以按START前ALU的输出值为0F0F,故输出值为0F0F。 此时的功能是实现R0的逻辑左移功能,由于只有一个值,所以只有B口有对应地址输入,B对应的是R0,所以B的地址为0000。因为最后的值存储到B口对应的地址并输出,所以I8-I6所选值为111,;该式实现的是逻辑左移,所以I5-I3取000(加法);数据来源是B,所以I2-I0所选值为011。 该式是左移操作,另三个标志不变,所以SST所选值为110;SSH SCI所选值为100。 因为R0=FEFE,实现逻辑左移后补0,所以按START之前R0为FEFE,按START后R0变为FDFC。 运算器实验(2) 实验步骤 将教学机左下方的5个拨动开关置为1XX00(单步、16位、脱机);先按一下“RESET”按键,再按一下“START”按键,进行初始化。接下来,按下表所列的操作在机器上进行运算器脱机实验,将结果填入表中:

大数据挖掘weka大数据分类实验报告材料

一、实验目的 使用数据挖掘中的分类算法,对数据集进行分类训练并测试。应用不同的分类算法,比较他们之间的不同。与此同时了解Weka平台的基本功能与使用方法。 二、实验环境 实验采用Weka 平台,数据使用Weka安装目录下data文件夹下的默认数据集iris.arff。 Weka是怀卡托智能分析系统的缩写,该系统由新西兰怀卡托大学开发。Weka使用Java 写成的,并且限制在GNU通用公共证书的条件下发布。它可以运行于几乎所有操作平台,是一款免费的,非商业化的机器学习以及数据挖掘软件。Weka提供了一个统一界面,可结合预处理以及后处理方法,将许多不同的学习算法应用于任何所给的数据集,并评估由不同的学习方案所得出的结果。 三、数据预处理 Weka平台支持ARFF格式和CSV格式的数据。由于本次使用平台自带的ARFF格式数据,所以不存在格式转换的过程。实验所用的ARFF格式数据集如图1所示 图1 ARFF格式数据集(iris.arff)

对于iris数据集,它包含了150个实例(每个分类包含50个实例),共有sepal length、sepal width、petal length、petal width和class五种属性。期中前四种属性为数值类型,class属性为分类属性,表示实例所对应的的类别。该数据集中的全部实例共可分为三类:Iris Setosa、Iris Versicolour和Iris Virginica。 实验数据集中所有的数据都是实验所需的,因此不存在属性筛选的问题。若所采用的数据集中存在大量的与实验无关的属性,则需要使用weka平台的Filter(过滤器)实现属性的筛选。 实验所需的训练集和测试集均为iris.arff。 四、实验过程及结果 应用iris数据集,分别采用LibSVM、C4.5决策树分类器和朴素贝叶斯分类器进行测试和评价,分别在训练数据上训练出分类模型,找出各个模型最优的参数值,并对三个模型进行全面评价比较,得到一个最好的分类模型以及该模型所有设置的最优参数。最后使用这些参数以及训练集和校验集数据一起构造出一个最优分类器,并利用该分类器对测试数据进行预测。 1、LibSVM分类 Weka 平台内部没有集成libSVM分类器,要使用该分类器,需要下载libsvm.jar并导入到Weka中。 用“Explorer”打开数据集“iris.arff”,并在Explorer中将功能面板切换到“Classify”。点“Choose”按钮选择“functions(weka.classifiers.functions.LibSVM)”,选择LibSVM分类算法。 在Test Options 面板中选择Cross-Validatioin folds=10,即十折交叉验证。然后点击“start”按钮:

实验一 运算器实验(1)

级班学号姓名 实验报告 实验一运算器实验 一、实验目的: 1、掌握简单运算器的数据传送通路; 2、验证运算功能发生器(74LS181)的组合功能; 3、验证带进位控制的算术运算功能发生器的功能; 4、按指定数据完成几种指定的算术运算。 二、实验设备 DVCC-C5JH计算机组成原理教学实验系统一台,排线若干。 三、实验原理 1、实验中所用的运算器数据通路图如附A图1-3所示。其中运算器由两片74LS181以并/串形式构成8位字长的ALU。运算器的输出经过一个三态门(74LS245)和数据总线相连,运算器的两个数据输入端分别由二个锁存器(74LS373)锁存,锁存器的输入连至数据总线,数据开关(“INPUT DEVICE”)用来给出参与运算的数据,并经过一三态门(74LS245)和数据总线相连,数据显示灯(“BUS UNIT”)已和数据总线相连,用来显示数据总线内容。 2、控制信号说明: T4:脉冲信号;实验时,将W/R UNIT的T4接至STATE UNIT的微动开关KK2的输出端,按动微动开关,即可获得实验所需的单脉冲。 S3~S0、M:运算器的功能控制信号;可参见74181芯片的功能表P64。 Cn:进位控制信号,低电平有效。 LDDR1、LDDR2:数据寄存器DR1和DR2的数据装载控制信号,高电平有效。ALU-B:该控制信号控制是否将ALU的结果送到总线上,低电平有效。

SW-B :三态门开关信号,控制是否打开三态门,低电平有效。 四、实验内容 1、算术逻辑运算实验: 实验步骤: ①按图1-2连接路线,仔细检查无误后,接通电源; ②用二进制数码开关向DR1和DR2寄存器置数。 A )数据开关置01100101; B )设置switch unit :ALU-B=1 SW-B=0 LDDR1=1 LDDR2=0 C )按动KK2给出一个单脉冲信号,即T4=┎┒ D )数据开关置10100111; E )设置switch unit :LDDR1=0 LDDR2=1 F )按动KK2给出一个单脉冲信号。 ③检验DR1和DR2中存的数是否正确: A )设置switch unit :SW-B=1 ALU-B=0 B )设置switch unit :当S 3S 2S 1S 0M=00000,总线显示灯显示DR1中的数,而 置为S 3S 2S 1S 0M=01010,总线显示灯显示DR2中的数。 ④验证74LS181的算术运算和逻辑运算功能:[给定A=(DR1)=65 H ,B=(DR2)=A7 H] A )改变运算器的功能设置,观察运算器的输出,填入下表: DR1 DR2 S 3S 2S 1S 0 M=1(算术运算) M=0(逻辑运算) Cn=1 (无进位) Cn=0 (有进位) 65 A7 0000 01100101 01100110 10011010 65 A7 0001 11100111 11101000 00011000 65 A7 0010 01111101 01111110 10000010 65 A7 0011 11111111 00000000 00000000 65 A7 0100 10100101 10100110 11011010 65 A7 0101 00100111 00101000 01011000

计算机组成原理运算器实验报告

计算机组成原理实验一 运算器实验 一、实验目的: 1、掌握简单运算器的数据传输方式。 2、验证运算功能发生器(74LS181)及进位控制的组合功能。 二、实验要求: 完成不带进位及带进位算数运算实验、逻辑运算实验,了解算数逻辑运算单元的运用。 三、实验原理: 74LS181是4位算术逻辑运算器,用两个74LS181并联可以实

现8位运算,为了实现双操作的运算,ALU 的输入端分别由两个锁存器DR1,DR2锁存数据。数据显示灯和数据总线相连接,用来显示数据总线上的内容。由于实验电路中的时序信号均已连接至W /RUIT相应的时序信号引出端,只要微动开关,即可获得实验所需的单脉冲。 四、 实验连接: 1.八位运算器控制信号连接: S3,S2,S1,S0,M ,/CN ,LDDR1,LDDR2,LDCZY ,/SW-B ,/ALU-B ,Cn+4 Cn+4I 2.完成连接并检查无误后接通电源。 五、实验仪器状态设定: 在闪动的“P.”状态下按动“增址”命令键,使LED 显示器自左向右第一位显示提示符“H ”,表示本装置已进入手动单元实验状态。 五、 实验项目: (一)算数运算实验 拨动二进制数据开关向DR1和DR2寄存器置数(灯亮为1,灯灭为0)。 步骤如下: [CBA=001] [LDDR1=1] [LDDR1=0] [LDDR2=0] [LDDR2=1] 数据开关 (01100101) 三态门 寄存器DR1 (01100101) 数据开关 (10100111) 寄存器DR2 (10100111)

[“按STEP”] [“按STEP”] 然后检查数据: 1.关闭数据输入三态门(CBA=000) 2.打开ALU输出三态门(CBA=010) 3.当置S3,S2,S1,S0,M为11111时,总线指示灯显示DR1中的数 4.当置S3,S2,S1,S0,M为10101时,总线指示灯显示DR2中的数 算数运算(不带进位)实验: 置CBA=010,S3,S2,S1,S0,M,/CN为100101,LDCZY=0,则数据总线指示灯显示00001100(0CH) (二)进位控制实验 (1)进位标志清零 CBA=000 置S3,S2,S1,S0,M为00000 置/CN为0,LDCZY为1 按STEP (2)向DR1和DR2置数(同上) (3)验证进位运算及进位锁存功能,使/CN=1,LDCZY=1,来进行算数运算。 给定DR1=65,DR2=A7,改变运算器功能(逻辑或非运算方法见逻辑运算实验),得到运算器输出记录如下: DR1 DR2 S3 S2 S1 S0 M=0 (算数运算) M=1 (逻辑运算)CN=1 无进位 CN=0 有进位 65 A7 0000 F=(65)F=(66)F=(9A) 0001 F=(E7)F=(E8)F=(18) 0010 F=(7D)F=(7E)F=(82) 0011 F=(FF)F=(0)F=(0) 0100 F=(A5)F=(A6)F=(82) 0101 F=(27)F=(B8)F=(58) 0110 F=(BD)F=(-42)F=(C2) 0111 F=(3F)F=(40)F=(40) 1000 F=(8A)F=(E3)F=(BF) 1001 F=(C)F=(10D)F=(3D) 1010 F=(A2)F=(BE)F=(A7) 1011 F=(25)F=(7D)F=(7D) 1100 F=(CA)F=(CB)F=(1) 1101 F=(4C)F=(DD)F=(7D) 1110 F=(E2)F=(E3)F=(77) 1111 F=(64)F=(65)F=(65)

计算机组成原理实验-运算器实验报告

1.逻辑运算 (1)S3S2S1S0=0000时,F=A,例如:当A=00010101,B=01101001时 F=00010101; 当A=01011000时,B=01011110时 F=01011000 (2)S3S2S1S0=0001时,F=B,例如: 当A=10110111,B=01110010时 F=01110010 当A=11100011,B=01010110 F=01010110 (3)S3S2S1S0=0010时,F=AB。例如:当A=10110010,B=10010111时 F=10010010 当A=11000011,B=00111100时 F=00000000 (4)S3S2S1S0=0011时,F=A+B。例如:当A=00110101,B=11001010时, F=11111111 当A=01011011,B=11000101时 F=11011111 (5)S3S2S1S0=0100时,F=/A。例如:

当A=00110100,B=11010010时, F=11001011 当A=01001111,B=10100101时 F=10110000 2.移位运算 (1)S3S2S1S0=0101时,F=A逻辑右移B(取低三位)位。例如: 当A=01000101,B=00000010时, F=00010001 当A=01011011,B=00000101时 F=00000010 (2)S3S2S1S0=0110时,F=A逻辑左移B(取低三位)位。例如: 当A=00110101,B=00000011时, F=10101000 当A=01101011,B=00000001时 F=11010110 (3)S3S2S1S0=0111时,F=A算术右移B位。例如:当A=01110101,B=00000010时, F=00011101 当A=01000111,B=00000101时