DESIGNING INTRUSION DETECTION SYSTEM FOR FPGA TECHNOLOGY ABSTRACT

DESIGNING INTRUSION DETECTION SYSTEM FOR

FPGA TECHNOLOGY

Petr KOBIERSKY,Bachelor Degree Programme(3)

Dept.of Computer Systems,FIT,BUT

E-mail:xkobie00@stud.?t.vutbr.cz

Supervised by:Ing.Jan Koˇr enek

ABSTRACT

Intrusion Detection System(IDS)is an integrated software/hardware tool capable of detecting unauthorised access to computer systems and malicious network traf?c such as viruses,trojan horses and worms.This paper introduce architecture of the hardware accelerated IDS for Field-Programmable Gate Arrays(FPGAs).The approach based on on Nondeterministic Finite Automation(NFA)[1]with optimalization focused to Snort[2] ruleset is used for payload scanning.Proposed architecture was implemented in VHDL and was tested in a hardware.

1úVOD

V posledním desetiletíjsme svˇe dky vyrazného rozvoje sít’ovych technologií.S roz-vojem Internetu se ale takémno?ívirovéhrozby aútoky na poˇcítaˇc ovésystémy.K zaji?tˇe níbezpeˇc nosti poˇcítaˇc ovych sítíji?nestaˇcí?rewaly,ale je nutnépou?ít so?stikovanˇe j?ísys-témy pro detekci nebezpeˇc ného provozu(IDS).IDS kombinuje funkci klasi?kace paket?u, kteráje obsa?enáv ka?dém?rewallu,a funkci vyhledávánívzor?u v datech paket?u.Tímto umo?ˇn uje IDS detekovat daleko více hrozeb?íˇr icích se po Internetu.

IDS musíhledatˇrádovˇe tisíceˇr etˇe zc?u a regulárních vyrazu na rychlostech10Gb/s a více.To je pro softwarováˇr e?ení,kterájsou omezena zejména pomalou sbˇe rnici a zpra-cováním na obecném procesoru,neˇr e?itelnáúloha.Bˇe?nˇe pou?ívanyvolnˇe?iˇr itelnyIDS systém Snort dosahuje v závislosti na poˇc tu IDS pravidel propustnosti vˇrádech100Mb/s, co?je pro dne?nígigabitovésítˇe nedostateˇc né.Aby bylo mo?nédosáhnout tˇe chto,ale i vy??ích rychlostí,je nutnépˇr esunoutˇc asovˇe kriticou operaci vyhledáváníˇr etˇe zc?u do hard-ware.

Pro relalizaci rychlého vyhledávánívzor?u se jevíjako vhodnátechnologie FPGA.Ta poskytuje mo?nost rekon?gurace,ˇcím?umo?ˇn uje vytvoˇr it obvod s po?adovanymi vlast-nostmi,jakymi jsou rychlost hledánívzor?u nebo pou?itáplochaˇc ipu.Existujeˇr ada pˇrístupu na bázi FPGA pro rychlévyhledávánívzor?u,nejlep?ích vysledku v?ak dosahuje pˇrístup na bázi NFA publikovanypanem Clarkem[1].Z tohoto pˇrístupu vycházím i v této práci.

2ARCHITEKTURA

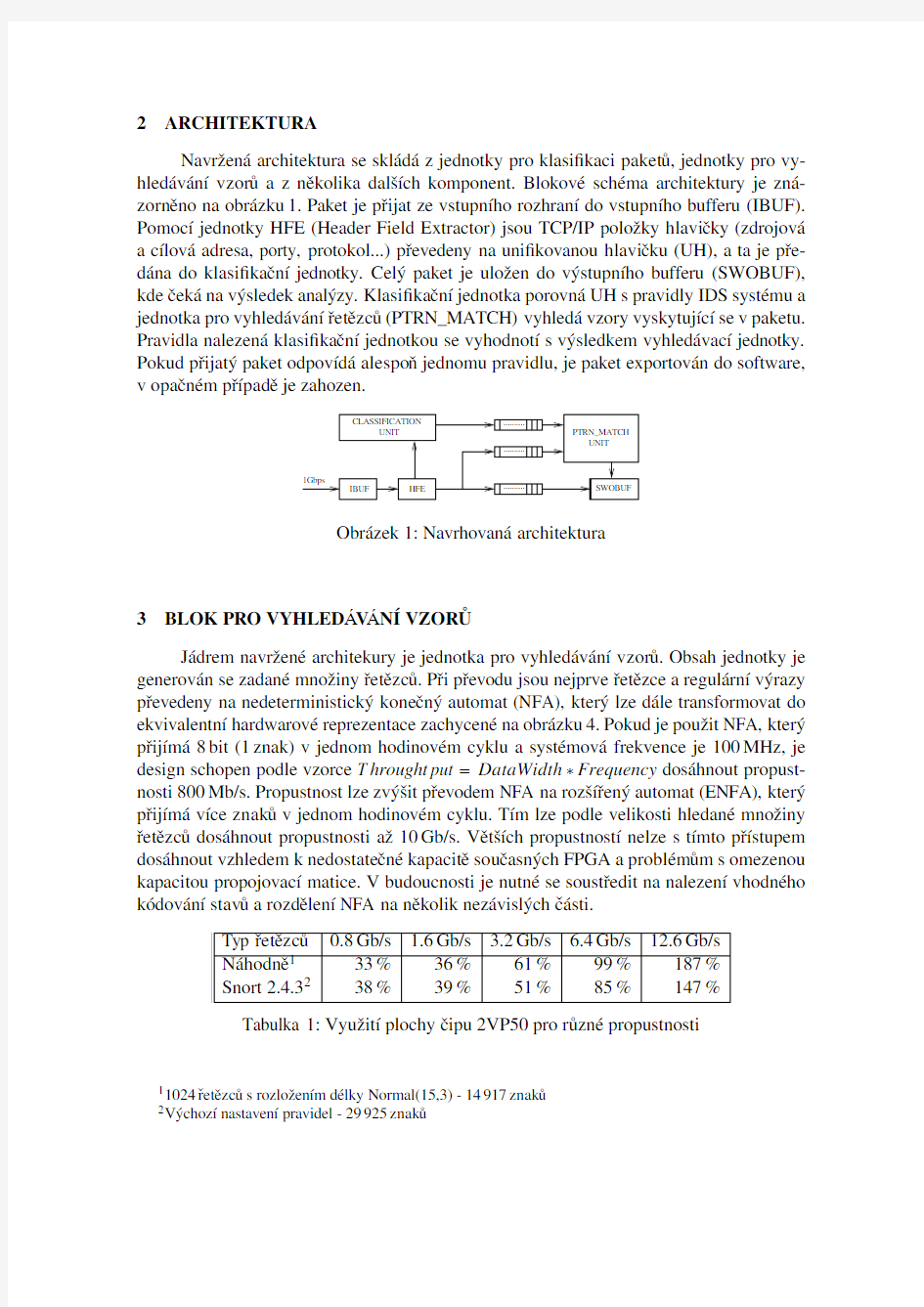

Navr?enáarchitektura se skládáz jednotky pro klasi?kaci paket?u ,jednotky pro vy-hledávánívzor?u a z nˇe kolika dal?ích komponent.Blokovéschéma architektury je zná-zornˇe no na obrázku 1.Paket je pˇr ijat ze vstupního rozhranído vstupního bufferu (IBUF).Pomocíjednotky HFE (Header Field Extractor)jsou TCP/IP polo?ky hlaviˇc ky (zdrojováa cílováadresa,porty,protokol...)pˇr evedeny na uni?kovanou hlaviˇc ku (UH),a ta je pˇr e-dána do klasi?kaˇc níjednotky.Celypaket je ulo?en do vystupního bufferu (SWOBUF),

kde ˇc ekána vysledek analyzy.Klasi?kaˇc níjednotka porovnáUH s pravidly IDS systému a jednotka pro vyhledáváníˇr etˇe zc?u (PTRN_MATCH)vyhledávzory vyskytujícíse v paketu.Pravidla nalezenáklasi?kaˇc níjednotkou se vyhodnotís vysledkem vyhledávacíjednotky.Pokud pˇr ijatypaket odpovídáalespoˇn jednomu pravidlu,je paket exportován do software,v opaˇc ném pˇr ípadˇe je zahozen.SWOBUF

..........

..........

..........UNIT PTRN_MATCH HFE IBUF UNIT CLASSIFICATION 1Gbps Obrázek 1:Navrhovanáarchitektura

3BLOK PRO VYHLEDáV áNíVZOR ?U

Jádrem navr?enéarchitekury je jednotka pro vyhledávánívzor?u .Obsah jednotky je generován se zadanémno?iny ˇr etˇe zc?u .Pˇr i pˇr evodu jsou nejprve ˇr etˇe zce a regulárnívyrazy pˇr evedeny na nedeterministickykoneˇc nyautomat (NFA),kterylze dále transformovat do ekvivalentníhardwarovéreprezentace zachycenéna obrázku 4.Pokud je pou?it NFA,kterypˇr ijímá8bit (1znak)v jednom hodinovém cyklu a systémováfrekvence je 100MHz,je design schopen podle vzorce T hrought put =DataWidth ?Frequency dosáhnout propust-nosti 800Mb/s.Propustnost lze zvy?it pˇr evodem NFA na roz?íˇr enyautomat (ENFA),kterypˇr ijímávíce znak?u v jednom hodinovém cyklu.Tím lze podle velikosti hledanémno?iny ˇr etˇe zc?u dosáhnout propustnosti a?10Gb/s.Vˇe t?ích propustnostínelze s tímto pˇr ístupem dosáhnout vzhledem k nedostateˇc nékapacitˇe souˇc asnych FPGA a problém?u m s omezenou kapacitou propojovacímatice.V budoucnosti je nutnése soustˇr edit na nalezenívhodného

kódovánístav?u a rozdˇe leníNFA na nˇe kolik nezávislych ˇc

ásti.Typ ˇr etˇe zc?u

0.8Gb/s 1.6Gb/s 3.2Gb/s 6.4Gb/s 12.6Gb/s Náhodnˇe 1

33%36%61%99%187%Snort 2.4.3238%39%51%85%147%

Tabulka 1:Vyu?itíplochy ˇc ipu 2VP50pro r?u znépropustnosti

11024ˇr etˇe zc?u

s rozlo?ením délky Normal(15,3)-14917znak?u 2Vychozínastavenípravidel -29925znak?u

Pˇr i tvorbˇe transformaˇc ního programu,kterypˇr evádíNFA do hardwarovéreprezen-tace popsanév jazyce VHDL,byla snaha minimalizovat poˇc et vyu?itych HW zdroj?u .ˇCást optimalizacíse provádípˇr i tvorbˇe NFA,kdy jsou sdíleny pre?xy ˇr etˇe zc?u a odstraˇn eny du-plicitníˇr etˇe zce.Dal?íoptimalizacíje sdílenílogiky pˇr echodu mezi stavy.Rovnˇe ?k im-plementaci sdíleného dekodéru,kterypˇr evádívstupníznak na kód 1z 256,jsem vyu?il BlockRam pamˇe ti,kteréjsou v designu jinak nevyu?ity.Uvedenéoptimalizace jsou velmi

vhodnépro pravidla systému Snort.V tabulce 1je uvedena závislost obsazeníˇc

ipu na cel-kovépropustnosti systému.Lep?ího pomˇe ru znak/kapacita u ˇr etˇe zc?u z IDS systému Snort je dosa?eno zejména díky uvedenym optimalizacím,kterése v náhodnych ˇr etˇe zcích nepro-jevily.Optimalizace ˇr etˇe zc?u systému Snort byly schopnézredukovat poˇc et stav?u NFA na

polovinu.

Obrázek 2:NFA pro ˇr etˇe zec …NIDS“

Obrázek 3:Roz?íˇr enyNFA (16bit)D Q

reg_1&D

Q reg_2&&D

Q

reg_0

"1"XN D Q reg_3&ID &

SX D Q reg_4

1DS MATCH NI Obrázek 4:HW.reprezentace ENFA

3.1ZáV ˇER

Byla navr?ena architektura pro hledáníˇr etezc?u na multigigabitovych rychlostech.Ar-chitektura byla implementována v jazyce VHDL a vyslednáimplementace byla ovˇe ˇr ena na desce COMBO6X a SFPRO [3].Navr?enéˇr e?enímonitoruje jeden port na 1Gb/s.Vy??ích propustnostílze dosáhnout,ale se zmen?ujícíse mno?inou vyhledávanych ˇr etˇe zc?u .Jak pro pomˇe rnˇe velkou mno?inu náhodnˇe vygenerovanych ˇr etˇe zc?u ,tak i pro celou sadu pravidel Snort se podaˇr ilo dosáhnout propustnosti 6.4Gb/s.

REFERENCE

[1]Clark Ch.,Schimmel D.:Scalable Pattern Matching for High-Speed Networks.In:

IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM),Napa,California,2004,pp.249-257.

[2]WWW stránka projektu Snort.https://www.360docs.net/doc/1f17908307.html, (únor 2006)

[3]WWW stránka projektu Liberouter.https://www.360docs.net/doc/1f17908307.html, (únor 2006)