计数器电路

实验报告

课程名称: 电路与电子技术实验II 指导老师: 周箭 成绩:__________________

实验名称: 计数器电路 实验类型: 同组学生姓名:

一、

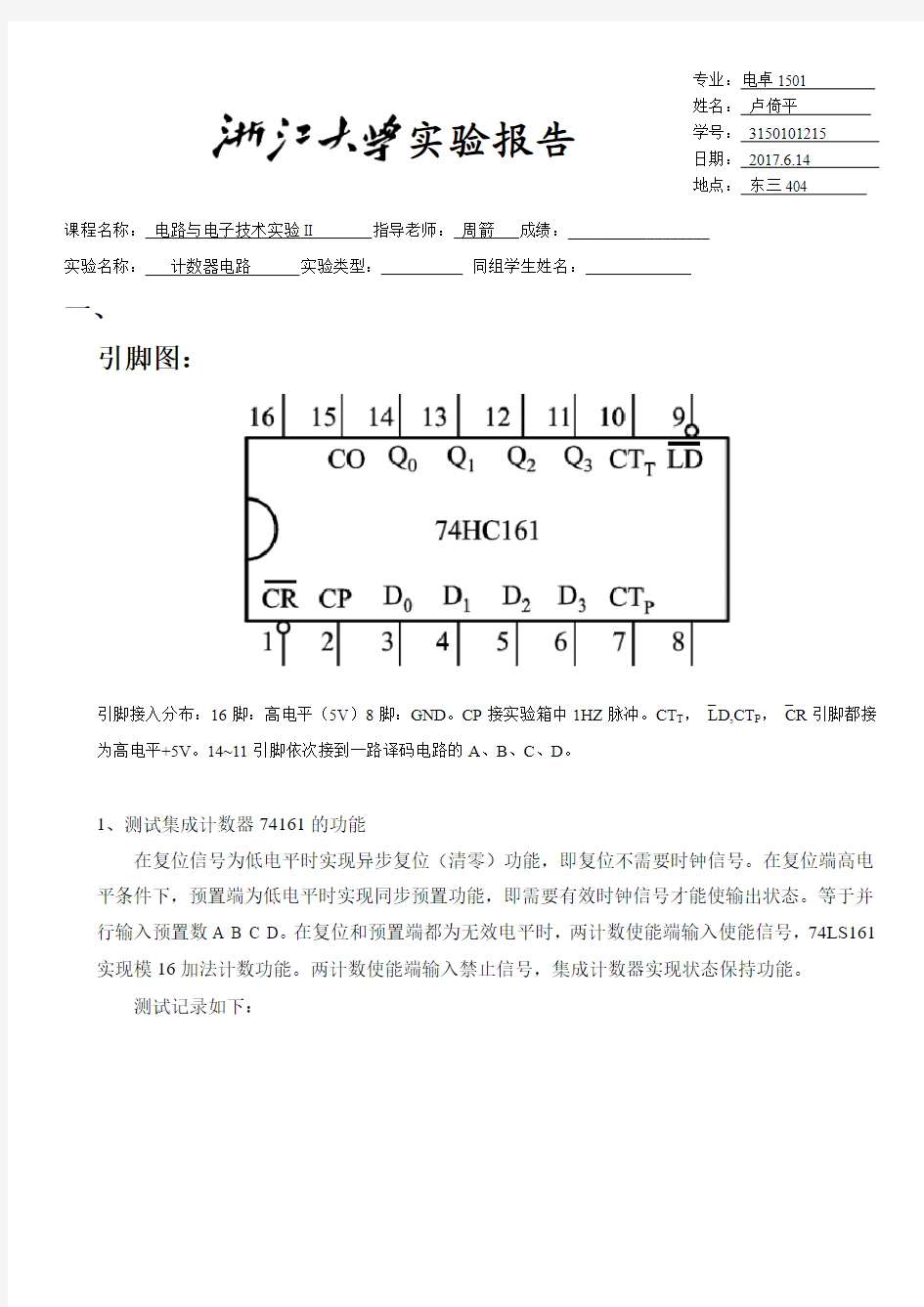

引脚图:

引脚接入分布:16脚:高电平(5V )8脚:GND 。CP 接实验箱中1HZ 脉冲。CT T ,?LD,CT P ,?CR 引脚都接为高电平+5V 。14~11引脚依次接到一路译码电路的A 、B 、C 、D 。

1、测试集成计数器74161的功能

在复位信号为低电平时实现异步复位(清零)功能,即复位不需要时钟信号。在复位端高电平条件下,预置端为低电平时实现同步预置功能,即需要有效时钟信号才能使输出状态。等于并行输入预置数A B C D 。在复位和预置端都为无效电平时,两计数使能端输入使能信号,74LS161实现模16加法计数功能。两计数使能端输入禁止信号,集成计数器实现状态保持功能。 测试记录如下:

与74161的功能表一致

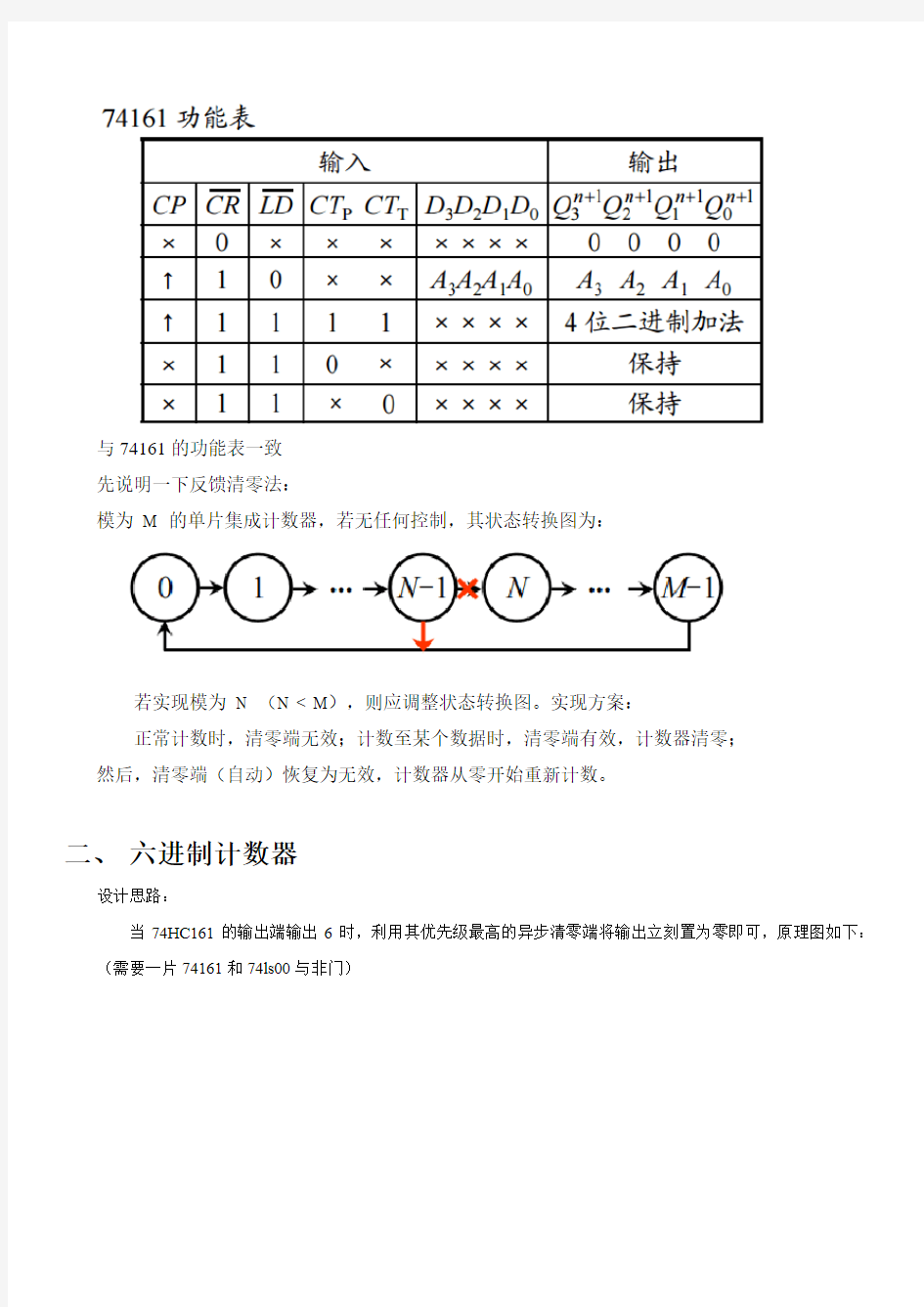

先说明一下反馈清零法:

模为M 的单片集成计数器,若无任何控制,其状态转换图为:

若实现模为N (N < M),则应调整状态转换图。实现方案:

正常计数时,清零端无效;计数至某个数据时,清零端有效,计数器清零;

然后,清零端(自动)恢复为无效,计数器从零开始重新计数。

二、六进制计数器

设计思路:

当74HC161的输出端输出6时,利用其优先级最高的异步清零端将输出立刻置为零即可,原理图如下:(需要一片74161和74ls00与非门)

三、二十四进制数字钟

在上一个实验所设计的十进制数字钟的基础上,加上一片74HC161,设计二十四进制数字钟。

电路图如下

共需用到3个与非门,一个与门,和2片74LS00完成

CP脉冲一开始设置为1Hz。实验结果用译码电路来显示,分别将两只74161的A,B,C,D接到两个译码电路的DA,DB,DC,DD上,接通电源后可以清晰看见译码器在0-23之间不断切换。切换CP脉冲的频率为32Hz,能更加清晰地看见计数器的变化(1Hz的数字显示跳动过快不易看清)。

但在实验中,我们发现了一个有趣的问题,就是当CP脉冲为32HZ时,这个电路的自启动过程有时候会

很缓慢(就是有时候一通电不会自动开始计数,而是要过一段时间才开始计数)。一开始我们怀疑是有一些引脚没有接上高电平导致(例如9号和10号管脚),但把这两个管脚接上了高电平,但后来一样也出现了自启动的相关问题。因此对于这个问题我还没有想明白。

四、二十八进制计数器

从理论上分析,与二十四进制数字钟基本一致,不同之处在于在两片74HC161的输出依次为2与8时,将两片74HC161的清零端均置零。

按照上述分析我一开始只改变一根接线,也就是个位的Qc改到了Qd,发现输出变为了20进制,分析原因,当个位为9时,给十位的74161一个上升沿,这时候十位的Qb为高电平‘1’,有一个短暂的时间内,使得个位和十位计数器同时被置零,因此做不到28进制的计数。

要解决这一短暂时间十位被异步清零的问题,必须要添加一位检查位,我选择了最高位,采用三与门将其加入了校验中。以下是对我设置的最高位检查位的仿真

在仿真中,很明显能看出28进制是可以实现的。

电子设计-两位自动计数器

课程作业 题目:《电子设计》 ——两位自动计数器 姓名:李XX 学院:物理机电与工程学院 系:电子科学系 专业:信电 年级: 学号: 指导教师: 年月日

两位自动计数器 一、两位自动计数器的功能工作原理 两位自动计数器两位数码管自动显示0-99,数字可清零。电路主要由NE555,4518,4511实现。上电后,电路自动计数.由0增至99,不断循环计数.数字上升速度快慢由NE555振荡频率决定.S1为计数清零按键.NE555构成时钟信号发生器,CD4518为二/十进制加法计数器,CD4511为译码驱动器,调节R17可调节NE555的振荡频率.C1为充放电电容,电容容量愈大,充电时间愈长,,则振荡频率愈低。 原理图: 二、元器件的选择 编号名称型号数量 R1、R2 电阻10KΩ 2 R3—R16 电阻1KΩ14 R17 可变电阻0—100KΩ 1 C1 极性电容10UF 1 C2 电容10^3 1 C3 电容10^4 1 U1 芯片NE555 1 U2A、U2B 芯片4518 2 U3、U4 芯片4511 2 ——八段数码管—— 2 S1 计数清零按键—— 1 三、芯片的功能 (1)NE555构成的是时钟信号发生器

(2)CD4518为二/十进制加数器

CD4518/CC4518是二、十进制(8421编码)同步加计数器,内含两个单元的加计数器,其功能表如真值表所示。每单个单元有两个时钟输入端CLK和EN,可用时钟脉冲的上升沿或下降沿触发。由表可知,若用ENABLE信号下降沿触发,触发信号由EN端输入,CLK 端置“0”;若用CL℃K信号上升沿触发,触发信号由CL℃K端输入,ENABLE端置“1”。RESET端是清零端,RESET端置“1”时,计数器各端输出端Q1~Q4均为“0”,只有RESET 端置“0”时,CD4518才开始计数。 CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。 CD4518功能: CD4518是一个双BCD同步加计数器,由两个相同的同步4级计数器组成。 CD4518引脚功能(管脚功能)如下: 1CP、2CP:时钟输入端。1CR、2CR:清除端。 1EN、2EN:计数允许控制端。1Q0~1Q3:计数器输出端。 2Q0~2Q3:计数器输出端。Vdd:正电源。Vss:地。 CD4518是一个同步加计数器,在一个封装中含有两个可互换二/十进制计数器,其功能引脚分别为1~7和9~{15}.该CD4518计数器是单路系列脉冲输入(1脚或2脚;9脚或10脚),4路BCD码信号输出(3脚~6脚;{11}脚~{14}脚)。 CD4518控制功能:CD4518有两个时钟输入端CP和EN,若用时钟上升沿触发,信号由CP输入,此时EN端为高电平(1),若用时钟下降沿触发,信号由EN输入,此时CP端为低电平(0),同时复位端Cr也保持低电平(0),只有满足了这些条件时,电路才会处于计数状态.否则没办法工作。 CD4518采用并行进位方式,只要输入一个时钟脉冲,计数单元Q1翻转一次;当Q1为1,Q4为0时,每输入一个时钟脉冲,计数单元Q2翻转一次;当Q1=Q2=1时,每输入一个时钟脉冲Q3翻转一次;当Q1=Q2=Q3=1或Q1=Q4=1时,每输入一个时钟脉冲Q4翻转一次。这样从初始状态(“0”态)开始计数,每输入10个时钟脉冲,计数单元便自动恢复到“0”态。若将第一个加计数器的输出端Q4A作为第二个加计数器的输入端ENB的时钟脉冲信号,便可组成两位8421编码计数器,依次下去可以进行多位串行计数。 清零原理:就是将CD4518的清零端连在一起,接一个开关,按下开关就会清零,但是如果直接连在一起前级的低电平会对后级的清零有影响,因此需要接一个二极管,因为二极管具有单向导电性,因此不会对后级有影响。 (3)CD4511为译码驱动器

电子计算器课程设计

目录 1 设计任务和性能指标 (1) 1.1 设计任务 (1) 1.2 性能指标 (1) 2 设计方案 (1) 2.1 需求分析 (1) 2.2 方案论证 (1) 3 系统硬件设计 (2) 3.1 总体框图设计 (2) 3.2 单片机选型 (2) 3.3 单片机附属电路设计 (3) 3.4 LCD液晶显示 (4) 4 系统软件设计 (5) 4.1 设计思路 (5) 4.2 总体流程图 (5) 4.3 子程序设计 (5) 4.4 总程序清单 (6) 5 仿真与调试 (6) 5.1 调试步骤 (6) 5.2 仿真结果及性能分析 (8) 6 总结 (8) 参考文献 (8) 附录1 系统硬件电路图 (10) 附录2 程序清单 (11)

1 设计任务和性能指标 1.1 设计任务 电子计算器设计 1、能实现4位整数的加减法和2位整数的乘法; 2、结果通过5个LED数码管显示(4位整数加法会有进位)或通过液晶显示屏显示。 1.2 性能指标 1.用数字键盘输入4位整数,通过LED数码显示管或液晶显示屏显示。 2.完成四位数的加减法应算。当四位数想加时产生的进位时,显示进位。 3.显示2位,并进行2位整数的乘法。 4.设计4*4矩阵键盘输入线的连接。 2 设计方案 2.1 需求分析 我们日常生活的开支,大额数字或是多倍小数的计算都需要计算器的帮助,处理数字的开方、正余弦都离不开计算器。虽然现在的计算器价格比较低廉,但是功能过于简单的不能满足个人需求,功能多的价格较贵,操作不便不说,很多功能根本用不到。所以,我们想到可不可以用自己所学为自己设计开发一个属于自己的简单计算器来完成日常生活的需求。 2.2 方案论证 使用单片机为ATMEL公司生产AT89C51,AT89C51提供以下标准功能:4K字节FLASH 闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个向量两级中断结构,一个全双工串行通讯口,内置一个精密比较器,片内振荡器及时钟电路,同时AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的工作模式,空闲方式停止CPU 的工作,但允许RAM,定时计数器,串行通信及中断系统继续工作。 显示用LCD液晶显示屏,减少线路连接。 用C言编写程序,易进行调试修改。 采用4*4矩阵键盘作为输入。

计数器设计和原理

二.计数器设计 1.实验目的 计数器在数字逻辑设计中的应用十分广泛,可以对时钟信号进行计数,分频和产生序列信号,也可以用在计时器和串并转换等电路。这次实验我们就来学习一下如何用Robei和Verilog语言来设计一个4比特计数器。 2.实验要求 计数器对每个时钟脉冲进行技术,并将计数值输出出来。这个实验我们来设计一个4比特的计数器,其技术范围在0~F之间,也就是计数到最大值16. 设计波形要求如图1所示。 图1. 计数器输出波形要求 3.实验内容 3.1 模型设计 1)新建一个模型。点击工具栏上的图标,或者点击菜单“File”然后在下 拉菜单中选择“New”,会有一个对话框弹出来(如图2所示)。在弹出的对话框中设置你所设计的模型。

图2. 新建一个项目 参数填写完成后点击“OK”按钮,Robei就会生成一个新的模块,名字就是counter,如图3所示: 图3. 计数器界面图 2)修改模型。在自动生成的界面图上进行名称的修改,输入引脚为clock, enable 和reset,输出引脚修改成count。其中count引脚的“Datasize”为4比特,用户可以输入4,也可以输入3:0。为了区分每个引脚,我们可以修改每个引脚的Color值,并点回车保存。修改完成后如图4所示。如果选中模块,按“F1”键,就会自动生成一个Datasheet,如图5所示。

图4. 修改引脚属性 图5. “Datasheet”截图 3)输入算法。点击模型下方的Code(如图6所示)进入代码设计区。

图6. 点击Code输入算法 在代码设计区内输入以下Verilog代码: always @ (posedge clock) //学习always语句的写法,并设置敏感信号。时钟上升沿触发begin //学习Verilog if else语句的写法 if (reset == 1) begin count<= 0; end //if enable is 1, counter starts to count else if (enable == 1) begin count <= count + 1; end end 4)保存。点击工具栏图标,或者点击菜单“File”中的下拉菜单“Saveas”, 将模型另存到一个文件夹中。 5)运行。在工具栏点击或者点击菜单“Build”的下来菜单“Run”,执 行代码检查。如果有错误,会在输出窗口中显示。如果没有错误提示,恭喜,模型counter设计完成。 3.2测试文件设计

实验二:+0~9999的计数器电路的设计

EDA实验报告 学院(部):电气与信息工程学院专业:电子信息工程 学生姓名:刘玉文 班级:电子信息工程1101 学号: 指导教师姓名:谭会生

实验二:0~9999的计数器电路的设计 1.实验目的 (1)进一步熟悉和掌握Quartus II软件的使用。 (2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。 (3)学习和掌握VHDL进程语句和元件例化语句的使用。 2.实验内容 设计并调试好一个技术范围为0~9999的4位十进制计数器电路CNT9999,并用GW48-CK或其他EDA实验开发系统(可选用的芯片为ispLSI 1032E-PLCC84或EPM7128S-PL84或XCS05/XCS10-PLCC84芯片)进行硬件验证。 3.实验条件 (1)开发软件:Quartus II8.0。 (2)实验设备:GW48-CK EDA实验开发系统。 (3)拟用芯片:EPM7128S-PL84。 4.实验设计 (1)系统原理框图 为了简化设计并便于显示,本计数器电路CNT9999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图所示的原理框图构成顶层电路CNT9999。

CNT9999电路原理框图 (2)VHDL程序 计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。 1)CNT10的VHDL源程序: --CNT10.VHD LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT10 IS PORT(CLK:IN STD_LOGIC; CLR:IN STD_LOGIC; ENA:IN STD_LOGIC; CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO:OUT STD_LOGIC); END ENTITY CNT10; ARCHITECTURE ART OF CNT10 IS

电子计数器原理及应用

实验三:电子计数器原理及应用 一、实验目的: 了解测频的方法和电子计数器的工作原理 熟悉电子计数器的操作,并采用不同闸门时间对不同的频率进行测量并分析。 二、实验原理: 1、测频原理 计数器的测频原理如图1 所示。fx 为输入待测信号频率,f0为时钟脉冲的频率。闸门信号GA TE 控制计数时间,Fx 和F0两个计数器在同一时间T 内分别对fx 和f0进行计数,f0已知,时间T 可由计数器F0的计数值算出。计数器Fx 的计数值Nx=fx ×T ,计数器F0的计数值N0=f0×T 。 由于 Nx/fx =N0/f0=T 则被测频率fx 为 fx =(Nx/N0)×f0 由于 Nx/fx =N0/f0=T 则被测频率fx 为 fx =(Nx/N0)× f0 显示 OUT3 Q Q GATE F X F O 图1 测频原理框图 2、电路工作原理 本实验系统中的计数器是采用8253芯片来实现的,电路原理如图2所示。 (1)Fx 、F0计数器: F0计数器:由8253计数器0和计数器1级联而成的计数器,对时钟计数,通过设定初值来确定闸门时间(采用二进制计数)。 Fx 计数器:由8253的计数器2构成的计数器,对被测信号计数(采用二进制计数)。 (2)开门脉冲发生器: 开门脉冲发生器由D 触发器构成,开门信号由软件产生,经out3到D1端,当软件发出开门信号后,D 触发器的翻转产生一个开门前置脉冲(经与非门G 输出),完成8253内的三个计数器从初值锁存器往计数器打入初值的置数脉冲作用。

OUT3 图2 电路原理框图 三、实验硬件及软件: 1、计算机一台 2、DVCC实验仪一台,函数信号发生器一台。 3、电子计数器程序。 四、实验预习要求: 1、复习好《电子测量》中电子计数器的有关章节。 2、作好测试记录的准备。 五、实验步骤: 1、在老师的指导下将实验平台准备就绪。 2、利用函数信号发生器产生不同频率的方波信号,由电子计数器对其进行测频,选择不同的闸门时间,对测量结果进行比较和分析。记录测量的频率值,并填写下表: 六、思考题: 1、分析以上测量数据,在用电子计数器对频率进行测量中,闸门时间对测量精度有何影响? 2、对于本实验系统而言,闸门时间的选择有何限制?

电子计数器的工作原理

由B通道输入频率为fB的经整形的信号控制闸门电路,即以一个脉冲开门,以随后的一个脉冲关门。两脉冲的时间间隔(TB)为开门时间。由A通道输入经整形的频率为fA的脉冲群在开门时间内通过闸门,使计数器计数,所计之数N=fA·TB。 对A、B通道作某些选择,电子计数器可具有以下三种基本功能。 ①频率测量:被测信号从A通道输入,若TB为1秒,则读数N即为以赫为单位的频率fA。由晶体振荡器输出的标准频率信号经时基电路适当分频后形成闸门时间信号而确定TB之值。 ②周期或时间间隔测量:被测信号由B信道输入,控制闸门电路,而A 通路的输入信号是由时基电路提供的时钟脉冲信号。计数器计入之数为闸门开放时间,亦即被测信号的周期或时间间隔。 ③累加计数:由人工触发开放闸门,计数器对A通道信号进行累加计数。 在这些功能的基础上再增加某些辅助电路或装置,计数器还可完成多周期平均、时间间隔平均、频率比值和频率扩展等功能。电子计数器性能指标主要包括:频率、周期、时间间隔测量范围、输入特性(灵敏度、输入阻抗和波形)、精度、分辨度和误差(计数误差、时基误差和触发误差)等。 艾驰商城是国内最专业的MRO工业品网购平台,正品现货、优势价格、迅捷配送,是一站式采购的工业品商城!具有10年工业用品电子商务领域研究,以强大的信息通道建设的优势,以及依托线下贸易交易市场在工业用品行业上游供应链的整合能力,为广大的用户提供了传感器、图尔克传感器、变频器、断路器、继电器、PLC、工控机、仪器仪表、气缸、五金工具、伺服电机、劳保用品等一系列自动化的工控产品。 如需进一步了解相关仪器仪表产品的选型,报价,采购,参数,图片,批发等信息,请关注艾驰商城https://www.360docs.net/doc/201584837.html,/

数字电子时钟逻辑电路设计

《数字逻辑》 课程设计报告 设计题目:数字电子钟 组员:黄土标黄维超蔡荣达孙清玉指导老师:麦山 日期:2013/12/27

摘要数字电子钟是一种用数字显示秒、分、时的计时装置,本次数字时钟电路设计采用GAL系列芯片来分别实现时、分、秒的24进制和60进制的循环电路,并支持手动清零和校正的功能。 关键词数字电子钟;计数器;GAL;4040芯片;M74LS125AP三态门 1设计任务及其工作原理 1.1设计任务 设计一台能显示时,分,秒的数字电子钟。 技术要求: (1)秒、分为00~59六十进制计数器。 (2)时为00~23二十四进制计数器。 (3)可手动校正:能分别进行秒、分、时的校正。只要将开关置于手动位置,可分别对秒、分、时进行手动脉冲输入调整或连续脉冲输入校正。并且可以手动按下脉冲进行清零。 1.2工作原理 本数字电子钟的设计是根据时、分、秒各个部分的的功能的不同,分别用GAL16V8D 设计成六十进制计数器和用GAL22V10。秒的个位,设计成十进制计数器,十位设计成六进制进制计数器(计数从00到59时清零并向前进位)。分部分的设计与秒部分的设计完全相同;时的个位,设计成二进制计数器,十位设计为四进制计数器,当时钟计数到23时59分59秒时,使计数器的小时部分清零,进而实现整体循环计时的功能。 2电路的组成 2.1 计数器部分:利用GAL16V8D和GAL22V10芯片分别组成二十四进制计数器和六十进制计数器,它们采用同步连接,利用外接标准脉冲信号进行计数。

2.2 显示部分:将三片GAL芯片对应的引脚分别接到实验箱上的七段共阴数码显示管上,根据脉冲的个数显示时间。 3.3 分频器:由于实验箱上提供的时钟脉冲的时间间隔太小,所以使用GAL16V8D和GAL16V8D、4040芯片和M74LS125AP三态门芯片设计一个分频器,使连续输出脉冲信号时间间隔为0.5s 3设计步骤及方法 3.1 分和秒部分的设计: 分和秒部分的设计是采用GAL16V8D芯片来设计的60进制计数器,具体设计如图1示: