串行接口FLASH存储器在8051单片机中的应用

串行接口FL AS H存储器在8051单片机中的应用3

张亚华,李福勤

(河南机电高等专科学校电子与通信工程系,河南新乡453002)

摘要:介绍了flash存储器A T25FS040与8051单片机的接口方法,详细叙述了A T25FS040读取,写入和擦除操作的具体方法和时序,设计了A T25FS040与8051单片机接口的硬件,并给出参考例子程序。

关键词:8051单片机;FL ASH存储器;SPI

中图分类号:TP368.1 文献标识码:A 文章编号:100822093(2007)0620001203

在单片机控制的大屏幕L ED显示屏中,需要存

储大量文字、图形的点阵数据。而8051

单片机内部

的程序存储器容量有限,且只能存储固定的点阵数据,缺乏灵活性。使用扩充外部数据存储器的方法存储点阵数据,除容量有限外,还存在占用单片机接口资源和数据掉电保护等问题。因此在此类单片机应用系统中,以尽量少的硬件资源,外扩大容量的FL ASH存储器,是一种较好的解决方案。

1 大容量FL ASH存储器A T25FS040

A T25FS040[1]是A TM EL公司生产的一种大容量串口FL A SH存储器,在一片SO IC封装的8脚芯片中,有4Mbit存储单元,组成512K×8的结构。整个存储区划分为8个64K字节的存储块,每一个块又划分为16个4K字节的扇区。数据写入时,一次可以写入一个字节或一个256字节的页面。读取数据时,可以一次读一个字节,也可以连续读相临单元的数据。数据擦除时,可以分别擦除一个扇区,一个数据块或者整个存储器。芯片可以反复擦写10000次。A T25FS040的I/O接口采用了4线的SPI接口,SPI时钟频率最高可达到50M Hz。该芯片采用低压供电,电源电压2.7V-3.6V。芯片还设计了完善的软硬件写保护功能和串口等待功能。

AT25FS040的引脚定义和引脚功能见图1和表1。

图1 A T25FS040引脚定义

表1 A T25FS040引脚功能

引脚功能引脚功能

/CS片选SI串行数据输入

SO串行数据输出SC K串行时钟

/WP写保护/HOLD串口等待

GND地线VCC电源

1.1 A T25FS040的操作指令

A T25FS040定义了11组操作指令,常用的有以下7种:

表2 A T25FS040常用指令表

指令代码操作WREN06H使能写操作

RDSR05H读状态寄存器

READ03H读操作

PRO GRAM02H写操作

SECTOR ERASE20H擦除扇区(4K)

BLOC K ERASE52H擦除块(64K)

CHIP ERASE60H擦除芯片(512K)

向A T25FS040发送操作指令的顺序是:SC K为低电平时,片选信号/CS由高电平变为低电平,然后单片机按SPI时序要求,在时钟脉冲作用下,经SI引脚向A T25FS040发送指令代码(高位在前),紧接着发送或接受指令的参数(地址、状态、数据等),完成后在SC K低电平时置“1”/CS信号。

1.2 A T25FS040的读操作

向A T25FS040发送读操作指令(03H),紧跟着

1

第15卷第6期 2007年11月

河南机电高等专科学校学报

Journal of Henan Mechanical and Electrical Engineering College

Vol.15№.6

Nov.2007

3收稿日期:2007209220

作者简介:张亚华(19512),男,河南郑州人,副教授,主要从事嵌入式系统开发研究。

发送三个字节的地址(高位在前),即可从SO 引脚串行读出所选中单元的数据。若只读一个字节,则需在读出最后一位后,将/CS 置为高电平,结束读操作。若要连续读相邻单元数据,只需保持/CS 为低电平,持续发时钟脉冲,A T25FS040内部的地址计数器会自动+1,将后续单元的数据由SO 引脚连续移出,直到/CS 变为高电平为止。地址计数器自动+1可持续到最高地址(07FFFF H ),再自动+1,会返回起始地址(000000H )。读出的数据高位在前。A T25FS040的读操作时序见图2

。

图2 A T25FS040读操作时序

1.3 A T25FS040的写操作

写入数据前要确保待写入的存储区为擦除状态(全“1”

),否则应先用擦除指令将待写入的存储区擦除。每次写入前要先向A T25FS040发送写入使能指令(06H )。写操作与读操作相似,先向A T25FS040发送写操作指令(02H ),紧跟着发送三个字节的地址,随即发送要写入的数据,一次最多可发送一个页面(256字节)。在连续发送过程中,内部地址计数器会自动+1,指向下一单元。需要注意的是,当地址指向页面边

界(低字节地址为0FF H )时,再+1,不是进入下一页面,而是返回当前页面的起始地址(低字节地址为00H )。发送完数据后,在SC K 低电平状态下,置“1”/CS ,将启动A T25FS040内部的写入操作,写入过程需

用时30

μs/字节。判断写入是否完成,可用RDSR 指令读状态寄存器,查询状态寄存器的D0位。D0=“1”表示正在写入,D0=“0”表示写入完成。每次写入操作完成后,芯片都自动进入写保护状态。A T25FS040的写操作时序见图3

。

图3 A T25FS040写操作时序

1.4 A T25FS040的擦除操作

A T25FS040在写入数据前要求待写入单元必须为擦除状态(全“1”

),因此在改写存储器前,要先进行擦除操作。A T25FS040定义了三种擦除操作指令:扇区擦除SEC TOR ERASE (20H ),一次擦除一个扇区4K 字节;块擦除BLOC K ERASE (52H ),一次擦除一块64K 字节;芯片擦除(60H ),一次擦除整个芯片512K 字节。使用擦除指令前,要求先执行写操作使能指令WREN 。执行擦除操作指令的顺序是:置/CS =“0”后发送擦除指令,紧跟三个字节的地址,选中待擦除扇区

(块)中任一单元,在SC K 低电平状态下,置/CS =

“1”,启动擦除过程开始。芯片擦除指令无须带地址参数。三种擦除指令的典型擦除时间分别为:扇区擦除,50ms ;块擦除,200ms ;芯片擦除,1.6s 。判断擦除是否完成,也可以用RDSR 指令读状态寄存器,查询状态寄存器的D0位。D0=“1”表示正在擦除,D0=

“0”表示擦除完成。

2 A T25FS040与8051单片机的接口与驱动

程序

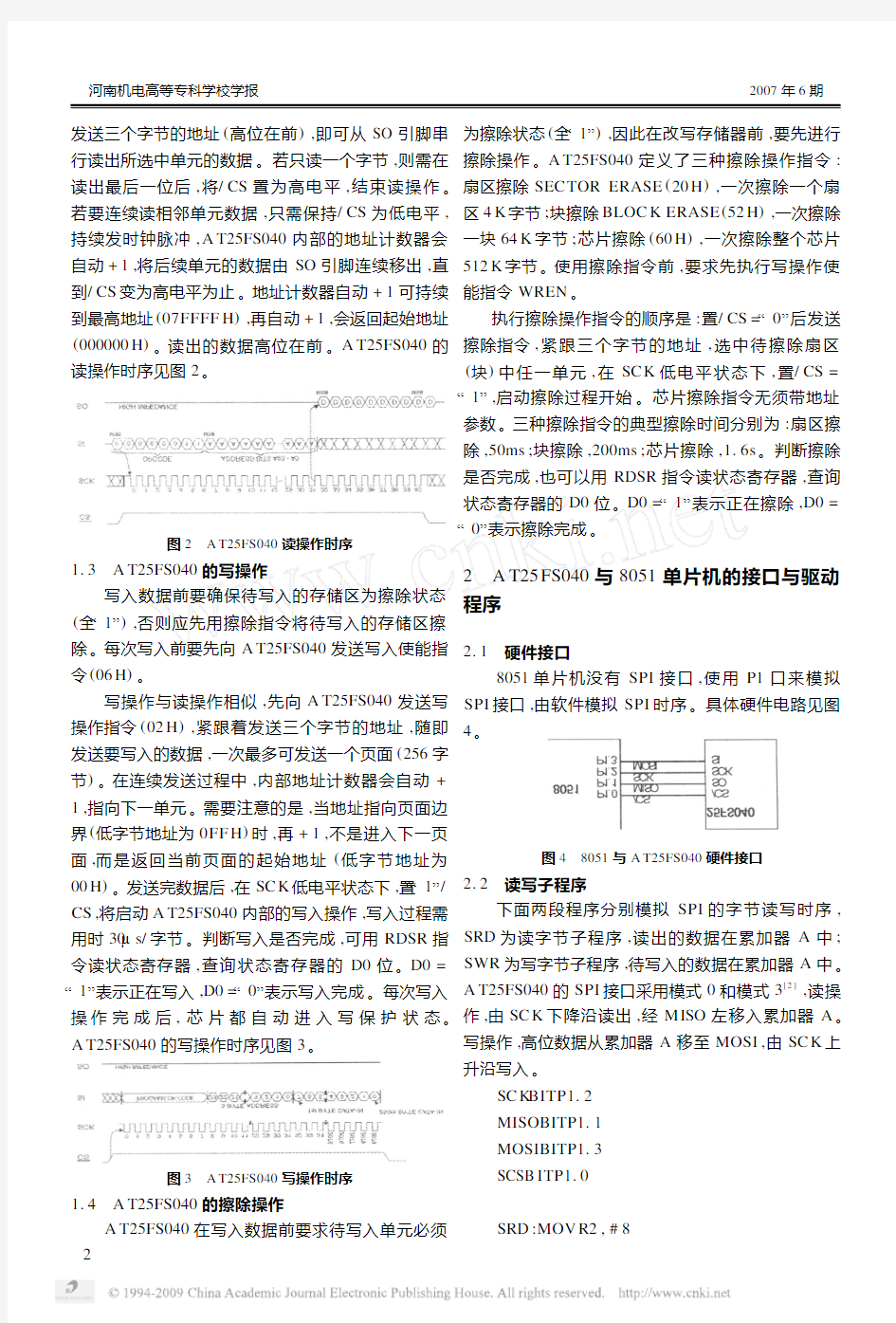

2.1 硬件接口8051单片机没有SPI 接口,使用P1口来模拟

SPI 接口,由软件模拟SPI 时序。具体硬件电路见图4

。图4 8051与A T25FS040硬件接口

2.2

读写子程序下面两段程序分别模拟SPI 的字节读写时序,

SRD 为读字节子程序,读出的数据在累加器A 中;SWR 为写字节子程序,待写入的数据在累加器A 中。

A T25FS040的SPI 接口采用模式0和模式3[2]

,读操作,由SC K 下降沿读出,经M ISO 左移入累加器A 。

写操作,高位数据从累加器A 移至MOSI ,由SC K 上升沿写入。

SC K BITP1.2MISOBITP1.1MOSIBITP1.3SCSB ITP1.0SRD :MOV R2,#8

2

河南机电高等专科学校学报 2007年6期

L SRD:CL RSC K

MOVC,M ISO

RL CA

SETBSC K

DJ NZR2,L SRD

RET

SWR:MOV R2,#8

L SWR:RL CA

CL R SC K

MOVMOSI,C

SETBSC K

DJ NZR2,L SWR

RET

2.3 读页面子程序

下面的程序是读页面子程序,页面地址位于8051内部RAM的30H(高位)、31H、32H,读出的数据存放到8051外扩RAM的0000H-00FF H存储区。

RP G:CL RSC K

CL RSCS

MOVA,#03H

ACALL SWR

MOVR3,#3

MOVR1,#30H

LADD:MOVA,@R1

ACALL SWR

INCR1

DJ N ZR3,L ADD

MOVDP TR,#0

MOVR4,#0

LOO P G:ACALL SRD

MOVX@DP TR,A

INCDP TR

DJ N ZR4,LOOP G

CL RSC K

SETBSCS

RET

A T25FS040具有体积小、耗电省、接口简单等优点,其512K字节的存储容量,能存入24×24点阵国标二级字库全部6763个汉字的点阵数据,或者50多幅320×240点阵图形。可以较好地解决大屏幕L ED 显示屏和嵌入式测控系统中图形液晶显示模块的显示数据存储问题,还可以用于移动式智能化仪表中,保存大量的测量数据,有着广泛的应用领域。

(责任编辑 吕春红)参考文献:

[1]At mel Corporation.A T25FS040Advance Information[Z].2006.

[2]陈世利,等.SPI串行Flash在数据存储系统中的应用[J].国外电

子元器件,2001,(10).

Application of Ser ial FLASH Memory in8051

ZHAN G Ya2hua,et al

(Henan Mechanical and Elect rical Engineering College,Xinxiang453002,China) Abstract:The paper discuss t he interface of t he flash memory A T25FS040and8051singlechip,recount detailed t he specific means and time sequence for reading、writing and erasing operations,int roduce t he de2 sign measures of A T25FS040interface hardware,and a reference procedure.

K ey w ords:8051;flash memory;interface

3

张亚华等:串行接口FL ASH存储器在8051单片机中的应用

第13章 Flash存储器

第13章Flash存储器 Flash存储器具有电可擦除、无需后备电源来保护数据、可在线编程、存储密度高、低功耗、成本较低等特点,这使得Flash存储器在嵌入式系统中的使用迅速增长。 本章主要以HC08系列中的GP32为例阐述Flash存储器的在线编程方法,也简要阐述了HCS08系列中GB60的在线编程方法。本章首先概述了Flash存储器的基本特点,并介绍其编程模式,随后给出M68HC908GP32的Flash存储器编程的基本操作及汇编语言和C语言的在线编程实例。最后讨论MC9S08GB60的Flash存储器编程方法。 Flash存储器编程方法有写入器模式与在线模式两种,本章讨论的是在线模式。有的芯片内部ROM中,包含了Flash擦除与写入子程序,在本章的进一步讨论中给出了调用方法,使Flash编程相对方便。有的芯片内部ROM中没有固化Flash擦除与写入子程序,只能自己编写Flash擦除与写入子程序。而编写Flash擦除与写入子程序需要较严格的规范,所以这是比较细致的工作,读者应仔细分析本章的例程,并参照例程编程。掌握了GP32芯片的Flash编程方法后,可以把此方法应用于整个系列的Flash编程。Flash在线编程对初学者有一定难度,希望通过实例分析学习。本章给出Flash在线编程的C语言实例,对于训练C语言与汇编联合编程技巧很有帮助。 13.1 Flash存储器概述与编程模式 理想的存储器应该具备存取速度快、不易失、存储密度高(单位体积存储容量大)、价格低等特点,但一般的存储器只具有这些特点中的一个或几个。近几年Flash存储器(有的译为:闪速存储器或快擦型存储器)技术趋于成熟,它结合了OTP存储器的成本优势和EEPROM的可再编程性能,是目前比较理想的存储器。Flash存储器具有电可擦除、无需后备电源来保护数据、可在线编程、存储密度高、低功耗、成本较低等特点。这些特点使得Flash存储器在嵌入式系统中获得广泛使用。从软件角度来看,Flash和EEPROM技术十分相似,主要的差别是Flash存储器一次只能擦除一个扇区,而不是EEPROM存储器的1个字节1个字节地擦除,典型的扇区大小是128B~16KB。尽管如此,因为Flash存储器的总体性价比,它还是比EEPROM更加流行,并且迅速取代了很多ROM器件。 嵌入式系统中使用Flash存储器有两种形式:一种是嵌入式处理器上集成了Flash,另一种是片外扩展Flash。 目前,许多MCU内部都集成了Flash存储器。Freescale公司在Flash存储器技术相当成熟的时候,在HC08系列单片机内集成了Flash存储器。该系列内部的Flash存储器不但可用编程器对其编程,而且可以由内部程序在线写入(编程),给嵌入式系统设计与编程提供了方便。存储器是MCU的重要组成部分,存储器技术的发展对MCU的发展起到了极大的推动作用。对于Freescale公司新推出的HCS08系列MCU采用第三

flash存储原理.

flash存储原理 一、半导体存储设备的原理 目前市面上出现了大量的便携式存储设备,这些设备大部分是以半导体芯片为存储介质的。采用半导体存储介质,可以把体积变的很小,便于携带;与硬盘之类的存储设备不同,它没有机械结构,所以也不怕碰撞;没有机械噪声;与其它存储设备相比,耗电量很小;读写速度也非常快。半导体存储设备的主要缺点就是价格和容量。 现在的半导体存储设备普遍采用了一种叫做“FLASH MEMORY”的技术。从字面上可理解为闪速存储器,它的擦写速度快是相对于EPROM而言的。FLASH MEMORY是一种非易失型存储器,因为掉电后,芯片内的数据不会丢失,所以很适合用来作电脑的外部存储设备。它采用电擦写方式、可10万次重复擦写、擦写速度快、耗电量小。 1.NOR型FLASH芯片 我们知道三极管具备导通和不导通两种状态,这两种状态可以用来表示数据0和数据1,因此利用三极管作为存储单元的三极管阵列就可作为存储设备。FLASH 技术是采用特殊的浮栅场效应管作为存储单元。这种场效应管的结构与普通场管有很大区别。它具有两个栅极,一个如普通场管栅极一样,用导线引出,称为“选择栅”;另一个则处于二氧化硅的包围之中不与任何部分相连,这个不与任何部分相连的栅极称为“浮栅”。通常情况下,浮栅不带电荷,则场效应管处于不导通状态,场效应管的漏极电平为高,则表示数据1。编程时,场效应管的漏极和选择栅都加上较高的编程电压,源极则接地。这样大量电子从源极流向漏极,形成相当大的电流,产生大量热电子,并从衬底的二氧化硅层俘获电子,由于电子的密度大,有的电子就到达了衬底与浮栅之间的二氧化硅层,这时由于选择栅加有高电压,在电场作用下,这些电子又通过二氧化硅层到达浮栅,并在浮栅上形成电子团。浮栅上的电子团即使在掉电的情况下,仍然会存留在浮栅上,所以信息能够长期保存(通常来说,这个时间可达10年。由于浮栅为负,所以选择栅为正,在存储器电路中,源极接地,所以相当于场效应管导通,漏极电平为低,即数据0被写入。擦除时,源极加上较高的编程电压,选择栅接地,漏极开

Flash存储器的技术和发展

湘潭大学论文 题目:关于Flash存储器的技术和发展 学院:材料与光电物理学院 专业:微电子学 学号:2010700518 姓名:李翼缚 完成日期:2014.2.24

目录 1引言 (4) 2Flash 存储器的基本工作原理 (4) 3 Flash存储器的编程机制 (5) 3.1 沟道热电子注入(CHE) (5) 3.2 F-N隧穿效应(F-NTunneling) (6) 4 Flash存储器的单元结构 (6) 5 Flash存储器的可靠性 (7) 5.1 CHE编程条件下的可靠性机制 (8) 5.2 隧道氧化层高场应力下的可靠性机制 (8) 6 Flash存储器的发展现状和未来趋势 (9) 参考文献: (10)

关于Flash存储器的技术和发展 摘要:Flash 存储器是在20世纪80年代末逐渐发展起来的一种新型半导体不挥发性存储器,它具有结构简单、高密度、低成本、高可靠性和在系统的电可擦除性等优点, 是当今半导体存储器市场中发展最为迅速的一种存储器。文章对F lash 存储器的发展历史和工作机理、单元结构与阵列结构、可靠性、世界发展的现状和未来趋势等进行了深入的探讨。 关键词:半导体存储器;不挥发性存储器; Flash存储器; ETOX结构 About Flash Memory Technology and Its Development Abstract: As a new non -volatile semiconductor memory introduced by Masuoka in 1984, flash memory has a number of advantages, such as simple structure, high integration density, low cost, and high reliability, and it is widely used in mobile phone, digital camer a, PCBIOS, DVD player, and soon. Its evolution, programming mechanism, cell structure, array structure, reliability are described, and its developing trend in the future is dis cussed. Key words: Semico nduct or memory; Flash memor y; Non-volatile memory ; ETOX

Flash做为存储器存储数据

STM32学习笔记-Flash做为存储器储存数据 说到STM32的FLSAH,我们的第一反应是用来装程序的,实际上,STM32的片内FLASH不仅用来装程序,还用来装芯片配置、芯片ID、自举程序等等。当然, FLASH 还可以用来装数据。 自己收集了一些资料,现将这些资料总结了一下,不想看的可以直接调到后面看怎么操作就可以了。 FLASH分类 根据用途,STM32片内的FLASH分成两部分:主存储块、信息块。主存储块用于存储程序,我们写的程序一般存储在这里。信息块又分成两部分:系统存储器、选项字节。系统存储器存储用于存放在系统存储器自举模式下的启动程序(BootLoader),当使用ISP方式加载程序时,就是由这个程序执行。这个区域由芯片厂写入BootLoader,然后锁死,用户是无法改变这个区域的。选项字节存储芯片的配置信息及对主存储块的保护信息。 FLASH的页面 STM32的FLASH主存储块按页组织,有的产品每页1KB,有的产品每页2KB。页面典型的用途就是用于按页擦除FLASH。从这点来看,页面有点像通用FLASH 的扇区。 STM32产品的分类 STM32根据FLASH主存储块容量、页面的不同,系统存储器的不同,分为小容量、中容量、大容量、互联型,共四类产品。 小容量产品主存储块1-32KB,每页1KB。系统存储器2KB。 中容量产品主存储块64-128KB,每页1KB。系统存储器2KB。 大容量产品主存储块256KB以上,每页2KB。系统存储器2KB。 互联型产品主存储块256KB以上,每页2KB。系统存储器18KB。 对于具体一个产品属于哪类,可以查数据手册,或根据以下简单的规则进行区分: STM32F101xx、STM32F102xx 、STM32F103xx产品,根据其主存储块容量,一定是小容量、中容量、大容量产品中的一种,STM32F105xx、STM32F107xx是互联型产品。 互联型产品与其它三类的不同之处就是BootLoader的不同,小中大容量产品的BootLoader只有2KB,只能通过USART1进行ISP,而互联型产品的BootLoader有18KB,能通过USAT1、4、CAN等多种方式进行ISP。小空量产品、中容量产品的BootLoader与大容量产品相同。 关于ISP与IAP ISP(In System Programming)在系统编程,是指直接在目标电路板上对芯片进行编程,一般需要一个自举程序(BootLoader)来执行。ISP也有叫ICP (In Circuit Programming)、在电路编程、在线编程。 IAP(In Application Programming)在应用中编程,是指最终产品出厂后,由最终用户在使用中对用

嵌入式—flash存储器

存储器存储器 FLASH存储器存储器章FLASH 13章 第13

本章主要内容 Flash Flash存储器概述与编程模式存储器概述与编程模式存储器 MC908GP32MC908GP32单片机单片机单片机Flash Flash Flash存储器编程方法存储器编程方法存储器GP32GP32单片机单片机单片机Flash Flash Flash在线编程汇编语言实例在线编程汇编语言实例GP32GP32单片机单片机单片机Flash Flash Flash在线编程在线编程在线编程08C 08C 08C语言实例语言实例HCS08HCS08系列单片机系列单片机系列单片机Flash Flash Flash编程方法编程方法

13.1 Flash 13.1 Flash存储器概述与编程模式存储器概述与编程模式13.1.1 Flash存储器的基本特点与编程模式 (1) Flash存储器的基本特点 ①固有不挥发性::Flash Flash存储器不需要后备电源来保持数据存储器不需要后备电源来保持数据存储器不需要后备电源来保持数据。。所以所以,,它具有磁存储器无需电能保持数据的优点它具有磁存储器无需电能保持数据的优点。。 ②易更新性易更新性:Flash :Flash :Flash存储器具有电可擦除特点存储器具有电可擦除特点存储器具有电可擦除特点。。相对于相对于EPROM(EPROM(EPROM(电可编电可编程只读存储器程只读存储器))的紫外线擦除工艺的紫外线擦除工艺,,Flash Flash存储器的电擦除功能为开发者存储器的电擦除功能为开发者节省了时间节省了时间,,也为最终用户更新存储器内容提供了可能也为最终用户更新存储器内容提供了可能。。 ③成本低成本低、、密度高密度高、、可靠性好可靠性好::与EEPROM(EEPROM(电可擦除可编程的只读存电可擦除可编程的只读存储器储器))相比较相比较,,Flash Flash存储器的成本更低存储器的成本更低存储器的成本更低、、密度更高密度更高、、可靠性更好可靠性更好。。

FLASH闪存总体介绍

Flash闪存器总体介绍 闪存的英文名称是“Flash Memory”,一般简称为“Flash”,它属于内存器件的一种。 不过闪存的物理特性与常见的内存有根本性的差异: 目前各类DDR、SDRAM或者RDRAM都属于挥发性内存,只要停止电流供应内存中的数据便无法保持,因此每次电脑开机都需要把数据重新载入内存; 闪存则是一种不挥发性(Non-V olatile)内存,在没有电流供应的条件下也能够长久地保持数据,其存储特性相当于硬盘,这项特性正是闪存得以成为各类便携型数字设备的存储介质的基础。 NAND闪存的存储单元则采用串行结构,存储单元的读写是以页和块为单位来进行(一页包含若干字节,若干页则组成储存块,NAND的存储块大小为8到32KB),这种结构最大的优点在于容量可以做得很大,超过512MB容量的NAND 产品相当普遍,NAND 闪存的成本较低,有利于大规模普及。 NAND闪存的缺点在于读速度较慢,它的I/O 端口只有8个,比 NOR 要少多了。这区区8个I/O 端口只能以信号轮流传送的方式完成数据的传送,速度要比NOR闪存的并行传输模式慢得多。再加NAND闪存的逻辑为电子盘模

块结构,内部不存在专门的存储控制器,一旦出现数据坏块将无法修,可靠性较NOR 闪存要差。 NAND闪存被广泛用于移动存储、数码相机、MP3播放器、掌上电脑等新兴数字设备中。由于受到数码设备强劲发展的带动, NAND 闪存一直呈现指数级的超高速增长. NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结构,强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。但是经过了十多年之后,仍然有相当多的硬件工程师分不清NOR和NAND闪存。 相“flash存储器”经常可以与相“NOR存储器”互换使用。许多业内人士也搞不清楚NAND闪存技术相对于NOR技术的优越之处,因为大多数情况下闪存只是用来存储少量的代码,这时NOR闪存更适合一些。而NAND则是高数据存储密度的理想解决方案。 NOR的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于flash的管理和需要特殊的系统接口。 性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。 由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。 执行擦除时块尺寸的不同进一步拉大了NOR和NADN之间的性能差距,统

实验六 8051单片机串行口实验

实验六8051单片机串行口实验 一实验目的: 理解8051单片机串行口工作原理和方式。学习和掌握8051单片机实现通讯的环境和程序编写。了解PC机通讯的基本要求。 二实验原理: 在实时控制和管理方面,采用多台微机处理机组成分级分布控制系统中,各CPU之间的通信一般都是串行方式。所以串行接口是微机应用系统常用的接口。所谓“串行通信”是指外设和计算机间使用一根数据信号线(另外需要地线,可能还需要控制线),数据在一根数据信号线上一位一位地进行传输,每一位数据都占据一个固定的时间长度。如图6-1所示。这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,当然,其传输速度比并行传输慢。 图6-1 在串行通讯时,RS-232C接口是目前最常用的一种串行通讯接口,RS-232C使用-3到-25V表示数字“1”,使用3V到25V表示数字“0”,RS-232C在空闲时处于逻辑“1”状态。8051单片机上有UART用于串行通信,发送时由TXD端送出数据,接收时则由RXD端输入数据。它是一个可编程的全双工串行口。 SCON是串行口控制和状态寄存器,其格式如下: 表6-1 其中,SM0,SM1为串行口工作方式控制位,具体的工作方式如下表(表6-2)所示: 表6-2

SM2为多机通信控制位,当SM2=1时,只有接受到RB8为1,RI才置位,当SM2=0时,接受到字符RI就置位。REN为串行口接收允许位。工作在方式2和3时,TB8为发送的第9位数据,也可以用作奇偶校验位,RB8为接受到的第9位数据,而方式1时,RB8为接受到的停止位。TI,RI分别为发送接受中断标志位,均由硬件置位,软件清0。 PCON是电源控制寄存器,其格式如下: 表6-3 其中,SMOD为串行口波特率加倍位。当SMOD=1时,方式1,3波特率=定时器1溢出率/16,方式2波特率为fosc/32;当SMOD=0时,方式1,3波特率=定时器1溢出率/32,方式2波特率为fosc/64。 三实验内容: 单片机与微机相连,微机键入一个字符后发送至单片机,单片机收到后又将此字符发送回微机,在微机屏幕上回显。要求在11.0592MHZ下,串行口的波特率为9600,方式1。 四实验电路图: 图6-2 五实验方法: 1.根据如上电路图6-2连接好实验电路。自己接线请注意,DB9的2脚与MAX232的R2IN 相连,DB9的3脚与MAX232的T2OUT相连。DB9用针型插座,这样,单片机与PC 通信时,两者是同等地位,PC可以作为主机向单片机发送数据,单片机也可以作为主机向PC发送数据。 2.如果用他实验板就比较简单了,因为板上本来已经接好,只要用串行数据线将J9与PC 的串行口相连即可进行通信。 3.按照实验要求编写实验程序,建立新工程,保存为COMMU。 4.调试程序。

8051单片机的内部结构

8051是MCS-51系列单片机的典型产品,我们以这一代表性的机型进行系统的讲解。 8051单片机包含中央处理器、程序存储器(ROM)、数据存储器(RAM)、定时/计数器、并行接口、串行接口和中断系统等几大单元及数据总线、地址总线和控制总线等三大总线,现在我们分别加以说明: ·中央处理器: 中央处理器(CPU)是整个单片机的核心部 件,是8位数据宽度的处理器,能处理8 位二进制数据或代码,CPU负责控制、指 挥和调度整个单元系统协调的工作,完成 运算和控制输入输出功能等操作。 ·数据存储器(RAM): 8051内部有128个8位用户数据存储单 元和128个专用寄存器单元,它们是统一 编址的,专用寄存器只能用于存放控制指 令数据,用户只能访问,而不能用于存放 用户数据,所以,用户能使用的的RAM只 有128个,可存放读写的数据,运算的中 间结果或用户定义的字型表。 ·程序存储器(ROM): 8051共有4096个8位掩膜ROM,用于存放用户程序,原始数据或表格。 ·定时/计数器(ROM): 8051有两个16位的可编程定时/计数器,以实现定时或计数产生中断用于控制程序转向。 ·并行输入输出(I/O)口: 8051共有4组8位I/O口(P0、P1、P2或P3),用于对外部数据的传输。 ·全双工串行口: 8051内置一个全双工串行通信口,用于与其它设备间的串行数据传送,该串行口既可以 用作异步通信收发器,也可以当同步移位器使用。 ·中断系统: 8051具备较完善的中断功能,有两个外中断、两个定时/计数器中断和一个串行中断,可

满足不同的控制要求,并具有2级的优先级别选择。 ·时钟电路: 8051内置最高频率达12MHz的时钟电路,用于产生整个单片机运行的脉冲时序,但8051 单片机需外置振荡电容。 单片机的结构有两种类型,一种是程序存储器和数据存储器分开的形式,即哈佛(Harvard)结构,另一种是采用通用计算机广泛使用的程序存储器与数据存储器合二为一的结构,即普林斯顿(Pri nceton)结构。INTEL的MCS-51系列单片机采用的是哈佛结构的形式,而后续产品16位的MCS-96系列单片机则采用普林斯顿结构。 下图是MCS-51系列单片机的内部结构示意图。 ■MCS-51的引脚说明: MCS-51系列单片机中的8031、8051及8751均采用 40Pin封装的双列直接DIP结构,右图是它们的引脚配 置,40个引脚中,正电源和地线两根,外置石英振荡 器的时钟线两根,4组8位共32个I/O口,中断口线与 P3口线复用。现在我们对这些引脚的功能加以说明: ·Pin20:接地脚。

51单片机的串行接口

51单片机的串行接口 串行接口的一般概念 单片机与外界进行信息交换称之为通讯。 8051单片机的通讯方式有两种: 并行通讯:数据的各位同时发送或接收。 串行通讯:数据一位一位顺序发送或接收。参看下图: 串行通讯的方式 异步通讯:它用一个起始位表示字符的开始,用停止位表示字符的结束。其每帧的格式如下: 在一帧格式中,先是一个起始位0,然后是8个数据位,规定低位在前,高位在后,接下来是奇偶校验位(可以省略),最后是停止位1。用这种格式表示字符,则字符可以一个接一个地传送。 在异步通讯中,CPU与外设之间必须有两项规定,即字符格式和波特率。字符格式的规定是双方能够在对同一种0和1的串理解成同一种意义。原则上字符格式可以由通讯的双方自由制定,但从通用、方便的角度出发,一般还是使用一些标准为好,如采用ASCII标准。 波特率即数据传送的速率,其定义是每秒钟传送的二进制数的位数。例如,数据传送的速率是120字符/s,而每个字符如上述规定包含10数位,则传送波特率为1200波特。 同步通讯:在同步通讯中,每个字符要用起始位和停止位作为字符开始和结束的标志,占用了时间;所以在数据块传递时,为了提高速度,常去掉这些标志,采用同步传送。由于数据块传递开始要用同步字符来指示,同时要求由时钟来实现发送端与接收端之间的同步,故硬件较复杂。 通讯方向:在串行通讯中,把通讯接口只能发送或接收的单向传送方法叫单工传送;而把数据在甲乙两机之间的双向传递,称之为双工传送。在双工传送方式中又分为半双工传送和全双工传送。半双工传送是两机之间不能同时进行发送和接收,任一时该,只能发或者只能收信息。 2.8051单片机的串行接口结构 8051串行接口是一个可编程的全双工串行通讯接口。它可用作异步通讯方式(UART),与串行传送信息的外部设备相连接,或用于通过标准异步通讯协议进行全双工的8051多机系统也可以通过同步方式,使用TTL或CMOS 移位寄存器来扩充I/O口。 8051单片机通过引脚RXD(P3.0,串行数据接收端)和引脚TXD(P3.1,串行数据发送端)与外界通讯。SBUF是串行口缓冲寄存器,包括发送寄存器和接收寄存器。它们有相同名字和地址空间,但不会出现冲突,因为它们两个一个只能被CPU读出数据,一个只能被CPU写入数据。 串行口的控制与状态寄存器 串行口控制寄存器SCON 它用于定义串行口的工作方式及实施接收和发送控制。字节地址为98H,其各位定义如下表:

RAM、SRAM、SDRAM、ROM、EPROM、EEPROM、Flash等常见存储器概念辨析

RAM、SRAM、SDRAM、ROM、EPROM、EEPROM、Flash等常见存储器概念辨析 常见存储器概念辨析:RAM、SRAM、SDRAM、ROM、EPROM、EEPROM、Flash存储器可以分为很多种类,其中根据掉电数据是否丢失可以分为RAM(随机存取存储器)和ROM (只读存储器),其中RAM的访问速度比较快,但掉电后数据会丢失,而ROM掉电后数据不会丢失。 ROM和RAM指的都是半导体存储器,ROM是Read Only Memory的缩写,RAM是Random Access Memory的缩写。ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都是在掉电之后就丢失数据,典型的RAM就是计算机的内存。 RAM 又可分为SRAM(Static RAM/静态存储器)和DRAM(Dynamic RAM/动态存储器)。SRAM 是利用双稳态触发器来保存信息的,只要不掉电,信息是不会丢失的。DRAM是利用MOS(金属氧化物半导体)电容存储电荷来储存信息,因此必须通过不停的给电容充电来维持信息,所以DRAM 的成本、集成度、功耗等明显优于SRAM。SRAM速度非常快,是目前读写最快的存储设备了,但是它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓冲,二级缓冲。DRAM保留数据的时间很短,速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。 而通常人们所说的SDRAM 是DRAM 的一种,它是同步动态存储器,利用一个单一的系统时钟同步所有的地址数据和控制信号。使用SDRAM不但能提高系统表现,还能简化设计、提供高速的数据传输。在嵌入式系统中经常使用。 ROM也有很多种,PROM是可编程的ROM,PROM和EPROM(可擦除可编程ROM)两者区别是,PROM是一次性的,也就是软件灌入后,就无法修改了,这种是早期的产品,现在已经不可能使用了,而EPROM是通过紫外光的照射擦出原先的程序,是一种通用的存储器。另外一种EEPROM是通过电子擦出,价格很高,写入时间很长,写入很慢。 Flash也是一种非易失性存储器(掉电不会丢失),它擦写方便,访问速度快,已大大取代了传统的EPROM的地位。由于它具有和ROM一样掉电不会丢失的特性,因此很多人称其为Flash ROM。FLASH存储器又称闪存,它结合了ROM和RAM的长处,不仅具备电子可擦出可编程(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据(NVRAM 的优势),U盘和MP3里用的就是这种存储器。在过去的20年里,嵌入式系统一直使用ROM (EPROM)作为它们的存储设备,然而近年来Flash全面代替了ROM(EPROM)在嵌入式系统中的地位,用作存储bootloader以及操作系统或者程序代码或者直接当硬盘使用(U 盘)。 目前Flash主要有两种NOR Flash和NADN Flash。NOR Flash的读取和我们常见的SDRAM 的读取是一样,用户可以直接运行装载在NOR FLASH里面的代码,这样可以减少SRAM 的容量从而节约了成本。NAND Flash没有采取内存的随机读取技术,它的读取是以一次读取一快的形式来进行的,通常是一次读取512个字节,采用这种技术的Flash比较廉价。用户不能直接运行NAND Flash上的代码,因此好多使用NAND Flash的开发板除了使用NAND Flah以外,还作上了一块小的NOR Flash来运行启动代码。

Flash存储W25Q16芯片

Flash存储W25Q16芯片 1 一般描述 W25Q16BV(16M-bit)是为有限的空间、引脚和功耗的系统提供一个存储解决方案。25Q系列比普通的串行Flash存储器更灵活,性能更优越。基于双倍/四倍的SPI,它们能够可以立即完成提供数据给RAM,包括存储声音、文本和数据。芯片支持的工作电压2.7V到3.6V,正常工作时电流小于4mA,掉电时低于1uA。工作温度为-40℃到85℃。所有芯片提供标准的封装。 W25Q16BV由8192个编程页组成,每个编程页256-bytes。每页的256字节用一次页编程指令即可完成。每次擦除16页(扇区擦除)、128页(32KB块擦除)、256页(64KB块擦除)和全片擦除。W25Q16BV有512个可擦除扇区或32个可擦除块。最小4KB扇区允许更灵活的应用去要求数据和参数保存(见图2)。 W25Q16BV支持标准串行外围接口(SPI),和高速的双倍/四倍输出,双倍/四倍用的引脚:串行时钟、片选端、串行数据I/O0(DI)、I/O1(DO)、I/O2(WP)和I/O3(HOLD)。SPI最高支持104MHz,双倍速是208MHz,四倍速是416MHz。这个传输速率比得上8位和16位的并行Flash存储器。连续读模式允许利用少至8-clocks指令去读取24-bit 地址来实现高效的存储访问,允许真正的XIP(execute in place)操作。 HOLD引脚和写保护引脚可编程写保护。此外,芯片支持JEDEC标准,具有唯一的64位识别序列号。 2 特性 l SPI串行存储器系列●灵活的4KB扇区结构 -W25Q80:8M位/1M字节(1,048,576) -统一的扇区擦除(4K字节) -W25Q16:16M位/2M字节(2,097,152) -块擦除(32K和64K字节) -W25Q32:32M位/4M字节(4,194,304) -一次编程256字节 -每256字节可编程页 -至少100,000写/擦除周期

单片机80c51的串行口

80C51的串行口 下面是学习过程中的一些总结: 总括:计算机与外界信息的交换称为通信,主要有两种方式:并行通信:传输速度快,但传输线较多,价格较贵。 串行通信:数据的各位按顺序一位一位发送或接收。 大多数单片机都配置了SCI串行口,主要有两种方式: 1、异步通信:每个字符为一帧,要包括: 起始位、数据位、校验位、停止位。 每帧数据之间的时间间隔是不固定的,字符间的同步依靠通信 协议实现;帧内每一位数据的同步依靠收、发时钟实现 2、同步通信:信息流中的字符与字符间和字符内部位与位之间都 需要一个同步时钟。,可以把许多字符组成一个信息组,也称为一帧。 串行通信数据传输速率: 意义是每秒钟传送多少个二进制数。 一般异步通信在:50~9600bit/s 同步通信在:100~2Mbit/s 我们称之为比特率,但在二进制的情况下,比特率和波特率数值相同,故而一般称作“波特率”。

串行口简介: 组成:两个数据缓冲寄存器SBUF 一个串行口控制寄存器SCON 一个输入移位寄存器 串行口波特率发生器用于控制串行通信的速率(由内部的分频器和控制开关电路组成),它的振荡源可以来自单片机的振荡频率 f OSC,也可以来自定时/计数器的时钟输出。 外界数据通过引脚RXD(P3.0)输入。数据先逐位进入输入移位寄存器,在进入接收寄存器(SBUF),在接收器中采用了双缓冲结构,避免数据重叠(因为CPU是被动的)。 要发送的数据通过发送控制器控制逻辑门电路经输出移位寄存器一位一位输出到TXD(P3.1)。

串行口控制寄存器SCON: SM0,SM1为串行方式选择位,可以有四种方式; SM2为多机通信控制位,在方式2、3中配合发送/接收数据的第九位(TB8/RB8)对主机发来的数据识别并处理。 REN为允许串行接收位,要由软件控制置1为允许接收。 TI、RI为发送/接收中断标志位。 注意:在发送完数据后硬件会自动置TI为1,若要继续发送,必须用软件清零。准备接收时,首先要清零RI,接收完8位数据后硬件会自动置RI为1,然后执行读数据指令MOV A,SBUF,然后一定要清RI为0。 波特率的设置: 方式0:时钟频率的1/12,不受SMOD位影响。 方式2: (2SMOD/64)*f osc 方式1和3:(2SMOD/32)*T1溢出率 T1溢出周期:(12/f osc)*(256-X)和定时器有关了 我们一般是根据波特率计算溢出初值X。

STM32的FLASH存储器

关于STM32的FLASH操作 说到STM32的FLSAH,我们的第一反应是用来装程序的,实际上,STM32的片内FLASH不仅用来装程序,还用来装芯片配置、芯片ID、自举程序等等。当然,FLASH还可以用来装数据。 FLASH分类 根据用途,STM32片内的FLASH分成两部分:主存储块、信息块。 主存储块用于存储程序,我们写的程序一般存储在这里。 信息块又分成两部分:系统存储器、选项字节。 系统存储器存储用于存放在系统存储器自举模式下的启动程序(BootLoader),当使用ISP方式加载程序时,就是由这个程序执行。这个区域由芯片厂写入BootLoader,然后锁死,用户是无法改变这个区域的。 选项字节存储芯片的配置信息及对主存储块的保护信息。 FLASH的页面 STM32的FLASH主存储块按页组织,有的产品每页1KB,有的产品每页2KB。页面典型的用途就是用于按页擦除FLASH。从这点来看,页面有点像通用FLASH的扇区。 STM32产品的分类 STM32根据FLASH主存储块容量、页面的不同,系统存储器的不同,分为小容量、中容量、大容量、互联型,共四类产品。 小容量产品主存储块1-32KB,每页1KB。系统存储器2KB。 中容量产品主存储块64-128KB,每页1KB。系统存储器2KB。 大容量产品主存储块256KB以上,每页2KB。系统存储器2KB。 互联型产品主存储块256KB以上,每页2KB。系统存储器18KB。 对于具体一个产品属于哪类,可以查数据手册,或根据以下简单的规则进行区分:STM32F101xx、STM32F102xx 、STM32F103xx产品,根据其主存储块容量,一定是小容量、中容量、大容量产品中的一种,STM32F105xx、STM32F107xx 是互联型产品。 互联型产品与其它三类的不同之处就是BootLoader的不同,小中大容量产品的BootLoader只有2KB,只能通过USART1进行ISP,而互联型产品的BootLoader 有18KB,能通过USAT1、4、CAN等多种方式进行ISP。小空量产品、中容量产品的BootLoader与大容量产品相同。 关于ISP与IAP ISP(In System Programming)在系统编程,是指直接在目标电路板上对芯片进行编程,一般需要一个自举程序(BootLoader)来执行。ISP也有叫ICP(In Circuit Programming)、在电路编程、在线编程。 IAP(In Application Programming)在应用中编程,是指最终产品出厂后,由最终用户在使用中对用户程序部分进行编程,实现在线升级。IAP要求将程序分成

TMS320C6201DSP处理器与FLASH存储器接口设计(精)

TMS320C6201 DSP处理器与FLASH存储器接口设计 DSP是针对实时数字信号处理而设计的数字信号处理器,由于它具有计算速度快、体积小、功耗低的突出优点,非常适合应用于嵌入式实时系统。自世界上第一片通用D5P芯片TMS320C10于1982年在美国T1公司产生以来,DSP处理器便显示出强盛的生命力。短短二十多年,世界上许多公司便开发出各种规格的DSP处理器,并使它们在通信、自动控制、雷达、气象、导航、机器人等许多嵌入式实时领域得到了广泛应用。20世纪90年代后期美国TI公司推出的面向通讯领域的新一代32位的T MS320C6000系列DSP芯片(简称C6000)是目前世界上最先进的DSP处理器,其中C62XX和C64XX为通用32位定点系列DSP处理器,C67XX为通用32位浮点系列DSP处理器,其指令速度分别高达960~4800MIPS和600MFLOPS~1GFLOPS,可与早期的巨型计算机速度相媲美,且单芯片功耗小于1.5W、采用BGA封装(小型球栅阵列)、体积也很小(最大35mm×35mm×3.5mm)。因此,这些DSP处理器将在许多科技领域发挥重要作用。FLASH存储器是新型的可电擦除的非易失性只读存储器,属于EEPROM器件,与其它的ROM器件相比,其存储容量大、体积小、功耗低,特别是其具有在系统可编程擦写而不需要编程器擦写的特点,使它迅速成为存储程序代码和重要数据的非易失性存储器,成为嵌入式系统必不可少的重要器件。DSP与FLASH存储器的接口设计是嵌入式系统设计的一项重要技术,本文以基于三个C6201/C6701 DSP芯片开发成功的嵌入式并行图像处理实时系统为例,介绍这一设计技术。 1 C6201/C6701新一代DSP处理器 1.1 C6201/C6701的特点及外部存储器接口EMIF C6201为通用32位定点DSP处理器,C6701为通用32位浮点DSP处理器,它们采用并行度很高的处理器结沟,从而具有许多突出的特点: DSP核采用改进的超长指令字(VLIW)体系结构和多流水线技术,具有8个可并行执行的功能单元,其中6个为ALU,两个为乘法器,并分成相同功能的两组,在没有指令相关情况下,最高可同时执行8条并行指令;·具有32个32位通用寄存器,并分成两组,每组16个,大大加快了计算速度; 片上集成了大容量的高速程序存储器和数据存储措,最高可以200Mbit/s 的速度访问,并采用改进的多总线多存储体的哈佛结构。程序存储器为64K字节、256位宽.每个指令周期可读取8个指令字,还可灵活设置为高速CACHE 使用;数据存储器采用双存储块,每个存储块又采用多个存储体,可灵活支持8/16/32位数据读写。C6701还可支持64位访问,每个时钟可访问双32位故据.C6701还可访问双64位IEEE双精度浮点数据;片上集成了32位外部存储器接口EMIF,并且分成4个时序可编程的空间(CE0、CEl、CE2、CE3),可直接支持各种规格SDRAM(除CEl空间外)、SBSRAM、SRAM、ROM、FLASH、FIFO存储器。同时,CEl空间还可直接支持8/16位宽的异步存储器读访问,EMIF接口信号如图1所示; 片上集成了4个主DMA控制器和一个辅助DMA控制器: 片上集成了两个32位多功能定时器;

Flash存储器概述

This document contains information on one or more products under development at Spansion LLC. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed product without notice. Publication Number FlashOverview_AN Revision A Amendment 0 Issue Date November 10, 2005 Introduction All computer-based systems contain memory. Memory is where information is stored while waiting to be operated on by the Central Processing Unit (CPU) of the computer . There are two types of memory. They are volatile memory and non-volatile memory. Volatile memory retains its information only while power is applied to the memory de-vice. The contents of this memory type may be easily and quickly changed. Non-volatile memory retains its information even when no power is applied to the memory device. Although the information in most non-volatile memories may be changed, the process involved is much slower than for volatile memory. Volatile Memory Volatile memory loses its contents when the device loses power . Random Access Mem-ory (RAM) is the traditional name used for volatile memory. The name refers to the ability to access any location of the memory quickly with no particular order of accesses needed. Static RAM (SRAM) and Dynamic RAM (DRAM) are two examples of volatile memories that have this characteristic. SRAM typically uses six transistors for each memory bit (cell) to retain data as long as power is being supplied. This makes each memory cell relatively large and limits SRAM to use in lower density memories. SRAM can provide faster access to data, use less standby power , and tends to be more expensive than DRAM. DRAM uses a single transistor and a small capacitor for each bit of memory. Since ca-pacitors do not hold a charge indefinitely, DRAM cells must be frequently recharged (refreshed) to avoid losing the contents. These smaller memory cells allow DRAM to be used for high density, low cost memories, but are typically slower than SRAM. Flash Memory: An Overview Application Note