一种低功耗射频CMOS电荷泵锁相环的设计_周海峰

第39卷第1期2009年2月

微电子学Microelectronics

Vo l 139,N o.1Feb.2009

收稿日期:2008-06-11;定稿日期:2008-10-31

基金项目:国家高技术研究发展(863)计划基金资助项目(2008A A 04Z309)

一种低功耗射频CM OS 电荷泵锁相环的设计

周海峰,韩 雁,董树荣,韩晓霞,程维维

(浙江大学微电子与光电子研究所,杭州310027)

摘 要: 描述了基于P 型CSL(Current Steer Log ic)架构压控振荡器的低功耗射频锁相环设计。

其鉴频鉴相器模块采用预充电模式,具有高速、无死区等特点;电荷泵模块在提高开关速度的基础上,改进了拓扑结构,使充放电电流的路径深度相同,更好地实现了匹配;为了达到宽调谐范围的目的,电荷泵模块采用1.8V 电源电压,而压控振荡器模块采用3.3V,这样可充分利用电荷泵的输出电压范围实现宽调谐。电路设计基于0.18L m 1P6M CM OS 工艺,芯片实测结果显示,锁相环工作在940M H z~ 2.23GH z 的频率范围内,功耗低于15.2m W,芯片面积为750L m @400L m(不包括IO)。

关键词: 锁相环;射频;压控振荡器;电荷泵

中图分类号:T N402 文献标识码:A

文章编号:1004-3365(2009)01-0049-04

A Low -Pow er RF CM OS Charge Pum p PL L

ZH OU H aifeng ,H AN Yan,DONG Shurong,H AN Xiao xia,CH ENG W eiw ei

(1.I nstitu te of M icr oelec tr onics and Ph otoe lec tr onics ,Zhe j iang Unive rsity ,H ang z hou 310027,P.R.China)

Abstract: A phase -lo cked lo op (PL L )based on voltage co nt ro lled o scillator (VCO )w ith P -type CSL (Cur rent

St eer L og ic)structure w as pr esented.A pre -char ge mode w as used in phase/frequency detecto r to realize hig h speed and dead zo ne free,etc.T he topolog y of the cir cuit w as also enhanced to equalize the dept hs of char ge and discharg e cur rents,w hich impr ov ed the cir cuit matching.In or der to ex pand the tuning range of the PL L ,a 1.8V po wer sup -ply w as used in the cha rge pump mo dule,while a 3.3V pow er supply was used for VCO mo dule.T his cir cuit w as implement ed in a 0.18L m 1P 6M CM O S technolog y,and the co re chip occupied an ar ea of 750L m @400L m.T est results sho wed that the PL L o per ated in the fr equency r ang e betw een 940M H z and 2.23GH z,w ith a pow er con -sumpt ion less than 15.2mW.

Key words: P hase lo cked loo p (P LL );R adio frequency (RF );Vo ltag e contro lled oscillato r (V CO);Charg e

pump

EEACC : 1280;2220

1 引 言

锁相环(PLL)技术广泛应用于通讯系统的时钟恢复及无线通讯系统的频率合成

[1,2]

。随着便携式

电子产品的流行,在VSLI 设计中,功耗成为设计关注的重点。随着SOC 的发展,PLL 需要集成在同一块芯片上,这对PLL 设计提出了更高的要求

[3,4]

。

低功耗的设计通常利用低电源电压来实现,但

是,降低电源电压往往受到所要求的工作频率的限

制;另外,这也限制了在电源和地之间用于提供尾电流的偏置电路的级联级数。

本文采用CSL 结构的压控振荡器设计低功耗射频锁相环,电路结构简单、性能高;电荷泵模块采用1.8V 电源电压,压控振荡器模块采用3.3V,这样可充分利用电荷泵的输出电压范围,使锁相环的锁频范围扩大。

2 锁相环结构

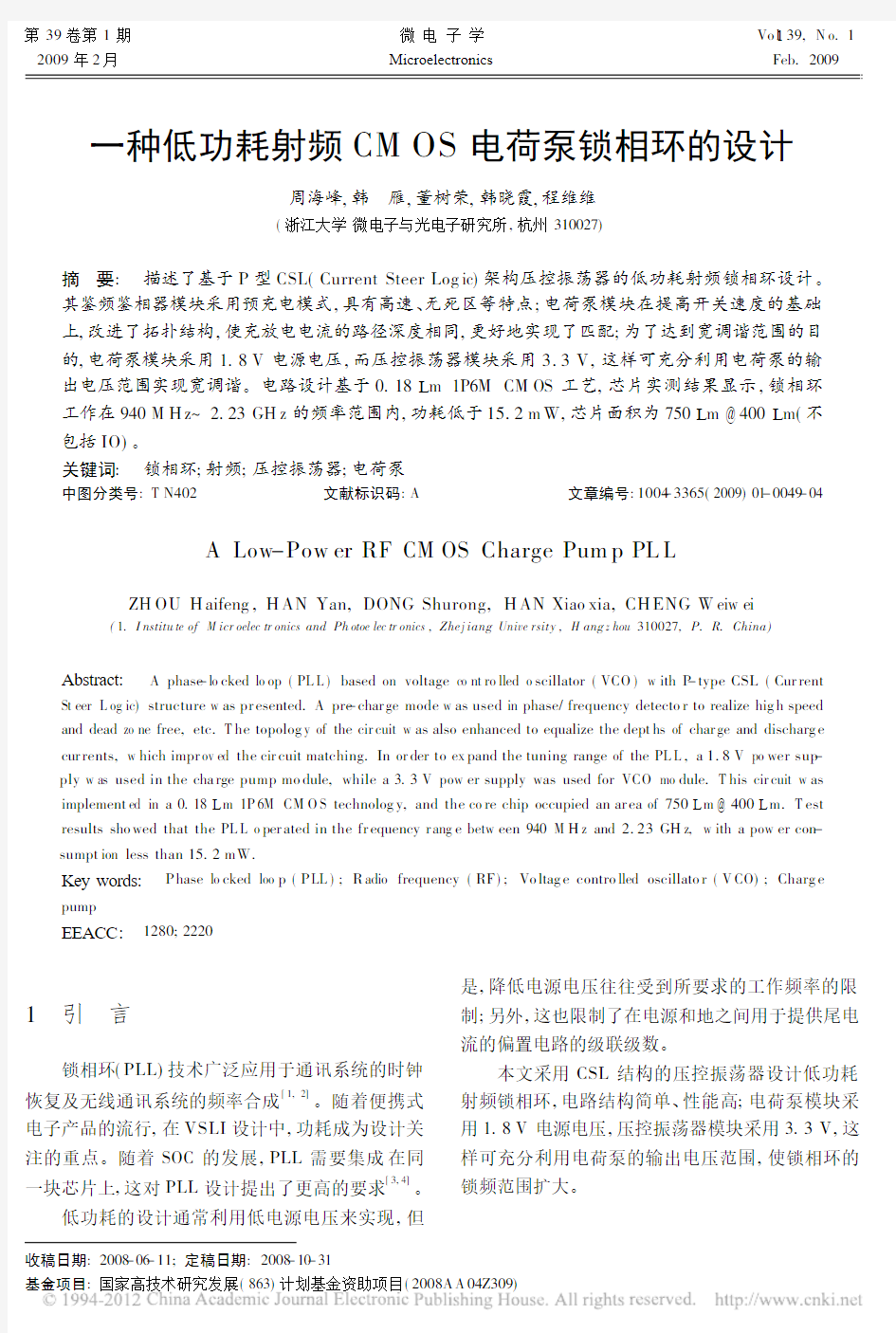

锁相环实现的功能是使输入参考信号与反馈的比较信号频率及相位一致。基于整数N 分频的频率合成器的方框图如图1所示。电路中,鉴频鉴相器(PFD)检测参考信号F in 及反馈信号F f b 在频率和相位上的偏差,PFD 输出的U P 、DOWN 数字信号控制电荷泵(CP)电路,将F in 和F f b 的偏差转换成相应的电流逻辑状态,环路滤波器(LF)将该电流转换为模拟电压,并滤除高频信号噪声;环路滤波器的输出电压用来控制压控振荡器(VCO)的输出频率,分频器(FB)置于反馈回路中,提供分频比N ,压控振荡器的输出频率最终锁定在参考频率的N

倍。

图1 电荷泵锁相环结构框图

Fig.1 Block diagr am of the char ge -pump P LL

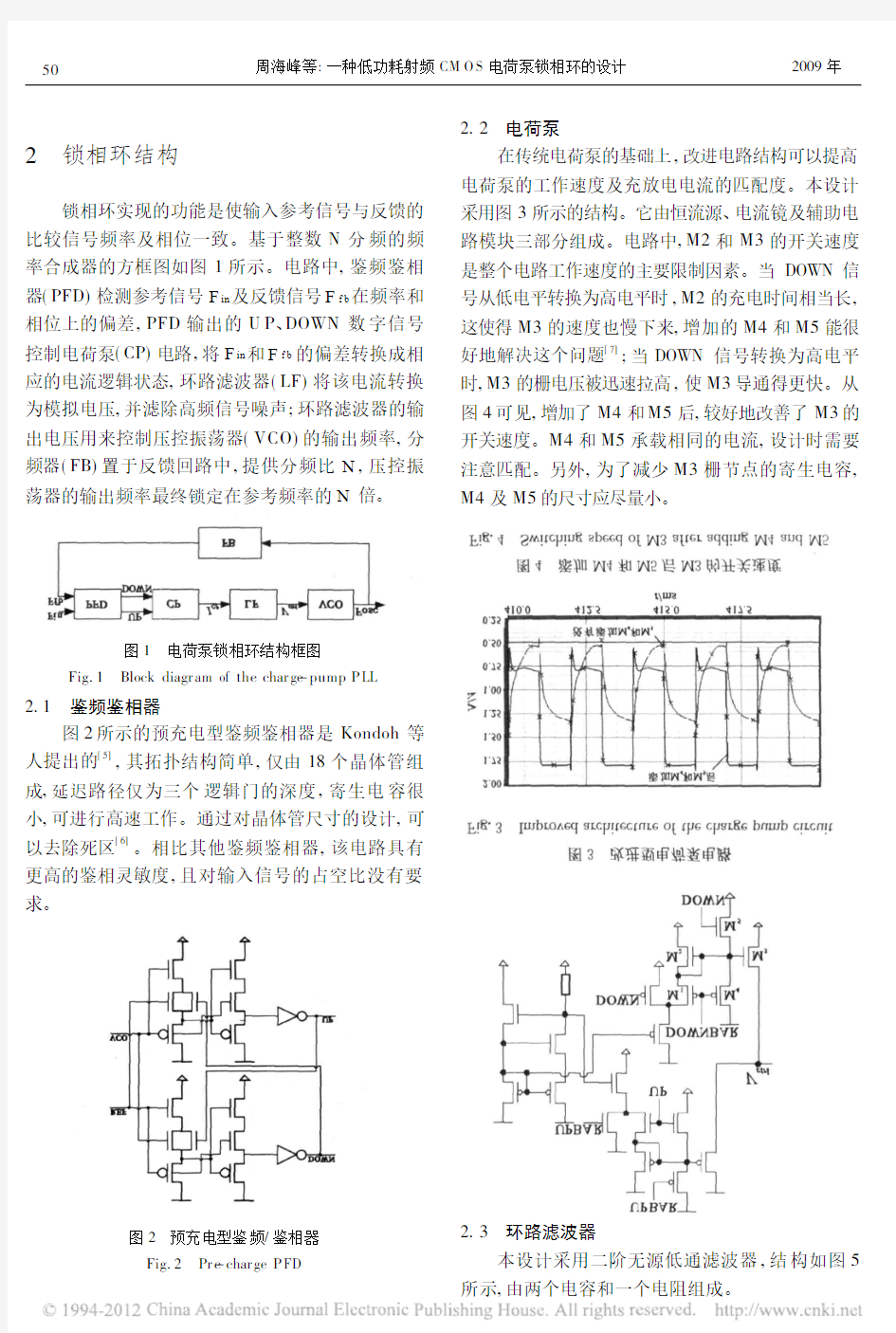

2.1 鉴频鉴相器

图2所示的预充电型鉴频鉴相器是Kondoh 等人提出的[5],其拓扑结构简单,仅由18个晶体管组成,延迟路径仅为三个逻辑门的深度,寄生电容很小,可进行高速工作。通过对晶体管尺寸的设计,可以去除死区[6]

。相比其他鉴频鉴相器,该电路具有更高的鉴相灵敏度,且对输入信号的占空比没有要

求。

图2 预充电型鉴频/鉴相器Fig.2 Pr e -char ge P FD

2.2 电荷泵

在传统电荷泵的基础上,改进电路结构可以提高电荷泵的工作速度及充放电电流的匹配度。本设计采用图3所示的结构。它由恒流源、电流镜及辅助电路模块三部分组成。电路中,M2和M3的开关速度是整个电路工作速度的主要限制因素。当DOWN 信号从低电平转换为高电平时,M2的充电时间相当长,这使得M3的速度也慢下来,增加的M4和M5能很好地解决这个问题[7];当DOWN 信号转换为高电平时,M3的栅电压被迅速拉高,使M3导通得更快。从图4可见,增加了M4和M5后,较好地改善了M3的开关速度。M4和M5承载相同的电流,设计时需要注意匹配。另外,为了减少M3栅节点的寄生电容,M4及M5

的尺寸应尽量小。

2.3 环路滤波器

本设计采用二阶无源低通滤波器,结构如图5所示,由两个电容和一个电阻组成。

图5 环路滤波器F ig.5 2nd -o rder passive filter

环路滤波器的开环传输函数为:F(s)=(R 1+1sC 11

sC 2)=s S z +1s(C 1+C 2)(1+s S p )

(1)

S

z =R 1C 1,S p =R 1C 1C 2

C 1+C 2

(2)

锁相环的开环传输函数为:G(s)=

K PFD K VCO F (s)sN =K PFD K VCO s 2N(C 1+C 2)1+s S z

1+s S p

(3)

]G(s)s =j X

=-

K PFD K VCO X 2

N (C 1+C 2)1+j X S z

1+j X S p

(4)

则环路的相位函数为:

U (X )=tan -1(X S z )-tan -1

(XS p )+180b (5)

设d U

(X )d X =0,得到环路带宽: X =X c ]X c =

1

S z S p

(6) ]U max =tan -1

(X c S z )-tan -1

(X c S p )(7) ]S p =

sec U max -tan U max X c ,S z =1

X 2

c S p

(8)

当X =X c 时,G(j X )=1,推出: ]C 2=

S

p S z

K PFD K VCO X 2N 1+(X C S Z )

2

1+(X C S P )2

(9) ]C 1=C 2S z

S p

-1(10) ]R 1=

S z C 1

(11)

由(9)、(10)、(11)式,可计算出环路滤波器中元器件的值。

3 压控振荡器

压控振荡器(VCO)是PLL 中的重要模块,其主要设计指标如下

[8]

。

1)调谐范围:VCO 的输出频率范围须覆盖应用环境中所需要的全部频率。

2)调谐线性度:理想的VCO 应在整个频率范

围内具有恒定的VCO 增益K VCO 。VCO 增益的恒定将给PLL 的设计带来简化。

3)功耗:VCO 在射频情况下有较大的动态功耗;在低频情况下则有较大的短路功耗,且VCO 是PLL 系统中主要的功耗源。

在PLL 电路中,环形V CO 电路可分为两种:单

端VCO 和差分VCO 。这两种结构各有优缺点。一般而言,单端VCO 电路的输出频率范围比较宽,差分VCO 电路相对会窄一些;但是,在抑制电源噪声方面,差分结构会好一些。本文采用单端VCO 中的CSL 架构。该结构一般用在低电压逻辑电路中,具有低功耗的特点,其结构如图6(a)所示[9]。

图6 (a)P 型CSL 延时单元;(b)电压传输曲线及噪声容限F ig.6(a)P -ty pe CSL delay cell;(b)VT C and no ise marg ins

本设计采用PM OS 对管作为电流控制延时单元的开关管,NMOS 作为电流源器件。这是考虑到可用N 阱隔离衬底对PM OS 对管的噪声,同时通过深阱工艺隔离衬底对NM OS 电流源的噪声,使衬底噪声整体上得到有效抑制。

上述P 型CSL 结构包括输入PM OS 开关管

M 1,二极管形式连接的M2及NMOS 电流源M3。经过推导,振荡幅度的表达式为:

$V =V O H -V O L =V tp +V dsatM 21-1G V (12)

其

中,

G v

=

(W/L)1

(W/L)2

,

V dsatM 2

=

2I bias /K c p (W /L)2。输出电压摆幅随偏置电流I bias 的平方根变化。

从电路的电压转移特性曲线(图6(b)),可推导出CSL 延时单元的噪声容限:

N M L =V dsatM 2(1-2

3G V

)(13)NM H =V tp +V dsa tM 2(

1

G 2V

-G V

+

G V -1

G B

-1)(14)

由以上分析可知,噪声容限和电路速度均受到G V 的影响。设计中,G V 取2~4之间。

当在CSL 输入端加入阶跃信号源时,根据动态特性分析,输出上升延迟时间t lh 和下降延迟时间t hl 分别为[10]:

t lh =A C out I bias (15) t hl =B C out I bias

(16)

式中,A 和B 为常数,可见该环形振荡器的输出频率与偏置电流I b ias 成正比,测试结果也证实了这一点。从(12)式也可看出,随着输出频率的提高,输出电压的摆幅也会增加,这对电源噪声的抑制是有益的。

图7是一个3级CSL 架构压控振荡电路,前一级是电压电流转换电路,中间是振荡级,后级是输出缓冲级。其中采用低净空压降的共源共栅电路来提高电流源的输出电阻,适合低压应用

[11]

。

图7 电流控制振荡电路

F ig.7 Schematics of V CO w ith p -type CSL str ucture

4 测试结果

本文锁相环采用0.18L m 1P6M CM OS 工艺实现。图8为流片后的裸片图,PLL 模块为750L m @400L m (不含IO)

。

图8 锁相环芯片照片F ig.8 Photog r aph of the PL L chip

环路设计中,电荷泵模块采用1.8V 电源电压,

VCO 模块采用3.3V 电源电压,这样可充分利用电荷泵的输出电压范围,扩大锁相环的锁定范围。图9所示为锁相环的锁定范围及与控制电压的关系。从图中可以看出,控制电压从0.17V 变化到1.72V,环路均能锁定。锁相环输出的频率范围为940M H z 到2.23GH z

。

图9 PL L 锁定频率范围及与控制电压的关系Fig.9 T uning character istics of the V CO

图10所示为压控振荡器及PLL 的功耗与频率的关系。随着输出频率的增加,VCO 及PLL 的功耗也随之增加,且VCO 的功率与输出频率呈良好的线性关系,这是由于CSL 结构的VCO 输出频率与它的偏置电流成正比,

即与功耗成正比。

图10 VCO 和P LL 的功耗与频率的关系

F ig.10 P ower consumptio n o f VCO and PL L vs.fr equency

(下转第57页)

5 结 论

设计了一个P 型CSL 架构的射频压控振荡器锁相环。设计中,采用预充电型鉴频鉴相器,且改进了电荷泵结构。电路采用0.18L m 1P6M CM OS

工艺实现。实测结果显示,锁相环工作在很宽的频率范围内,从940MH z 到2.23GH z;芯片面积小、功耗低、最大功耗仅15.2m W 。

第1期龙英等:任意阶开关电流低通滤波器的系统设计

计具有非常重要的意义。

参考文献:

[1]H U G HES J B,BIRD N C,M ACBET H I C,Sw itched-

curr ent s,a new technique for analog ue sampled-data signal pr ocessing[C]//I EEE Cir c and Sy st Symp.

Por tland,U SA.1989:1584-1587.

[2]N GA E J,SEWEL L J I.Feasible designs for hig h or-

der sw itched-current filters[J].I EE Dev Circ and Syst.1998,145(5):297-305.

[3]BARU A A,CH A NDR AK A R M K.SYSCU F:auto-

mated synthesis of sw itched current filter[C]//P roc

7t h IEEE I nt Co nf Electro,Cir c and Sy st.Jounieh,

L ebanon.2000:999-1003.

[4]ROBERT S G W,SEDRA A S.Synthesizing switched

current filter by transposing the SFG of sw itched capacitor

filter circuits[J].IEEE Trans Circ and Syst,1991,38

(2):337-340.

[5]FI EZ T,A LL ST O T D.A CM O S sw itched cur rent fi-l

ter technique[J].IEEE Int Sol Sta Cir c Conf,1990,

37(2):206-207.

[6]T O U M A ZOU C,HU GH ES J B,BA T T ERSBY N C.

Sw itched-cur rents:an analog ue technique for digital

technolog y[M].L o ndon:Peter Per egr inus L td,

1993:161-175.

[7]GA O Q ing yun,Q IN Shicai,JIA Xiangluan,et al.

Co mputer aided desig n of sw itched current filters[C]

//Pro c4th I nt Conf ASIC.Shanghai,China.2001:

94-97.

[8]高清运,曹政新.开关电流双二次滤波器的设计[J].

固体电子学研究与进展,2003,23(3):287-291. [9]朱达斌.开关电流椭圆低通滤波器的设计[J].电路

与系统学报,1999,4(1):64-69.

作者简历:

龙英(1975)),女(汉族),湖南安化人,讲师,2006年6月于湖南师范大学

获硕士学位,主要研究方向为开关电流技

术、滤波器设计和信息处理等。

何怡刚(1966)),男(汉族),湖南邵阳人,博士,教授,学术带头人,主要研究方向

为模拟与数字系统自动测试与故障诊断、

电工新技术、高速低功耗电路与系统、智能

信号与信息处理、VLSI、SOC、MEM S理

论、设计与测试等。

(上接第52页)

参考文献:

[1]RA ZA V I B.M ono lithic phase-locked loo ps and clo ck

recov ery circuits theo ry and desig n[M].IEEE P ress,

1996.

[2]张奉江,周述涛,李儒章,等.一种新型低抖动快速

锁定时钟稳定电路[J].微电子学,2008,38(1):137-

140.

[3]CH EN R-Y,H SI EH M-Y,PEN G P-M,A w ide-range

pow er-efficient CM OS phase-locked loo p w ith a differ-

ential rang e-pr og rammable V CO[C]//I nt Sy mp Sig n,Circ and Sy st.2005.2:673-676.

[4]李明剑,万天才,刘永光.单片集成的高频宽带LC

V CO设计[J].微电子学,2007,37(6):794-797. [5]K ON DO H H. 1.5-V250-M Hz t o3.0-V622-M Hz op-

eration CM OS phase-locked loo p w ith pr echarg e ty pe

phase-fr equency detector[J].I EICE T r ans Electr on-

ics.1995,78-C(4):381-388.

[6]谭润钦,史江一,马晓华.预充电型鉴频鉴相器pt-

PF D的分析与改进[J].电子质量,2004,(9):56-

58.[7]杨运福,戴庆元,刘天伟.一种新型的低电压高速

CM O S锁相环电荷泵[J].微处理机,2006,(3):11-

13.

[8]CH EN G K-H,L A I C-Y,L O Y-L.A CM OS V CO for

1V,1GH z P L L applications[C]//Pr oc IEEE A sia-

Pacific Conf A dv Syst Integr Circ.2004:150-153. [9]SA EZ R T L,K A YA L M,D ECL ERCQ M,et al.De-

sig n g uidelines fo r CM OS cur rent st eer ing log ic[C]//

IEEE Int Symp Circ and Sy st.1997:1982-1885. [10]缪国清,徐国庆,唐璞山,等.一种适用于模/数混

合集成电路的新型低噪声电流控制逻辑[J].半导体

学报,1997,18(3):184-192.

[11]L EE T H.T he design of CM OS radio-fr equency inte-

gr ated circuits[M].Cambr idg e,U K:Cambridg e

U niver sity Press,1998:239-240.

作者简介:

周海峰(1981)),男(汉族),江苏泰兴人,博士研究生,主要研究方向为纳米器件

与射频集成电路设计。

57

锁相环设计

锁相环测量简述 一、锁相环路的基本工作原理 锁相环路是一个相位反馈自动控制系统。它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。其组成方框图如下所示。 锁相环路的基本方框图 锁相环可用来实现输出和输入两个信号之间的相位同步。当没有基准(参考)输入信号时,环路滤波器的输出为零(或为某一固定值)。这时,压控振荡器按其固有频率fv进行自由振荡。当有频率为fR的参考信号输入时,uR 和uv同时加到鉴相器进行鉴相。 如果fR和fv相差不大,鉴相器对uR和uv进行鉴相的结果,输出一个与uR和uv的相位差成正比的误差电压ud,再经过环路滤波器滤去ud中的高频成分,输出一个控制电压uc,uc将使压控振荡器的频率fv(和相位)发生变化,朝着参考输入信号的频率靠拢,最后使fv= fR,环路锁定。 环路一旦进入锁定状态后,压控振荡器的输出信号与环路的输入信号(参考信号)之间只有一个固定的稳态相位差,而没有频差存在。环路的锁定状态是对输入信号的频率和相位不变而言的,若环路输入的是频率和相位不断变化的信号,而且环路能使压控振荡器的频率和相位不断地跟踪输入信号的频率和相位变化,则这时环路所处的状态称为跟踪状态。锁相环路在锁定后,不仅能使输出信号频率与输入信号频率严格同步,而且还具有频率跟踪特性,所以它在电子技术的各个领域中都有着广泛的应用。 二、环路部件的测量 I.鉴相器特性的测量 鉴相器的主要性能可用鉴相特性曲线和鉴相灵敏度来表示。 鉴相特性曲线是表示鉴相器的输出电压Vd与两个输入比相信号之间相位差θe的关系曲线,其测量方法如右图所示,在测量精度要求不高的情况下,可用双踪示波器来代替相位计。

LED日光灯电源的设计要求

关于外形 现在LED日光灯电源,做灯的厂家普遍要求放在灯管内,如放T8灯管内.很少一部分外置.不知道为什么都要这样.其实内置电源又难做,性能也不好.但不知为什么还有这么多人这样要求.可能都是随风倒吧.外置电源应该说是更科学,更方便才对.但我也不得不随风倒,客户要什么,我就做什么.但做内置电源,有相当难度哦.因为外置的电源,形状基本没有要求,想做多大做多大,想做成什么形状也没关系.内置电源,只能做成两种,一种是用的最多的,就是说放在灯板下面,上面放灯板。 下面是电源,这样就要求电源做的很薄,不然装不进.而且这样只能把元件倒下,电源上的线路也只有加长.我认为这样不是个好办法.不过大家普遍喜欢这样搞.我就搞.还有就是用的少一些,放两端的,即放在灯管两头,这样好做些,成本也低些.我也有做过,基本就是这两种内置形状了。 关于此种电源的要求和电路结构的问题 我的看法是,因为电源要内置在灯里,而发热是LED光衰最大的杀手,所以发热一定要小,就是效率一定得高.当然得有高效率的电源.对于T8一米二长的那种灯,最好是不要用一支电源,而是用二支,两端各一只,将热量分散.从而不使热量集中在一个地方.电源的效率主要取决于电路的结构和所用的器件.先说电路结构,有些人还说要隔离电源,我想绝对是没必要的,因为这种东西本来就是置于灯体内部,人根本摸不到.没必要隔离,因为隔离电源的效率比不隔离效率要低,第二是,最好输出要高电压小电流,这样的电源才能把效率做高.现在普遍用到的是,BUCK电路,即降压式电路.最好是把输出电压做到一百伏以上,电流定在100MA 上那样,如驱动一百二十只,最好是三串,每串四十只,电压就是一百三十伏,电流60MA.这种电源用的很多,本人只是认为有一点不好,如果开关管失控通咱,LED会玩完.现在LED这么贵.我比较看好升压式电路,此种电路的好处,我反复的说过,一是效率较降压式的高些,二是电源坏了,LED灯不会坏.这样能确保万无一失,如果烧坏一个电源,只是损失几块钱,烧一个LED日光灯,就会赔掉上百元的成本.所以我一直首推还是升压式的电源.还有就是,升压式电路,很容易把PF值作高,降压式的就麻烦一些.我绝对升压式电路用于LED日光灯的好处还是有压倒性的强于降压式的.只是有一年缺点,就是在220V市电输入情况下,负载范围比较窄,一般只能适用于100至140个一串或两串LED,对于少于此数的,或是夹在中间的,却用起来不方便.不过现在做LED日光灯的,一般60CM长那种都是用100至140,一米二的那种,一般就是用二百到二百六那样,使用起来还是可以的.所以现在LED日光灯一般使用的是不隔离降压电路,还有不隔离升压电路,此种电路用于LED日光灯,应该可以算是本人首创。 关于高PFLED日光灯电源,大电流的LED日光灯电源的看法: 个人认为这些做法有很多时候实在是舍本逐末而已.现在先请问一下LED相对于传统灯具的优势在哪,第一,节能,第二长寿,然后是不怕开关,对吧.但是现在使用的高PF的方法,均是使用无源填谷PF电路,由原来的驱动方式,即48串,6并改为,24串12并,这样的话,在220V榭鱿?效率会降下五个百分点左右,于是LED日光灯电源,发热量更高了,灯珠也会受到一点影响。 还有一个问题,就是,24串12并的做法,会让LED日光灯灯珠的布线变的很难受,不好布线了.我看,最好的方式还是48串一串方式好,主要是效率高,发热小,而且布线容易,不复杂。 更有甚者,现在还有人提出什么24并,12串,这种方式只适合用于隔离电源,不隔离电源根本不适用.更有些不懂电源常识的人觉得自己非隔离电源做到恒流600MA输出就好牛比了,其实他都没有自己仔细的放在灯管里试过,象这种不热爆了才怪。所以说,现在搞什么低压大

PLL(锁相环)电路原理及设计 [收藏]

PLL(锁相环)电路原理及设计[收藏] PLL(锁相环)电路原理及设计 在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。如果采用PLL(锁相环)(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。 一PLL(锁相环)电路的基本构成 PLL(锁相环)电路的概要 图1所示的为PLL(锁相环)电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。 此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Controlled Oscillator……电压控制振荡器)的相位比较。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。 (将VCO的振荡频率与基准频率比较,利用反馈电路的控制,使两者的频率为一致。) 利用此一误差信号,可以控制VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致。 PLL(锁相环)可以使高频率振荡器的频率与基准频率的整数倍的频率相一致。由于,基准振荡器大多为使用晶体振荡器,因此,高频率振荡器的频率稳定度可以与晶体振荡器相比美。 只要是基准频率的整数倍,便可以得到各种频率的输出。 从图1的PLL(锁相环)基本构成中,可以知道其是由VCO,相位比较器,基准频率振荡器,回路滤波器所构成。在此,假设基准振荡器的频率为fr,VCO的频率为fo。 在此一电路中,假设frgt;fo时,也即是VC0的振荡频率fo比fr低时。此时的相位比较器的输出PD 会如图2所示,产生正脉波信号,使VCO的振荡器频率提高。相反地,如果frlt;fo时,会产生负脉波信号。

锁相环电路设计

锁相环的原理 2007-01-23 00:24 1.锁相环的基本组成 许多电子设备要正常工作,通常需要外部的 输入信号与部的振荡信号同步,利用锁相环 路就可以实现这个目的。 锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成的原理框图如图8-4-1所示。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u D(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u C(t),对振荡器输出信号的频率实施控制。 2.锁相环的工作原理 锁相环中的鉴相器通常由模拟乘法器组成,利用模拟乘法器组成的鉴相器电路如图8-4-2所示。鉴相器的工作原理是:设外界输入的信号电压和压控振荡器输出的信号电压分别为: (8-4-1) (8-4-2) 式中的ω0为压控振荡器在输入控制电压为零或为直流电压时的振荡角频率,称为电路的固有振荡角频率。则模拟乘法器的输出电压u D为: 用低通滤波器LF将上式中的和频分量滤掉,剩下的差频分量作为压控振荡器的输入控制电压u C (t)。即u C(t)为: (8-4-3) 式中的ωi为输入信号的瞬时振荡角频率,θi(t)和θO(t)分别为输入信号和输出信号的瞬时位相,根据相量的关系可得瞬时频率和瞬时位相的关系为:

锁相环电路

手机射频部分的关键电路----锁相环电路 锁相坏电路是一种用来消除频率误差为目的反馈控制电路,目前市场销售的手机基本上都是采用这种电路来控制射频电路中的压控振荡器。使其输出准确稳定的振荡频率。如锁相坏(PLL)电路出现故障将导致本振的频率输出不准确,则导致手机无信号。 目前通信终端设备中对频率的稳定采用的是频率合成CSYN技术。频率合成的基本方法有三种:第一种直接频率合成;第二种锁相频率合成(PLL);第三种直接数字频率合成(DDS)。由于锁相频率合成技术在电路设计方面(简单),成本方面控制灵敏度方面,频谱纯净度方面等。都要胜于直接频率合成,与直接数字频率合成。所以被移动通信终端设备广范采用。它在手机电路中的作用是控制压控振荡器输出的频率,相位与基准信号的频率,相位保持同步。 锁相坏电路的构成与工作原理: 1、构成:它是由鉴相器(PD)低通滤波器(LPF) 压控振荡器(VCO)三部分组成。 鉴相器:它是一个相位比较器。基准频率信号和压控振荡器输出的取样频率在其内部 进行相位比较,输出误差电压。 低通滤波器:是将鉴相器输出的锁相电压进行滤波,滤除电流中的干扰和高频成分。得到一个纯净的直流控制电压。 压控振荡器:产生手机所要的某一高频频率。 (注:SYNEN、SYNCLK、SYNDATA来自CPU控制分频器,对本振信号进行N次分频)。 当VCO产生手机所须的某一高频频率。一路去混频管,另一路反馈给锁相环,中的分频器进行N次分频。在这里为什么要进行N次分频呢?首先要说明一下基准频率与VCO振荡取样频率在鉴相要满足3个条件。 ①频率相同。②幅度相同。③相位不同。为了满足鉴相条件,所以在电路中设置了分 频器。VCO振荡频率取样信号送入分频器完成N次分频后,得到一个与基准频率相位不同,但频率

汽车电源设计的六项基本原则

汽车电源设计的六项基本原则 大多数汽车电源架构需要遵循六项基本原则: 1.输入电压VIN范围:12V电池电压的瞬变范围决定了电源转换IC的输入电压范围。 典型的汽车电池电压范围为9V至16V,发动机关闭时,汽车电池的标称电压为12V;发动机工作时,电池电压在14.4V左右。但是,不同条件下,瞬态电压也可能达到±100V。ISO7637-1行业标准定义了汽车电池的电压波动范围。图1和图2所示波形即为ISO7637标准给出的部分波形,图中显示了高压汽车电源转换器需要满足的临界条件。 除了ISO7637-1,还有一些针对燃气发动机定义的电池工作范围和环境。大多数新的规范是由不同的OEM厂商提出的,不一定遵循行业标准。但是,任何新标准都要求系统具有过压和欠压保护。 2.散热考虑:散热需要根据DC-DC转换器的最低效率进行设计。 空气流通较差甚至没有空气流通的应用场合,如果环境温度较高(>30°C),外壳存在热源(>1W),设备会迅速发热(>85°C)。例如,大多数音频放大器需要安装在散热片上,并需要提供良好的空气流通条件以耗散热量。另外,PCB材料和一定的覆铜区域有助于提高热传导效率,从而达到最佳的散热条件。如果不使用散热片,封装上的裸焊盘的散热能力限制在2W 至3W(85°C)。随着环境温度升高,散热能力会明显降低。 将电池电压转换成低压(例如:3.3V)输出时,线性稳压器将损耗75%的输入功率,效率极低。为了提供1W的输出功率,将会有3W的功率作为热量消耗掉。受环境温度和管壳/结热阻的限制,将会明显降低1W最大输出功率。对于大多数高压DC-DC转换器,输出电流在150mA 至200mA范围时,LDO能够提供较高的性价比。

锁相环应用电路仿真

高频电子线路实训报告锁相环路仿真设计 专业 学生姓名 学号 2015 年 6 月24日

锁相环应用电路仿真 锁相环是一种自动相位控制系统,广泛应用于通信、雷达、导航以及各种测量仪器中。锁相环及其应用电路是“通信电子电路”课程教学中的重点容,但比较抽象,还涉及到新的概念和复杂的数学分析。因此无论是教师授课还是学生理解都比较困难。为此,我们将基于Multisim的锁相环应用仿真电路引入课堂教学和课后实验。实践证明,这些仿真电路可以帮助学生对相关容的理解,并为进行系统设计工作打下良好的基础。锁相环的应用电路很多,这里介绍锁相环调频、鉴频及锁相接收机的Multisim仿真电路。 1.锁相环的仿真模型 首先在Multisim软件中构造锁相环的仿真模型(图1)。基本的锁相环由鉴相器(PD)、环路滤波器(I P)和压控振荡器(VCO)三个部分组成。图中,鉴相器由模拟乘法器A 实现,压控振荡器为V3,环路滤波器由R1、C1构成。环路滤波器的输出通过R2、R3串联分压后加到 压控振荡器的输入端,直流电源V2用来调整压控振荡器的中心频率。仿真模型中,增加R2、R3及的目的就是为了便于调整压控振荡器的中心频率。 图1 锁相环的仿真模型 2.锁相接收机的仿真电路 直接调频电路的振荡器中心频率稳定度较低,而采用晶体振荡器的调频电路,其调频围又太窄。采用锁相环的调频器可以解决这个矛盾。其结构原理如图2所示。

图2 锁相环调频电路的原理框图 实现锁相调频的条件是调制信号的频谱要处于低通滤波器通带之外,也就是说,锁相环路只对慢变化的频率偏移有响应,使压控振荡器的中心频率锁定在稳定度很高的晶振频率上。而随着输人调制信号的变化,振荡频率可以发生很大偏移。 图3 锁相环调频的仿真电路 根据图2建立的仿真电路如图3所示。图中,设置压控振荡器V1在控制电压为0时,输出频率为0;控制电压为5V时,输出频率为50kHz。这样,实际上就选定了压控振荡器的中心频率为25kHz,为此设定直流电压V3为2.5V。调制电压V4通过电阻Rs接到VCO的输人端,R实际上是作为调制信号源V4的阻,这样可以保证加到VCO输人端的电压是低通滤波器的输出电压和调制电压之和,从而满足了原理图的要求。本电路中,相加功能也可以通过一个加法器来完成,但电路要变得相对复杂一些。 VCO输出波形和输人调制电压的关系如图4所示。由图可见,输出信号频率随着输人信号的变化而变化,从而实现了调频功能。

电源设计规范

整车电负荷设计规范 编制_______________ 校对_______________ 审核—批准 北汽福田汽车股份有限公司 汽车工程研究院 电子电器中心

、发动机、发电机基本状态 X X发动机匹配额定电流时发电机特性曲线(见下图一、根据具体的发动机匹配的发电机的特性曲线): 图一(发电机特性曲线)

编号 BJ X X X系列车型整车电负荷设计规范一—J_e_-——— ------------- 共3 页第2页 二、发电机的功率确定 按以下两个方面确定发电机的功率: 1、发电机对应发动机怠速输出电流最低限度应超过永久及长期耗电器的耗电电流的1.1~1.3 倍。考虑倍乘因子后,即使短途行驶、发动机空转也可保证蓄电池充分充电; 2、发电机额定电流应大于永久及长期耗电器、短期耗电器耗电电流之和。 三、整车电气设备功率与发电机的功率平衡计算 1、按用电器耗电功率加权计算(参考Robert Bosch公司的倍数规则)

2、按爬长坡极限工况下用电器耗电功率计算(整车最大连续用电组合) 结论:(按用电器耗电功率加权计算,确认发电机的功率是否满足要求。)具体实例见下页:

实例 : 轴叙(xlOOOrpj } 4G64二加PDA :送泪谑桝 编号 共3页 第1页 发动机型号 4G64 发电机皮带轮外径 62 发动机曲轴皮带轮外径 149 发电机皮带轮传动速比 2.4 发动机怠速(rpm ) 750 ± 30 发电机对应怠速(rpm ) 1800 发动机最大扭矩点(rpm ) 2400~2800 发电机对应最大扭矩点(rpm ) 5760 发电机初始临界转速(rpm ) 1300 蓄电池容量(A.h ) 65 畜电池补充充电电流(A ) 6.5 蓄电池标称电荷量的10% 发电机输出电压(V ) 13.5 折合充电功率88W BJ6486系列轻型客车整车电负荷设计规范 、发动机、发电机基本状态 4G64发动机配额定电流120A 发电机特性:

开关电源类产品设计的安全规范

仅供参考[整理] 安全管理文书 开关电源类产品设计的安全规范 日期:__________________ 单位:__________________ 第1 页共14 页

开关电源类产品设计的安全规范 1.范围 1.1本规范规定了0公司户内使用、额定电压≤600V的开关电源类产品的设计安全要求,它包括参考标准资料、标志说明、一般要求和试验一般条件、电气技术参数规格、材料和结构、电气试验、机械试验、环境可靠性试验、包装、存放、出货和附录项内容。 1.2它主要以信息技术设备,包括电气事务设备及与之相关设备的安全标准为基础编写。 2.主要参考资料 2.1IEC60950-1999:信息技术设备的安全。 2.2IEC61000-4(所有系列):电磁兼容--试验和测量技术。 2.3IEC61000-3-2-1998:电磁兼容第3部分:限值第2章低压电气及电子设备发出的谐波 电流限值(设备每相输入电流≤16A)。 2.4IEC61000-3-3-1998:电磁兼容第3部分:限值第3章标称电流≦16A的低压电气及电子设备的供电系统中电压波动和变化的限值。 2.5IEC60384-14-1993:电子设备用固定电容器第14部分:分规范拟制电源电磁干扰用固定电容器。 2.6CISPR22-1998:信息技术设备的无线电干扰特性的限值和测量方法。 2.7CISPR24-1997:信息技术设备的无线电抗干扰特性的限值和测量方法。 2.8IEC60695-10-2:1995:着火危险试验第10部分:减少着火对电子技术产品而引起的不正常发热效应的指南和试验方法第2部分: 第 2 页共 14 页

开关电源设计

& 课程设计任务书 学生姓名:专业班级: 指导教师:工作单位: 题目: 开关电源设计 初始条件: 输入交流电源:单相220V,频率50Hz。 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)? 1、输出两路直流电压:12V,5V。 2、直流最大输出电流1A。 3、完成总电路设计和参数设计。 时间安排: 课程设计时间为两周,将其分为三个阶段。 第一阶段:复习有关知识,阅读课程设计指导书,搞懂原理,并准备收集设计资料,此阶段约占总时间的20%。 第二阶段:根据设计的技术指标要求选择方案,设计计算。 ) 第三阶段:完成设计和文档整理,约占总时间的40%。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 ) 引言 (1) 1设计意义及要求 (2) 设计意义 (2) 开关电源的组成部分 (2) 开关电源的工作过程 (2) 开关电源的工作方式 (3) 脉宽调制器的基本原理 (3) 2方案设计 (5) ) 设计要求 (5) 方案选择 (5) 整流滤波部分 (6) 降压斩波电路 (7) 脉宽调制电路 (8) MOSFET管的驱动电路 (9) 总电路图 (11) 3主电路参数设定 (12) { 变压器、二极管、MOSFET管选择 (12) 反馈回路的设计 (13) MOSFET的驱动设计 (14) 结束语 (15) 参考文献 (16)

附录一 (17) ]

引言 随着电力电子技术的高速发展,电力电子设备与人们的工作、生活的关系日益密切,而电子设备都离不开可靠的电源,进入80年代计算机电源全面实现了开关电源化,率先完成计算机的电源换代,进入90年代开关电源相继进入各种电子、电器设备领域,远程控制交换机、通讯、电子检测设备电源、控制设备电源等都已广泛地使用了开关电源,更促进了开关电源技术的迅速发展。 开关电源高频化是其发展的方向,高频化使开关电源小型化,并使开关电源进入更广泛的应用领域,特别是在高新技术领域的应用,推动了高新技术产品的小型化、轻便化。开关电源是利用现代电力电子技术,控制开关管开通和关断的时间比率,维持稳定输出电压的一种电源,开关电源一般由脉冲宽度调制(PWM)控制IGBT和MOSFET构成。随着电力电子技术的发展和创新,使得开关电源技术也在不断地创新。目前,开关电源以小型、轻量和高效率的特点被广泛应用几乎所有的电子设备,是当今电子信息产业飞速发展不可缺少的一种电源方式。 开关电源根据输入输出的性质不同可分为AC/DC和DC/DC两大类。AC/DC称为一次电源,也常称为开关整流器。值得指出的是,AC-DC变换不单是整流的意义,而是整流后又做DC-DC变换。所以说,DC-DC变换器是开关电源的核心。DC/DC称为二次电源,其设计技术及生产工艺在国内外均已成熟和标准化,所以学习设计开关电源有重要的意义。

电荷泵的锁相环电路

Application Report ZHCA090 – August 2010 电荷泵锁相环的数字锁定检测电路应用分析Steven Shi, Nick Dai China Telecom Application Team 摘要 电荷泵锁相环的锁定指示电路设计,常用的方法是在PFD电路中通过检测经分频后的参考输入和本振反馈信号的相位误差来实现,当相位误差超过某个锁定检测窗口时,锁相环电路就上报失锁告警。由于数字锁定指示电路设计简单,易于被监控而被广泛应用。在实际的锁相环电路设计中,往往由于电路参数选择不合理,尽管锁相环处于正常的锁定状态,但由于PFD的相位误差超过锁定检测窗口而导致数字锁定指示电路显示失锁。因此,必须需要根据特定锁相环配置和外围电路选择合适的检测窗口,或者根据检测窗口要求设计合适的锁相环环路参数和外围电路。 目录 1概述 (2) 2电荷泵锁相环电路的数字锁定检测原理 (2) 2.1PFD、电荷泵电流和相位误差 (2) 2.2数字锁定检测原理 (3) 3数字锁定电路设计 (4) 3.1电荷泵锁相环电路锁定状态下的相位误差分析 (4) 3.2数字锁定检测电路设计和实验测试 (5) 4总结 (7) 5参考资料 (7) 图 1PFD输出和相位误差---------------------------------------------------------------------------------------------------------------3 2锁定检测窗口------------------------------------------------------------------------------------------------------------------------3 3数字锁定检测原理图---------------------------------------------------------------------------------------------------------------4 4CDCE72010电路中影响相位误差的漏电流模型-----------------------------------------------------------------------------5 表 1不同VCXO输入阻抗值对CDCE72010数字锁定指示的影响------------------------------------------------------------6 1

锁相环设计与MATLAB仿真

本科毕业设计论文 题目锁相环设计与MATLAB仿真 _______________________________________ 专业名称电子科学与技术 学生姓名何鹏 指导教师李立欣 毕业时间2010年6月

毕业 任务书 一、题目 《锁相环设计与MATLAB 仿真》 二、指导思想和目的要求 在了解锁相环的基本工作原理的基础上,熟悉其构成及数学模型,在对锁相环有了充分的要了解后,运用MATLAB 仿真软件对其进行仿真。通过仿真看锁相环是否工作正常,参数指标是否合格来判断是否达到了仿真要求。 三、主要技术指标 1.锁相环的基本原理 2.锁相环工作期间是否经历了失锁、跟踪、捕获、锁定等四个状态。 3.锁定后平率相位是否平稳。 四、进度和要求 第3~5 周:查阅和整理资料文献,确定研究模型和研究方向; 第6~8 周:分析模型,找出其中的缺陷; 第9~11 周: 提出更容易实现的结构,对该结构具体分析; 第11~13 周:整理资料进行论文撰写、装订并翻译英文文献; 第14~15 周: 论文评阅,答辩准备,答辩 五、主要参考书及参考资料 Floyd M .Gardner,锁相环技术(第三版)姚剑清 译,人民邮电出版社,2007 Roland E.Best,锁相环设计、仿真与应用(第五版),李永明 等译,清华学出版社,2007.4 学生 ___________ 指导教师 ___________ 系主任 ___________ 设计 论文

目录 中文摘要 (3) 英文摘要 (4) 前言 (6) 第一章绪论 (7) 1.1 锁相环的发展及国内外研究现状 (7) 1.2 本文的主要内容组织 (9) 第二章锁相环的基本理论 (10) 2.1锁相环的工作原理 (11) 2.1.1鉴相器 (11) 2.1.2 低通滤波器 (13) 2.1.3 压控振荡器 (15) 2.2锁相环的工作状态 (15) 2.3锁相环的非线性工作性能分析 (17) 2.3.1跟踪性能 (18) 2.3.2捕获性能 (18) 2.3.3失锁状态 (19) 2.4锁相环的稳定性 (20) 2.5信号流程图 (21) 2.6锁相环的优良特性 (21) 2.7锁相环的应用 (22) 2.7.1锁相环在调制和解调中的应用 (22) 2.7.2锁相环在频率合成器中的应用 (23) 2.8本章小结 (23) 第三章锁相环的噪声分析 (24)

锁相环

如今,数字电路,特别是大规模集成数字电路技术的发展,给通信技术领域的发展提供了更有力的支持。各种电子产品潮水般涌现入各个领域。电子线路以其制作简单、易于控制、可靠性强、体积小、成本低廉等优点,以广泛应用于各个行业,电子产品无处不在,电子技术无处不用。随着新器件的不断面市,新电路出现了更多的新功能,新的设计如雨后春笋般涌现!电子系统设计的多样化和复杂化的发展趋势,推动着EDA(电子设计自动化)软件的发展和完善进程。 传统的实现载波提取的部件通常是由CMOS 集成电路构成4046数字锁相环,中小规模TTL 集成电路74系列构成平方律部件和分频电路。这类的载波提取部件工作频率低,可靠性差。正因为大规模数字电路的发展,现在可将数字锁相环,平房律部件以及分频器直接写入FPGA,完成载波提取的功能。 现场可编程门阵列(FPGA)的出现是超大规模集成电路技术和计算机辅助设计技术发展 的结果。FPGA 器件集成度高、体积小,具有通过用户编程实现专门应用的功能。他允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直到达到预期的结果。使用FPGA 器件可以大大缩短系统的研制周期,减少资金投入。更吸引人的是,采用FPGA 器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗,提高了可靠性,同时还可以很方便地对设计进行在线修改。FPGA 器件成为研制开发的理想器件,特别适合产品地样机开发和小批量生产,因此有时人们也把FPGA 称为可编程的ASIC。另一方面,20世纪90年代以后高精密度PLD 在生产工艺、器件地编程和测试技术等方面都有了飞速的发展。例如CPLD 的集成度一般可达数千甚至上万门,ALTERA 公司推出的EPM9560,其单密度达到12000个可用门,包括多达50个宏单元,216个用户I/O 引脚, 并能提供15ns 的脚至脚延时,16位计数器的最高工作频率为118MHZ。可编程逻辑器件的技术的高速发展。技术上使传统的“自下而上”的设计方法,变为一种新的“自顶向下”的设计方法,设计者可以利用计算机对系统进行方案设计和功能划分,系统的关键电路可以采用一片或几片专用的集成电路(ASIC)来实现,因而使系统的体积、重量减小,功耗降低,而且具有高性能、高可靠性和保密性好等有点。 本次毕设运用FPGA 进行实现,在技术上跟上了时代的发展。该设计过程中用到了Altera 公司的可编程逻辑器件EPM7064SLC44-10。这种芯片是Altera 公司生产的MAX7000系列。MAX7000系列是Altera 公司速度最快的高速可编程逻辑器件系列,是采用先进的CMOS EEPROM 技术制造的EPLD。MAX7000系列(包括MAX7000A、MAX7000E 和MAX7000S)的集成度为600~10000可用门,32~1024个宏单元,以及36~212个用户I/O 引脚。这些基于EEPROM 的器件能够提供快至4.5ns 的组合传输延迟,16位计数器工作频率可达192.3MHz。此外,MAX7000的输入寄存器的建立时间非常短,能提供多个系统时钟且由可编程的速度/功耗控制。MAX7000E 是MAX7000系列的增强型,具有更高的集成度。MAX7000S 器件也具有MAX7000E 期间的增强特性,通过工业标准四引脚JTAG 接口实现在 ------------------------------装 ---------------- 订----------------- 线 ----------------------------------

锁相环滤波器的设计

创新课题设计报告 题 目: 锁相环路滤波器的设计 南昌航空大学信息工程学院 20 11 年 10 月 26日 姓 名: 梁勇 专 业: 通信工程 班级学号: 08042135 指导教师: 刘敏

通信工程专课程设计任务书 20 10-20 11 学年第 2 学期第 1 周- 20 周 题目锁相环滤波器的设计 内容及要求 抑制鉴相器输出电压中的载频分量和高频噪声,降低由压控振荡器控制电压不纯而引起的寄生输出。采用无源滤波器可以达到电路结构简单、低噪声、高稳定度的目的。由于上次设计的无源滤波器仿真效果不理想,老师让我们改做有源滤波器。 学生姓名:梁勇 指导时间指导地点:E楼 408 室任务下达20 11年 6月 13 日任务完成2011年 7 月 8 日 考核方式 1.评阅□ 2.答辩□ 3.实际操作□ 4.其它□ 指导教师刘敏系(部)主任 注:1、此表一组一表二份,课程设计小组组长一份;任课教师授课时自带一份备查。 2、课程设计结束后与“课程设计小结”、“学生成绩单”一并交院教务存档。

摘要 滤波器在通信中经常用到的一个模块,具有成熟的设计理论,一个好的滤波器能让整个电路的效果更为清晰、直观,因而对信号的要求直接体现在滤波器上。滤波效果影响到整个电路的好坏,不同功能的滤波器能让信号跟着要求走,使设计理想。 此次设计的二阶有源低通滤波器能够过滤不需要的载频分量和高频噪声,可以有效 的抑制压控震荡引起的寄生输出。 关键字:滤波器效果有源

目 录 第一章 题目要求与方案论证 (5) 1.1 题目要求 (5) 1.2 方案论证 (5) 1.3 工作原理 (6) 第二章 电子线路设计与仿真 (8) 2.1 设计思路 (8) 2.2 参数选择 (8) 2.2 二阶有源低通滤波器 (8) 第三章 结果与分析 (10) 第四章 心得体会 (12) 参考文献 (13) 附录 芯片资料 (14)

电源设计的标准化Word版

统一电源设计的标准化要求如下: 1、通用LDO使用部分(1117类型,) 使用如下的典型电路 输入端要有0.1uF小电容滤波 输出端为100uF点解电容(可以更换为47uF贴片钽电容)并联2.2uF瓷片电容Lyout部分 100mA以下电流使用SOT223封装 100mA-300mA电流使用SOT252封装 300mA以上电流使用SOT263封装 输出端先接100uF电解电容,后接2.2uF瓷片电容 2、CMOS LDO使用部分 使用如下典型电路 输入端要有0.1uF小电容滤波 输出端为100uF电解电容(可以更换为47uF贴片钽电容)并联2.2uF瓷片电容Lyout部分 100mA以下电流使用SOT223封装(小于这个封装的都使用223封装) 100mA-300mA电流使用SOT252封装 300mA以上电流使用SOT263封装 输出端先接100uF电解电容,后接2.2uF瓷片电容 注意这种类型的LDO底部一定要预留散热焊盘过孔

3、DCDC使用部分 12V降压到1.8V及以下 2A 此类型要求使用MP1482 参考电路 Lyout部分 DCDC电路要独立分地,

储能电感要兼容插件、磁密封、背贴三种封装 DCDC底部一定要预留散热接地焊盘过孔 12V降压到1.8V及以下 3A 此类型要求使用MP1484 参考电路同上 Lyout部分 DCDC电路要独立分地, 储能电感使用贴片磁密封 12x12大功率封装 DCDC底部一定要预留散热接地焊盘过孔 12V降压到5V 此类型要求使用LA8535或LA8517 参考电路 Lyout部分 DCDC电路要独立分地, 储能电感兼容插件普通、贴片磁密封三种封装

数字锁相环设计

引言 锁相的概念是在19世纪30年代提出的,而且很快在电子学和通信领域中获得广泛应用。尽管基本锁相环的从开始出现几乎保持原样,但是使用不同的技术制作及满足不同的应用要求,锁相环的实现对于特定的设计还是蛮大的挑战。 锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。锁相环技术在众多领域得到了广泛的应用。如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的锁相环相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。随着通讯技术、集成电路技术的飞速发展和系统芯片(SoC)的深入研究,全数字锁相环必然会在其中得到更为广泛的应用。因此,对全数字锁相环的研究和应用得到了越来越多的关注。 传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。对于高阶全数字锁相环,其数字滤波器常常采用基于DSP的运算电路。这种结构的锁相环,当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SOC(system on chip )的设计带来一定困难。另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N后M序列滤波器等。这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确定锁相环的设计参数。不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用需求。 由于数字电子技术的迅速发展,尤其是数字计算和信号处理技术在多媒体、自动化、仪器仪表、通讯等领域的广泛应用,用数字电路处理模拟信号的情况日益普遍。所以模拟信号数字化是信息技术的发展趋势,而数字锁相环在其中扮演着重要角色。近年来,随着VLSI技术的发展,随着大规模、超高速集成电路的飞速发展,数字系统的集成度和逻辑速度越来越高,这使得数字锁相环在数字通信、控制工程及无线电电子学的各个领域中的应用也越来越广泛。数字锁相环路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。在基于FPGA勺通信 电路中,可以把全数字锁相环路作为一个功能模块嵌入FPGA中,构成片内锁相环。

分立锁相环设计与验证

锁相环 一、实验原理 许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号同步,利用锁相环路就可以实现这个目的。锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成,锁相环组成框图如图1所示。 )t 图1 锁相环基本原理框图 图1所示的是锁相环基本原理框图。锁相环路是一种反馈控制电路,简称锁相环(PLL)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。 因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。 锁相环中的鉴相器又称为相位比较器,它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成u d(t)电压信号输出,该信号经低通滤波器滤波后形成压控振荡器的控制电压u c(t),对振荡器输出信号的频率实施控制。 锁相环法载波提取: 当u i(t)为固定频率正弦信号(θi(t)为常数)时,在环路的作用下,VCO输出信号频率可以由固有振荡频率ωo(即环路无输入信号、环路对VCO无控制作用是VCO的振荡频率),变化到输入信号频率ωi,此时θo(t)也是一个常数,u d(t)、u c(t)都为直流。称此为环路的锁定状态。定义△ω=ω-ωo为环路固有的频率差,△ωp表示环路的捕捉带,△ωh表示环路的同步带,模拟锁相环中△ωp<△ωh。当|△ωo|<△ωp时,环路可以进入锁定状态;当|△ωo|<△ωh时,环路也可以保持锁定状态;当|△ωo|>△ωp时,环路不能进入锁定状态,环路锁定后若△ωo发生变化使|△ωo|>△ωh,环路也不能保持锁定状态。这两种情况下,环路都将处于失锁

数字锁相环参数设计与仿真

%%***********************************************% % author: sjqian % date: 2013 07 17 % description: %**************************************************** %*************system initial************************* clc; clear all; close all; Legtick=['g-o';'k-x';'b-v';'r-o';'m-x';'c-v';'r-s';'y-v';'g-s';'k-x';'b-o';]; adB=10; Qb=10; % generate input signal f=100; fs=400; Ts=1/fs; N=10;% depth of lookuptable resulution=fs/(2^N); freqCon=round(f/resulution); Kd=2^(adB+Qb); K0=2*pi/(2^N); loop=1; BL=10; BWacq=0.42*BL; wn=BL/0.53; Tacq=1.2/BL/Ts; Gain=Kd*K0; zeta=sqrt(2)/2; c1=2*zeta*wn*Ts/Gain; c2=(wn*Ts)^2/Gain; t=0/fs:1/fs:2;

fmod=f+BWacq; a=2^adB*sin(2*pi*fmod*t+pi/6)+10*randn(1,length(t)); a=round(a); b=zeros(1,length(a)); index=(0:2^N-1)/(2^N); table=round(2^Qb*sin(2*pi*index)); phaseindex=freqCon+1; b(1)=table(1);b(2)=table(freqCon+1); path2(1)=0; for i=2:length(t) dp(i)=a(i-1)*b(i)-a(i)*b(i-1); path1=c1*dp(i); path2(i)=path2(i-1)+c2*dp(i); phaseindex=phaseindex+freqCon+path1+path2(i); phaseindex=mod(round(phaseindex),2^N); b(i+1)=table(phaseindex+1); end figure; plot(a); hold on; plot(b,'r'); title('timing waveform'); grid on; figure; plot(dp); stit=sprintf('phase detector output,converge time=%d point',Tacq); title(stit); grid on; figure; plot(path2*resulution); title({'frequency offset estimation value ',num2str(BWacq)});

锁相环电路及工作原理(免费)

锁相环是一种控制晶振使其相对于参考信号保持恒定相位的电路,在数字通信系统中使用比较广泛。目前微处理器或DSP集成的片上锁相环,主要作用则是通过软件实时地配置片上外设时钟,提高系统的灵活性和可靠性。此外,由于采用软件可编程锁相环,所设计的系统处理器外部允许较低的工作频率,而片内经过锁相环微处理器提供较高的系统时钟。这种设计可以有效地降低系统对外部时钟的依赖和电磁干扰,提高系统启动和运行的可靠性,降低系统对硬件的设计要求。 TMS320F28l2处理器的片上晶振和锁相环模块为内核及外设提供时钟信号,并且控制器件的低功耗工作模式。片上晶振模块允许使用2种方式为器件提供时钟,即采用内部振荡器或外部时钟源。如果使用内部振荡器,必须在XI/XCLKIN和X2这两个引脚之间连接一个石英晶体,一般选用30 MHz。如果采用外部时钟,可以将输人的时钟信号直接接到XI/XCLKIN引脚上,而X2悬空,不使用内部振荡器。晶体振荡器及锁相环模块结构如图1 所示。

图1 晶体振荡器及锁相环模块 外部X PLL DIS引脚可以选择系统的时钟源。当XPLLDIS为低电平时,系统直接采用外部时钟或外部晶振作为系统时钟;当XPLLDIS为高电平时,外部时钟经过PLL倍频后为系统提供时钟。系统可以通过锁相环控制寄存器来选择锁相环的工作模式和倍频的系数。表1列出了锁相环配置模式。 表1 锁相环配置模式 锁相环模块除了为C28x内核提供时钟外,还通过系统时钟输出提供快速和慢速2种外设时钟,如图2所示。而系统时钟主要通过

外部引脚XPLLDIS及锁相环控制寄存器进行控制。因此,在系统采用外部时钟并使能PLL(XPLLDIS=1)的情况下,可以通过软件设置C28x内核的时钟输人。 图2 处理器内部时钟电路 如果XPLLDIS为高电平,使能芯片内部锁相环电路,则可以通过控制寄存器PLLCR软件设置系统的工作频率。但要注意,在通过软件改变系统的工作频率时,必须等待系统时钟稳定后才可以继续完成其他操作。此外,还可以通过外设时钟控制寄存器使能外设时钟。在具体的应用中,为降低系统功耗,不使用的外设最好将其时钟禁止。外设时钟包括快速外设和慢速外设两种,分别通过HISPCP和LOSPCP寄存器进行设置。下面给出改变锁相环倍频系数和外设时钟的具体应用程序。