一种可定制模块化的闪存转换层的设计与实现

http:∥www.j

dxb.cn第44卷 第8期2010年8月

西 安 交 通 大 学 学 报

JOURNAL OF XI′AN

JIAOTONG UNIVERSITYVol.44 №8Aug

.2010收稿日期:2010-02-09. 作者简介:杜溢墨(1986-),男,硕士生;肖侬(联系人),男,教授,博士生导师. 基金项目:国家自然科学基金重点资助项目(60736013);国家自然科学基金资助项目(60903040);国家高技术研究发展计划资助项目(2006AA01A106);新世纪优秀人才支持计划资助项目(NCET-08-0145).

一种可定制模块化的闪存转换层的设计与实现

杜溢墨,肖侬,刘芳,陈志广

(国防科学技术大学计算机学院,410073,长沙)

摘要:针对闪存转换层(FTL)的具体设计和实现细节不公开问题,提出了一种模块化的FTL设计,将地址映射、垃圾回收、损耗均衡等几个重要部分设计成不同的模块,并提供可定制接口,在每个模块上都可以针对不同的应用定制不同的算法.用文件系统模拟了一个Flash Memory的存储芯片阵列,并将FTL设计部署在该模拟器上,这样就构成了一个完整的SSD模拟器,为研究FTL中的各种算法和机制以及开发基于SSD的各种应用提供了一个实验平台.通过实验测试了FTL设计的性能,并进行了分析.

关键词:闪存转换层;固态盘;地址映射;垃圾回收;损耗均衡

中图分类号:TP333 文献标志码:A 文章编号:0253-987X(2010)08-0042-06

A Customizable and Modular Flash Translation Lay

er(FTL)Design and Imp

lementationDU Yimo,XIAO Nong,LIU Fang,CHEN Zhiguang

(School of Computer,National University

of Defense Technology,Changsha 410073,China)Abstract:Flash translation layer(FTL)is the key

technique of flash-based SSD.There are manyp

roductions of SSD,but their detailed design and implementation are kept as a secret.A customi-zable and modular FTL design is presented in detail which divides the FTL design into several dif-ferent parts and supplies an interface to make modification for special applications.A file sy

stemis employed to simulate a flash memory array,and the FTL design is implemented on the simula-tor to form a complete simulator of SSD,which provides a platform for users who make resear-ches on algorithms and mechanisms of FTL and on applications based on SSD.The properties ofthe FTL design are evaluated through experiments and analyzing

.Keywords:flash translation layer;solid state disk;address mapping;garbag

e reclamation;wearleveling

固态盘(Solid State Disk,简称SSD)

提供了类似磁盘的块级接口,存储实体是闪存阵列.在接口与存储实体之间是SSD控制器,用来管理SSD上的RAM和通过Flash控制器访问Flash Memory上

的存储单元.与硬盘相比,Flash Memory有以下三个问题:①修改数据不能直接在原数据上重写,导致非定点更新;②数据读写的基本单位是页,而擦除的基本单位是块;③由于寿命问题,

每个擦除块只能被擦除有限的次数.闪存转换层(Flash TranslationLay

er,简称FTL)的引入就是为了解决这几个问题,它主要包括地址映射、垃圾回收、损耗均衡等部分.当然,这几个部分并不是独立的,例如,损耗均衡可以在地址映射时利用数据布局算法来实现,也可以在垃圾回收时通过合理地选择擦除块来实现.

目前,SSD已经引起了国内外工业界和学术界的广泛关注.在工业界,各种SSD的产品层出不穷,

但是在他们提供的产品说明书中,FTL的设计与实

现细节作为SSD的核心技术则很难被找到,而且各厂商为了宣传自己的产品难免会有些片面.在学术界,关于FTL的论文也有很多,从地址映射、垃圾回收到损耗均衡都有专门的研究,但却很少有完整的实现和实验测试.本文提出了一种模块化的FTL设计,将地址映射、垃圾回收、损耗均衡等几个重要部分设计成不同的模块,并提供可定制接口,然后通过模拟实验测试了FTL的设计并进行了分析.

1 SSD和FTL的相关研究工作

Agrawal等[1]基于模拟实验比较分析了SSD的各种设计策略,并根据它们对性能的影响做了权衡,包括并行度、页大小、条带化程度等.Dirik和Ja-cob[2]在模拟器上进行了大量的实验,指出了SSD的性能瓶颈,并测试了从设备级到系统级之间的各个级别增大并行度所带来的性能改善.Chen等[3]用实验比较了几种SSD产品的性能以及其他特点,展示了许多厂商在说明书中没有提到或者与说明书不太符合的一些特征.

Gal和Toledo[4]总结了2005年以前关于FlashMemory的各种典型算法和数据结构,其中也涉及到了FTL设计,包括地址映射、垃圾回收和损耗均衡,但是这篇论文属于报告性质,只是分门别类的介绍,并没有给出完整的FTL设计.

地址映射作为FTL的核心部分,是垃圾回收和损耗均衡的基础,包含许多重要的数据结构和算法,例如Gupta等[5]提出的DFTL是在页级映射上做的改进,其他地址映射方法则主要针对页级和块级的混合映射结构,包括BAST、FAST、LAST等[6-8].Birrell等[9]针对高性能SSD提出一种基于页映射的FTL设计策略,并给出了部分数据结构,对上电逻辑进行了详细的描述,但是其他部分提到的不多,而且没有实现和测试部分.

2 FTL的设计与实现

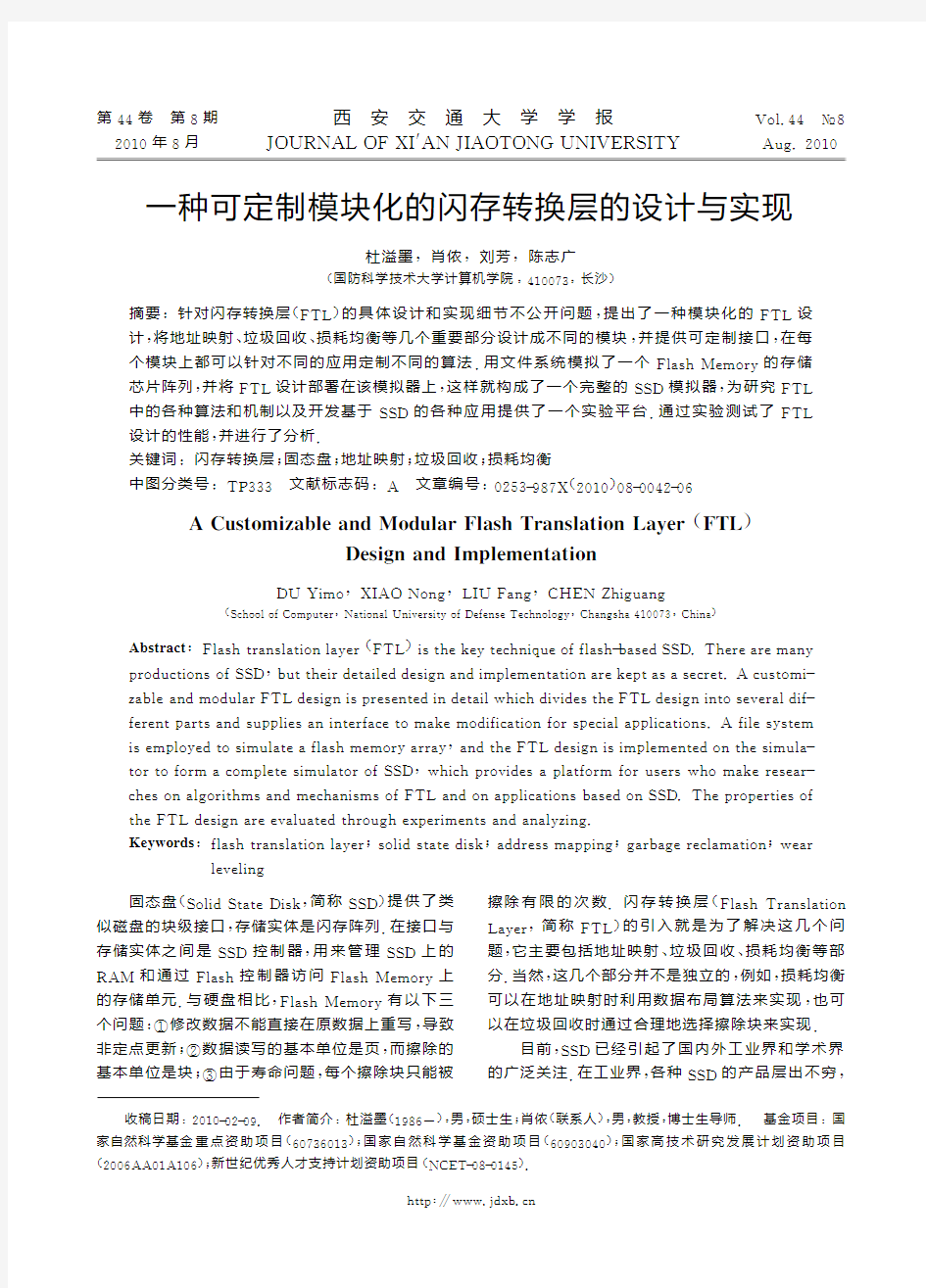

本文提出的FTL设计的软件体系结构如图1所示.软件采用模块化设计,主要模块的功能描述如下.

由于本文的FTL设计针对的是高性能SSD,因此地址映射完全采用了页映射方式[9],在RAM中保存有完整的页映射表,通过查

找映射表可以直

http:∥www.jdxb.cn

http:∥www.j

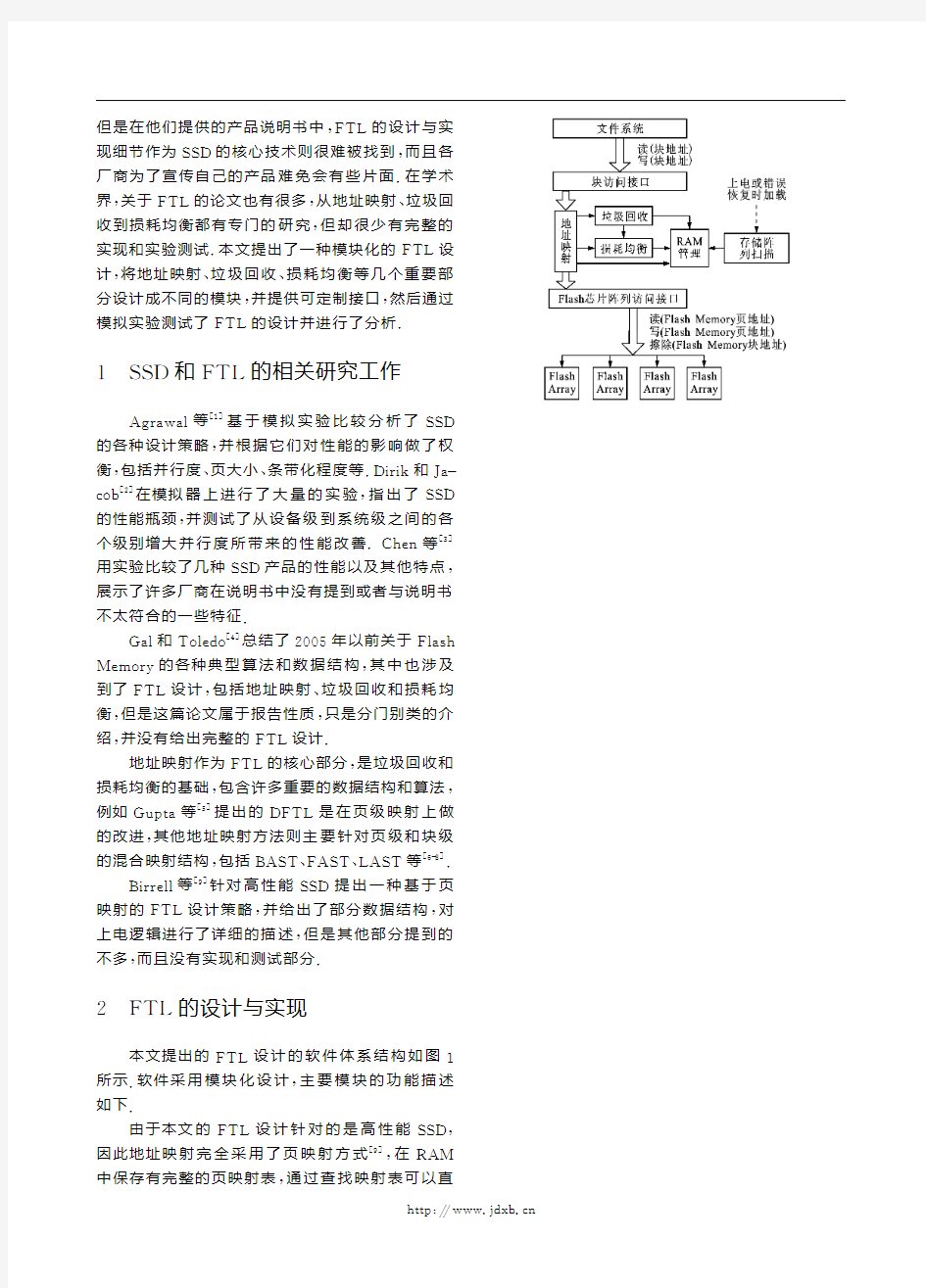

dxb.cn表1 RAM上的主要数据结构

名称功能描述类型

LBATable

地址映射表,保存

逻辑地址到物理地址的映射

数组,元素个数为存储阵列的总页数FreeBlocks

空闲块标记表,标记每块是否为空闲

数组,元素个数为存储阵列的总块数BlockUsag

e有效页个数表,记录每块上有效页的个数数组,元素个数为存储阵列的总块数ActivePag

e当前可以写入的页

结构体,标识Flash

Memory

中的一个地址

表2 Sp

are data区域的格式设计字节号(1-64)功能描述

备注

1坏块标识每块的第一页中2封装标识每块的第一页中3-6块序号每块的第一页中7-10块的擦除次数每块的第一页中11

该页是否有效的标识

每块的所有页上12-15该页对应的逻辑地址每块的所有页上16-35EDC(Error Detect Code)每块的所有页上36-64ECC(Error Correct Code

)每块的所有页上

2.2 块访问接口模块

FTL层的块访问接口模块为上层文件系统提供读和写2个接口.读操作与以硬盘为存储介质的操作区别不大,

主要还是定位和读取.但是,由于Flash Memory的非定点更新以及写之前需要擦除整个块,导致写操作与以硬盘为存储介质的写有很大不同.下面对写接口的逻辑进行描述.

步骤1 当FTL层接到写命令后,直接将所要写入的数据和生成的元数据信息写入ActivePage中,如果ActivePage是块中的第一页,则还需要根据表2生成那些只在第一页中包含的元数据信息.步骤2 根据写命令中需要访问的逻辑地址查找LBATable,记录当前LBATable中该逻辑地址上对应的物理页地址.如果记录的该页地址为0,转到步骤3;否则,将该页置为无效的元数据信息写入该页,并将该页所对应块的BlockUsage个数减一.步骤3 在步骤2中查找到的LBATable位置上记录新写入页的地址,并将新写入页对应块的Block-Usag

e个数加一

.

http:∥www.j

dxb.cn表3 RAM管理模块中的主要函数及其功能描述

函数名称

描述struct path getPath(intblockposition,int pageposi-tion

);根据

blockp

osition和

pageposition这个二维地址生成所需要可以访问的包含array号,chip号,plane号,block号和page号的五维的可以访问的地址.

void AddFreeBlocks(intblockp

osition)将块blockposition对应的FreeBlocks置为空闲

void ModifyLBATable(intblockposition,int pageposi-tion

)根据页上的元数据信息修改LBATable

void AbandonBlock(intblockp

osition)作废块blockposition,即将坏块标识写入该块的第一页上

void RecordActivePage(intblockposition,int pageposi-tion

)将ActivePage指向参数中所给的页

void InitiateBlockUsag

e()初始化BlockUsage数组void Invalid(Struct p

athOrig

inalPath)将OriginalPath指向的页置为无效页的个数占总页数的比例来衡量,比例越高,擦除时需要迁移的页越少,

效率越高.损耗均衡一般由所选块的擦除次数和损耗最严重块的擦除次数之差来衡量,差值越大,说明该块越应该被擦除来使总体损耗趋于均衡.在选择需要擦除的块时,为了综合两方面的考虑,用式(1)(其中i、j均表示块号,Score(j)表示第j块的得分,ρ为调整因子,obsolete(j)表示第j块上无效页的个数,total(j)表示第j块上的总页数,erasure(j)表示第j块的擦除次数)给每一个候选擦除块打分,按照得分由高到低排序作为擦除的顺序.通过调整公式中的参数ρ,可以动态调整效率与损耗均衡的侧重点.

Score(j)=ρobsolete(j)totalj+(1-ρ)(maxi≥1{

erasure(i)}-erasure(j))(1) 采用主程序根据存储状况调用垃圾回收模块的方法,

当空闲块数小于总块数的5%时调用该模块,每次垃圾回收时将所有的垃圾块(块上没有空闲页且存在无效页)都回收,其逻辑描述如图3所示.

除了在垃圾回收中考虑损耗因素以达到损耗均衡的目的外,还可以在数据写入时考虑损耗均衡,

将

http:∥www.j

dxb.c

n图4 Flash Memory存储阵列的文件系统模拟图

内核版本号为2.6.27,文件系统为Ext3.3.3 实验结果

通过调整参数测试不同规模SSD的上电扫描时间,结果如图5所示.对每种规模下的SSD分别测试出厂扫描时间、经过出厂扫描后的空块扫描时间、SSD中写入部分数据后的扫描时间以及SSD中写满数据后的扫描时间.如图5所示,不同规模下的SSD出厂扫描时间差别很大,而后扫描时间相差并不太大.这是因为出厂扫描时需要将所有的页都扫描一遍,而后的扫描通过每块首页的元数据信息或者每块最后一页的元数据信息就可以得到整个Flash Memory存储阵列的状态,并在RAM中构建起所需的数据结构,所以扫描时间要比出厂首次扫描短很多.

用trace[10]

测试FTL的读写响应时间,

结果见图6.横坐标用Flash Memory存储阵列的总页数来表示SSD的规模,纵坐标表示每个I/O的响应时间.从图中可以看出,无论在哪种规模下,读延迟都大大小于写延迟,而不同规模下的延迟差别不大.这与SSD非对称的读写性能很吻合.

在trace运行完后,通过查看每块上记录的擦除次数,

列出了各块的损耗情况,见图7.从图中我们可以看出,

在经常被使用的块之间的损耗基本能

(a)51 200页 (b)512 000页 (c)2 097

152页图7 不同存储阵列规模下的损耗分布图

6

4西 安 交 通 大 学 学 报 第44卷

的算法,通过配置参数可以调整Flash Memory阵列的存储规模和组织结构.最后,本文验证了FTL的设计,并用trace测试了各种Flash Memory存储阵列规模下FTL设计的性能.

下阶段的工作有两个方向:一是把本文中FTL的设计实现到硬件上,做成一个SSD产品,再测试它的性能;二是研究基于Flash Memory的I/O调度,因为以往的I/O调度策略都是针对磁盘的,并没有利用Flash Memory随机读性能好的优点,我们可以用本文的SSD模拟器进行实验,设计一个专门用于Flash Memory的I/O调度算法,以提高系统的整体性能.

参考文献:

[1] AGRAWAL N,PRABHAKARAN V,WOBBER T,et al.Design tradeoffs for SSD performance[C]∥

Proceedings of the 2008USENIX Technical Confer-

ence.Berkeley,USA:USENIX,2008:57-70.

[2] DIRIK C,JACOB B.The performance of PC solid-state disks(SSDs)as a function of bandwidth,concur-

rency,device architecture,and system organization

[C]∥Proceedings of ISCA’09.New York,USA:ACM,2009:279-289.

[3] CHEN Feng,DAVID A K,ZHANG Xiaodong.Un-derstanding intrinsic characteristics and system impli-

cations of flash memory based solid state drives[C]∥

Proceedings of 2009ACM SIGMETRICS conferenceon Measurement and Modeling of computer systems.New York,USA:ACM,2009:181-192.

[4] GAL E,TOLEDO S.Algorithms and data structuresfor flash memories[J].ACM Computing Survey,2005,37(2):138-163.

[5] GUPTA A,KIM Y,URGAONKAR B.DFTL:aflash translation layer employing demand-based selec-

tive caching of page-level address mappings[C]∥Pro-

ceedings of ASPLOS’09.New York,USA:ACM,2009:229-240.

[6] KIM J,KIM J M,NOH S H,et al.A space-efficientflash translation layer for CompactFlash systems[J].IEEE Transactions on Consumer Electronics,2002,48

(2):366-375.

[7] LEE S W,PARK D J,CHUNG T S,et al.A logbuffer-based flash translation layer using fully-associa-

tive sector translation.[J/OL]∥Transactions on Em-

bedded Computing Systems,2007,6(3).[2010-01-

09].http:∥portal.acm.org/citation.cfm?id=

1275986.1275990.[8] LEE S,SHIN D,KIM Y J,et al.Last:locality-aware sector translation for NAND flash memory-

based storage systems[J].SIGOPS Oper Syst Rev,2008,42(6):36-42.

[9] BIRRELL A,ISARD M,THACKER C,et al.A de-sign for high-performance flash disks[J].SIGOPS O-

per Syst Rev,2007,41(2):88-93.

[10]CHANG Lipin,KUO Teiwei.An adaptive strippingarchitecture for flash memory storage systems of em-

bedded systems[C]∥Proceedings of the Eighth IEEE

Real-Time and Embedded Technology and Applications

Symposium.Piscataway,NJ,USA:IEEE,2002:187

-196.

[本刊相关文献链接]

应用变量因果序分析的符号有向图建模方法.西安交通大学学报,2010,44(5):85-90.

一种面向写穿透Cache的写合并设计及验证.西安交通大学学报,2010,44(4):1-4.

利用互易定理的混响声场数值模拟.西安交通大学学报,2010,44(3):110-114.

一种分段测量保证QoS约束的任播通信模型.西安交通大学学报,2010,44(2):44-49.

用属性单值表示的决策表简化算法及属性核计算.西安交通大学学报,2010,44(1):87-90.

一种支持负载均衡的存储调度算法.西安交通大学学报,2009,43(10):61-65.

CorsairFS:一种面向校园网的分布式文件系统.西安交通大学学报,2009,43(8):43-47.

面向存储资源管理的多协议存储系统.西安交通大学学报,2009,43(6):10-14.

利用角度测量估计机动目标运动参数的方法.西安交通大学学报,2009,43(6):67-71.

面向Cell宽带引擎架构的异构多核访存技术.西安交通大学学报,2009,43(2):1-5.

一种基于网关的网格数据互操作框架.西安交通大学学报,2009,43(2):20-24.

利用最大似然准则的双向联想网络研究.西安交通大学学报,2008,42(8):963-966.

一种基于角度测量估计飞行目标运动参数的新方法.西安交通大学学报,2008,42(8):986-990.

一种电子设备电磁敏感性的仿真建模与优化设计方法.西安交通大学学报,2008,42(6):688-692.

一种Log-Gabor滤波结合特征融合的虹膜识别方法.西安交通大学学报,2007,41(8):889-893.

(编辑 武红江)

7

4

第8期 杜溢墨,等:一种可定制模块化的闪存转换层的设计与实现

http:∥www.jdxb.cn

有关建筑转换层结构设计中的关键性问题综述

有关建筑转换层结构设计中的关键性问题综述 本文首先介绍了建筑转换层的概念与特点,然后探讨了建筑转换层结构设计的原则和分类,最后提出了建筑转换层结构设计中的注意事项,本文提出了自己的一些观点和看法,望能为建筑转换层的结构设计提供参考。 标签建筑设计;转换层;结构设计;注意事项; 一、概念与特点分析研究 转换层是建筑施工领域常见的一种建筑结构,由于建筑物不同层面之间的使用功能和结构存在差异,因此需要通过设置转换层的方式作为过渡,对楼层的上下部的结构与设施进行转换。当前,我国的建筑设计、特别是高层建筑的设计,常常会采用商业功能与住宅功能结合的设计模式,在建筑物下部构建举架较高的大跨度商用建筑空间,而上层则采用更加紧密的设计,体现建筑的居住功能。为了对不同的实用功能和建筑结构进行划分,便需要在建筑内部设置转换层,以调整不同结构之间的受力情况,确保建筑物的使用安全。转换层主要功能包括:对建筑物内部的剪力墙结构或框架—剪力墙体系进行转换,实现剪力墙与框架之间的变换;改变建筑物上下受力柱的分布情况和分布密度;同时转变建筑层的结构形式和结构轴网,形成上下结构的不对齐布置三种。根据建筑物自身的特点和使用功能的需要,合理的选择转换层的设计模式,充分发挥出转换层在建筑领域所发挥的作用,能够进一步提高建筑物的稳定性,延长建筑物的使用寿命,对我国建筑行业的发展有着积极的促进作用。由于转换层的结构需要同时承受上部构造在重力的作用下产生的垂直荷载,以及悬挂下部结构产生的多层荷载,导致转换层结构内部长期存在有较大的内应力。此外,转换层的存在会对建筑物整体的受力状况造成较大的影响,在一程度上降低了建筑物的整体性,这就要求转换层的结构设计不能单纯遵循传统的建筑设计原则,而是要根据建筑物自身的特点进行灵活的设计,以满足转换层对刚度和强度的需求,确保建筑物的使用安全。 二、原则及分类分析研究 1、转换层的设计原则。首先,由于转换层的设置会造成建筑物纵向刚度的突变,使其成为建筑物的薄弱环节,因此,在进行转换层的结构设计时,应当尽可能减少需要结构转换的纵向构件,并相应的增加直接落地的纵向构件数量,从而降低建筑刚性突变的程度,提高结构的抗震能力。其次,当转换层高度较低时,对建筑物重心与受力状况的影响相对较小,建筑物也因此更加稳固。所以,在进行转换层结构设计时,应当尽量降低转换层所处的位置,保证建筑物结构的稳固。最后,转换层的结构设计应当采取强化下部结构,弱化上部结构的设计思路,并选择具有明确传力路径的设计模式,在保证工程质量的前提下,降低转成的施工难度,控制转换成的施工成本,更好的实现建筑物的经济效益社会效益。 2、转换层的结构设计的分类。一是梁式转换结构。梁式转换结构采用剪力墙、框支梁与框支柱相结合的结构布置方式来提高转换层的强度与刚度,具有结

装饰装修转换层解决方法

1.1.1型钢转换层施工方案 施工部位:有吊顶的房间 1.1.1.1施工准备 1)材料准备 50×50×5角钢,胀栓,防锈漆材料技术参数满足国标和图纸较高标准。 2)机具准备 一般应备有电焊机、切割机、扫帚、剪刀、皮卷尺、小线绳、粉笔、消防器材等。 3)作业条件 ①安装完顶棚内的各种管线及设备,确定好灯位、通风口及各种露明孔口位置。 ②各种材料全部配套备齐,且复试合格。 ③顶棚罩面板安装前,应做完墙、地湿作业工程项目。 ④搭好顶棚施工操作平台架子。 1.1.1.2工艺流程 1.1.1.3施工要点 1)测量放线 清理现场,复测轴线、标高线控制线,根据吊顶转换层深化图纸,在顶板上弹线定位,吊点间距为3000mm×1200mm。 2)打孔埋胀栓 根据定位使用电钻打孔,清孔后将胀栓砸如孔中。 3)安装角钢吊杆 将已开孔的50×50×5角码与角钢一端焊接(角钢长度根据吊顶高度确定),此端与顶板内胀栓连接拧紧。部分房间应顶板下布满管线,无法安装吊杆,或者房间跨度较大(超过2.5m),吊顶转换层高度较大的则需要在不影响天花标高的情况下,在墙面上设置直角三角形反支撑点,横向使用方钢管直接与支撑点焊接,具备设置吊杆条件的,方钢管要与

吊杆栓接或焊接,具体是否需要设置三角反支撑点,需要在现场实测实量后确定,如需设置参考此节内容,部分无法生根的型钢转换层可根据现场实际情况墙面生根用穿墙螺栓连接。 4)焊接转换层钢架 根据下图将角钢焊接形成装换层。转换层角钢末端用角码与墙体固定。转换层水平网架由50角钢组成,间距3000mm×1200mm,竖向构件间距亦为3000mm×1200mm,网架边缘部分距墙200mm设置50角钢边框,走廊等狭窄空间装换层必须形成“井”字框架体系以增加整体刚度。 转换层平面布置图 转换层剖面图 5)涂刷防锈漆 涂刷灰色防锈漆,分三遍涂刷。

试论高层建筑工程的转换层结构设计

试论高层建筑工程的转换层结构设计 先进科技在建筑领域的应用为现代建筑行业的发展带来了强大的动力,在现代建筑技术的支持下,高层建筑工程的大量建设与实施得以实现,现代高层建筑不仅在高度上较以往有了很大的增加,同时在建筑外观及结构的复杂性上也与以往有了很大的不同,要充分保障高层建筑工程的结构受力的稳定性,保障高层建筑在建设与使用过程中的安全性,加强对转换层设计的研究是十分必要的,本文就将对此展开探讨。 标签:高层建筑工程;转换层;结构设计 现代城市人口增加以及城市功能的日益丰富和完善,对于城市建筑工程的建设也有着更高的需求,一方面,要求城市建筑工程要在有限的开发土地面积上,创造更多的居住、办公、休闲等功能空间,这可以通过高层建筑工程的建设予以满足,同时还要保障建筑工程的质量与可靠性,这就要求针对高层建筑的结构受力特性进行深入研究,并通过对转换层机构的优化设计予以保证。 一、高层建筑工程转换层结构的主要类型 1.梁式转换层 梁式转换层是现代高层建筑中应用非常广泛的一种转换层结构形式,尤其适用于底部大空间的框支剪力墙结构体系的高层建筑结构转换中,此类转换层结构形式的作用原理主要是通过将转换层上部的剪力墙落在框支梁上,而框支梁则是通过稳定的框支柱进行支撑,从而保证整体建筑结构的稳定性,形成较为稳固的转换结构体系,其在实际应用中的主要优势在于设计简单,便于施工操作,结构传力十分明确,且施工成本较低,具有着良好的经济性优势,因而受到许多建筑企业的青睐。 2.箱式转换层 箱式转换层结构形式相对适用范围要小于梁式转换层,其主要应用于转换梁截面超出一定范围,不能够通过一层楼板的设置来满足其需要的刚度要求情况下的转换层构建。为充分保证建筑结构的稳定性,箱式转换层结构形式通常是在转换梁的顶与底分别设置一层楼板,两层楼板和四周围护的墙壁结构之间形成一个箱式的空间,从而使转换层结构的形式整体呈现为箱式结构。这种结构形式在应用中能够有效的保障对转换梁的较强约束力,同时转换梁的刚度也相对较大,从上到下整体结构在传力效果方面相对更为均匀,同时箱式结构中间所形成的空间也可以满足建筑设备层设置的功能需求,具有着良好的应用效果。但相对的,此类转换层结构形式在建设过程中需要在转换梁中进行较多的开洞处理,相对施工操作的复杂性更高,其施工成本也相对较高,经济效益一般。 3.厚板式转换层

闪存芯片封装技术和存储原理技术的介绍

闪存芯片封装技术和存储原理技术介绍 目前NAND Flash封装方式多采取TSOP、FBGA与LGA等方式,由于受到终端电子产品转向轻薄短小的趋势影响,因而缩小体积与低成本的封装方式成为NAND Flash封装发展的主流趋势 TSOP(Thin smaller outline package)封装技术,为目前最广泛使用于NAND Flash的封装技术,首先先在芯片的周围做出引脚,采用SMT技术(表面安装技术)直接附着在PCB板的表面.TSOP封装时,寄生参数减小,因而适合高频的相关应用,操作方便,可靠性与成品率高,同时具有价格便宜等优点,因此于目前得到了极为广泛的应用. FBGA(Ball Grid Array,也称为锡球数组封装或锡脚封装体)封装方式,主要应用于计算机的存、主机板芯片组等大规模集成电路的封装领域,FBGA封装技术的特点在于虽然导线数增多,但导线间距并不小,因而提升了组装良率,虽然

功率增加,但FBGA能够大幅改善电热性能,使重量减少,信号传输顺利,提升了可靠性. 采用FBGA新技术封装的存,可以使所有计算机中的存在体积不变的情况下容量提升数倍,与TSOP相比,具有更小的体积与更好的散热性能,FBGA封装技术使每平方英寸的储存量有很大的提升,体积却只有TSOP封装的三分之一,与传统TSOP封装模式相比,FBGA封装方式有加快传输速度并提供有效的散热途径,FBGA封装除了具备极佳的电气性能与散热效果外,也提供存极佳的稳定性与更多未来应用的扩充性. LGA(land grid array) 触点列封装,亦即在底面制作有数组状态坦电极触点的封装,装配时插入插座即可,现有227触点(1.27mm 中心距)和44触点(2.54mm 中心距)的瓷LGA,应用于高速逻辑LSI电路,由于引线的阻电抗小,对高速LSI相当适用的,但由于插座制作复杂,成本较高,普及率较低,但未来需求可望逐渐增加. 目前NAND Flash一般封装大多采用TSOP、FBGA 与LGA的方式,而记忆卡则多采用COB方式进行封装手机应用领域则多用MCP的封装形式,随着终端产品的变化,未来WLP与3D TSV的封装方式也将逐渐为业界广为应用. U盘的一个大特点便是它的写入速度远不如读取速度快,但这并不不是所有U盘的共同问题,只是较大围存在这样的问

【结构设计】必须学习的结构转换层知识

必须学习的结构转换层知识 转换层的分类 1.上层和下层结构类型转换。多用于剪力墙结构和框架-剪力墙结构,它将上部剪力墙转换为下部的框架,以创造一个较大的内部自由空间。 2.上、下层的柱网、轴线改变。转换层上、下的结构形式没有改变,但是通过转换层使下层柱的柱距扩大,形成大柱网,并常用于外框筒的下层形成较大的入口。 3.同时转换结构形式和结构轴线布置。即上部楼层剪力墙结构通过转换层改变为框架的同时,柱网轴线与上部楼层的轴线错开,形成上下结构不对齐的布置。 结构形式 1.当内部要形成大空间,包括结构类型转变和轴线转变时,可采用梁式、桁架式、空腹桁架式、箱形和板式转换层。 2.当框筒结构在底层要形成大的入口,可以有多种转换层的形式,如梁式、桁架式、墙式、合柱式和拱式等。 3.当上下柱网、轴线错开较多,难以用梁直接承托时,可以做成厚板或箱式转换层,但其自重较大,材料耗用较多,计算分析也较复杂。 4.目前,国内用得最多的是梁式转换层,它设计和施工简单,受力明确,一般用于底部大空间剪力墙结构。

转换层的应用 梁式转换层 作为目前高层建筑结构转换层中应用最广的结构形式,它具有传力直接明确及传力途径清晰,同时受力性能好、工作可靠、构造简单、计算简便、造价较低及施工方便等优点。转换梁不宜开洞,若必须开洞则洞口宜位于梁中和轴附近。转换梁有托柱与托墙两种形式,其截面设计有4种方法,即普通梁截面设计法、偏心受拉构件截面设计法、深梁截面设计法和应力截面设计法。转换梁的截面尺寸一般由剪压比计算确定,应具有合适的配箍率,以防发生脆性破坏。 厚板转换层 当转换层上、下柱网轴线错开较多而难以用梁直接承托时,可采用厚板转换层,但厚板的巨大荷载会集中作用于建筑物中部,振动性能复杂,且该层刚度很大、下层刚度相对较小,容易产生底部变形集中,其传力途径十分复杂,是一种对抗震十分不利的复杂结构体系,应进行整体内力分析、动力时程分析及板的内力分析等。厚板的厚度可由抗弯、抗剪、抗冲切计算确定;可局部做成薄板,厚薄交界处可加腋或局部做成夹心板,一般厚度可取2.0~2.8m,约为柱距的1/3~1/5。厚板应沿其主应力方向设置暗梁,一般可在下部

全闪存存储系统的类型和功能

存储知识:全闪存存储系统的类型和功能 全闪存存储系统是完全由固态存储介质(通常是NAND闪存)而没有硬盘驱动器(HDD)构成的独立的存储阵列或设备。这些系统是用于增强可能包含磁盘阵列的环境的性能,或者用于取代所有传统的硬盘存储阵列。它们也是用于支持由于NAND闪存较佳的性能带来的特定需求和功能,以及克服对闪存存储独有的写/擦除周期的挑战。 在一个全闪存存储系统中,控制器被优化以获得SSD的高性能。传统的磁盘控制器通常每个可支持少于200 IOPS的存储媒介(磁盘驱动器)。高性能的SAS HDD几乎可以达到这个数字的2倍,但与一个普通的固态驱动器提供8000 IOPS相比仍然微不足道。考虑到磁盘驱动器的延时,HDD阵列控制器可以处理周期剩余,大多数的处理周期用于处理快照、卷管理和复制之类的存储服务。 当SSD取代HDD,即这个延时消失后,控制器成为瓶颈,而且其性能显著变差。全闪存存储系统推出保持数据流向较快的存储介质的控制器,无论这些存储介质是驱动器规格的SSD或是闪存电路卡模块形式的。它们通常具有允许更多数据流进出存储介质的分布式的控制器架构,经常会以独立的处理器处理存储服务的系统开销。有些也具有降低网络协议处理对性能的影响的板载(onboard)功能。 全闪存存储系统的控制器也处理耐久性问题。与磁盘驱动器不同,NAND闪存无法在位级别进行覆盖写入。为了适应这种变化,闪存的一个块在新数据写入前必须整个擦除。这需要单独的内部管理程序,整合打算删除而从块里面保存出来的数据,在擦除前创建额外的数据拷贝步骤。所有这些被称作"垃圾收集"的额外的系统开销步骤消耗存储控制器的CPU 周期,如果这些周期同时从处理数据I/O的处理器被偷走,会影响性能。 这些解决方案也无独特之处,全闪存存储系统拥有指定专门硬件处理这种闪存特有的系统开销的闪存控制器,因此不会降低性能。与基于软件的闪存控制器相比,它们运行这些NAND闪存操作(减少写入放大、提高损耗均衡)的工作更有效率。该功能也使低成本的多层单元(MLC)和企业级MLC(eMLC)NAND闪存芯片的使用成为可能,有助于降低全闪存存储系统每GB的实际成本。 现在我们讨论一下现有的全闪存存储系统的类型以及用户是如何使用的。 功能1:增强性能 全闪存存储系统的第一个功能是作为对已有的基于磁盘的基础设施的高性能存储设备的增强。新技术最早的采用者通常是处于最前沿的那些人,那些似乎不惜代价需要更多性能的用户。现在,这些闪存设备成本已经下降,但通常只是用于增强性能。在这种环境里,全闪存系统能够为游戏或者高事务数据库等在线应用在负载高峰期的时候的运行提供了临时或兼任的块存储区域。EBay就是使用全闪存设备增强这类环境的性能。

浅析高层建筑桁架转换层结构设计

浅析高层建筑桁架转换层结构设计 发表时间:2019-07-30T11:57:40.153Z 来源:《基层建设》2019年第14期作者:黄桂生 [导读] 摘要:复杂的建筑结构常常需要采用结构转换层来完成上、下层建筑物结构的转换,一般结构层相比,转换层结构具有结构重量大、结构层刚度大、几何尺寸超大、受力复杂等特点。 身份证:45252819750527XXXX 摘要:复杂的建筑结构常常需要采用结构转换层来完成上、下层建筑物结构的转换,一般结构层相比,转换层结构具有结构重量大、结构层刚度大、几何尺寸超大、受力复杂等特点。这意味着转换结构组成了建筑物的主要构件,它们的设计是否合理、安全、经济对整个结构的安全性、结构造价、施工费用等有着重要的影响。通过时钢桁架转换层高层建设结构体系的工程实例的分析,从结构选型的确定等方面进行系统的研究。以得到一些对设计有实际指导意义的结论。 关键词:建筑工程;结构设计;转换层构造 在当前建筑结构设计过程中,为了更好的适合建筑物的各部楼层所体现的安全使用功能的需求,往往需要在各楼层之间布置转换层以消除楼层中间的较大差异。转换层的设置起到传承上部结构荷载,保持结构稳定的作用,是建筑结构中的重要部位,也是建筑结构设计的重点和难点。因此,深入探讨高层建筑转换层结构设计问题,对于促进我国民用高层建筑的发展具有一定的现实意义。 1.转换层高层建筑结构的构造要求 结构设计不仅是对建筑物本身功能的设计,还关系到建筑物的建设成本,这就需要设计人员优化结构设计,降低建设成本。其优化目标就是实现建筑的本体功能性、安全性、经济性与环保性。为了实现这一目标,未来的从事结构设计者将遵循功能性、安全性、经济性、环保性四位一体的设计思路,真正实现未来建筑结构的优化升级,为人类提供一个更好的物质生存与发展环境。 转换层的结构应按“强化转换层及其下部、弱化转换层上部”的原则,使转换层上下主体结构的侧向刚度尽量接近,平滑过渡。抗震设计时。控制转换层上下主体的结构侧向刚度,当转换层设置在3层及3层以上时。其楼层侧向刚度尚不应小于相邻上部楼层侧向刚度的60%。将转换桁架置于整体空间结构中进行整体分析。此时,腹杆作为柱单元。上、下弦杆作为梁单元,按空间协同工作玻三维空间分析程序计算整体的内力和位移。计算时,转换桁架按实际杆件布置参与整体分析,但上、下弦杆的轴向刚度、弯曲刚度中应计入楼板的作用。整体结构计算需采用两个以上不同力学模型的程序进行抗震计算。还应进行弹性时程分析并宜采用弹塑性时程分析校核。转换层的结构设计中应按转换层“强斜腹杆,强节点”。桁架转换层上部框架结构接“强柱弱梁、强边柱弱中柱”的原则,以保证转换层的结构具有较好的延性,确保塑性饺在梁端出现,能够满足工程抗震的要求。转换桁架的相邻层楼板宜双向双层配筋,每个方向贯通钢筋的配筋率不宜小于0.25%,且在楼板边缘、孔洞边缘应结合边粱设置予以加强。转换桁架上、下弦杆的配筋应加上楼板平面内弯曲计算引起的附加钢筋。 2.转换层商层建筑结构实例分析 对于大跨度的钢桁架转换层结构的受力。各方面的影响因素较多,导致结构受力情况比较复杂,对它的受力影响因素进行探讨具有实际意义,可为实际工程的设计与施工提供理论依据。因此,通过对大跨度钢桁架转换层的受力影响因素进行分析,认识钢桁架转换层的受力特点。以期充分利用钢结构构件受力性能好的特点,使其承担较多的荷载作用。以调整端部混凝土结构的受力,减少混凝土结构的荷载作用,使整个结构体系的受力更为合理。下面结合工程实例分析高层转换桁架的受力影响因素及其受力特点,某高层建筑为地上24层,地下2层,总建筑面积72788m2,其中地上58300m2,地下14488m2。平面长92.1M,宽49M。结构檐口标高为108.80m,中间有电梯、楼梯、机房等的高层建筑。 2.1梁式转换与精架转换的比较确定 与最为常见的转换结构形式粱式转换相比,本例中转换粱的跨度很大而且上部荷载较大,采用梁式的转换结构,转换梁的截面必然很大,一方面导致转换梁下部空间无法再利用、自重大、配筋多、不经济等缺点;另一方面导致沿竖向结构质量和刚度分布在转换层的变化不连续。发生突变,对结构的整体抗震性能不利。因此,需要另一种形式的转换构件来解决这个问题,而转换桁架具有传力明确,传力途径清楚,虽构造和施工复杂,但转换桁架不仅为开洞和设置管道创造了条件,而且它们的位置与大小都有很大的灵活性,可以充分利用该转换层的建筑空间,而且桁架转换层的节间采用轻质建筑材料填充甚至可以外露不填充,有利于减轻结构的自重;转换桁架的抗侧力刚度比转换粱要小,也就是说。具有桁架转换层的高层建筑其质量和刚度的突变要比带转换粱的高层建筑缓和。因此带转换桁架的高层建筑其地震反应要比带转换梁的高层建筑小得多,由此可见,在本例工程的三层转换构件采用转换大粱的结构形式是不合适的,而采用转换桁架的结构形式将很好的避免了上述的多个问题且将节约混凝土用量近30%。将是一个较为合理正确的选择。 2.2转换桁架的具体形式的确定 在本例工程的三层转换构件采用确定桁架结构后,设计人员则需要进一步确定桁架的结构形式。根据前面的论述,转换桁架的结构形式有多种,但是根据本例工程的三层转换构件的具体情况,采用何种最合理的结构形式,则必须加以比较分析后方可确定。 2.2.1单层转换桁架与双层转换桁架的确定 采用精架结构作为高层建筑的转换构件时,一般情况是取出一层层高的高度作为转换桁架的高度。对于本项目,转换桁架位于结构的边缘,建筑师为了使转换桁架对于立面的影响降至最小,希望桁架仅在中庭设置,即取一层高度(4.00m)作为转换桁架的高度。在本例中各层的层高情况分别是:底层:6.44ml,二层:4.80m,三层以上:4.00mt,而结构的柱距为9.0m,若仅取4.00m为桁架高度时,在柱与柱之间必须另设一个桁架节点以保证桁架斜腹杆与水平弦杆的角度在合理的450~550之间。若取建筑的两层层高即8.00m为转换桁架的高度,则在柱与柱之间可以不必设置多余的桁架节点,使桁架的结构形式趋于简单。 2.2.2空腹桁架、斜杆桁架、无竖杆桁架的比较确定 作为高层建筑中的转换结构一桁架结构有如下的主要结构形式:空腹桁架、交叉斜杆桁架、无竖杆的交叉斜杆桁架。作为一种相对独立的结构形式,无论采用何种结构形式。应该说都是可以实现的。对于建筑师来说,空腹桁架如果在构件尺寸可以接受的条件下。当然是首选,当然,采用无竖杆的交叉斜杆桁架形式,结构上可以使桁架的构造节点趋于简单,在建筑师看来,也可以接受。 2.2.3单跨桁架与多跨桁架的确定 在确定了以交叉斜杆桁架作为本次项目的转换结构的结构形式后,结构工程师尚发现在这个计算模型中的框架柱的内力较大。作为抗震设计“强柱弱梁”的一般设计原则,框架柱中的内力相对越大,则在柱中率先出现塑性铰的可能性将越大。而在模型计算中同样可以发

NOR和NAND是现在市场上两种主要的非易失闪存技术

NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结构,强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。但是经过了十多年之后,仍然有相当多的硬件工程师分不清NOR和NAND闪存。 相“flash存储器”经常可以与相“NOR存储器”互换使用。许多业内人士也搞不清楚NAND闪存技术相对于NOR技术的优越之处,因为大多数情况下闪存只是用来存储少量的代码,这时NOR闪存更适合一些。而NAND则是高数据存储密度的理想解决方案。 NOR的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于flash的管理和需要特殊的系统接口。 性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。 由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。 执行擦除时块尺寸的不同进一步拉大了NOR和NADN之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作必须在基于NOR的单元中进行。这样,当选择存储解决方案时,设计师必须权衡以下的各项因素。 ● NOR的读速度比NAND稍快一些。 ● NAND的写入速度比NOR快很多。 ● NAND的4ms擦除速度远比NOR的5s快。 ● 大多数写入操作需要先进行擦除操作。 ● NAND的擦除单元更小,相应的擦除电路更少。 接口差别 NOR flash带有SRAM接口,有足够的地址引脚来寻址,可以很容易地存取其内部的每一个字节。 NAND器件使用复杂的I/O口来串行地存取数据,各个产品或厂商的方法可能各不相同。8个引脚用来传送控制、地址和数据信息。 NAND读和写操作采用512字节的块,这一点有点像硬盘管理此类操作,很自然地,基于NAND的存储器就可以取代硬盘或其他块设备。

未来存储器技术及芯片发展(精)

存储器技术是一种不断进步的技术,每一种新技术的出现都会使某种现存的技术走进历史,这是因为开发新技术的初衷就是为了消除或减轻某种特定存储器产品的不足之处。 举例来说,闪存技术脱胎于EEPROM ,它的第1个主要用途就是为了取代用于PC 机BIOS 的EEPROM 芯片,以便方便地对这种计算机中最基本的代码进行更新。 这样,随着各种专门应用不断提出新的要求,新的存储器技术也层出不穷,从PC 机直到数字相机。本文即着眼于对现有的存储器技术及其未来走向进行考察。 DRAM 严重依赖于PC 的DRAM 市场总是处于剧烈的振荡之中。对目前处于衰退过程中的供应商们来说,降低每比特DRAM 生产成本唯一划算的方法就是缩小DRAM 芯片的尺寸。所以,制造商们就不断地寻找可以缩小DRAM 芯片尺寸的方法。 随着市场的复苏和边际效益的增长,供应商们会逐渐转向使用300mm 的大圆片。但现在,大多数DRAM 生产商都承担不起在300mm 圆片上生产的费用。 许多生产商都开始针对这些市场开发专门的DRAM 产品。 不幸的是,随着人们开始对各种模块和服务器进行升级,PC 市场在未来仍将是DRAM 应用最主要的推动力。尽管一些生产商认为通信将成为另一个主要的推动力,但根据iSuppli 公司的预测,至少在2002年,通信市场在DRAM 销售中所占的份额将仍低于2%。 生产商对消费电子市场的期望值更高。网络设备和数字电视是DRAM 应用增长最迅速的领域,但与PC 市场相比,其份额仍然太小了。 但是,不论是消费电子市场还是PC 市场,DRAM 面临的最大挑战都是以下需求:更高的密度、更大的带宽、更低的功耗、更少的延迟时间以及更低的价格。因

对建筑转换层结构设计的探讨

对建筑转换层结构设计的探讨 摘要:结合多年工作经验,分析梁式转换层的主要结构形式及特点,阐述转换层设计中应该注意的原则性问题,并提出高层建筑梁式转换层结构设计的关键要点。关键词:高层建筑;梁式转换层;施工abstract: combined with years work experience, analysis of the main girder storey structure form and characteristics, this paper expounds the conversion layers should pay attention to in the design of principle problems, and put forward the high-rise buildings beam type conversion layers structure design of the key points.keywords: high building; beam type conversion layers; construction 中图分类号:tu97 文献标识码:a 文章编号:随着我国经济的持续快速发展,高层建筑一般上部需要较多的墙体来分隔空间以满足住宅户型的需要;而下部则希望有较大的自由灵活空间,大柱网、少墙体,以满足公共使用要求。这样的建筑上部楼层部分竖向构件(剪力墙、框架柱)不能直接连续贯通落地时,为了满足建筑要求就必须在上下不同结构体系转换的楼层设置转换层,在结构转换层布置转换结构构件。转换层结构形式有以下几种:梁式转换层、板式转换层、箱式转换层、桁架式转换层、空腹桁架式转换层等。 1 梁式转换层结构形式 1.1 梁式转换层结构形式实际工程中应用的梁式转换层结构有多 种形式,主要原理就是利用下部的转换大梁来支托上部结构。

闪存的应用前景分析

闪存简介及应用前景分析 1.闪存的概念 闪存(Flash Memory)是一种长寿命的非易失性(在断电情况下仍能保持所存储的数据信息)的存储器,数据删除不是以单个的字节为单位而是以固定的区块为单位,区块大小一般为256KB到20MB。闪存是电子可擦除只读存储器(EEPROM)的变种,EEPROM与闪存不同的是,它能在字节水平上进行删除和重写而不是整个芯片擦写,这样闪存就比EEPROM的更新速度快。由于其断电时仍能保存数据,闪存通常被用来保存设置信息,如在电脑BIOS(基本输入输出程序)、PDA(个人数字助理)、数码相机中保存资料等。另一方面,闪存不像RAM (随机存取存储器)一样以字节为单位改写数据,因此不能取代RAM。 闪存卡(Flash Card)是利用闪存(Flash Memory)技术达到存储电子信息的存储器,一般应用在数码相机,掌上电脑,MP3等小型数码产品中作为存储介质,所以样子小巧,有如一张卡片,所以称之为闪存卡。根据不同的生产厂商和不同的应用,闪存卡大概有SmartMedia(SM卡)、Compact Flash(CF卡)、MultiMediaCard(MMC卡)、Secure Digital (SD卡)、Memory Stick(记忆棒)、XD-Picture Card(XD卡)和微硬盘(MICRODRIVE)这些闪存卡虽然外观、规格不同,但是技术原理都是相同的。 2.闪存的技术及特点 NOR型与NAND型闪存的区别很大,打个比方说,NOR型闪存更像闪存,有独立的地址线和数据线,但价格比较贵,容量比较小;而NAND型更像硬盘,地址线和数据线是共用的I/O线,类似硬盘的所有信息都通过一条硬盘线传送一般,而且NAND型与NOR型闪存相比,成本要低一些,而容量大得多。因此,NOR型闪存比较适合频繁随机读写的场合,通常用于存储程序代码并直接在闪存内运行,手机就是使用NOR型闪存的大户,所以手机的“内存”容量通常不大;NAND型闪存主要用来存储资料,我们常用的闪存产品,如闪存盘、数码存储卡都是用NAND型闪存。 这里我们还需要端正一个概念,那就是闪存的速度其实很有限,它本身操作速度、频率就比内存低得多,而且NAND型闪存类似硬盘的操作方式效率也比内存的直接访问方式慢得多。因此,不要以为闪存盘的性能瓶颈是在接口,甚至想当然地认为闪存盘采用USB2.0接口之后会获得巨大的性能提升。 前面提到NAND型闪存的操作方式效率低,这和它的架构设计和接口设计有关,它操作起来确实挺像硬盘(其实NAND型闪存在设计之初确实考虑了与硬盘的兼容性),它的性能特点也很像硬盘:小数据块操作速度很慢,而大数据块速度就很快,这种差异远比其他存储介质大的多。这种性能特点非常值得我们留意。 3.闪存的发展史 在1984年,东芝公司的发明人Fujio Masuoka 首先提出了快速闪存存储器(此处简称闪存)的概念。与传统电脑内存不同,闪存的特点是非易失性(也就是所存储的数据在主机掉电後不会丢失),其记录速度也非常快。 Intel是世界上第一个生产闪存并将其投放市场的公司。1988年,公司推出了一款256K bit闪存芯片。它如同鞋盒一样大小,并被内嵌于一个录音机里。後来,Intel

反支撑(吊顶转换层)方案

目录 一、编制说明: (2) 二、编制依据: (2) 三、施工准备 (2) (一)技术准备 (2) (二)材料准备 (2) (三)机具准备 (3) 四、主要施工方法及措施 (3) (一)施工工序 (3) (二)施工方法及措施 (3) 五、质量标准 (5) 1. 保证项目 (5) 2. 基本项目 (5) 六、安全措施 (6) 七、文明施工 (8)

一、编制说明: 资中县城新区综合体项目是一个大型公共建筑,且空间多维变换,吊顶内设 备繁多,吊顶的空间跨度大,高度高,是典型的大跨度大空间的室内吊顶工程,吊顶施工的技术要求高,根据国家现行规范 GB50210-2001 建筑装饰装修工程质量验收规范第六章吊顶工程, 6.1 一般规定的 6.1.11中规定“当吊杆长度大于 1.5m 时,应设置反支撑”中要求,项目部编制此专项方案。 二、编制依据: 1. 深圳市中建大康建筑有限公司资中县城新区综合体装饰合同文件 2. 中国建筑西南设计研究院资中县城新区综合体装饰工程施工图 3. 深圳市中建大康建筑有限公司资中县城新区综合体装饰工程施工方案 4. 相关的规范、规程和标准 4.1 《建筑工程质量管理条例》 4.2 《建筑装饰装修工程质量验收标准》 (GB50210-2001) 4.3 《建筑工程施工质量验收统一标准》(GB50300-2013) 4.4 《建筑施工手册》 5. 本公司质量、安全、现场文明施工管理和各种工序工法的标准程序文件 三、施工准备 (一)技术准备: 1. 施工现场轴线、标高控制线已交接并完成校核复测。 2. 吊顶排版、深化、节点图纸齐全,具备指导施工条件。 3. 将吊顶图纸与机电专业图纸核对,及时发现相互影响的部位并协商解决 4. 分析前后工序对转换层施工的影响,如出现问题则对工序进行适当调整 (二)材料准备: 「L50 X 50X 5 角钢、200X 200X 10 钢板 2. 膨胀螺栓 3. 防锈漆

什么是NOR和NAND闪存

什么是NOR和NAND闪存? NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开 发出NORflash技术,紧接着,1989年,东芝公司 发表了NAND flash结构。NAND flash的单元尺寸几乎是NOR器件的一半,由于生产过程更为简单,NAND结构可 以在给定的模具尺寸内提供更高的容量,也就相应地降低了产品的价格。而且,它的写入和擦除速度很快,因此,其主要功能是存储资料,例如在CompactFlash、Secure Digi-tal、PCCards和MMC存储卡市场上所占份额最大。 NOR的传输效率很高,在小容量时具有很高的成本效益,更加安全,不容易 出现数据故障,因此,主要应用以代码存储为主,多与运算相关。 目前,NAND闪存主要用在数码相机闪存卡和MP3播放机中,这两个市场的 增长非常迅速。而NOR芯片主要用在手机和机顶盒中,这两个市场的增长速度相 对较慢。 NOR和NAND Flash存储器的区别 NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结构,强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。但是经过了十多年之后,仍然有相当多的硬件工程师分不清NOR和NAND闪存。 相“flash存储器”经常可以与相“NOR存储器”互换使用。许多业内人士也搞不清楚NAND闪存技术相对于NOR 技术的优越之处,因为大多数情况下闪存只是用来存储少量的代码,这时NOR闪存更适合一些。而NAND则是高数据存储密度的理想解决方案。 NOR的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。 NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于flash的管理和需要特殊的系统接口。 性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何flash 器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。 由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND

高层转换层结构设计

浅析高层转换层结构设计 摘要:本文从高层建筑转换层的布置、抗震设计和转换层上下结构刚度比等三个方面探讨了高层建筑转换层结构设计要点,在此基础上提出了若干注意事项,以期保证高层转换层结构设计的合理性。 关键词:高层建筑;转换层;结构设计 abstract: this article from the high building conversion layers of layout, seismic design and conversion layers structure stiffness ratio and three aspects high-rise building conversion layers structure design points, based on this, advances some matters needing attention, so as to ensure top conversion layers the rationality of the structure design. keywords: high building; conversion layers; structure design 中图分类号:[tu208.3]文献标识码:a 文章编号: 现代高层建筑向多功能和综合用途发展,在同一竖直线上,顶部楼层布置住宅、旅馆,中部楼层作办公用房,下部楼层作商店、餐馆和文化娱乐设施。不同用途的楼层,需要大小不同的开间,采用不同的结构形式。建筑要求上部小开间的轴线布置、较多的墙体,中部办公用房要小的和中等大小的室内空间,下部公用部分,则希望有尽可能大的自由灵活空间,柱网要大,墙尽量少。这种要求与

高层建筑结构转换层的结构设计

高层建筑结构转换层的结构设计 前言 一般而言,当高层建筑下部楼层竖向结构体系或形式与上部楼层差异较大,或者下部楼层竖向结构轴线距离扩大或上、下部结构轴线错位时,就必须在结构改变的楼层布置水平转换构件,即结构转换层。因此,转换结构可根据其建筑功能和结构传力的需要,沿高层建筑高度方向一处或多处灵活布置,且自身的这个空间既可作为正常使用楼层,也可作为技术设备层,但应保证转换层有足够的刚度,以防止沿竖向刚度过于悬殊。对底层大空间多塔楼的商住建筑,塔楼的转换层宜设置在裙房的屋面层,并加大屋面梁、板尺寸和厚度,以避免中间出现刚度特别小的楼层,减小震害。 一、高层建筑转换层结构形式及受力特点 高层建筑转换层的主要结构形式及特点 1、粱式转换 粱式转换层是目前高层建筑中实现垂直转换最常用的结构形式,其传力途径为上部墙—转换粱—下部柱。具有传力直接、明确和清楚

的优点,便于工程计算、分析和设计,且造价较为节省,据资料统计,粱式转换层数量约占转换层总量的77%。转换梁的截面高度为0.8- 6m,高层建筑带转换层结构的绝大多数为梁式转换层。 2、箱式转换 是单向托粱和双向托粱同上、下层较厚的楼板浇筑成一整体共同工作,从而形成刚度较大的箱式转换层。 3、板式转换 当转换层上下柱网错开较多。布置又不规则,难以用梁直接承托时,则需要做成厚板,形成板式转换层,从抗剪和抗冲切考虑,转换板厚度往往很大,实际转换板厚度可达2.0- 2.8m,板式转换层的下层柱可以灵活布置,但自重很大,材料耗用多,拖工难度大。 4、桁架转换 桁架分为空腹桁架与实腹桁架两种。桁架转换层与梁式转换相比,受力状态更明确,可使用空间更大,自重小,抗震性能好,但其节点设计难度大,“强斜腹杆、强节点”是桁架转换层设计的基本原则,而节点的受力状态复杂,容易发生剪切脆性破坏,造成计算配筋

NOR与NAND非易失闪存技术的原理与区别

NOR与NAND非易失闪存技术的原理与区别NOR和NAND是现在市场上两种主要的非易失闪存技术。Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。紧接着,1989年,东芝公司发表了NAND flash结构,强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。但是经过了十多年之后,仍然有相当多的硬件工程师分不清NOR和NAND闪存。简单的来说,NAND规格快闪记忆体像硬碟,以储存数据为主,又称为Data Flash,晶片容量大,目前主流容量已达二Gb;NOR规格记忆体则类似DRAM,以储存程序代码为主,又称为Co deFlash,所以可让微处理器直接读取,但晶片容量较低,主流容量为512Mb。 相“flash存储器”经常可以与相“NOR存储器”互换使用。许多业内人士也搞不清楚NAND闪存技术相对于NOR技术的优越之处,因为大多数情况下闪存只是用来存储少量的代码,这时NOR闪存更适合一些。而NAND则是高数据存储密度的理想解决方案。 NOR的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。 NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。 NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。应用NAND的困难在于flash的管理和需要特殊的系统接口。 1.性能比较 flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。由于擦除NOR器件时是以64~128KB的块进行的,执行一个写入/擦除操作的时间为5s,与此相反,擦除NAND器件是以8~32KB的块进行的,执行相同的操作最多只需要4ms。 执行擦除时块尺寸的不同进一步拉大了NOR和NADN之间的性能差距,统计表明,对于给定的一套写入操作(尤其是更新小文件时),更多的擦除操作必须在基于NOR的单元中进行。这样,当选择存储解决方案时,设计师必须权衡以下的各项因素。 ● NOR的读速度比NAND稍快一些。 ● NAND的写入速度比NOR快很多。

Flash闪存有哪些类型,Flash闪存分类

Flash闪存有哪些类型,Flash闪存分类 Flash 闪存是非易失性存储器,这是相对于SDRAM 等存储器所说的。即 存储器断电后,内部的数据仍然可以保存。Flash 根据技术方式分为Nand 、Nor Flash 和AG-AND Flash,而升级。但是经过了十多年之后,仍然有相当多的硬件工程师分不清NOR 和NAND 闪存。大多数情况下闪存只是用来存储 少量的代码,这时NOR 闪存更适合一些。而NAND 则是高数据存储密度的理 想解决方案。项目NOR flashNAND flash 特点芯片内执行系统RAM 中传输效率高中写入/擦除操作的时间5s4ms 擦除器件时块大小64~128KB8~32KB 接口SRAM 接口I/O 口来寿命(耐用性)十万次一百万次Nor Flash 常常用于存储程序,最初MP3 芯片不太成熟的时,曾经有使用过Nor Flash,比如炬力ATJ2075,SunplusSPCA7530 等。目前这种Flash 已经使用的不多了,只有少数的读卡MP3 和数码相框中还有见到,因为这种支持SD 卡的产品中没有内存, 芯片内的ROM 不够存储程序,所以需要用到Nor Flash 存储程序。另外AG- AND Flash 是日本Renesas(瑞萨)公司的技术,良品率不是很高,而且有效容量也比较低。原厂推出的Flash,容量有88%、92%、96%,96%可以用于MP3 产品中,而另外两种只能用于U 盘和SD 卡产品中。我个人认为其性能比较差,尽量不要使用。现在Renesas 已经推出Flash 的生产商行列,而AG-AND 技术也转给台湾力晶公司在继续生产。Nand Flash 也有几种,根据技术方式,分为SLC、MCL、MirrorBit 等三种。SLC 是Single level cell 的缩写,意为每个存储单元中只有1bit 数据。而MLC 就是Multi-Level-Cell,意为该技术允许2 bit 的 数据存储在一个存储单元当中。而MirrorBit 则是每个存储单元中只有4bit 数 据。SLC 与MLC 的参数对比:SLC 与MLC 的参数对比:项目SLCMLC 电压3.3V/1.8V3.3V 生产工艺0.12um0.16um 页容量/块容量