ISE应用基础实验

实验课程名称:FPGA原理及应用

1.3实验准备

(1)将光盘下03. Examples of Program 实验程序目录下的01. ISE9.1 文件夹拷贝到E:盘根目录下;

(2)将USB 下载电缆与计算机及XUPV2Pro 板的J8 连接好;

(3)将RS232 串口线一端与计算机连接好,另一端与板卡的J11 相连接;

(4)启动计算机后,将XUPV2Pro 板的电源开关SW11 打开到ON 上。观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源。

1.4实验步骤

一.ISE9.1 使用流程实验

(1)创建工程

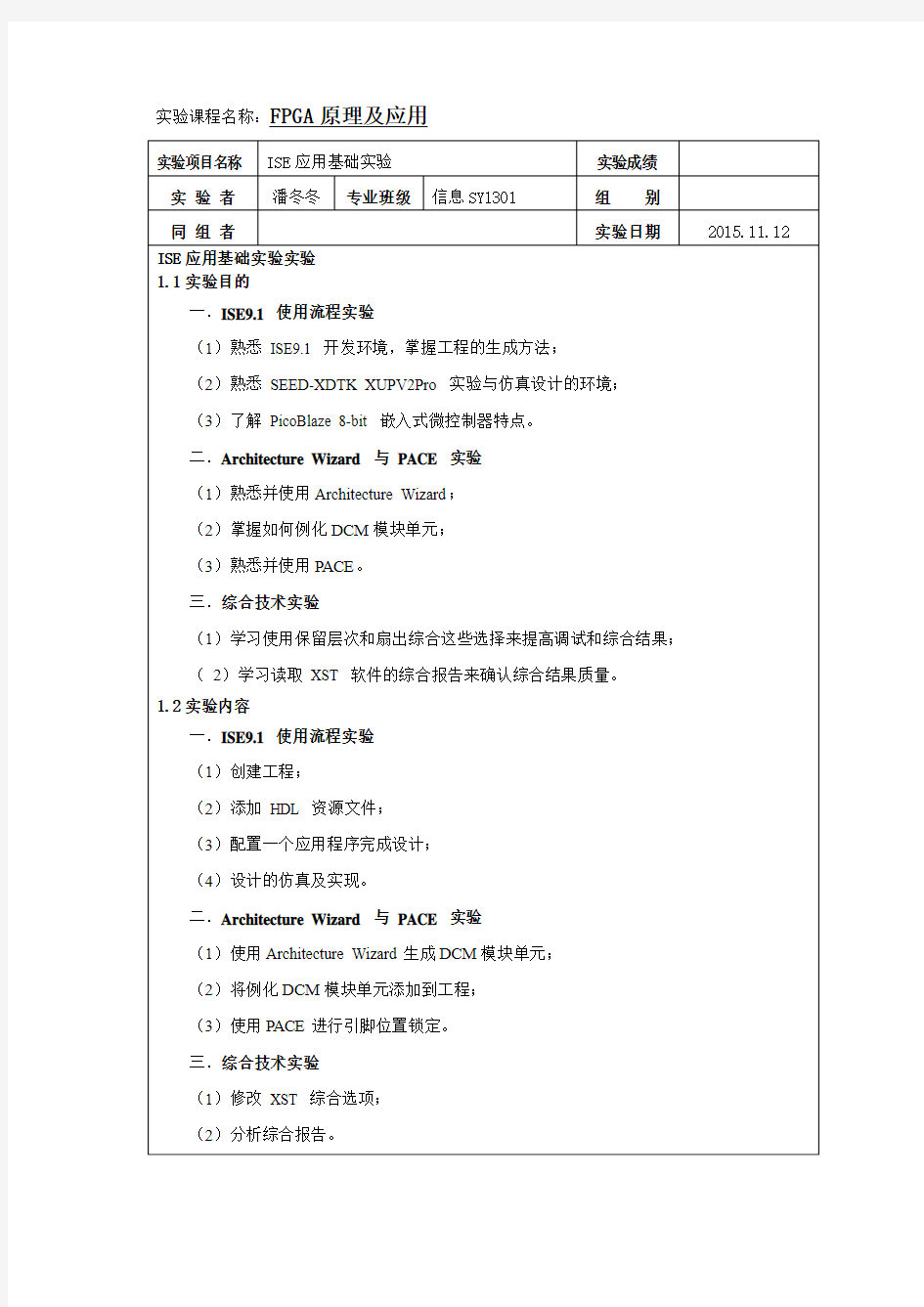

1)双击桌面Xilinx ISE9.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2)打开Project Navigator 后,选择File → New Project ,弹出新建工程对话框;

3)在工程路径中单击“…”按钮,将工程指定到如下目录,单击确定。

Verilog 使用者:E: \01. ISE9.1\xupv2pro \labs\ verilog\lab1

VHDL使用者:E: \01. ISE9.1\xupv2pro \labs\vhdl\lab1

4)在工程名称中输入Flow_lab,点击Next 按钮,弹出器件特性对话框。器件族类型(Device Family)选择“Virtex2P”,器件型号(Device)选“XC2VP30 ff896 -7”,综合工具(Synthesis Tool)选“XST (VHDL/Verilog)”,仿真器(Simulator)选“ISE Simulator”,如图所示。

5)单击Next 按钮,弹出创建新资源(Create New Soure)对话框,可以使用这个对话框来创建新的HDL 资源文件,或者也可以创建工程后,新建HDL 资源文件;

6)单击Next 按钮,弹出添加存在资源对话框;

(2)添加HDL 资源文件

1)点击Add Source 按钮,指向E:\01. ISE9.1\KCPSM3\VHDL(Verilog)活页夹下,选择kcpsm3_int_test 和kcpsm3 文件,单击Open 按钮;

单击Next 按钮,弹出工程信息后单击Finish 按钮;

2)单击OK 按钮

(3)配置一个应用程序完成设计

1)打开E:\01. ISE9.1\KCPSM3 目录下的Assembler 文件夹。

2)用文件编辑器打开int_test.psm 文件,浏览一下代码,此档就是设计者编写和输入的源文件;

3)在开始菜单中的所有程序的附件,点击命令提示符,使用cd 命令指向汇编编译器的目录下,输入> kcpsm3 int_test.psm 命令;

4)执行完命令后,会看到在Assembler 下生成了一些文件,其中包括VHDL (int_test.vhd) 和Verilog (int_test.v),这就是汇编编译系统把编写的汇编源文件int_test.psm 自动生成用于程序内存的VHDL/Verilog 格式文件,以用于综合和仿真。

5)在ISE Project Navigator,点击Project --Add Copy of Source,指向E:\01. ISE9.1\KCPSM3\Assembler 目录下的int_test.vhd 或者int_test.v 文件;

点击OK 后,则将int_test.vhd 或者int_test.v 文件添加到工程里,解决了出现红色问号的问题;

(4)设计的仿真

1)如前所述,在ISE Project Navigator点击Project --Add Copy of Source,指向E:\01. ISE9.1\KCPSM3\vhdl (或者verilog)目录,选择test_bench.vhd (或者testbench.v)文件,点击打开;

2)选择Simulation Only,点击OK,则将测试范本(Testbench)test_bench.vhd/.v文件添

加到工程里;

3)单击Sourcese 窗口中的testbench,则在Processes 窗口中显示Xilinx ISE Simulator 工具栏,扩展开后,右键单击Simulator Behavioral Model,选择Properties,对Simulation Run Time 输入10000ns,单击OK 按钮;

4)双击Processes 窗口中的Simulate Behavioral Model 对设计进行仿真,在右方窗口弹出仿真结果的波形;

(5)设计的实现

1)在工程的Sources 窗口,Sources for 选择Synthesis/Implementation,并单击工程的顶层文件kcpsm3_int_test.vhd/v;

2)在工程的资源操作窗(Processes),双击Implement Design;

3)当实现设计(Implement Design)运行的过程中,展开实现(Implement Design)的步骤,会看到实现过程中,首先是进行综合(Synthesis),然后才依次完成实现的步骤。当完成相关操作后,在每个操作步骤前会显示一个小图标,表示该步骤的完成情况。对于本设计,在一些操作步骤前显示的是叹号,这些警告是可以忽略的。上图的示意如下:

?对号表示该操作步骤成功完成;

?叹号表示该操作步骤虽完成但有警告信息;

?叉号表示该操作步骤因错误而未完成。

4)当完成这些操作步骤后,生成相应的操作报告供查看。实现操作完成后,再看design utilization 的Design Summary 窗口;

二.Architecture Wizard 与PACE 实验

(1)使用Architecture Wizard 生成DCM 模块单元

1)选择Start → Programs → Xilinx ISE 9.1i → Project Navigator,进入ISE 的Project Navigator 环境;

2)选择File → Open Project,并指向如下目录,选择arwz_pace.ise 打开工程;

Verilog 使用者: E: \01. ISE9.1\xupv2pro \labs\ verilog\lab 2\arwz_pace

VHDL 使用者: E: \01. ISE9.1\xupv2pro \labs\ vhdl\lab 2\arwz_pace

3)双击Processes 窗口中的Creat New Source,弹出新资源向导窗口,选择IP (CoreGen & Architecture Wizard),输入my_dcm;

图5-21 操作示意

4)单击Next 按钮,弹出Select IP 窗口,展开FPGA Features and Design 和Clocking目

录,选择Single DCM;

5)单击Next 按钮,显示新建资源信息,单击Finish 按钮则弹出Xilinx Clocking Wizard-General Setup 窗口,选中CLK0、CLKFX 和LOCKED,不选中RST,输入时钟频率为100MHz

6)单击Next 按钮,弹出Xilinx Clocking Wizard – Clock Buffers 窗口,保持默认选项;7)单击Next 按钮,弹出Xilinx Clocking Wizard – Clocking Frequency Synthesizer窗口,输入50MHz 输出频率;

8)单击Next 按钮,显示新建资源信息。

(2)DCM 组件的例化

1)选中my_dcm.xaw 文件,则在工程的Processes 窗口双击View HDL Source,在HDL 编辑器中可以看到由Architecture Wizard 生成的DCM 的VHDL 源代码。

2)在工程的Sources 窗口,双击uart_clock.vhd 在HDL 编辑器中打开源代码;

3)在工程的Sources 窗口,选择my_dcm.xaw,在Processes 窗口双击View HDL Instantiation Template 在HDL 编辑器中打开例化组件的模板。在HDL 例化范本my_dcm.vhi 中,拷贝组件声明(从COMPONENT my_dcm 到END COMPONENT)并粘贴到uart_clock.vhd 代码中的-- Insert DCM component declaration here 注释的下方;

4)在uart_clock.vhd 代码中的“-- Insert DCM component instantiation here”注释下方,添加如下对端口的名称映像完成对组件的例化:

Inst_my_dcm: my_dcm PORT MAP(

CLKIN_IN => clk,

CLKFX_OUT => clk50MHz,

CLKIN_IBUFG_OUT => open,

CLK0_OUT => open,

LOCKED_OUT => lock

);

5)在“--Signals for DCM, as follows:”注释的下方添加DCM 的50MHz 的信号声明:signal clk50MHz : std_logic;

6)在实体说明里添加lock 输出管脚如下:

entity uart_clock is

Port (

tx : out std_logic;

rx : in std_logic;

alarm : out std_logic;

clk : in std_logic;

lock : out std_logic );

end uart_clock;

7)保存后,my_dcm.xaw 作为一个模块加入顶层设计文件中;

(3)使用PACE 进行管脚分配

1)在工程的Sources 窗口,选择顶层设计文件uart_clock.vhd/.v,则在Processes 窗口,扩展User Constraints 并双击Assign Package Pins 打开PACE,在此过程中弹出询问是否添加UCF 文件到工程中对话框,单击“yes”按钮

2)在PACE 中浏览Design Object List-I/O Pins 窗口,可看到所列的信号名称和信号方向是Output 还是Input。在Loc 栏里每个信号对应于FPGA 的管脚.

3)保存后出现Bus Delimiter 对话框,选择XST Default,单击OK 按钮。在Device

Architecture 窗口放大直到可以看清每个管脚;

4)保存后出现Bus Delimiter 对话框,选择XST Default,单击OK 按钮。单击菜单栏中的File → Exit,退出PACE;

5)单击工程中Sources 窗口中的uart_clock.ucf 文件,然后双击Prosesses 窗口中User Constraints 目录下的Edit Constraints (Text),就可以看到由PACE 生成的uart_clock.ucf 管脚约束文件;

(4)检查Pad 报告并打开超级终端

1)单击工程中的Sources 窗口的uart_clock.vhd/v 文件,然后打开Processes 窗口中的Implement Design 目录下的Place & Route 目录,双击Pad Report。当Place & Route 完成后,Pad Report 在HDL 编辑器中打开,可以看Pad Report 来确定I/O信号管脚约束是否与分配的管脚相匹配;

2)在开始菜单――所有程序――附件--通讯中单击超级终端,输入名字并单击OK 按钮,选择COM1 作为端口连接。

3)单击超级终端菜单中属性中的设置,单击ASCII 设置,选中“将换行符附加到传入行末尾”并单击确定按钮。再次单击确定按钮退出属性对话框;

(5)程序的下载并操作UART 实时时钟

1)给板卡上电,打开SW11 开关;

2)单击工程的顶层文件uart_clock.vhd/v 文件,然后双击Processes 窗口中的Generate Programming File 来生成此工程的Bitstream 文件并下载到芯片中去;

3)当这个过程完成后,打开Generate Programming File 目录,双击Configure Device (iMPACT),弹出iMPACT 对话框后选择Configure Devices using Boundary-Scan (JTAG),然后单击Finish 按钮;

4)当等到弹出Assign New Configuration File 对话框后,前两个器件都选择bypass按钮,最后一个器件单击uart_clock.bit 文件选择Open 按钮,然后再点击OK 按钮后弹出一个警告信息,单击OK 按钮;

5)在iMPACT 窗口右键点击xc2vp30,选择Program 后弹出Programming Properties窗口单击OK 按钮

6)在超级终端窗口则会看到KCPSM3>提示符如图;

注意:这里超级终端是否显示成功不仅与下载是否成功有关,而且还与电脑的连接有关。如果COM1不行的话,可以试一下COM2。

7)在KCPSM3>提示符后输入“time”命令

8)在命令提示符后输入“alarm”命令,则以hh:mm:ss 形式显示当前警告时间,此时alarm 是关闭的;

9)输入“alarm on”命令,则警告变成有效,然后输入“alarm 00:00:30”设定警告时间为30 秒,输入“time 00:00:00”设定时间后,会看到板卡上的LED1 灯会在30 秒警告后熄灭。当你输

入“alarm off”命令后则关闭警告,LED1 灯则再次亮起。

三.综合技术实验

(1)浏览设计并生成软件

1)选择Start → Programs → Xilinx ISE 9.1i → Project Navigator,进入ISE 的Project Navigator 环境;

2)选择File → Open Project,并指向如下目录,选择synth_lab.ise 打开工程;

3)用文件编辑器打开在lab4 目录下的Assembler 文件包中的program.psm

4)在开始菜单中的所有程序的附件,点击命令提示符,使用cd 命令指向汇编编译器的目录下,输入> kcpsm3 program.psm ,命令如图5-49。

cd E:\01. ISE9.1\labs\ verilog\lab4\Assembler

5)汇编编译系统把编写的汇编源文件program.psm 自动生成的用于程序内存的VHDL/Verilog 格式文件program.vhd/v 添加到工程中。

(2) 默认选项进行综合和实现

1)在工程的Sources 窗口单击顶层文件loopback.vhd/v 文件,双击Processes 窗口中的Synthesize – XST 进行综合;

2)综合完成后,双击View Synthesis Report;

3)在此报告中找到“Device utilization summary”,信息如下:

(3) 改变选项进行综合和实现

1)右击Synthesize 选择Properties,弹出Process Properties 对话框,将“Keep Hierarchy”值选为“Yes”,然后点击OK 按钮,重新双击Processes 窗口中的Synthesize –XST 进行综合;

2)综合完成后,双击View Synthesis Report ;

3)在此报告中找到“Device utilization summary”;

4)在此报告中也可看到线网最多的扇出为71,如图5-53。扇出会引起布线问题,因此综合会通过复用门或者嵌入缓存来限制扇出数。

5)右击Synthesize 选择Properties,弹出Process Properties 对话框,单击Category窗口的Xilinx Specific Options,将“Max Fanout”值改为50,单击OK 按钮。重新双击Processes 窗口中的Synthesize – XST 进行综合;

6)综合完成后,双击View Synthesis Report;

7)在此报告中找到“Timing Summary”,时钟频率评估值为378.146MHz;

(4)下载并测试系统

1)在工程的Sources 窗口单击顶层文件loopback.vhd/v 文件,展开Processes 窗口中的Generate Programming File,双击Configure Device (iMPACT);

2)弹出 Welcome iMPACT 对话框后,选择“ Configure devices using Boundary-Scan(JTAG)”,单击Finish 按钮,按照ISE9.1 程序下载过程,将loopback.bit 文件下载到FPGA 中后,超级终端显示如图所示。

1.5总结与体会

通过本次实验,我熟悉了ISE9.1 使用流程实验,了解了Architecture Wizard 与PACE 实验,并使用PACE,并且完成了一次综合技术实验,过程中熟悉了ISE9.1 开发环境,掌握工程的生成方法,掌握如何例化DCM模块单元并且学习使用保留层次和扇出综合这