准循环多进制LDPC码构造

第35卷第2期电子与信息学报Vol.35 No.2 2013年2月 Journal of Electronics & Information Technology Feb. 2013

准循环多进制LDPC码构造

杨民①张文彦②钟杰*②吴杰②

①(同方电子科技有限公司九江 332000)

②(浙江大学信息与通信工程研究所杭州 310027)

摘要:该文研究准循环多进制LDPC码的构造,给出多进制LDPC码的设计流程和构造方法。详细讨论了多进制LDPC码的性能影响因素,综合考虑了环长和环的连通性对性能的影响,研究了母矩阵扩展中偏移因子的选择以及GF(q)上非零元素替代。同时提出了次优解的搜索方法,以降低搜索复杂度。最后,将提出的方法用于不同阶数下LDPC码的构造。仿真结果表明,通过新方法构造得到的多进制LDPC码与二进制码相比,在BPSK调制方式下在误帧率4

10?附近有0.2 dB的性能提升;在有限域阶数与调制阶数匹配的情况下,有更大的性能提升。与相近码长,相同码率的多进制循环码相比,该文构造得到的多进制LDPC码在误帧率4

10?附近有0.25 dB的性能提升。

关键词:多进制LDPC;码构造;环长;满秩条件

中图分类号:TN911.22 文献标识码:A 文章编号:1009-5896(2013)02-0297-06 DOI: 10.3724/SP.J.1146.2012.00403

Construction of Non-binary QC-LDPC Codes

Yang Min① Zhang Wen-yan② Zhong Jie②Wu Jie②

①(Tong Fang Electronic Technology Co., Ltd., Jiujiang 332000, China)

②(Institute of Information and Communication Engineering, Zhejiang University, Hangzhou 310027, China)

Abstract: The construction of non-binary quasi-cyclic low-density parity-check codes are investigated. Important factors that influence the performance of non-binary LDPC codes are discussed in detail. The circle length and connectivity are taken into account in the construction. The selection of shift values to extend the mother matrix and the replacement of non-zero elements over GF(q) for the parity check matrix are studied. Meanwhile, a suboptimum method with lower complexity is proposed to search for the solution according to the new formula.

The method is applied to the construction of non-binary LDPC codes over different Galois fields. Simulation results show that the codes constructed by this method outperform the corresponding binary codes by 0.2 dB at FER around 4

10? on the BPSK AWGN channel. The performance gap is larger when the order of the Galois field equals the order of the modulation. Compared with non-binary cycle code with the same code rate and approximate code length, the constructed non-binary LDPC code gets an improvement of 0.25 dB at FER around 4

10?.

Key words: Non-binary LDPC; Code construction; Girth; Full Rank Condition (FRC)

1引言

LDPC码是一种具有接近香农极限的优秀信道编解码方案。文献[1]引入了多进制LDPC码,并且给出了相应的译码算法。与二进制LDPC码相比,多进制LDPC码具有更好的性能,且具有更好的抗突发错误能力。同时准循环结构的LDPC码具有更低的实现复杂度,因此吸引了广泛的研究。文献[2]研究了准循环矩阵中环的形成条件。文献[3]对环的

2012-04-09收到,2012-11-06改回

国家自然科学基金(61001133)资助课题

*通信作者:钟杰 zhongjie@https://www.360docs.net/doc/821441910.html, 连通性进行了研究,提出了ACE(Approximate Circle EMD(Extrinsic Message Degree))作为另外一个重要的性能影响因素。除此之外,多进制LDPC 码的校验矩阵还需要考虑GF()q上非零元素的替代。文献[4]研究了多进制LDPC码校验矩阵的二进制表示,提出了行满秩条件FRC(Full Rank Condition)用于非零元素的替代。针对特殊结构,文献[5-7]研究了基于有限域的准循环多进制LDPC 码的构造方法。文献[8,9]研究了基于代数几何的准循环多进制LDPC码的构造方法。文献[10,11]研究了环形图结构的多进制QC-LDPC码的构造。

基于有限域和代数几何的构造方法比较简单,

298 电 子 与 信 息 学 报 第35卷

但是适用于高码率LDPC 码的构造。基于环形图结构构造的多进制LDPC 码适用于64q ≥的情况[12]。本文在上述研究的基础上,提出了一种新的构造方法,用于16q ≤的中等码率多进制LDPC 码的构造。同时提出了搜索偏移因子和非零元素的方法,可以大大降低构造复杂度。两者相结合可以方便地根据码的参数构造得到相应的校验矩阵。本文的主要内容和章节安排如下。第2节简单介绍了准循环多进制LDPC 码的基本结构和表示方法;第3节分析了多进制LDPC 码的性能影响因素,推导得到构造的基本准则;第4节详细描述了准循环多进制LDPC 码构造算法;第5节给出了仿真结果,最后进行了总结。

2 准循环多进制LDPC 码简介

考虑定义在GF()q 上的多进制LDPC 码,q 为

质数的幂次方。

α是有限域的本原元,且有11q α?=。GF()q 中的元素都可以用α的幂次方表示,分别为22{0,1,,,,}q ααα? 。多进制LDPC 码的校验矩阵H 由GF()q 上的元素组成,有效码字c 满足

T ?=H c 0 (1) 多进制LDPC 码的构造思路是首先通过母矩阵扩展得到二进制LDPC 码的校验矩阵b H ,然后将校验矩阵中‘1’的位置用GF()q 上的非零元素替代,

得到多进制LDPC 码的校验矩阵q H 。

准循环LDPC 码的母矩阵表示为

1,11,21,11,2,12,22,12,,1,2,1,n n n n m m m n m n p p p p p p p p p p p p ?????????

??=?

?????????

P

… (2) 在P 中,,1i j p =?的位置表示对应位置由s s ×的全零矩阵替代,,i j p 为非负的位置表示对应位置由循环右移p 位的s s ×的单位矩阵替代,从而得到二进制校验矩阵b H 。然后将b H 上‘1’的位置用GF()q 上的非零元素替代,得到q H 。b H 的构造主要考虑的是环长的影响,尽可能消除短环。q H 上非零元素的选择主要考虑的是进一步消除b H 上短环的影响。

3 准循环多进制LDPC 码的构造影响因素

3.1 码距 多进制LDPC 码为线性分组码,其纠错性能受最小码距影响。对于GF(q )上码长为N ,信息位长度为K 的多进制LDPC 码(K 比较大),其最小码距d 满足普洛特金限:

(1)(1)

(1)K K Nq q N q d q q q

??≤≈

? (3) 多进制LDPC 码的码距主要由环长和环的连通性决定,校验矩阵中GF(q )元素的替代对码距也有一定的影响。

3.2 环长与环的连通性

定理1 假设122(,,,)t p p p 是H 矩阵上一个长度为2t 的环上的元素,定义

211gcd mod (1),,t i i i s

w p s s +==

???????????????????????

∑ (4) 则在扩展后矩阵中,存在长度为2w t ×的环,环的数量为/s w 。

定理1由文献[2]中的定理推导得到。根据环的形成条件,精心选择H 中的偏移值,可以使扩展后

的矩阵b H 中环长尽可能大。

扩展后矩阵中环的个数为/s w ,通过统计母矩阵中的环,然后计算环上元素的值,由此计算得到扩展后矩阵b H 上环的分布情况。

环的连通性一般通过停止集衡量。停止集v S 表示v 个变量节点组成的集合,与这个集合相连的子图中不存在任何度为1的校验节点。停止集被认为是二进制删除信道中译码失败的主要因素。外部信息度(EMD)是一个变量节点集合中外部校验节点的个数。对于停止集,它的外部信息度为0。一个外部信息度大的集合需要添加更多的变量节点才能形成停止集,因此得到的停止集更大。对于变量节点度大于2的矩阵,停止集是在环的基础上形成的。因此外部信息度小的短环在构造中是需要避免的。我们选择环的近似外部信息度(Approximate Circle EMD, ACE)作为衡量环的连通性的标准。假设2t C 表示一个长度为2t 的环,则2t C 的ACE [3]的计算方法为

1

(2)j

j t

v

j d ==?∑ (5)

3.3 行满秩条件

即使精心选择母矩阵中的偏移因子,扩展后的矩阵中仍然存在短环。因此需要通过GF()q 上非零元素的选择,进一步消除短环的影响。矩阵中形成环的部分通过行列调整都可以构成一个方阵。 式(6)所示为长度为2l 的环组成的方阵:

234522211

2000000d l l l ββββββββ?????????????????????=?????????????????????C (6) 如果d C 线性相关则存在一组非零系数T ,使得

第2期 杨 民等: 准循环多进制LDPC 码构造 299

0d ?=C T 。由此可能存在一个码字{0,,0,,′=c T 0,,0} ,满足0q ′?=H c 。由此引入低重量码字,

等价于小的码距,带来比较高的误码平层。因此需要通过GF()q 上非零元素的选择避免这个情况出现。矩阵d C 线性无关的条件是det()0d ≠C ,因此有如下所示行满秩条件(Full Rank Condition, FRC)[4]:

2121

1

l l

i i i i ββ?==≠∏∏ (7)

由于GF()q 上的元素可以用本原元的幂次方表示,此时形成环的矩阵可以表示为

2345222112000000l l l r r r r d r r r r αααααααα???????????????????????=?????????????????????C (8) 满秩条件中GF()q 上的乘法可以通过本原元幂的加

法表示,新的满秩条件为

211mod (1),10l i i i r q +=??????≠????

∑ (9) 通过对上面条件的变换,将环的形成条件与满秩条件统一起来。此时可以用相同的方法统一考虑二者的影响。

4 准循环多进制LDPC 码的构造算法

多进制LDPC 码的构造步骤主要根据度分布,通过PEG [9]算法构造母矩阵。然后根据环的形成条件和环的连通性确定偏移因子,得到扩展后的二进制LDPC 矩阵b H 。最后根据环的满秩条件确定b H 上‘1’的位置GF()q 非零元素的替代值,从而得到校验矩阵H 。

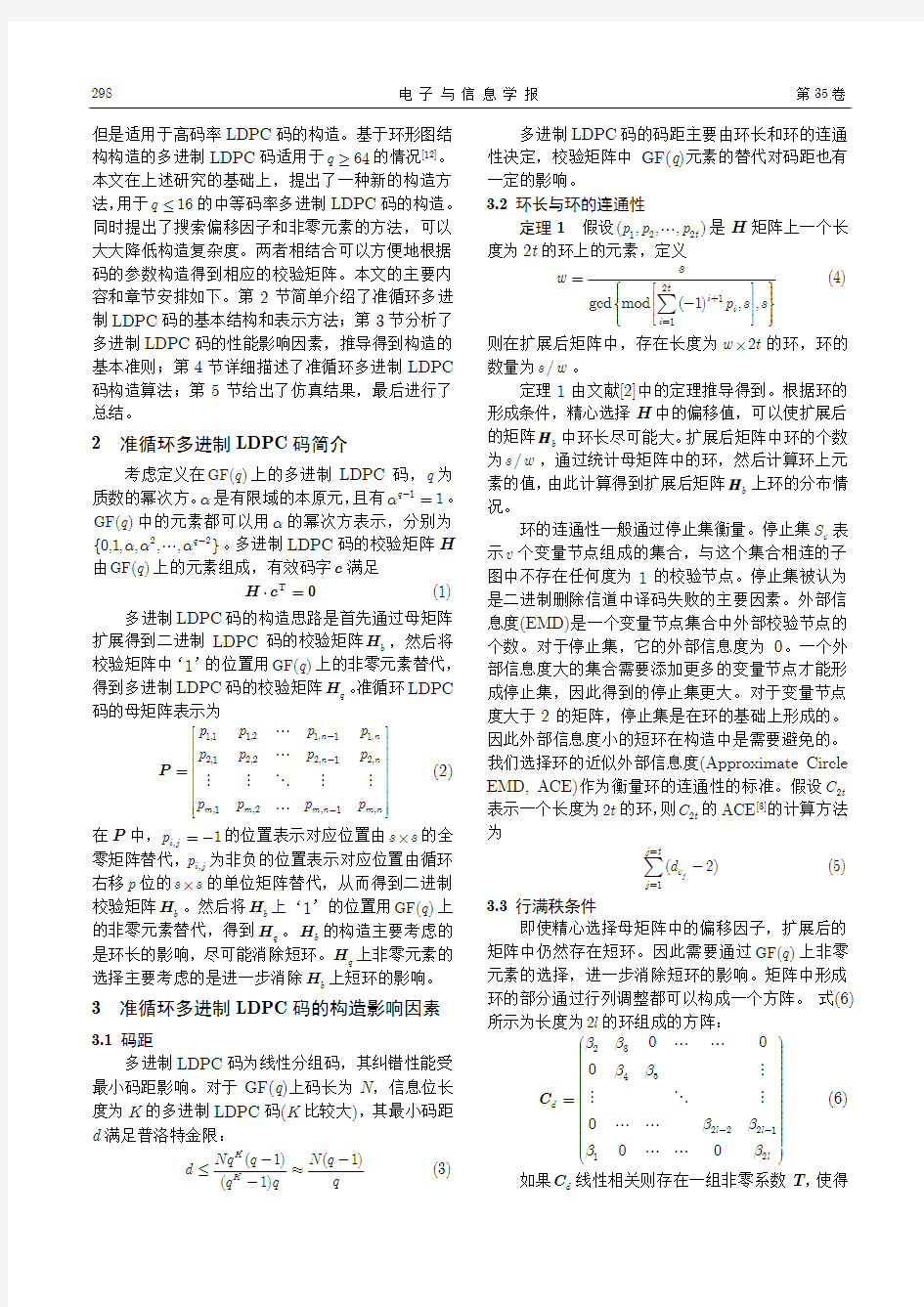

一般情况下,校验矩阵H 是否满秩由母矩阵结构、偏移因子和非零位置替代值共同决定。而当母矩阵满足某些特定结构或者度分布特性,如采用eIRA 结构[13]或者d v =2的满秩矩阵时,扩展得到的H 矩阵一定是满秩的,码率也由母矩阵的大小唯一确定。下面将对准循环多进制LDPC 码的构造算法展开进行讨论。图1所示为该构造算法的简要流程。 4.1 母矩阵构造

由于经过迭代译码之后变量节点度越小的点越不可靠,因此需要优先考虑度小的变量节点,尽量避免度小的变量节点之间形成短环。在构造过程中按照度的大小从小到大进行排序,通过PEG (Progressive Edge Growth)算法逐步添加到母矩阵中进行构造。PEG 算法是贪婪算法,每次添加的边,都使当前添加的变量节点局部环长最大。

图1 构造算法简要流程

4.2 母矩阵扩展

通过逐个添加变量节点的方式,根据扩展后矩阵中环的形成条件和环的连通性逐列确定偏移因子。对于新添加的变量节点,首先搜索与已添加变量节点在母矩阵中形成的短环,得到环的集合,然后建立方程组确定偏移因子,从而得到扩展矩阵b H 。

4.2.1 搜索图中的环 为了找到母矩阵中的环,我们把母矩阵展开为树的形式。在PEG 算法中,通过建立最小生成树找到图中最短的环。然而最小生成树并不能帮助找到图中所有的环,因此我们采用了一个新的方法。假设l Q 为第l 层中所有节点的集合,1l +Q 表示图中与l Q 中的节点相连的所有节点的集合。如果在集合l Q 中存在相同的节点,同时它们在树中的父节点不同,那么母矩阵中存在一个长度为2l 的环。

环的搜索复杂度随着环的层数增加几何级数增长,同时对性能影响比较大的主要是短环,因此不需要设置太大的展开层数。文献[14]给出了规则LDPC 码(,)c v d d 中最小环长的下界。

lg(/1)

1lg(1)(1)

c c v v c m

d m d d m t d d ×?×?+=

??? (10)

??(2)2g t =+× (11)

其中m 为码长,c d 为校验节点度,v d 为变量节点度,???为下取整操作。

令搜索的层数/2+1t L g ≥。在复杂度允许的范围内适当增大t L 的值,最小为/2+1g 。

下面以变量节点j V 为例,说明如何搜索得到与它有关的环。

(1)初始化:0l =,{}l j V =Q ;

(2)寻找所有与l Q 相连的节点,加入队列1

l +Q 中,记录各自的父节点信息;1l l =+;

(3)如果t l L ≤,则返回步骤(2),否则跳出,完

300 电 子 与 信 息 学 报 第35卷

成了环的搜索过程。

步骤(2)中,如果l Q 中元素同时满足下面3个条件,则形成了一个当前变量节点相关的环:

(a)在同一层存在相同的节点; (b)它们的父节点不同;

(c)它们在第1层中祖先节点不同。

条件(a)保证了环的存在,条件(b)和条件(c)保证了形成的环起止于根节点。

当满足这些条件的节点存在时,在树中回溯它们的祖先节点,并记录在一个链表上,从而得到与j V 有关的长度小于2t L 的所有环,记为j Ψ。同时计算环的ACE 。

4.2.2 偏移值的搜索 找到图中所有长度小于2t L 的环后,根据环的形成条件建立相应的方程组。令j V 为当前连接到图c G 的变量节点,它的度为j V d , 12[,,,]v j

j d b b b =B 是偏移矩阵中与j V 有关的元素的

集合。j B 中的每一个元素的取值范围是[0,1]s ?内

的整数,记为j dv

j ∈B X 。j B 中的所有元素初始化为0,建立的方程组与j B 的两个元素有关。根据

211(1)t

i i i p +=?∑,建立起所有环对应的方程组集合

E 。由于要同时考虑环长和环的连通性,在偏移因

子的搜索时首先确保没有4环,然后考虑ACE 与环长的一半之和作为度量,以此减少小的停止集出现的概率。

偏移因子的穷举搜索可以得到方程组最优解,但是搜索空间的大小随着变量节点的度和单位矩阵大小的增加呈几何级数增长。在两者比较大的时候,穷举搜索复杂度太高,因此考虑随机构造得到一个偏移矩阵,然后使用次优的贪婪算法进行搜索。

将集合j B 分为(1)/2j j V V d d ?组,

每组包含两个不同的元素,表示为

{(,)|,[1],[1]}j j m n v v CLU b b m n m d n d =≠∈∈ (12) 然后建立对应的方程组集合,集合中的每一个方程组都与CLU 中元素有关。贪婪算法的具体步骤如下:

(1)初始化k 为1;

(2)将集合E 中所有的与k b 有关方程合并到集合k E 中;

(3)遍历0到1s ?区间内的所有值,将集合中max min(ACE /2)G +的值作为解输出,同时更新k E 中所有的方程。k 自增1。如果j v k d >,那么跳至步骤(4),否则跳至步骤(2);

(4)更新j B 中的元素。 4.3 非零元素替代

通过前面的方法得到了扩展后二进制矩阵后,根据满秩条件式(8),进行非零元素的替代。由于扩

展后的矩阵中部分变量节点所在的环比较长,可能不在搜索的环长范围内,因此我们首先通过随机替代的方式初始化多进制LDPC 码的校验矩阵q H 信息位部分,然后在校验位部分对应的位置填1。接着搜索扩展后的矩阵b H 中的短环,根据 211(1)l

i i i r +=?∑建立对应的方程组集合q E 。最后通过贪婪算法搜索得到相应的非零元素进行调整。令

12(,,,)q V

j

j d r r r =R 是q H 中与q j V 有关的元素的集合。j R 中的每一个元素的取值范围是[0,2]q ?内的整数。将集合j R 分为(1)/2q q j j V V d d ?组,每组包含两 个不同的元素,表示为

{(,)|,[1],[1]}q q j j R m n v v CLU r r m n m d n d =≠∈∈(13) 然后建立对应的方程组集合,集合中的每一个方程组都与R CLU 中元素有关。非零元素替代的具体步骤如下:

(1)初始化k 为1;

(2)将集合q E 中所有的与k r 有关方程合并到集合q

k

E 中; (3)遍历0到2q ?区间内的所有值,将集合中

211(1)0l

i i i r +=?≠∑,或者等于零的个数最少的值作

为解输出,同时更新k E 中所有的方程。k 自增1。 如果q j v k d >,那么跳至步骤(3),否则跳至步骤(1); (4)更新j R 中的元素。

得到对应的元素后,转换到对应的GF()q 元素上,得到最终的多进制LDPC 码校验矩阵。

5 仿真结果与分析

在这一节中,我们利用前面描述的方法构造了GF(8), GF(16)域上的LDPC 码,等效比特码长1152,码率1/2,母矩阵大小为1632×。同时构造了相同参数的二进制LDPC 码进行比较。这些LDPC 码的校验矩阵均为eIRA 结构[13]。表1所示为对应的构造参数。

图2表示了当码长比特数一定时,GF 域的阶数q 与最小码距d 的上界的对应关系(码长归一化到1 bit)。从图中可以看出,当码长比特数不变时,q 越大,LDPC 码最小码距的上界越小,因而越容易出现误码平层。根据普洛特金限,构造得到的GF(2)上的LDPC 码的最小码距上界约为576, GF(8)上的

表1 LDPC 码构造参数

有限域 GF(2) GF(8) GF(16) 码长

1152 384 288

s 36 12 9

第2期杨民等:准循环多进制LDPC码构造301

图2 q与sup(d min)对应关系图

LDPC码的最小码距上界约为336, GF(16)上的LDPC码的最小码距上界约为213。

利用参考文献[15]中给出的对应参数下优化后的度分布,构造母矩阵:

GF(2)上度分布为

26

()0.26550.23890.4956

x x x x

λ=++(14)

67

()0.92920.0708

x x x

ρ=+(15)

GF(8)上度分布为

234

()0.45450.10230.2727+0.1705

x x x x x

λ=++(16)

45

()0.45450.5455

x x x

ρ=+(17) GF(16)上度分布为

234 ()0.640.240.05330.0667

x x x x x

λ=+++ (18)

34

()0.26670.7333

x x x

ρ=+(19) 仿真环境为AWGN信道,采用的译码算法为BP译码算法[1],迭代次数50次。通过PEG算法,根据式(13)~式(18)给出的度分布构造得到对应的母矩阵。然后根据环的形成条件式(4)得到对应的二进制矩阵。最后根据行满秩条件进行非零元素的替代,从而得到多进制矩阵。

图3所示为GF(8)上随机替代和根据FRC准则搜索得到的多进制LDPC码与二进制LDPC码的性能比较。从仿真结果可以看出,根据FRC准则搜索得到的多进制LDPC码与随机替代得到的多进制LDPC码相比有更好的性能,特别是在高信噪比条件下。优化后的八进制LDPC码与二进制LDPC码相比,在BPSK调制方式下,性能有0.2 dB的提升;在8PSK调制方式下,性能有0.3 dB的提升。

图4所示为GF(16)上随机替代和根据FRC准则搜索得到的多进制LDPC码与二进制LDPC码的性能比较。从仿真结果同样可以看到,根据FRC准则搜索得到的多进制LDPC码与随机替代得到的多进制LDPC码相比有更好的性能。优化后的十六进制LDPC码与二进制LDPC码相比,在BPSK调制方式下,性能有0.2 dB的提升;在16QAM调制方式下,性能有0.35 dB的提升。

图5所示为GF(16)上不同的构造方法得到的码的误帧率性能比较。图中循环码为文献[4]中给出的仿真结果,码长1504、码率1/2,仿真环境为AWGN 信道下采用BPSK调制,最大迭代次数为1000。我们用前面的方法构造得到了码长为1536、码率1/2的多进制LDPC码,采用相同的仿真环境,最大迭代次数为50次。从仿真结果我们可以看到在4

10?附近有0.25 dB的性能提升。

从仿真结果看,根据FRC准则进行非零元素的替代得到的多进制LDPC码具有更好的性能。优化后的多进制LDPC码与二进制LDPC码相比,性能有比较大的提升。在有限域阶数与调制阶数匹配的情况下,性能提升更明显。同时在有限域阶数比较低的情况下,采用本文中提出的构造方法得到的多进制LDPC码与循环码相比具有更好的性能。

图3 GF(2)与GF(8) 图4 GF(2)与GF(16) 图5 GF(16)上码率1/2不同构造误帧率性能比较误帧率性能比较方法得到的码的误帧率性能比较

302 电子与信息学报第35卷

6 结束语

本文研究了准循环多进制LDPC码的构造,详

细说明了准循环多进制LDPC码的设计流程和构造

方法。在母矩阵扩展时综合考虑了环长和环的连通

性对性能的影响,进行偏移因子的选择。为了进一

步减小短环对性能的影响,降低误码平层,我们对

多进制LDPC码校验矩阵中GF()q上非零元素替代

进行了研究。在前人研究的基础上,推导得到新的

替代准则。新的替代准则与偏移因子的选择具有类

似的表示方法,从而可以统一到一个框架下进行研究。在这个统一的框架下,我们提出了次优解的搜

索方法,具有更低的复杂度。最后,我们将提出的

方法用于不同阶数下LDPC码的构造。仿真结果表明,优化后的多进制LDPC码的性能与二进制码相比,在BPSK调制方式下在误帧率4

10?附近性能有0.2 dB的提升;在有限域阶数与调制阶数匹配的情况下,性能有0.3~0.35 dB的提升。新的构造方法

具有很好的灵活性,并且具有比较低的构造复杂度,可以用于不同参数的准循环多进制LDPC码的构造。

参考文献

[1]Davey M C and MacKay D J C. Low density parity check

codes over GF(q)[J]. IEEE Communications Letters, 1998,

2(6): 165-167.

[2]Myung S, Yang K, and Kim J. Quasi-cyclic LDPC codes for

fast encoding[J]. IEEE Transactions on Information Theory,

2005, 51(8): 2894-2901.

[3]Tian T, Jones C R, Villasenor J D, et al.. Selective avoidance

of cycles in irregular LDPC code construction[J]. IEEE

Transactions on Communications, 2004, 52(8): 1242-1247. [4]Poulliat C, Fossorier M, and Declercq D. Design of regular (2,

dc)-LDPC codes over GF(q) using their binary images[J].

IEEE Transactions on Communications, 2008, 56(10):

1626-1635.

[5]Zeng L, Lan L, Tai Y Y, et al.. Construction of nonbinary

cyclic, quasi-cyclic and regular LDPC codes: a finite

geometry approach[J]. IEEE Transactions on Communications, 2008, 56(3): 378-387.

[6]Song S, Zhou B, Lin S, et al.. A unified approach to the

construction of binary and nonbinary quasi-cyclic LDPC

codes based on finite fields[J]. IEEE Transactions on Communications, 2009, 57(1): 84-93.

[7]Zhou B, Kang J, Song S, et al.. Construction of non- binary

quasi- cyclic LDPC codes by arrays and array dispersions[J].

IEEE Transactions on Communications, 2009, 57(6): 1652-1662.

[8]Kang J, Huang Q, Zhang L, et al.. Quasi-cyclic LDPC codes:

an algebraic construction[J]. IEEE Transactions on Communications, 2010, 58(5): 1383-1396.

[9]Chen C, Bai B, Wang X, et al.. Nonbinary LDPC codes

constructed based on a cyclic MDS code and a low- complexity nonbinary message-passing decoding algorithm[J].

IEEE Communications Letters, 2010, 14(3): 239-241.

[10]Huang J, Zhou S, and Willett P. Structure, property, and

design of nonbinary regular cycle codes[J]. IEEE

Transactions on Communications, 2010, 58(4): 1060-1071.

[11]Chen C, Bai B, and Wang X. Construction of nonbinary

quasi-cyclic LDPC cycle codes based on singer perfect difference set[J]. IEEE Communications Letters, 2010, 14(2):

181-183.

[12]Li G, Fair I J, and Krzymie W A. Density evolution for

nonbinary LDPC codes under Gaussian approximation[J].

IEEE Transactions on Information Theory, 2009, 55(3):

997-1015.

[13]Zhang Y, Ryan W E, and Li Y. Structured eIRA codes with

low floors[C]. Proceedings of International Symposium on

Information Theory, Adelaide, 2005: 174-178.

[14]Hu X Y, Eleftheriou E, and Arnold D M. Regular and

irregular progressive edge-growth tanner graphs[J]. IEEE

Transactions on Information Theory, 2005, 51(1): 386-398. [15]Wu J, Zhao M, Zhong J, et al.. Statistical-based density

evolution algorithm for nonbinary low-density parity-check

codes[C]. IEEE Vehicular Technology Conference, San Francisco, 2011: 1-5.

杨民:男,1975年生,工程师,研究方向为短波通信与信道编码.

张文彦:男,1988年生,硕士生,研究方向为信道编码.

钟杰:男,1981年生,副研究员,研究方向为无线通信.

二进制转BCD码

二进制转换成十进制 BCD码(加3移位法 底下还附带了BCD码转二进制码转化的VHDL程序 算法 "二进制数调整BCD码的方法是将二进制码左移8次,每次移位后都检查低四位LSD+3是否大于7,如是则加3,否则不加,高4位MSD作同样处理" 一、为什么左移8次 原寄存器是存二进制数的,新寄存器是存十进制数的,当然要左移8次,把数据全部移进去。 但这里要注意两件事,第一,如果只安排一个字节作十进制寄存器,原数据要小于 64H (即100)。第二,由于新寄存器是十进制的,要随时调整。 二、检查半字节+3 是否大于 7,是,则 +3 在 51 系列里有十进制调节指令(半字节大于 9,则加 6,应该不难理解),PIC 里没有,只好采取变通的方法。 检查半字节+3 是否大于 7,也就是检查半字节是否大于 4。因为,如果大于 4(比如5、6),下一步左移就要溢出了,所以加 3,等于左移后的加 6,起到十进制调节的作用。 那为什么要绕个圈子去检测半字节+3 是否大于 7 呢?这样程序编起来会简练一些。 一个例子 假如有一个八位二进制数255,我把他转255的十进制数 0 1111 1111 原数 1 0000 0001 ;左移一次 2 0000 0011 ; 左移二次 3 0000 0111 ;左移三次,检查低四位+3>7? 3.1 0000 1010 ;大于7,加3进行调整 4 0001 0101 ;左移四次, 检查低四位+3>7?

4.1 0001 1000 ;大于7,加3进行调整 5 0011 0001 ;左移五次 6 0110 0011 ;左移六次,检查高四位+3>7? 6.1 1001 0011 ;大于7,加3进行调整 7 1 0010 0111 ;左移七次,检查低四位+3>7? 7.1 1 0010 1010 ;大于7,加3进行调整 8 10 0101 0101 ;左移八次(得到BCD码255 Library ieee; --16位二进制转BCD码(0到9999) Use ieee.std_logic_unsigned.all; Use ieee.std_logic_1164.all; Entity B_BCD is Port ( clk,ena:in std_logic; a: in std_logic_vector(15 downto 0); q: out std_logic_vector(15 downto 0)); end B_BCD; architecture behav of B_BCD is begin process(clk,a) variable i: std_logic_vector(4 downto 0); variable in_a,out_a :std_logic_vector(15 downto 0); begin if ena='0'then in_a:=a; i:="00000"; out_a:="0000000000000000"; elsif clk'event and clk='1' then if i="10000" then out_a:=out_a; else out_a:=out_a(14 downto 0)&in_a(15); in_a:=in_a(14 downto 0)&'0'; i:=i+1; if i<"10000" then if out_a( 3 downto 0)>4 then out_a( 3 downto 0):=out_a( 3 downto 0)+3; end if; if out_a( 7 downto 4)>4 then out_a( 7 downto 4):=out_a( 7 downto 4)+3; end if; if out_a(11 downto 8)>4 then out_a(11 downto 8):=out_a(11 downto 8)+3;

格雷码转二进制原理

在精确定位控制系统中,为了提高控制精度,准确测量控制对象的位置是十分重要的。目前,检测位置的办法有两种:其一是使用位置传感器,测量到的位移量由变送器经a/d转换成数字量送至系统进行进一步处理。此方法精度高,但在多路、长距离位置监控系统中,由于其成本昂贵,安装困难,因此并不实用;其二是采用光电轴角编码器进行精确位置控制。光电轴角编码器根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式三种。而绝对式编码器是直接输出数字量的传感器,它是利用自然二进制或循环二进制(格雷码)方式进行光电转换的,编码的设计一般是采用自然二进制码、循环二进制码、二进制补码等。特点是不要计数器,在转轴的任意位置都可读出一个固定的与位置相对应的数字码;抗干扰能力强,没用累积误差;电源切断后位置信息不会丢失,但分辨率是由二进制的位数决定的,根据不同的精度要求,可以选择不同的分辨率即位数。目前有10位、11位、12位、13位、14位或更高位等多种。 其中采用循环二进制编码的绝对式编码器,其输出信号是一种数字排序,不是权重码,每一位没有确定的大小,不能直接进行比较大小和算术运算,也不能直接转换成其他信号,要经过一次码变换,变成自然二进制码,在由上位机读取以实现相应的控制。而在码制变换中有不同的处理方式,本文着重介绍二进制格雷码与自然二进制码的互换。 一、格雷码(又叫循环二进制码或反射二进制码)介绍 在数字系统中只能识别0和1,各种数据要转换为二进制代码才能进行处理,格雷码是一种无权码,采用绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。格雷码属于可靠性编码,是一种错误最小化的编码方式,因为,自然二进制码可以直接由数/模转换器转换成模拟信号,但某些情况,例如从十进制的3转换成4时二进制码的每一位都要变,使数字电路产生很大的尖峰电流脉冲。而格雷码则没有这一缺点,它是一种数字排序系统,其中的所有相邻整数在它们的数字表示中只有一个数字不同。它在任意两个相邻的数之间转换时,只有一个数位发生变化。它大大地减少了由一个状态到下一个状态时逻辑的混淆。另外由于最大数与最小数之间也仅一个数不同,故通常又叫格雷反射码或循环码。下表为几种自然二进制码与格雷码的对照表: 十进制数自然二进制数格雷码十进制数自然二进制数格雷码 0 0000 0000 8 1000 1100 1 0001 0001 9 1001 1101 2 0010 0011 10 1010 1111 3 0011 0010 11 1011 1110 4 0100 0110 12 1100 1010 5 0101 0111 13 1101 1011 6 0110 0101 14 1110 1001 7 0111 0100 15 1111 1000 二、二进制格雷码与自然二进制码的互换 1、自然二进制码转换成二进制格雷码 自然二进制码转换成二进制格雷码,其法则是保留自然二进制码的最高位作为格雷码的最高位,而次高位格雷码为二进制码的高位与次高位相异或,而格雷码其余各位与次高位的求法相类似。 2、二进制格雷码转换成自然二进制码 二进制格雷码转换成自然二进制码,其法则是保留格雷码的最高位作为自然二进制码的最高位,而次高位自然二进制码为高位自然二进制码与次高位格雷码相异或,而自然二进制

一种高效的混合M元扩频通信方案

doi :10.3969/j.issn.1001-893x.2016.07.014引用格式:刘跃宣,马志强,曾辉,等.一种高效的混合M 元扩频通信方案[J].电讯技术,2016,56(7):794-798.[LIU Yuexuan,MA Zhiqiang,ZENG Hui,et al.An efficient hybrid M-ary spread spectrum communication scheme[J].Telecommunication Engineering,2016,56(7):794-798.] 一种高效的混合M 元扩频通信方案 * 刘跃宣**,马志强,曾 辉,余大波 (通信训练基地,河北宣化075100)摘 要:为进一步提高扩频通信系统的频带利用率和抗截获性能,将正交扩频技术与码相位循环移位调制技术相结合,提出了一种新的高效多进制扩频通信方案三在正交信道的每条支路上,首先采用M 元双正交扩频调制,再以每一个扩频码为原型码进行码相位循环移位调制,选用专用的伪噪声码进行同步,在接收端用基于变换域处理的循环相关器进行解扩三计算机仿真表明,该方案易于实现同步,同时有较高的频带利用率和更强的抗截获性能三该方案在卫星隐蔽通信二数据链通信等领域有较大的应用价值三 关键词:直接序列扩频通信;M 元扩频;双正交扩频;码相位循环移位调制;循环相关 中图分类号:TN914.4 文献标志码:A 文章编号:1001-893X (2016)07-0794-05 An Efficient Hybrid M -ary Spread Spectrum Communication Scheme LIU Yuexuan,MA Zhiqiang,ZENG Hui,YU Dabo (Communications Training Base,Xuanhua 075100,China) Abstract :In order to further improve the bandwidth efficiency and anti-intercept capability of spread spec-trum(SS)communication system,a new efficient M -ary SS communication scheme is proposed,which combines orthogonal SS and code phase shifting keying(CPSK)technique.In each branch of orthogonal channels,double M-ary biorthogonal SS modulation is adopted at first.Then every SS code is treated as a original code to adopt CPSK modulation,and the unattached pseudo noise(PN)code is chosen to achieve system synchronization.At the receiver,a circular correlator based on transform domain processing is em-ployed to despread the received signals.The simulations show that,the proposed scheme is easy to achieve synchronization,and is effective in improving the bandwidth efficiency and anti-intercept capability.The proposed scheme has great application value in the field of satellite covert communications and data link communications.Key words :direct sequence spread spectrum communication;M -ary spread spectrum;dual orthogonal spread spectrum;code phase shifting keying;circular correlation 1 引 言 直接序列扩频通信因具有较强的抗干扰二抗截 获二抗多径性能而应用广泛,但频带利用率较低三M 元扩频(或称为多进制扩频)通信与传统的直扩系 统相比,在相同的带宽条件下可以获得更高的信息 传输速率或扩频处理增益,大大提高了频带利用率,且其频谱更接近于白噪声,从而具有更强的抗截获性和信息保密性,得到了日益广泛的应用三选用M 个相互正交(或近似正交)的伪噪声(Pseudo Noise,PN)码构成扩频码集,利用一个扩频码传输lb M 比特信息(lb 表示以2为底的对数),称为正交扩频[1]三在其基础上进行BPSK 调制,称为四497四第56卷第7期2016年7月电讯技术Telecommunication Engineering Vol.56,No.7July,2016***收稿日期:2015-12-16;修回日期:2016-03-17 Received date :2015-12-16;Revised date :2016-03-17通信作者:yuexuanliu@https://www.360docs.net/doc/821441910.html, Corresponding author :yuexuanliu@https://www.360docs.net/doc/821441910.html,

二进制转换成BCD码 实验报告

一、实验目的 (1)进一步熟练掌握8086汇编语言编译调试工具和环境的操作; (2)掌握完整8086汇编的程序设计编写方法; (3)掌握简单的数值码制转换方法; (4)掌握键盘输出的DOS功能调用方法。 二、实验要求: 将AX中的一个二进制数(对应的十进制数范围是0-65535),转换成压缩性BCD 码表示的十进制,并从屏幕输出转换结果。要求用减法实现,并比较与除法方法进行运行速度比较。 三、实验及报告要求: 3.1、简要说明算法,并画出正确的程序流程图; 3.2、给出完整正确的源程序代码,要求给每一句伪指令或指令加上注释; 3.3、分别在DOS和Windows下编译、连接源程序生成可执行文件并调试,比较两个环境下生成的机器码的长度、寄存器内容、计算结果的异同。 3.4、如何观察转换过程中标志寄存器中各标志位的结果?如何观察转换结果的变化?试改变被转换数值,对结果与编制为的变化加以说明和解释。 3.5、写出完整的实验报告,特别是“实验结果”与“实验总结体会”部分,是评分的主要依据。 3.6、实验总结中要求结合实验中的经验、教训或体会对汇编语言格式、调试方法和微机原理学习方法作出总结。 四、程序流程图 减法。即五位数先循环减10000,直到不够减了,做减法的次数就是万分位的结果;将不够减之前一次的余数恢复,再循环减去1000,直到不够减了,做减法的次数就是千分位的结果;以此类推,最后恢复的正余数就是个位的结果. 除法。即五位数先除以10000,得到的商存放万位数的变量上;再将余数除以1000,得到的商存放千位数的变量上;之后将余数除以100,得到的商存放百分位的变量上;以此类推,最后的余数存放在个位的变量上。

单片机实验4 子程序设计-- BCD码转换为二进制

实验4. 子程序设计----BCD 码转换为二进制 单字节可存放两位压缩BCD 码(0—99) 为0 —9) 单字节BCD 码转换为二进制子程序 入口:(R0)= 压缩BCD 码的地址 出口:(A)= 转换结果 DSFR::MOV A,@R0 ANL A,#0F0H ;取十位数 SWAP A ;变为标准BCD 码 MOV B,#10 MUL AB ;(A)=D1×10 MOV R7,A ;D1× 10暂存 R7 MOV A,@R0 ANL A,#0FH ;取个位 ADD A,R7 ;A=D1×10+D0 RET 1、实验内容: 子程序设计要点: 1) 子程序一般为多次返复使用的程序段,一般应说明入口条件,DSFR 子程序的 入口条件是:被转换为二进制的单字节BCD 码为间接寻址,间接寻址寄存器为R0。要调用DFSR 子程序必需先将压缩BCD 码的存放地址赋与R0。而出口条件是指最后结果在哪儿存放。本子程序转换结果在ACC 内。 2) 主程序调用子程序,在调试时一般要先调试子程序、再调试主程序。

2、实验步骤 1)打开PV32编程序。汇编正确进入调试界面。否则修改程序重新汇编直到通过。 2)打开DATD窗口给20H、21H、R6、R7赋值 3)单步调试DSFR子程序观察并记禄寄存器、内存的变化。判断程序是否正确。若发现 问题重返编辑界面,修改、存盘、汇编。返回调试界面调试通过。 4) 设断点调试主程序观察并记禄寄存器、内存的变化。判断程序是否正确。若发现问 题重返编辑界面,修改、存盘、汇编。返回调试界面调试通过。 3.实验报告 1.写出主程序流程图、子程序流程图、程序清单 2.根据记渌数据给程序加注解 3.调试心得

多进制数字相位调制(MPSK)系统.doc

多进制数字相位调制(MPSK)系统 多相移键控(MPSK -多相移键控)也被称为多相位系统,它是二相系统的推广。它是利用不同载波的相位状态来表征数字信息的调制。与二进制数字相位调制相似,它有绝对相位调制(MPSK)和相位调制(MDPSK)两种调制方式。本文以4PSK为例,主要介绍基于Xilinx ISE 仿真软件的多相移键控系统(MPSK)的设计。调制方法是简单的相位选择方法。它只专注于数字系统的设计,而忽略了模拟电路系统。关键词:多相移键控MPSK西林ISE选相方法摘要多进制数字相位调制(MPSK -多相移键控)又称多相制,是二相制的推广。它是利用载波的多种不同相位状态来表征数字信息的调制方式。与二进制数字相位调制相同,多进制数字相位调制也有绝对相位调制(MPSK)和相对相位调制(MDPSK)两种。本文主要研究基于Xilinx ISE仿真软件设计的多进制数字相位调制(MPSK)系统,以4PSK系统为例。调制方法采用简便的相位选择法,且略去模拟电路系统部分,仅对数字系统进行设计。关键字: 多进制数字相位调制MPSK锡林郭勒ISE相位选择法武汉理工大学《FPGA课程设计》说明书目录摘要1摘要11 多进制数字相位调制11.1 MPSK概念11.2 MPSK原理12 四相相位调制(4PSK) 22.1 4PSK调制22.1.1相位选择法22.1.2直接调相法32.2 4PSK解调42.3 4PSK调制与解调系统设计53 ISE设计与仿真73.1 ISE操作环境73.1.1输入(设计条目)73.1.2综合(综合83.1.3)实现(实施83.1.4)验证(验证83.1.5)下载(下载)93.2 ISE程序设计93.2.1调制系统程

多进制数字相位调制(MPSK)系统

Abstract Multiple Phase Shift Keying (MPSK - multiple phase shift keying) is also called multi-phase system, which is the promotion of the two-phase system. It is the modulation to characterize digital information using the different carrier’s phase state. Similar with the Binary Digital Phase Modulation, it has the absolute phase modulation (MPSK) and phase modulation (MDPSK) as the two kinds of modulation methods. This article is mainly about the Multiple Phase Shift Keying system (MPSK) based on Xilinx ISE simulation software design, setting 4PSK as an example. The modulation method is the simple phase-selection method. It only concentrates on the design of digital system, neglecting the analog circuit system. Keywords: Multiple Phase Shift Keying MPSK Xilinx ISE phase-selection method

格雷码、二进制转换及译码电路

EDA技术与应用 实验报告 实验名称:格雷码、二进制转换及译码电路 姓名:陈丹 学号:100401202 班级:电信(2)班 时间:2012.11.27 南京理工大学紫金学院电光系

一、实验目的 1)学习用VHDL代码描述组合逻辑电路的方法。 2) 掌握when….else….,generate和case并行语句的使用。 二、实验原理 1)学习VHDL的when….else….,generate和case并行语句。 2)利用when….else….并行语句描述4位二进制码/格雷码转换电路。 3)利用generate并行语句描述n位格雷码/二进制码转换电路。 4)利用case并行语句实现译码电路。 5)利用实验箱验证所设计的电路的正确性,要求将输入输出的数据用数码管显示。 三、实验内容 1、二进制转换为格雷码 4位二进制格雷码转换的真值表如图所示:

1.1建立工程,输入代码 先建立工程,工程命名为“btog”,顶层文件名为“btog”。 选择“file→new”,在弹出的窗口中选择“VHDL File”建立“VHDL”文件。 在新建的VHDL文件中输入二进制格雷码转换的VHDL代码,将文件保存。 二进制转换为格雷码的代码: 1.2 编译仿真 对当前文件进行编译,编译通过以后建立仿真波形,保存为“b_to_g.vwf”.为波形文件添加节点,将“end time”设置为100μs ,将输入输出编组,并为输入信号赋值,其中“start value”为“0000”,“count every”设置为5μs.其波形如下:

仿真结果 2、generate语句实现格雷码转换为二进制 对于n位二进制转换为格雷码的码转换电路,转换表达式如下: Bn=Gn Bi=Gi⊕B(i+1) 2.1建立工程,输入代码 先建立工程,工程命名为“gtob”,顶层文件名为“g_to_b2”。 选择“file→new”,在弹出的窗口中选择“VHDL File”建立“VHDL”文件。 在新建的VHDL文件中输入格雷码二进制转换的VHDL代码,将文件保存。 转换代码:

二进制码转换为BCD码实验报告

实验二二进制码转换为BCD码 一、实验目的 1、掌握数码转换基本方法,加深对数码的理解。 2、用于十进制BCD码显示。 二、实验内容 将AX的内容转换为十进制BCD码。 三、实验程序框图 四、实验步骤 脱机模式: (1)在P、态,按SCAL键,输入2CE0,按EXEC键。 (2)复位RST键,由于AX中给定数为0FFFF,查瞧BCD码结果保留在4100H~4104H单元中,故其值应为06、05、05、03、05。 联机模式: (1)在PC机与实验系统联机状态下,运行该实验程序,可用鼠标左键单击菜单栏“文件”或工具栏“打开图标”,弹出“打开文件”的对话框,然后打开8kAsm文件夹,点击S2、ASM文件,单击“确定”即可装入源文件,再单击工具栏中编译,即可完成源文件自动编译、装载目标代码功能,再单击“调试”中“连续运行”或工具图标运行,即开始运行程序。 (2)复位“系统复位”键,由于AX中给定数为0FFFF,查瞧BCD码结果保留在4100H~4104H

单元中,故其值应为06、05、05、03、05。 注:操作过程参照“实验一二进制多位加法运算”。 五、实验程序清单 X:\DICE-8086K3微机原理与接口实验箱CDROM\CODE\86kasm\S2、ASM ;将AX拆为5个BCD码,并存入Result开始的5个单元 DATA SEGMENT AT 0 ;S2、ASM,BIN-->BCD ORG 4000H RESULT DB 5 DUP(?) DATA ENDS CODE SEGMENT ASSUME CS:CODE, DS:DATA ORG 2CE0H START PROC NEAR MOV AX, DATA MOV DS, AX MOV DX,0000H MOV AX, 65535 MOV CX, 10000 DIV CX MOV RESULT, AL ; 除以 10000, 得WAN位数 MOV AX,DX MOV DX,0000H MOV CX, 1000 DIV CX MOV RESULT+1, AL ; 除以 1000, 得QIAN位数 MOV AX,DX MOV DX,0000H MOV CX, 100 DIV CX MOV RESULT+2, AL ; 除以 100, 得BAI位数 MOV AX,DX MOV DX,0000H MOV CX, 10 DIV CX MOV RESULT+3, AL ; 除以 10, 得SHI位数 MOV RESULT+4, DL ; 得GE位数 JMP $ CODE ENDS END START

二进制数到BCD码的转换

得分教师签名批改日期课程编号1801770001 深圳大学实验报告课程名称:微机原理及应用 实验名称:二进制数到BCD码的转换 学院:物理科学与技术学院 指导教师: 报告人:组号: 学号实验地点K302 实验时间:2014 年10 月22 日 提交时间:2014.11.12

一、实验要求: 将AX中的一个二进制数(对应的十进制数范围是0-65535),转换成压缩性BCD码表示的十进制,并从屏幕输出转换结果。要求用减法实现,并比较与除法方法进行运行速度比较。 二、实验目的: (1)进一步熟练掌握8086汇编语言编译调试工具和环境的操作; (2)掌握完整8086汇编的程序设计编写方法; (3)掌握简单的数值码制转换方法; (4)掌握键盘输出的DOS功能调用方法。 三、实验说明: 计算机中的数值有各种表达方式,这是计算机的基础。掌握各种数制、码制之间的转换是一种基本功;利用DOS功能调用实现在屏幕上显示字符或数字的方法是本课程的基本要求之一。 四、除法方法: 1、算法说明:三位数先除以100,得到的商就是百分位的结果;将之前一次的余数除以10,得到的商就是十分位的结果;剩下来的余数就是个位的结果。 2、程序流程图: 图1 除法程序流程图 3、程序: DATA SEGMENT ; 数据段 RESULT_1 DB 1

RESULT_2 DB 1 RESULT_3 DB 1 DATA ENDS STACK SEGMENT STACK ; 堆栈段 STA DB 64 DUP(0) STACK_TOP DB 0 STACK ENDS CODE SEGMENT ; 代码段 ASSUME CS:CODE , DS:DATA , ES:DATA , SS:STACK START: ; 程序开头必须要有的五条指令 MOV AX, DATA MOV DS, AX ; 设置数据段 MOV AX, STACK MOV SS, AX ; 设置堆栈段 LEA SP, STACK_TOP ; 设置栈顶指针 ;--------------------------------------- ; 程序的中间部分 MOV AX, 467 MOV CL, 100 DIV CL MOV RESULT_1, AL ; 除以 100, 得百位数 MOV AL, AH MOV AH, 0 MOV CL, 10 DIV CL MOV RESULT_2, AL ; 余数除以 10, 得十位数 MOV RESULT_3, AH ; 余数为个位数 ;------------------------------------------ ; 程序结束必须要有的两条指令 MOV AX, 4C00H ; INT 21H ; ;------------------------------------------ CODE ENDS

格雷码和二进制码的转换

二进制格雷码与自然二进制码的互换 中国科学院光电技术研究所游志宇 示例工程下载 在精确定位控制系统中,为了提高控制精度,准确测量控制对象的位置是十分重要的。目前,检测位置的办法有两种:其一是使用位置传感器,测量到的位移量由变送器经A/D转换成数字量送至系统进行进一步处理。此方法精度高,但在多路、长距离位置监控系统中,由于其成本昂贵,安装困难,因此并不实用;其二是采用光电轴角编码器进行精确位置控制。光电轴角编码器根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式三种。而绝对式编码器是直接输出数字量的传感器,它是利用自然二进制或循环二进制(格雷码)方式进行光电转换的,编码的设计一般是采用自然二进制码、循环二进制码、二进制补码等。特点是不要计数器,在转轴的任意位置都可读出一个固定的与位置相对应的数字码;抗干扰能力强,没用累积误差;电源切断后位置信息不会丢失,但分辨率是由二进制的位数决定的,根据不同的精度要求,可以选择不同的分辨率即位数。目前有10位、11位、12位、13位、14位或更高位等多种。 其中采用循环二进制编码的绝对式编码器,其输出信号是一种数字排序,不是权重码,每一位没有确定的大小,不能直接进行比较大小和算术运算,也不能直接转换成其他信号,要经过一次码变换,变成自然二进制码,在由上位机读取以实现相应的控制。而在码制变换中有不同的处理方式,本文着重介绍二进制格雷码与自然二进制码的互换。 一、格雷码(又叫循环二进制码或反射二进制码)介绍 在数字系统中只能识别0和1,各种数据要转换为二进制代码才能进行处理,格雷码是一种无权码,采用绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。格雷码属于可靠性编码,是一种错误最小化的编码方式,因为,自然二进制码可以直接由数/模转换器转换成模拟信号,但某些情况,例如从十进制的3转换成4时二进制码的每一位都要变,使数字电路产生很大的尖峰电流脉冲。而格雷码则没有这一缺点,它是一种数字排序系统,其中的所有相邻整数在它们的数字表示中只有一个数字不同。它在任意两个相邻的数之间转换时,只有一个数位发生变化。它大大地减少了由一个状态到下一个状态时逻辑的混淆。另外由于最大数与最小数之间也仅一个数不同,故通常又叫格雷反射码或循环码。下表为几种自然二进制码与格雷码的对照表: 十进制数自然二进制数格雷码十进制数自然二进制数格雷码 0 0000 0000 8 1000 1100 1 0001 0001 9 1001 1101 2 0010 0011 10 1010 1111 3 0011 0010 11 1011 1110 4 0100 0110 12 1100 1010 5 0101 0111 13 1101 1011 6 0110 0101 14 1110 1001 7 0111 0100 15 1111 1000

常用多进制数字调制技术基础

常用多进制数字调制技术基础 1 常用多进制数字调制技术及应用 1.1 QPSK(四相相移键控)技术及应用 (1)QPSK技术 在相移键控(PSK)技术中,通过改变载波信号的相位来表示二进制数0、1,而相位改变的同时,最大振幅和频率则保持不变。例如,可以用两种不同相位的正弦信号分别表示0和1,用0°相位表示0,用180°相位表示1,这种PSK技术称为二相位PSK或2-PSK,信号之间的相位差为180°。 同样,可以用4种不同相位的正弦信号分别表示00、01、10和11,例如,用0°相位表示00,用90°相位表示01,用180°相位表示10,用270°相位表示11。这样每种相位的正弦信号可以表示两位二进制信息,信号之间的相位差为90°,这种PSK技术称为四相位PSK或QPSK,由于4个相位与四进制的4个符号相对应,也称四进制PSK调制。因每种相位的正弦信号可以表示两位二进制信息,与2-PSK相比,其编码效率提高了1倍。 以此类推,当不同相位的载波数为8、16……时,分别称为8-PSK(八进制PSK)、16-PSK(十六进制PSK)……,理论上,不同相位差的载波越多,可以表征的数字输入信息越多,频带的压缩能力越强,可以减小由于信道特性引起的码间串扰的影响,从而提高数字通信的有效性。但在多相调制时,相位取值数增大,信号之间的相位差也就减小,传输的可靠性将随之降低,因而实际中用得较多的是四相制(4-PSK)和八相制(8-PSK)。 (2)QPSK的应用 QPS K广泛应用于数字微波通信系统、数字卫星通信系统、宽带接入与移动通信及有线电视的上行传输。在卫星数字电视传输中普遍采用的QPSK调谐器可以说是当今卫星数字电视传输中对卫星功率、传输效率、抗干扰性以及天线尺寸等多种因素综合考虑的最佳选择。欧洲与日本的数字电视首先考虑的是卫星信道,采用QPSK调制,我国也出现了采用QPSK调制解调的卫星广播和数字电视机。 要实现卫星电视的数字化,必须在卫视传输中采用高效的调制器和先进的压缩技术,因为我国现行的PAL制彩色电视是采用625行/50场,其视频带宽5 MHz,根据4∶2∶2的标准,625行/50场的亮度信号(Y)的取样频率为13.5 MHz,每个色差信号(R-Y)和(B-Y)的取样频率均为6.75 MHz。当Y,(R-Y),(B-Y)信号的每个取样为8 bit量化时,电视信号经数字化后的亮度信号码率为13.5×8=108 Mbps,色度信号的码率为6.75×8×2=108 Mbps,总码率为色亮码率之和,即216 Mbps,在现有的传输媒介中要传送这样宽带的数字电视信号是不可能的。

实验二二进制码转换为bcd码实验报告终审稿)

实验二二进制码转换为 B C D码实验报告 公司内部档案编码:[OPPTR-OPPT28-OPPTL98-OPPNN08]

实验二二进制码转换为BCD码 一、实验目的 1、掌握数码转换基本方法,加深对数码的理解。 2、用于十进制BCD码显示。 二、实验内容 将AX的内容转换为十进制BCD码。 三、实验程序框图 四、实验步骤 脱机模式:

(1)在P.态,按SCAL键,输入2CE0,按EXEC键。 (2)复位RST键,由于AX中给定数为0FFFF,查看BCD码结果保留在4100H~4104H单元中,故其值应为06、05、05、03、05。 联机模式: (1)在PC机和实验系统联机状态下,运行该实验程序,可用鼠标左键单击菜单栏“文件”或工具栏“打开图标”,弹出“打开文件”的对话框,然后打开8kAsm文件夹,点击文件,单击“确定”即可装入源文件,再单击工具栏中编译,即可完成源文件自动编译、装载目标代码功能,再单击“调试”中“连续运行”或工具图标运行,即开始运行程序。 (2)复位“系统复位”键,由于AX中给定数为0FFFF,查看BCD码结果保留在4100H~4104H单元中,故其值应为06、05、05、03、05。 注:操作过程参照“实验一二进制多位加法运算”。 五、实验程序清单 X:\DICE-8086K3微机原理与接口实验箱CDROM\CODE\86kasm\ ;将AX拆为5个BCD码,并存入Result开始的5个单元 DATA SEGMENT AT 0 ;,BIN-->BCD ORG 4000H RESULT DB 5 DUP() DATA ENDS CODE SEGMENT

格雷码与二进制代码的转换规则

格雷码与二进制代码的转换规则 一、什么是格雷码? 首先我们来了解一下格雷码。前面我们介绍了一些常见的BCD码,8421BCD、2421BCD、5421BCD,还有余三码,那么这个格雷码我们接触较少,什么是格雷码呢?这种码是一个叫弗兰克*格雷的人在1953年发明的,最初用于通信。 格雷码,又叫循环二进制码或反射二进制码,它的基本的特点就是任意两个相邻的代码只有一位二进制数不同,这点在下面会详细讲解到。在数字系统中,常要求代码按一定顺序变化。例如,按自然数递增计数,若采用8421码,则数0111变到1000时四位均要变化,而在实际电路中,4位的变化不可能绝对同时发生,则计数中可能出现短暂的其它代码(1100、1111等)。在特定情况下可能导致电路状态错误或输入错误。使用格雷码可以避免这种错误。格雷码属于可靠性编码,是一种错误最小化的编码方式。 举个例子来说吧,如果用一个8位的二进制数表示热水壶的温度,温度是不断连续变化的,36°C、37°C、38°C......,那么温度每升高一度,二进制数就加1。这时候,二进制数有可能是多个位同时变化的:当温度由119°C变成120°C时,二进制数由01110111变化成01111000,有四个位发生变化;当二进制数由177°C变化成178°C时,二进制数由01111111变化成10000000,有8个位发生了变化。也就是说,自然二进制数在表示一个连续变化的数值时,可能会有多个位同时发生变化,每个位翻转(变化)的频率是比较高的,这在某些应用场合,是十分不利的。而格雷码,由于具有循环特性和单步特性,当用它表示

一个连续变化的数值时,仅有一个位会翻转,大大的降低了位翻转的频率,因而可以保证传输的稳定性,较少传输误码率。格雷码的单步特性呢就是是指,当格雷码表示的一个数值,连续变化时,格雷码只有一个位会变化。就是我刚才说的它最基本的特点了。还有格雷码的单步特性是指,当格雷码表示的一个数值,连续变化时,格雷码只有一个位会变化。看表,1000变到0000,格雷码只有一位翻转。 二、格雷码与二进制码转换规则 大家看一下这个表,有没有发现二进制转为格雷码的规律?看上去,格雷码似乎很乱,不像8421码那样连续的。我们记8421码的时候很轻松,因为它每位的值都是固定的数,有位权。那么我们怎么记格雷码呢?死背真值表?当然了,这是一种方法,有能力又勤奋的同学可以用这种方法。不过呢,很多东西都是有它独特的规律的,格雷码也不例外。现在我们先来看二进制转换为格雷码的过程,也就是编码。 最初就说了,格雷码的基本特点就是任意两个相邻的代码只有一位二进制 十进制数 自然二进制数 格雷码 十进制数 自然二进制数 格雷码 0 0000 0000 8 1000 1100 1 0001 0001 9 1001 1101 2 0010 0011 10 1010 1111 3 0011 0010 11 1011 1110 4 0100 0110 12 1100 1010 5 0101 0111 13 1101 1011 6 0110 0101 14 1110 1001 7 0111 0100 15 1111 1000

chirp扩频综述

Chirp扩频技术综述 摘要:众所周知,扩频技术具有显著的抗干扰和抗衰落特性,并且具有低功耗,及低的被检测概率,因此,扩频技术被广泛的应用于民用和军用通信中。常用的扩频技术主要有三种:直接序列扩频,跳频和chirp扩频(Chirp Spread Spectrum,CSS)技术。相比于前两者,Chirp 扩频技术的抗多普勒频移能力更强,且可有效的抗深度衰落。由于水声信道的多普勒频移是不可忽略的,因此,有必要对chirp扩频技术进行深入的研究,使其能成为水声通信中一种新的调制体制。另外,近年来FRFT(Fractional Fourier Transform,分数阶傅里叶变换)是信号处理领域一个研究热点,不同于普通的傅里叶变换,FRFT的基函数正是一系列chirp 函数,这使得FRFT可用于检测chirp信号和chirp参数估计,因此,将其引入Chirp扩频系统。本文将介绍chirp扩频技术的基本原理,及其主要发展和应用,并对基于chirp扩频的多址方案进行讨论。最后还将介绍基于FRFT的Chirp扩频系统。 一.Chirp扩频技术简介 CSS技术是用线性调频的Chirp脉冲调制发送信息来达到扩频效果的。Chirp脉冲是正弦信号,在一定时间段内,其频率随时间线性增加或减小。与DSSS、FHSS相似,CSS利用了它的整个带宽去扩展信号的频谱,不同的是CSS不需要加入任何伪随机序列,它利用了Chirp脉冲自身的频率线性特征,其频率是连续变化的。 CSS与DSSS的解扩原理也有相似之处。DSSS是通过PN序列扩频的,其解扩需要利用PN序列良好的自相关特性,即:其自相关远大于互相关。在接收端,如果本地PN序列与接收到的PN序列具有相同的相位时,相关运算出现最大值。所以可以通过自相关运算,对信号进行解扩,实现数据符号的检测。CSS的解扩利用了脉冲压缩原理。接收信号经过匹配滤波后,出现了尖峰脉冲,接收机可以通过对尖峰脉冲的能量捕获来进行数据符号的检测。匹配滤波在一定程度上可以看作是求自相关。所以可以认为CSS和DSSS都是通过对扩频序列(信号)求自相关来解扩的。 与传统的扩频技术相比,Chirp扩频有其独特的优点:Chirp扩频的处理增益由信号的时间带宽积TB决定,而Chirp信号的时间带宽积远大于1,所以利用Chirp脉冲传送数据,有较强的抗干扰能力。Chirp扩频利用了非常宽的频带,即使在非常低的发射功率下,仍然可以抗多径衰落。同时Chirp扩频还能抗移动通信中常见的多普勒频移。【1】

格雷码与二进制转换

在数字系统中只能识别0和1,各种数据要转换为二进制代码才能进行处理,格雷码是一种无权码,采用绝对编码方式,典型格雷码是一种具有反射特性和循环特性的单步自补码,它的循环、单步特性消除了随机取数时出现重大误差的可能,它的反射、自补特性使得求反非常方便。格雷码属于可靠性编码,是一种错误最小化的编码方式,因为,自然二进制码可以直接由数/模转换器转换成模拟信号,但某些情况,例如从十进制的3转换成4时二进制码的每一位都要变,使数字电路产生很大的尖峰电流脉冲。而格雷码则没有这一缺点,它是一种数字排序系统,其中的所有相邻整数在它们的数字表示中只有一个数字不同。它在任意两个相邻的数之间转换时,只有一个数位发生变化。它大大地减少了由一个状态到下一个状态时逻辑的混淆。另外由于最大数与最小数之间也仅一个数不同,故通常又叫格雷反射码或循环码。 二、二进制格雷码与自然二进制码的互换 1、自然二进制码转换成二进制格雷码 自然二进制码转换成二进制格雷码,其法则是保留自然二进制码的最高位作为格雷码的最高位,而次高位格雷码为二进制码的高位与次高位相异或,而格雷码其余各位与次高位的求法相类似。 例如:自然二进制编码如下: 1001 那么转换为格雷码的方法是:保留最高位1,然后将第二位0与第一位1做异或操作,第三位的0与第二位的0做异或操作,第四位的1与第三位的0做异或操作,得到结果如下: 1 1 0 1 Gray

2、二进制格雷码转换成自然二进制码 二进制格雷码转换成自然二进制码,其法则是保留格雷码的最高位作为自然二进制码的最高位,而次高位自然二进制码为高位自然二进制码与次高位格雷码相异或,而自然二进制码的其余各位与次高位自然二进制码的求法相类似。例如:将格雷码1000转换为自然二进制码: 1000 1111 上排为格雷码,下排为自然二进制,从左到右分别为1~4位 将上排的第一位高位作为自然二进制的最高位,因此在下排的第一位填入1,然后以上排第二位与下排第一位做异或操作,得到下排第二位结果为1,将上排第三位与下排第二位做异或操作,得到下排第三位的结果为1,同理,下排第四位的结果为1,因此,我们得到了转换结果如下: 1 1 1 1 Bin 二进制码->格雷码(编码):从最右边一位起,依次将每一位与左边一位异或(XOR),作为对应格雷码该位的值,最左边一位不变(相当于左边是0); 格雷码-〉二进制码(解码):从左边第二位起,将每位与左边一位解码后的值异或,作为该位解码后的值(最左边一位依然不变).