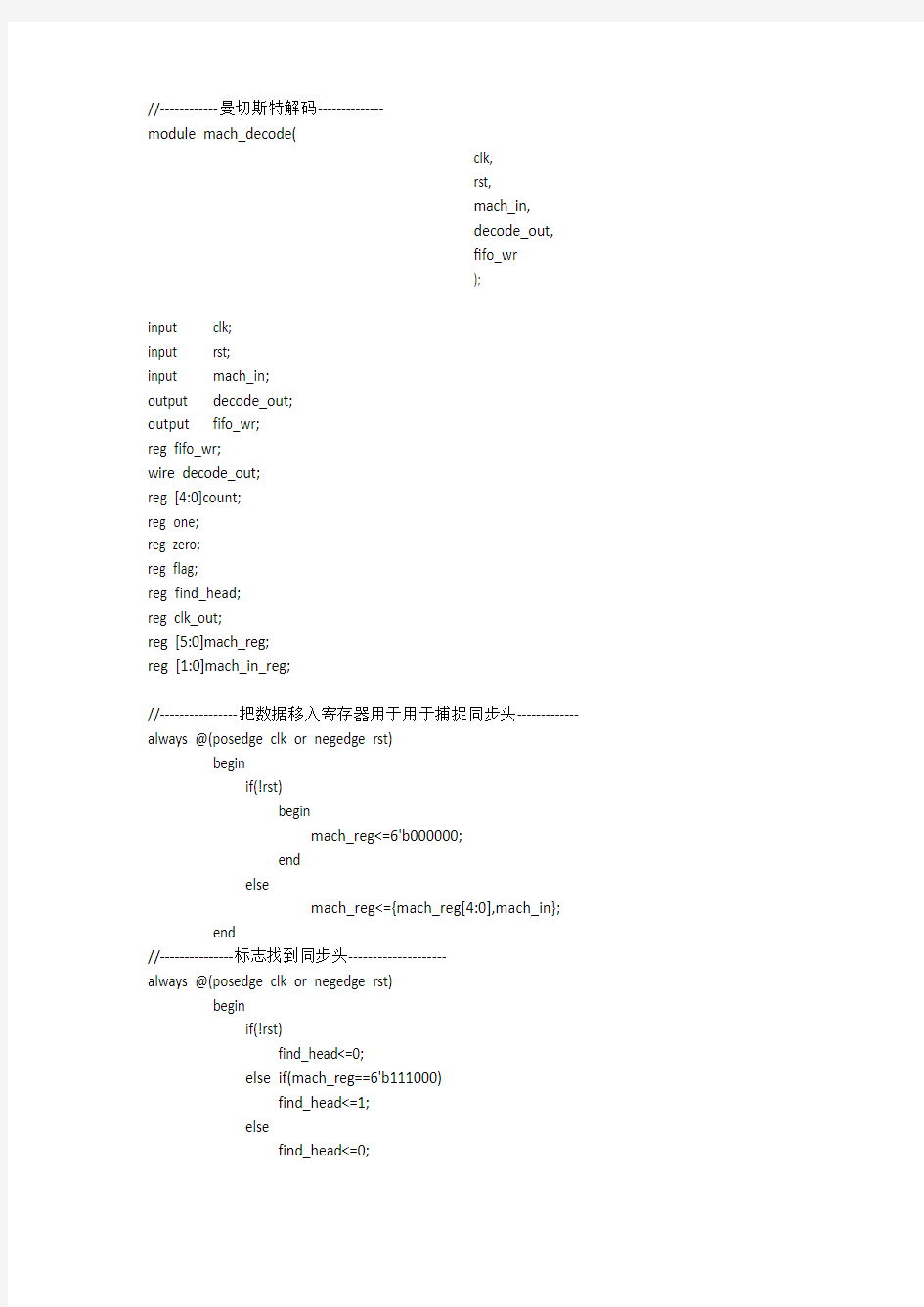

verilog曼切斯特解码

//------------曼切斯特解码--------------

module mach_decode(

clk,

rst,

mach_in,

decode_out,

fifo_wr

);

input clk;

input rst;

input mach_in;

output decode_out;

output fifo_wr;

reg fifo_wr;

wire decode_out;

reg [4:0]count;

reg one;

reg zero;

reg flag;

reg find_head;

reg clk_out;

reg [5:0]mach_reg;

reg [1:0]mach_in_reg;

//----------------把数据移入寄存器用于用于捕捉同步头------------- always @(posedge clk or negedge rst)

begin

if(!rst)

begin

mach_reg<=6'b000000;

end

else

mach_reg<={mach_reg[4:0],mach_in};

end

//---------------标志找到同步头--------------------

always @(posedge clk or negedge rst)

begin

if(!rst)

find_head<=0;

else if(mach_reg==6'b111000)

find_head<=1;

else

find_head<=0;

end

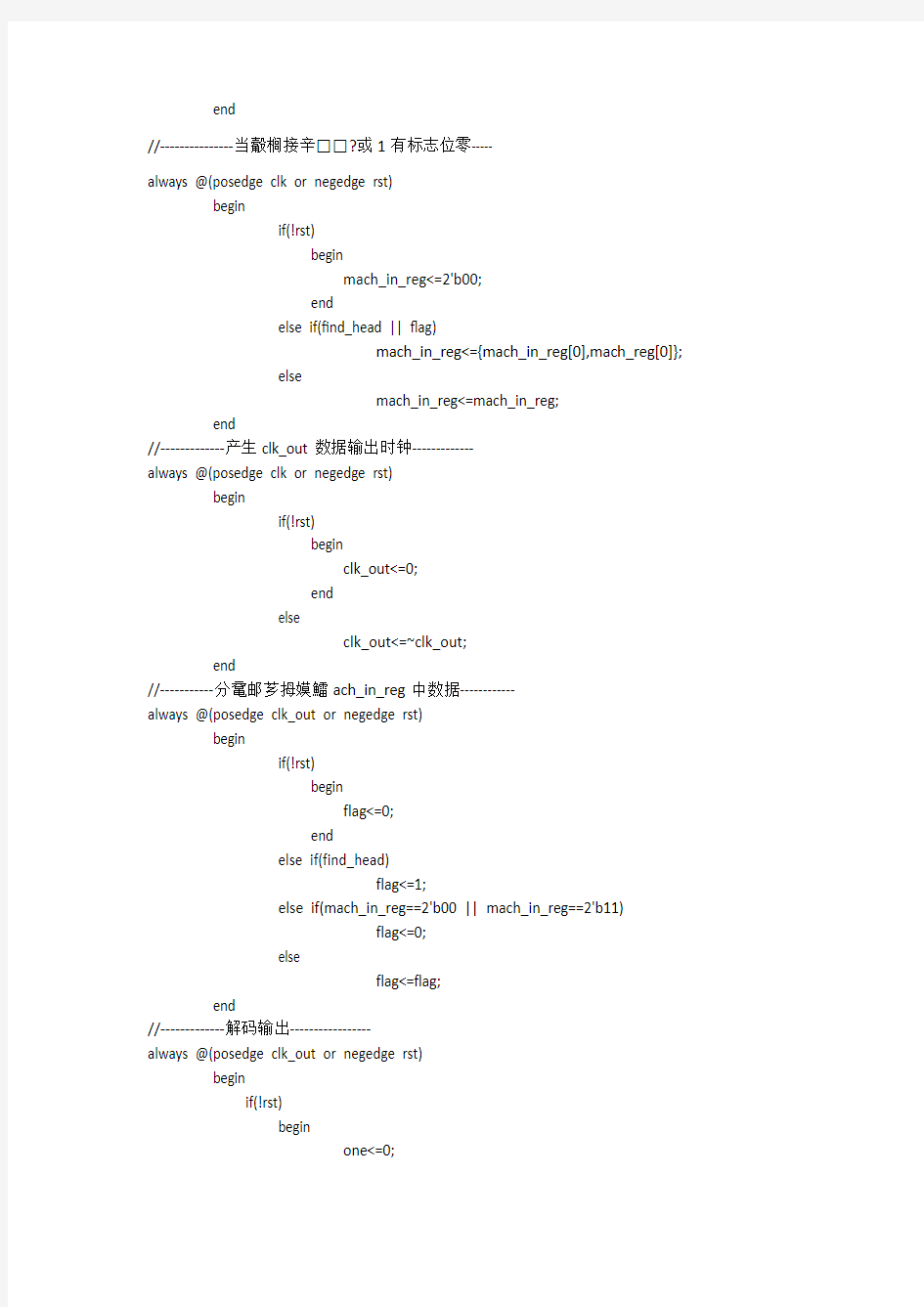

//---------------当觳榈接辛 ?或1有标志位零-----

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

mach_in_reg<=2'b00;

end

else if(find_head || flag)

mach_in_reg<={mach_in_reg[0],mach_reg[0]};

else

mach_in_reg<=mach_in_reg;

end

//-------------产生clk_out数据输出时钟-------------

always @(posedge clk or negedge rst)

begin

if(!rst)

begin

clk_out<=0;

end

else

clk_out<=~clk_out;

end

//-----------分鼋邮芗拇嫫鱩ach_in_reg中数据------------

always @(posedge clk_out or negedge rst)

begin

if(!rst)

begin

flag<=0;

end

else if(find_head)

flag<=1;

else if(mach_in_reg==2'b00 || mach_in_reg==2'b11)

flag<=0;

else

flag<=flag;

end

//-------------解码输出-----------------

always @(posedge clk_out or negedge rst)

begin

if(!rst)

begin

one<=0;

zero<=0;

// decode_out<=0;

fifo_wr<=0;

end

else if(flag && mach_in_reg==2'b10)

begin

// decode_out<=1;

one<=1;

zero<=0;

fifo_wr<=1;

end

else if(flag && mach_in_reg==2'b01)

begin

one<=0;

zero<=1;

// decode_out<=0;

fifo_wr<=1;

end

else

begin

one<=0;

zero<=0;

// decode_out<=0;

fifo_wr<=0;

end

end

assign decode_out=(one && flag)?1:((zero && flag)?0:'bz); endmodule