抗ESD的VDMOS器件的研制

抗ESD的VDMOS器件的研制

刘宗贺

(深圳深爱半导体股份有限公司广东深圳 518118)

摘 要: ESD是导致VDMOS器件损坏的一个重要原因,通过分析VDMOS器件ESD损坏的机理,提出在VDMOS器件的内部制造ESD保护单元,为节约芯片面积,提出在VDMOS器件的栅压焊区位置制造连接栅源的齐纳二极管,通过串联齐纳二极管达到ESD保护单元一定的耐压要求。并介绍利用多晶硅来制造栅源之间的ESD保护单元,工艺简单容易实现又节约成本。

关键词: VDMOS;ESD保护;串联齐纳二极管

中图分类号:TN386 文献标识码:A 文章编号:1671-7597(2011)0720058-02

1 VDMOS器件的静电损坏现象以及影响区S(图中N+扩散区与P+扩散区所形成的区域),漏区D(图中的N-外延,

N+衬底与背面电极所构成的区域)以及沟道区(图中PBODY扩散区与N+扩ESD(Electrostatic Discharge)即静电释放,两个带不同静电的物

散区以及N-外延层所形成的区域)形成电流通路上的隔离,这样就形成了体通过直接接触或在静电电场的作用下,两物体的静电电荷发生位移,当

一个以多晶硅栅和下面的外延层扩散区为电极以中间的薄栅氧化层为介电静电电场达到一定能量时,两物体之间的介质就会被击穿而产生放电,此

质的MOS电容结构,当该结构器件在生产制造,包装运输以及使用时有静时就发生了ESD事件。

电荷产生时,静电荷就会积累在多晶硅栅上,积累到一定程度或在一定的在VDMOS器件中的ESD现象,是在器件的制造、运输、使用过程中,芯

外界条件下就会发生ESD事件,造成器件损坏。

片的外部环境或者内部结构会积累一定量的电荷,这些积累的电荷会瞬间

通过芯片的管脚进入器件的内部。瞬间通过器件内部的峰值电流可以达到

数安培,这个瞬态大电流值足以将芯片烧毁(图1),这就是VDMOS器件的

ESD损坏现象。

图1 分离器件中的ESD损坏图片

ESD是EOS(电过应力)中的一种,是引起VDMOS器件失效的最主要的可靠性问题之一。一般因ESD损坏,造成电子元器件突发性完全失效的只占10%,表现为短路、开路以及参数的严重退化,器件完全丧失了其功能,突发性完全失效的有如下例子:MOS结构氧化层被击穿,PN结严重漏电、二次击穿、硅片局部区域熔化、铝条损伤和铝条熔断;另外,因ESD危害的器件约有90%不会完全失效,而是潜伏下来,发生潜在性失效,即ESD在器件中造成的损伤是一定的,器件内部会出现某种程度的轻微损伤,不足以引起器件立即完全失效,器件的功能仍满足要求,但若这种元器件继续带伤工作,随着ESD次数的增加,积累效应愈加明显,其损伤程度逐渐加剧,最终必将导致完全失效,潜在性失效一般要在客户使用过程中才能发现,相比突发性的完全失效,潜在性失效造成的损失更大[1-2]。

2 VDMOS器件的ESD损伤机理

要研究VDMOS器件静电损坏机理,首先需要从VDMOS器件的结构入手,图2给出了常用的N沟道增强型的VDMOS晶体管的纵向剖面结构示意图,该VDMOS 是由多个单元图形并联而成的集成器件,多晶硅栅网格将各单元的栅极相连,底部由N+衬底与背面电极作为公用的漏极D[3]。在多晶硅栅的下方是一层薄薄的栅氧化层,栅氧化层的存在使多晶硅栅G与VDMOS的源

图2 N沟道增强型VDMOS器件结构

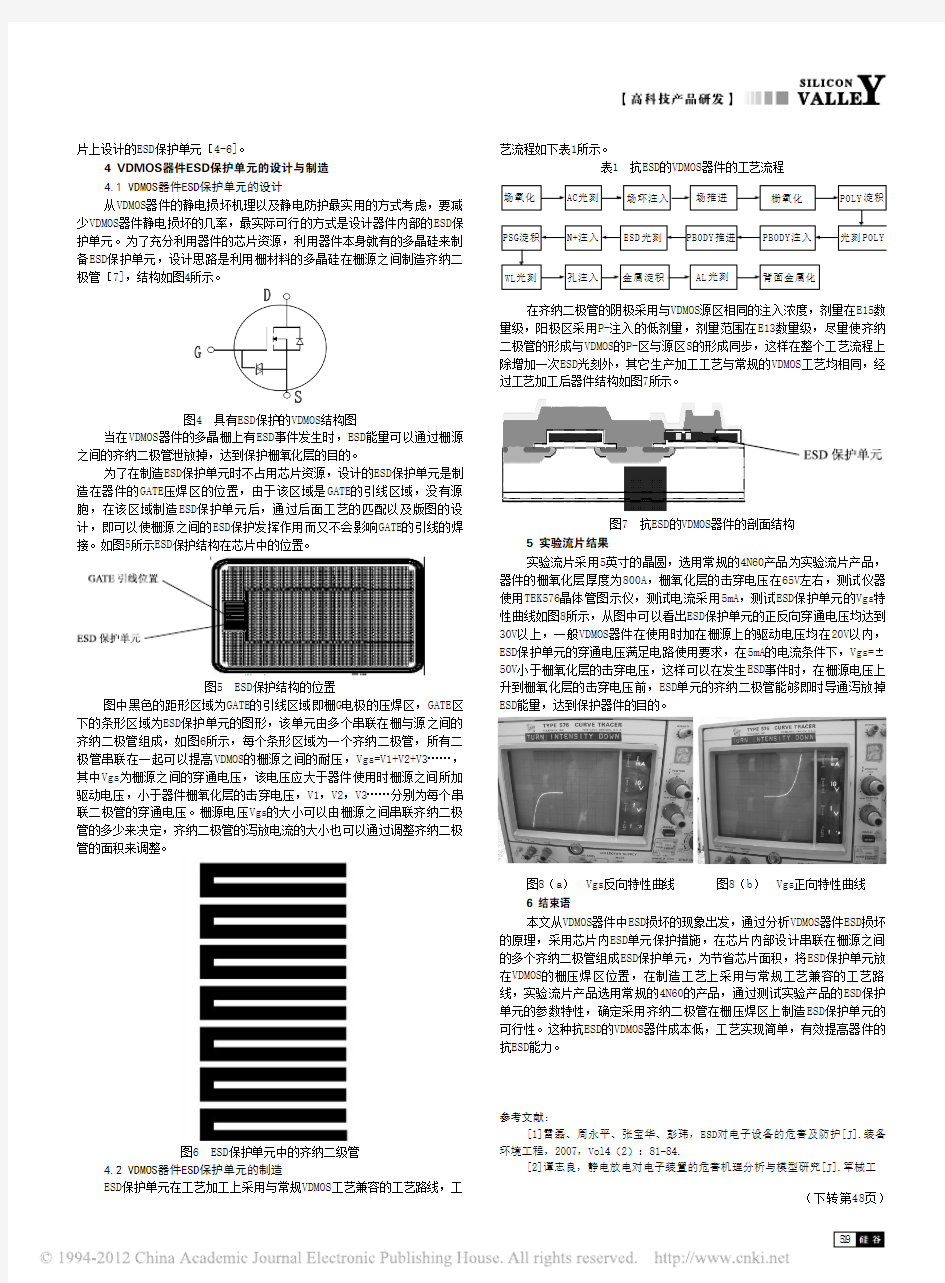

一般VDMOS器件的栅氧化层厚度都在几百到一千埃左右,所能承受的理论击穿电压只有几十到一百伏;而在电子行业中最常见的静电模式为HBM模式,它对应于一个已经积累了静电后的直立的人,用手指触摸一个与地相连的器件时所触发的静电放电现象,其中等效人体电阻R1=1500Ω,等效人体电容C1=100pF,通常商用集成电路要求至少能够承受2kV的HBM静电放电电压,2kV的HBM静电放电电压能够激发峰值为1.3A左右的电流,如图3所示,高电压与大电流很容易造成薄薄的柵氧化层击穿或损伤,带来器件特性的恶化或失去功能。

图3 2000V电压下的人体模型的电流波形

3 VDMOS器件静电损伤的防护措施

ESD防护问题一般主要从两个方面考虑,一是预防ESD事件的发生,主要措施包括接地,静电屏蔽,离子中和,控制环境温湿度等措施;第二是采取器件上的ESD保护设计,其中ESD保护设计又包括芯片外的ESD保护单元的设计与芯片上的ESD保护单元的设计,由于芯片外ESD保护器件占用较多的系统资源或板级资源,并且对于芯片使用者来说,需要单独购买片外的ESD保护器件,在成本上是一种压力,因此,ESD

保护结构主要指的是芯

片上设计的ESD 保护单元[4-6]。

艺流程如下表1所示。

表1 抗ESD 的VDMOS 器件的工艺流程

4 VDMOS器件ESD保护单元的设计与制造

4.1 VDMOS器件ESD保护单元的设计

从VDMOS 器件的静电损坏机理以及静电防护最实用的方式考虑,要减少VDMOS 器件静电损坏的几率,最实际可行的方式是设计器件内部的ESD 保护单元。为了充分利用器件的芯片资源,利用器件本身就有的多晶硅来制备ESD 保护单元,设计思路是利用栅材料的多晶硅在栅源之间制造齐纳二极管[7],结构如图4所示。

在齐纳二极管的阴极采用与VDMOS 源区相同的注入浓度,剂量在E15数量级,阳极区采用P-注入的低剂量,剂量范围在E13数量级,尽量使齐纳二极管的形成与VDMOS 的P-区与源区S 的形成同步,这样在整个工艺流程上除增加一次ESD 光刻外,其它生产加工工艺与常规的VDMOS 工艺均相同,经过工艺加工后器件结构如图7所示。

图4 具有ESD 保护的VDMOS 结构图

当在VDMOS 器件的多晶栅上有ESD 事件发生时,ESD 能量可以通过栅源之间的齐纳二极管泄放掉,达到保护栅氧化层的目的。

为了在制造ESD 保护单元时不占用芯片资源,设计的ESD 保护单元是制造在器件的GATE 压焊区的位置,由于该区域是GATE 的引线区域,没有源胞,在该区域制造ESD 保护单元后,通过后面工艺的匹配以及版图的设 图7 抗ESD 的VDMOS 器件的剖面结构计,即可以使栅源之间的ESD 保护发挥作用而又不会影响GATE 的引线的焊 5 实验流片结果

接。如图5所示ESD 保护结构在芯片中的位置。

实验流片采用5英寸的晶圆,选用常规的4N60产品为实验流片产品,器件的栅氧化层厚度为800A ,栅氧化层的击穿电压在65V 左右,测试仪器使用TEK576晶体管图示仪,测试电流采用5mA ,测试ESD 保护单元的Vgs 特性曲线如图8所示,从图中可以看出ESD 保护单元的正反向穿通电压均达到30V 以上,一般VDMOS 器件在使用时加在栅源上的驱动电压均在20V 以内,ESD 保护单元的穿通电压满足电路使用要求,在5mA 的电流条件下,Vgs=±50V 小于栅氧化层的击穿电压,这样可以在发生ESD 事件时,在栅源电压上图5 ESD 保护结构的位置

升到栅氧化层的击穿电压前,ESD 单元的齐纳二极管能够即时导通泻放掉图中黑色的距形区域为GATE 的引线区域即栅G 电极的压焊区,GATE 区ESD 能量,达到保护器件的目的。

下的条形区域为ESD 保护单元的图形,该单元由多个串联在栅与源之间的齐纳二极管组成,如图6所示,每个条形区域为一个齐纳二极管,所有二极管串联在一起可以提高VDMOS 的栅源之间的耐压,Vgs=V1+V2+V3……,其中Vgs 为栅源之间的穿通电压,该电压应大于器件使用时栅源之间所加驱动电压,小于器件栅氧化层的击穿电压,V1,V2,V3……分别为每个串联二极管的穿通电压。栅源电压Vgs 的大小可以由栅源之间串联齐纳二极管的多少来决定,齐纳二极管的泻放电流的大小也可以通过调整齐纳二极管的面积来调整。

图8(a ) Vgs 反向特性曲线 图8(b ) Vgs 正向特性曲线6 结束语

本文从VDMOS 器件中ESD 损坏的现象出发,通过分析VDMOS 器件ESD 损坏的原理,采用芯片内ESD 单元保护措施,在芯片内部设计串联在栅源之间的多个齐纳二极管组成ESD 保护单元,为节省芯片面积,将ESD 保护单元放在VDMOS 的栅压焊区位置,在制造工艺上采用与常规工艺兼容的工艺路线,实验流片产品选用常规的4N60的产品,通过测试实验产品的ESD 保护单元的参数特性,确定采用齐纳二极管在栅压焊区上制造ESD 保护单元的可行性。这种抗ESD 的VDMOS 器件成本低,工艺实现简单,有效提高器件的抗ESD 能力。

参考文献:

[1]雷磊、周永平、张宝华、彭玮,ESD 对电子设备的危害及防护[J].装备环境工程,2007,Vol4(2):81-84.

图6 ESD 保护单元中的齐纳二级管

[2]谭志良,静电放电对电子装置的危害机理分析与模型研究[J].军械工

4.2 VDMOS器件ESD保护单元的制造

ESD 保护单元在工艺加工上采用与常规VDMOS

工艺兼容的工艺路线,工

(下转第48页)

I P a d用户W i F i数据流量远超其他移动设备

北京时间6月24日凌晨消息,根据云普遍的上网工具。

计算网络提供商Meraki周四公布的报告显根据Meraki的追踪的WiFi接入点的示,iPad平均每月使用的WiFi数据流量是记录显示,目前苹果的iOS和Android系统iPhone、iPod或者Android系列设备所使是使用量最大的移动设备平台,占据了用的流量的4倍。

所有接入到WiFi网络的设备中的58%,而通过今年上半年与2010年上半年同在一年之前,这一数字仅为33%。其中接期的数据使用情况进行进行比较,入WiFi网络的iOS设备的使用比例从去年Meraki也发现使用WiFi的移动设备数量的32%上升到了今年的47%,而接入已超过PC,移动设备已经成为了使用最

WiFi网络的Android移动设备的使用比例IDC便已经根据多方数据的汇总结果预则从2010年的1%上升到了今年的11%。

测,到2012年移动设备的出货量将会最与此相对应的是,接入WiFi网络的终超过个人电脑的出货量。IDC预测移动电子设备中,使用Windows和Mac OS操设备的出货量在2012年将达到4.62亿台,作系统的电子设备的使用比例从去年的而PC出货量将仅为4.48亿台。

63%下降至了今年的36%。特别是使用Meraki指出这份报告是针对全美国Windows的PC的使用比例更是从去年的接入通用、公共和教育WiFi网络的超过42%暴跌至今年的23%,而苹果Mac的使10万台设备进行使用情况调查,并对用比例则从去年的21%下降至今年13%。

2011年上半年和2010年上半年同期,这随着广大用户对移动设备的需求不些设备的接入用途和操作系统的情况进断增长,这一统计结果的变化并不出乎行比较和分析得出的。

人们的意料。去年12月,市场调研机构

新浪科技

触屏化将终结鼠标时代

当鼠标被鼠标时代的霸主微软公司变。

置于“兼容”地位,人们终于可以大方从开始界面的应用商店“Store”的地承认,快到了和鼠标说再见的时候链接看,微软将会推出应用程序商店。

了。

现在判定Win8是否成功还为时过在日前举行的《华尔街日报》D9数早,但是有一点现在已经可以确认,触字大会上,微软展示了新一代操作系统屏化已是大势所趋。联想ThinkPad副总Windows8(下称Win8)。这个操作系统裁PeterHortensius就说:“Win8系统的触最吸引眼球的地方在于,它可以应用于屏化将开创PC的一个新世界。”而苹果触摸型平板电脑。

近日将推广的新操作系统MacOSXLion也在Win8界面上,所有的程序都以卡势必会加快平板电脑的普及。美国一些片的形式展示,并可以通过触摸点击进科技网站更是预测,微软将在年内推出行操作。用户也可以在应用程序之间自自己的平板电脑。

击左边空白处则可以切换正在运行的应由转换,用手指点击屏幕右部,会展开用程序。Win8中的IE10浏览器率先被改诸如“搜索”、“分享”等菜单,而敲

《中华工商时报》造成触摸应用,但Office系列还维持

不

程学院学报,1994,Vol.6(4):265-269.

[5]陶剑磊、培源、王家辑,由版图引起的CMOS ESD 保护电路失效的分析[3]王英、何杞鑫、方绍华,高压功率VDMOS 管的设计研制[J].电子器件,[J].半导体技术,2007,Vol.32,(11):1003-1006.

2006,Vol.29(1):6-8.

[6]Ming-Dou Ker and Kun-Hsien Lin. ESD Protection Design for [4]Yu-Da Shiu1, Bo-Shih Huang1, and Ming-Dou Ker. CMOS Power Mixed-Voltage I/[J].IEEE ,2005,493-498.

Amplifier with ESD Protection Design Merged in Matching [7]孙郯,ESD 保护器件在多晶硅上的实现[J].信息技术,2008(12):Network[J].IEEE ,2007:825-828.

74-76.

(上接第59页)