1642年 计算机雏形——Pascaline(加法器)

1642年计算机雏形——Pascaline(加法器)回目录

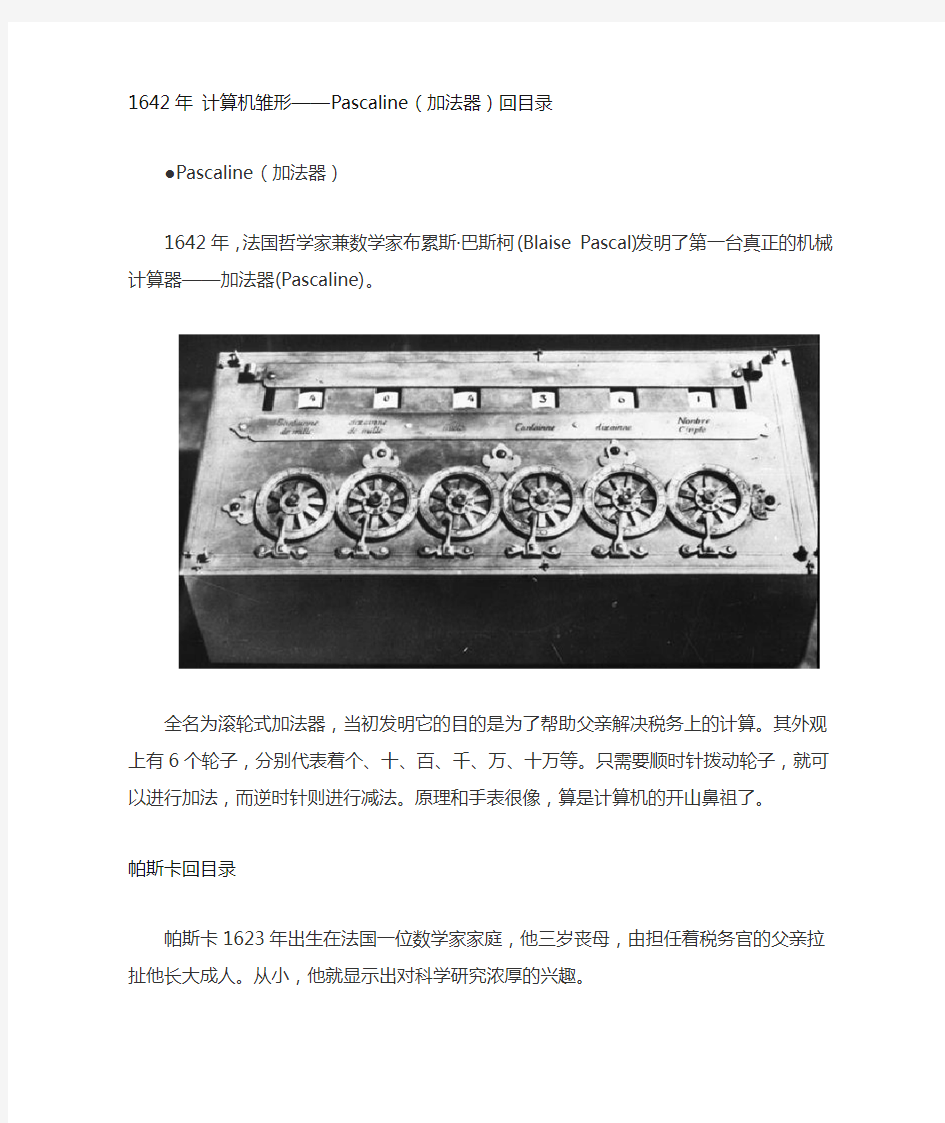

●Pascaline(加法器)

1642年,法国哲学家兼数学家布累斯·巴斯柯(Blaise Pascal)发明了第一台真正的机械计算器——加法器(Pascaline)。

全名为滚轮式加法器,当初发明它的目的是为了帮助父亲解决税务上的计算。其外观上有6个轮子,分别代表着个、十、百、千、万、十万等。只需要顺时针拨动轮子,就可以进行加法,而逆时针则进行减法。原理和手表很像,算是计算机的开山鼻祖了。

帕斯卡回目录

帕斯卡1623年出生在法国一位数学家家庭,他三岁丧母,由担任着税务官的父亲拉扯他长大成人。从小,他就显示出对科学研究浓厚的兴趣。

少年帕斯卡对他的父亲一往情深,他每天都看着年迈的父亲费力地计算税率税款,很想帮助做点事,可又怕父亲不放心。于是,未来的科学家想到了为父亲制做一台可以计算税款的机器。19岁那年,他发明了人类有史以来第一台机械计算机。

帕斯卡的计算机是一种系列齿轮组成的装置,外形像一个长方盒子,用儿童玩具那种钥匙旋紧发条后才能转动,只能够做加法和减法。然而,即使只做加法,也有个“逢十进一”的进位问题。聪明的帕斯卡采用了一种小爪子式的棘轮装置。当定位齿轮朝9转动时,棘爪便逐渐升高;?一旦齿轮转到0,棘爪就“咔嚓”一声跌落下来,推动十位数的齿轮前进一档。

Pascaline calculating machine of Blaise Pascal (1623-62),

帕斯卡发明成功后,一连制作了50台这种被人称为“帕斯卡加法器”的计算机,至少现在还有5台保存着。?比如,在法国巴黎工艺学校、英国伦敦科学博物馆都可以看到帕斯卡计算机原型。据说在中国的故宫博物院,也保存着两台铜制的复制品,是当年外国人送给慈僖太后的礼品,“老佛爷”哪里懂得它的奥妙,只把它当成了西方的洋玩具,藏在深宫里面。

帕斯卡是真正的天才,他在诸多领域内都有建树。后人在介绍他时,说他是数学家、物理学家、哲学家、流体动力学家和概率论的创始人。凡是学过物理的人都知道一个关于液体压强性质的“帕斯卡定律”,这个定律就是他的伟大发现并以他的名字命名的。他甚至还是文学家,其文笔优美的散文在法国极负盛名。可惜,长期从事艰苦的研究损害了他的健康,1662年英年早逝,死时年仅39岁。他留给了世人一句至理名言:“人好比是脆弱的芦苇,但是他又是有思想的芦苇。”

详解回目录

Blaise Pascal invented the second mechanical calculator, called alternatively the Pascalina or the Arithmetique, in 1645, the first being that of Wilhelm Schickard in 1623.

A Pascaline, signed by Pascal in 1652

Pascal began to work on his calculator in 1642, when he was only 19 years old. He had been assisting his father, who worked as a tax commissioner, and sought to produce a device which could reduce some of his workload. Pascal received a Royal Privilege in 1649 that granted him exclusive rights to make and sell calculating machines in France. By 1652 Pascal claimed to have produced some fifty prototypes and sold just over a dozen machines, but the cost and complexity of the Pascaline—combined with the fact that it could only add and subtract, and the latter with difficulty—was a barrier to further sales, and production ceased in that year. By that time Pascal had moved on to other pursuits, initially the study of atmospheric pressure, and later philosophy.

Pascaline made for French currency. The least significant denominations, sols and

deniers, are on the right.

Pascalines came in both decimal and non-decimal varieties, both of which exist in museums today. The contemporary French currency system was similar to the Imperial pounds ("livres"), shillings ("sols") and pence ("deniers") in use in Britain until the 1970s.

In 1799 France changed to a metric system, by which time Pascal's basic design had inspired other craftsmen, although with a similar lack of commercial success. Child prodigy Gottfried Wilhelm Leibniz devised a competing design, the Stepped Reckoner, in 1672 which could perform addition, subtraction, multiplication and division; Leibniz struggled for forty years to perfect his design and produce sufficiently reliable machines. Calculating machines did not become commercially viable until the early 19th century, when Charles Xavier Thomas de Colmar's Arithmometer, itself using the key break through of Leibniz's design, was commercially successful.

The initial prototype of the Pascaline had only a few dials, whilst later production variants had eight dials, the latter being able to deal with numbers up to 9,999,999.

View through back of calculator above showing wheels.

The calculator had spoked metal wheel dials, with the digit 0 through 9 displayed around the circumference of each wheel. To input a digit, the user placed a stylus in the corresponding space between the spokes, and turned the dial until a metal stop at the bottom was reached, similar to the way a rotary telephone dial is used. This would display the number in the boxes at the top of the calculator. Then, one would simply redial the second number to be added, causing the sum of both numbers to appear in boxes at the top. Since the gears of the calculator only rotated in one direction, negative numbers could not be directly summed. To subtract one number from another, the method of nines' complements was used. To help the user, when a number was entered its nines' complement appeared in a box above the box containing the original value entered.

图说回目录

16位超前加法器实验报告

16位超前加法器设计实验 一、实验分析: 四位超前进位加法器HDL程序: module add4_head ( a, b, ci, s, pp, gg); input[3:0] a; input[3:0] b; input ci; output[3:0] s; output pp; output gg; wire[3:0] p; wire[3:0] g; wire[2:0] c; assign p[0] = a[0] ^ b[0]; assign p[1] = a[1] ^ b[1]; assign p[2] = a[2] ^ b[2]; assign p[3] = a[3] ^ b[3]; assign g[0] = a[0] & b[0]; assign g[1] = a[1] & b[1]; assign g[2] = a[2] & b[2]; assign g[3] = a[3] & b[3]; assign c[0] = (p[0] & ci) | g[0]; assign c[1] = (p[1] & c[0]) | g[1]; assign c[2] = (p[2] & c[1]) | g[2]; assign pp = p[3] & p[2] & p[1] & p[0]; assign gg = g[3] | (p[3] & (g[2] | p[2] & (g[1] | p[1] & g[0]))); assign s[0] = p[0] ^ ci; assign s[1] = p[1] ^ c[0]; assign s[2] = p[2] ^ c[1]; assign s[3] = p[3] ^ c[2]; endmodule p表示进位否决信号(pass),如果p为0就否决调前一级的进位输入。否决的意思就是即使前一级有进位,本级也不会向后一级产生进位输出。 g表示进位产生信号(generate),如果g为1就表示一定会向后一级产生进位输出。p[n] = a[n] ^ b[n]这句话的意思是说,当a=1,b=0或a=0,b=1时前一级的进位输入信号不能否决。这样就有个问题了,即当a=1,b=1时前一级的进位输入信号也不能否决啊,怎么没有体现出来?其实当a=1,b=1时产生了进位产生信号g,它的优先级高于p信号,就忽略了p信号,直接产生了向后一级产生进位输出,是没有逻辑错误的。 g[n] = a[n] & b[n] 这句话的意思是说,如果a=1,b=1时就直接向后一级产生进位输出信号,而不用考虑其它的任何因素。

微机原理习题及答案

一、选择 1、在微型计算机中,微处理器的主要功能是进行( )。 D A、算术运算 B、逻辑运算 C、算术、逻辑运算 D、算术、逻辑运算及全机的控制 2、Pentium I属于()位CPU C A、16 B、8 C、32 D、64 3、Intel 8086属于()位CPU A A、16 B、8 C、32 D、64 4、CPU与I/O设备间传送的信号通常有( ) D A、控制信息 B、状态信息 C、数据信息 D、以上三种都有 5、存储器用来存放计算机系统工作时所需要的信息,即( )。 D A、程序 B、数据 C、技术资料 D、程序和数据 6、运算器的核心部件是( )。 D A、加法器 B、累加寄存器 C、多路开关 D、算逻运算单元 二、填空 1、内存可分为2大类:随机存储器RAM 和 2、数据总线是向的,地址总线是向的。 3、计算机的五大部件是:、、、、输出设备 4、总线可分为三类:、、 5、存储程序工作原理最先由提出 6、在计算机内部,一切信息的存取、处理和传送都是以形式进行的。 1、只读存储器ROM 2、双、单 3、运算器、控制器、存储器、输入设备 4、地址总线、数据总线、控制总线 5、冯·诺依曼 6、二进制 三、简答 1、冯·诺依曼型计算机的特点是什么? (1).以二进制表示指令和数据 (2).程序和数据存放在存储器中,从存储器中取指令并执行 (3).由运算器、控制器、存储器、输入设备、输出设备构成计算机硬件系统。 一、选择 1、在机器数______中,零的表示形式是唯一的()。BD A、原码 B、补码 C、反码 D、移码 2、计算机内部表示带符号整数通常采用()。C A、原码 B、反码 C、补码 D、移码

4位全加器实验报告

四位全加器 11微电子黄跃21 【实验目的】 采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。 【实验内容】 加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。 实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0). 【实验原理】

表2 全加器逻辑功能真值表 图4 全加器方框图 图5 全加器原理图 多位全加器连接可以是逐位进位,也可以是超前进位。逐位进位也称串行进位,其逻辑电路简单,但速度也较低。 四位全加器 如图9所示,四位全加器是由半加器和一位全加器组建而成: 图9 四位全加器原理图 【实验步骤】 (1)建立新工程项目: 打开modelsim软件,进入集成开发环境,点击File→New project建立一

个工程项目adder_4bit。 建立文本编辑文件: 点击File→New在该项目下新建Verilog源程序文件 并且输入源程序。 (2)编译和仿真工程项目: 在verilog主页面下,选择Compile— Compile All或点击工具栏上的按钮启动编译,直到project出现status栏全勾,即可进行仿真。 选择simulate - start simulate或点击工具栏上的按钮开始仿真,在跳出来的 start simulate框中选择work-test_adder_4bit测试模块,同时撤销Enable Optimisim前的勾,之后选择ok。 在sim-default框内右击选择test_adder_4bit,选择Add Wave,然后选择simulate-run-runall,观察波形,得出结论,仿真结束。 四位全加器 1、原理图设计 如图9所示,四位全加器是由半加器和一位全加器组建而成: 图9 四位全加器原理图 【仿真和测试结果】 下图为四位全加器的仿真图:

32位浮点加法器设计

32位浮点加法器设计 苦行僧宫城 摘要:运算器的浮点数能够提供较大的表示精度和较大的动态表示范围,浮点运算已成为现代计算程序中不可缺少的部分。浮点加法运算是浮点运算中使用频率最高的运算。因此,浮点加法器的性能影响着整个CPU的浮点处理能力。文中基于浮点加法的原理,采用Verilog硬件描述语言设计32位单精度浮点数加法器,并用modelsim对浮点加法器进行仿真分析,从而验证设计的正确性和可行性。 关键词:浮点运算浮点加法器 Verilog硬件描述语言 Studying on Relation ofTechnology and Civilization 苦行僧宫城 (School of Mechatronic Engineering and Automation, Shanghai University, Shanghai , China) Abstract: The floating-point arithmetic provides greater precision and greater dynamic representation indication range, with floating point calculations have become an indispensable part of the program. Floating-point adder is the most frequently used floating point arithmetic. Therefore, the performance of floating point adder affecting the entire CPU floating point processing capabilities. In this paper the principle-based floating-point addition, Verilog hardware description language design 32-bit single-precision floating-point adder and floating-point adder using modelsim simulation analysis in order to verify the correctness and feasibility of the desig 小组成员及任务分配: 1浮点数和浮点运算 1.1浮点数 浮点数是属于有理数中某特定子集的数的数字表示,在计算机中用以近似表示任意某个实数。具体的说,这个实数由一个整数或定点数(即尾数)乘以某个基数(计算机中通常是2)的整数次幂得到,这种表示方法类似于基数为10的科学记数法。 1.2浮点格式 常用的浮点格式为IEEE 754 标准,IEEE 754 标准有单精度浮点数、双精度浮点数和扩展双精度浮点数3 种,单精度为32 位,双精度为64 位,扩展双精度为80 位以上,位数越多精度越高,表示范围也越大。在通常的数字信号处理应用中,单精度浮点数已经足够用了,本文将以它为例来设计快速浮点加法器。单精度浮点数如图1所示。 其中s为符号位,s为1 时表示负数,s为0时表示正数;e为指数,取值范围为[1,254],0和255表示特殊值;f有22位,再加上小数点左边一位隐含的1总共23位构成尾数部分。 1.3 浮点运算 浮点加法运算由一些单独的操作组成。在规格化的表示中,对于基为2的尾数的第1个非0位的1是隐含的,因此,可以通过不存储这一位而使表示数的数目增加。但在进行运算时不能忽略。浮点加法一般要用以下步骤完成: a) 指数相减:将2个指数化为相同值,通过比较2个指数的大小求出指数差的绝对值ΔE。 b) 对阶移位: 将指数较小的操作数的尾数右移ΔE位。 c) 尾数加减:对完成对阶移位后的操作数进行加减运算。

四位超前进位加法器原理

超前进位加法器原理 74283为4位超前进位加法器,不同于普通串行进位加法器由低到高逐级进位,超前进位加法器所有位数的进位大多数情况下同时产生,运算速度快,电路结构复杂。其管脚如图1所示: 图1 74283管脚图 其真值表如下所示: 表1 4位超前进位加法器真值表

由全加器的真值表可得S i 和C i 的逻辑表达式: 定义两个中间变量G i 和P i : 当A i =B i =1时,G i =1,由C i 的表达式可得C i =1,即产生进位,所以G i 称为产生量变。若P i =1,则A i ·B i =0,C i =C i-1 ,即P i =1时,低位的进位能传 送到高位的进位输出端,故P i 称为传输变量,这两个变量都与进位信号无关。 将G i 和P i 代入S i 和C i 得: 进而可得各位进位信号的逻辑表达如下:

根据逻辑表达式做出电路图如下: 逻辑功能图中有2输入异或门,2输入与门,3输入与门,4输入与门,2输入或门,3输入或门,4输入或门,其转化成CMOS晶体管图如下:

电路网表如下: *xor 2 .subckt xor2 a b c d f mxorpa 1 a vdd vdd pmos l=2 w=8 mxorpb f d 1 vdd pmos l=2 w=8 mxorpc 2 b vdd vdd pmos l=2 w=8 mxorpd f c 2 vdd pmos l=2 w=8 mxorna f a 3 0 nmos l=2 w=4 mxornb 3 b 0 0 nmos l=2 w=4 mxornc f c 4 0 nmos l=2 w=4 mxornd 4 d 0 0 nmos l=2 w=4 .ends xor2 *and2 .subckt and2 a b f mandpa f a vdd vdd pmos l=2 w=4 mandpb f b vdd vdd pmos l=2 w=4 mandna f a 1 0 nmos l=2 w=4 mandnb 1 b 0 0 nmos l=2 w=4 .ends and2 *and3 .subckt and3 a b c f mandpa f a vdd vdd pmos l=2 w=4 mandpb f b vdd vdd pmos l=2 w=4 mandpc f c vdd vdd pmos l=2 w=4 mandna f a 1 0 nmos l=2 w=6 mandnb 1 b 2 0 nmos l=2 w=6 mandnc 2 c 0 0 nmos l=2 w=6 .ends and3 *and4 .subckt and4 a b c d f mandpa f a vdd vdd pmos l=2 w=4 mandpb f b vdd vdd pmos l=2 w=4 mandpc f c vdd vdd pmos l=2 w=4 mandpd f d vdd vdd pmos l=2 w=4 mandna f a 1 0 nmos l=2 w=8 mandnb 1 b 2 0 nmos l=2 w=8 mandnc 2 c 3 0 nmos l=2 w=8 mandnd 3 d 0 0 nmos l=2 w=8 .ends and4

实验一四位串行进位加法器的设计实验报告

实验一四位串行进位加法器的设计 一、实验目的 1.理解一位全加器的工作原理 2.掌握串行进位加法器的逻辑原理 3.进一步熟悉Quartus软件的使用,了解设计的全过程, 二、实验内容 1.采用VHDL语言设计四位串行进位的加法器 2.采用画原理图的方法设计四位串行进位加法器 三、实验步骤 1、使用VHDL语言设计 1.打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后保存、编译。打开File—>New—>Other File—>Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。从Assignments—>Settings—>Simulator Settings —>Functional 然后Processing—>Generate Functional Simnlation Netlist —>确定。选择Start Simulation保存最后的波形图,打开File —>close关闭工程。 底层文件: LIBRARY ieee;

USE fadder IS PORT ( a, b,cin : IN STD_LOGIC; s, co : OUT STD_LOGIC ); END fadder; ARCHITECTURE arc1 OF fadder IS BEGIN s<=a xor b xor cin; co<=((a xor b)and cin)or(a and b); END arc1; 顶层文件: LIBRARY ieee; USE adder4 IS PORT ( c0: IN STD_LOGIC; a,b : IN STD_LOGIC_VECTOR(3 DOWNTO 0); s : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); c4 : OUT STD_LOGIC );

基于流水线结构的浮点加法器IP核设计

万方数据

陋的论文得到两院院士关注l软件时空 后选择其尾数进入右移模块.如图2a所示。该部分的功能是使移部件和指数修止部件分别进行左移操作和指数修止,并最后两个数的指数位相同.以便进行尾数部分的加法运算。输出整个浮点加法运算的结果。指数修正部件在收到移位位数图2a中,E1、E2分别为两操作数的指数部分,M1、M2为对信号后。会将较大的指数Ex减去移位位数作为最后的指数输应的尾数部分,Ex为两指数中较大的一个指数,Rm为尾数右出。该两部分如图3b所示。 移位数,rsa为需要进行右移操作的尾数,adl为进入加法器的图中lnum为前导判断出的左移位数。inan为左移后的尾另一个操作数的尾数。数部分.Exp为修正后的指数部分;V表示指数溢出,UF表示指3.3右移部分及指数加1部分数下溢.它们用于标志位。 该部分是流水线的第二级。需要右移的尾数在进入右移网络后右移。在尾数相加时有可能会出现溢出的情况,因此需要对在第一级中输出的指数加“l”操作.其结果作为尾数溢出时输出的指数.gapExl。Ex_v表示在Ex加“l”时,指数溢出,也就是浮点数相加时上溢的情况。该部分如图2b所示。 毕南串 ●thlhh,棚 (a)(b) 图2指数对阶及右移网络 3.4加法部件 加法部件的延时向来都在浮点加法器中起关键的作用。此时,尾数部分的加法就可以按照定点数来处理r。定点加法器的常用算法中有行波进位(RCA),超前进位(CLA),和选择进位(CSA)算法。行波进位结构简单,硬件开销少,但进位串行逐级向前传递.在位宽较大时时延会变得难以忍受:而超前进位结构消除了进位逐级传递的效应.且各级的进位输出将同时产生,其速度也最快.但硬件开销也最大;选择进位(CSA)结构则将进位链分组并行。组间采用串行方式连接。每组有两条路径,进位输入为…0’和“l”的丽种情况,通过两条路径同时计算。一旦该组进位输入信号到来,通过多路选择器就可选择出正确的进位输出及和输出.其速度和硬件开销都介于RCA和CLA之间,而在位宽较小的情况下(如32位)时,其速度与CLA相差不大,因此本文中采用CSA结构。该部分如图3a所示。在Dc综合后,该部件的延时为1.56ns.为整个浮点加法器中的关键路径。啦槎 (a)(b) 图3加法器及尾数规格化 3.5规格化部件及指数修正部件 规格化部件和指数修正部件分为两级流水线,第四级流水线主要产生前导…0’或…1’的判断.经过编码产生移位位数信号。与IEEE754数据格式不同的是.在做前导判断的时候,IEEE754只需要检查第一个“l”的位置.而1'I格式是要对与符号数的相反数进行查询.其过程相对复杂,因此本文将该部分单独作为一级流水线处理。第五级流水线则将移位信号送入左 4结论 本文设计的是一种高速浮点加法器的IP软核,使用SMIC提供0.18unlCMOS丁艺单元库并采用Synopsys公司的DesignCoinpiler软件进行综合后发现。如果使用传统的加法器结构,整个设计的关键路径延时为6.3ns.其最高理论运行频率为158MHz.综合后的单元面积为65859um2。而采用本文的加法器结构、算法以及使用流水线分层后,关键路径的延时仅为1.56ns.工作频率可达500MHz以上,单元面积为66742um2。由此可见.在单元面积并未明显增加的基础上。本文方法大幅度的提高了加法器的性能。图4为使用NC—Verilog软件。采用周期为2ns的时钟仿真综合后电路的仿真波形。 本文作者创新点:对传统加法器进行5级流水线合理划分.达到设计高速浮点加法器的目的。 幽4电路仿真波形图 参考文献 『llR.VK.P{llai,D.AL—Khalili,A.J.AL—KhaliliandS.Y.A.Shah.AlowPowerApproachtoFloatingPointAdderDesignforDSPAp?-plications.JounalofVLSISignalProcessing27,195-213,2001[2]DenzilFemandes,VijayRaj,NarsimhanDoriswamy.ASynthesisToolBasedDesignofA1l1MHzCMOSFloatingPointAdderWithBuiltInTestability.IEEE1993 【31D.Narasimhan,D.Femandes,V.K.R且j_J.Dorenbosch,M.Bowden,V.S.KapoorA100MHzFPGABasedFloatingPointAdder.IEEE19930—7803—0826-3/93 【4]NEILBURGESS.NewModelsofPrefixAdderTopologies.Jour-nalofVLSISignalProcessing40,125—141,2005. 【5]TMS320C3xUser’sGuide.2004. 『61钟冬庆。嵌入式DSP处理器的体系结构设计。微计算机信息,2006,10Z:70一71. 作者简介:夏杰(1981一),男(汉),江苏江阴人,江南大学信息工程学院.硕士,研究方向为数字电路设计。 Biography:XIAJie,male(ban),Jiangyin,Jiangsu,Informationde?partmentofJiangnanUniversity,Master,MajorinDigitalCircuitDesign. (214122无锡江南大学信息工程学院)夏杰宣志斌 (214035无锡中国电子科技集团第58研究所)薛忠杰 通讯地址:(214122无锡江南大学信息工程学院)夏杰 (收稿日期:2008.7.25)(修稿日期:2008.9.15)(多目自控嗣邮局订阅号:82-946 36。元,年一193— 万方数据

西安邮电大学Verilog 四位超前进位全加器

西安邮电大学Verilog HDL实验报告(二) ——带超前进位的四位全加器 学院名称:电子工程学院 班级:电子 学生姓名: 学号:

实验题目带超前进位的四位全加器 一、实验内容 设计的一个带超前进位的四位全加器。 二、实验步骤 1、在ModelSim软件中对激励模块和设计模块进行书写和编译; 2、对编译好的模块进行仿真。 三、源代码: 1、主程序 module fulladd4(sum, c_out, a, b, c_in); output [3:0] sum; output c_out; input [3:0] a,b; input c_in; wire p0,g0,p1,g1,p2,g2,p3,g3; wire c4,c3,c2,c1; xor a1(p0,a[0],b[0]); xor a2(p1,a[1],b[1]); xor a3(p2,a[2],b[2]); xor a4(p3,a[3],b[3]); and b1(g0,a[0],b[0]); and b2(g1,a[1],b[1]); and b3(g2,a[2],b[2]); and b4(g3,a[3],b[3]); and d1(e1,p0,c_in); or f1(c1,e1,g0); and d2(e2,p1,g0);and d3(e3,p1,p0,c_in);or f2(c2,g1,e2,e3); A nd d4(e4,p2,g1);and d5(e5,p2,p1,g0);and d6(e6,p2,p1,c_in);or f3(c3,g2,e4,e5,e6); and d7(e7,p3,g2);and d8(e8,p3,p2,g1);and d9(e9,p3,p2,p1,g0);and d10(e10,p3,p2,p1,p0,c_in);or f4(c4,g3,e7,e8,e9,e10); xor m0(sum[0],p0,c_in); xor m1(sum[1],p1,c1); xor m2(sum[2],p2,c2); xor m3(sum[3],p3,c3); and n1(c_out,c4,c4); endmodule 2、激励程序 module fulladd4_tb;

微机原理加法器课程设计1

中文摘要和关键词 微机原理课程设计——8255,加法器设计2 本实验是对加法器的输入、运算、输出而进行的编程,利用了8255芯片,通过8255的A,B端口输入两个八位二进制数,经CPU运算后,由C端口输出. 通过编写相应程序用8086/8088的“OUT”指令可将8255的控制字送入其控制字寄存器所对应的地址,以达到将控制字送入8255的目的,以此来控制8255的工作方式以及A、B、C三个端口的输入,输出状态,格式化8255。本实验8255工作在方式0,即基本输入输出状态,A、B端口是输入状态,C端口是输入状态。再用相同方法可将8255的A、B两个端口的内容送入A、B两个端口。 通过A,B端口输入的两个二进制数经编程运算,然后在C口输出,通过循环语句实现两个二进制数求和的连续运算、输出. 关键字: 循环、工作方式、编程、运算、格式化

目录 课程设计任务书 1设计任务描述 1.1 设计目的 1.2 设计的要求 1.3对设计说明书撰写内容、格式、字数的要求 1.4设计完成后应提交成果的种类、数量、质量等方面的要求 1.5时间进度安排 2微机原理课程设计成绩评定表 3 设计思路 (3) 4 设计原理流程图.............………..….……..….………………….…..….…...…4~5 4.1主程序 4.2键盘扫描子程序 5 实际硬件接线图 (6) 6 源程序清单及注释…………..………..….….……………………….…………7~9 7主要元器件介绍………………………………………………………………10~12 7.1键盘 7.1.1键盘的工作原理 7.1.2键盘输入信息的过程 7.1.3键盘扫描(识别键)的过程 7.2 可编程并行接口8255A 7.2.1 8255简介 7.2.2 8255的控制字 参考文献 (13) 设计总结 (14)

加法器实验报告文档2篇

加法器实验报告文档2篇 Adder experiment report document 编订:JinTai College

加法器实验报告文档2篇 小泰温馨提示:实验报告是把实验的目的、方法、过程、结果等记录下来,经过整理,写成的书面汇报。本文档根据实验报告内容要求展开说明,具有实践指导意义,便于学习和使用,本文下载后内容可随意修改调整及打印。 本文简要目录如下:【下载该文档后使用Word打开,按住键盘Ctrl键且鼠标单击目录内容即可跳转到对应篇章】 1、篇章1:加法器实验报告文档 2、篇章2:加法器的基本原理实验报告文档 篇章1:加法器实验报告文档 【实验名称】 【目的与要求】 1.掌握1位全加器的设计 2.学会1位加法器的扩展【实验内容】 1.设计1位全加器

2.将1位全加器扩展为4位全加器 3.使4位的全加器能做加减法运算 【操作步骤】 1.1位全加器的设计 (1)写出1位全加器的真值表 (2)根据真值表写出表达式并化简 (3)画出逻辑电路 (4)用quartusII进行功能仿真,检验逻辑电路是否正确,将仿真波形截图并粘贴于此 (5)如果电路设计正确,将该电路进行封装以用于下一个环节 2.将1位全加器扩展为4位全加器 (1)用1位全加器扩展为4位的全加器,画出电路图 (2)分别用两个4位补码的正数和负数验证加法器的正确性(注意这两 个数之和必须在4位补码的数的范围内,这两个数包括符号在内共4位),用quartusII进行功能仿真并对仿真结果进行截图。

3.将4位的全加器改进为可进行4位加法和减法的运算器 (1)在4位加法器的基础上,对电路进行修改,使该电路不仅能进行加 法运算而且还能进行减法运算。画出该电路 (2)分别用两个4位补码的正数和负数验证该电路的正确性(注意两个 数之和必须在4位补码的数的范围内),用quartusII 进行功能仿真并对仿真结果进行截图。 【附录】 篇章2:加法器的基本原理实验报告文档【按住Ctrl键点此返回目录】 一、实验目的 1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。 2、学习和掌握半加器、全加器的工作和设计原理

4位超前进位加法器设计讲解学习

4位超前进位加法器 设计

、、 模拟集成电路分析与设计课程设计报告 题目4位超前进位加法器设计 学院(部)电控学院 专业电子科学与技术 班级 学生姓名 学号

前言 20世纪是IC迅速发展的时代。计算机等信息产业的飞速发展推动了集成电路(Integrated Circuit—IC)产业。大多数超大规模集成电路(Very Large Scale IC—VLSI)在日常生活中有着广泛的应用。在这些广泛应用的运算中,加法器是组成这些运算的基本单元。在高性能微处理器和DSP处理器中,加法器的运算时间至关重要。加法器运算常常处于高性能处理器运算部件的关键路径中,特别是在算术逻辑单元中加法器的运算时间对处理器的速度起着决定性的作用。随着微处理器的运算速度越来越快,对快速加法器的需求也越来越高。 当今,加法器的设计面临两大课题,首先是如何降低功耗。随着便携式IC产品例如MP3播放器,手机和掌上电脑等的广泛使用,要求IC工程师对现有运算模块的性能作进一步改进,尤其是在电路的功耗和尺寸方面。由于现在相应的电池技术难以和微电子技术的发展速度匹敌,这使得IC设计师遇到了许多限制因素,比如高速,大吞吐量,小尺寸,低功耗等。因此,这使得研究低功耗高性能加法单元持续升温。另一方面就是如何提高加法器的运算速度。因为加法运算存在进位问题,使得某一位计算结果的得出和所有低于它的位相关。因此,为了减少进位传输所耗的时间,提高计算速度,人们设计了多种类型的加法器,如超前进位加法器曼彻斯特加法器、进位旁路加法器、进位选择加法器等。它们都是利用各位之间的状态来预先产生高位的进位信号,从而减少进位从低位向高位传递的时间。 本文首先介绍了的加法器的类型以及其工作原理,然后重点分析了超前进位加法器的组成结构、结构参数以及

计组-加法器实验报告

半加器、全加器、串行进位加法器以及超前进位加法器 一、实验原理 1.一位半加器 A和B异或产生和Sum,与产生进位C 2.一位全加器 将一位半加器集成封装为halfadder元件,使用两个半加器构成一位的全加器 3.4位串行进位加法器 将一位全加器集成封装为Fulladder元件,使用四个构成串行进位加法器

4.超前进位加法器(4位) ⑴AddBlock 产生并行进位链中的ti(即Cthis)和di(即Cpass),以及本位结果Sum ⑵进位链(Cmaker) 四位一组并行进位链,假设与或非门的级延迟时间为1.5ty,与非门的延迟时间为1ty,在di和ti产生之后,只需2.5ty就可产生所有全部进位

⑶超前进位加法器 将以上二者结合起来即可完成,A和B各位作为各个AddBlock的输入,低一位的进位Ci-1作为本位AddBlock的C-1的输入。各个AddBlock输出的C_this和C_pass作为对应的Cmaker的thisi和passi的输入。

二、实验器材 QuartusII仿真软件,实验箱 三、实验结果 1.串行进位加法器结果 2.超前进位加法器结果

四、实验结果分析 1.实验仿真结果显示串行加法器比超前进位加法器快,部分原因应该是电路结构优化 不到位。另外由于计算的位数比较少,超前进位加法链结构较复杂,所以优势没体现出来,反倒运作的更慢一点。当位数增加的时候,超前进位加法器会比串行的更快。 2.波形稳定之前出现上下波动,应该与“竞争冒险”出现的情况类似,门的延迟和路径 的不同导致了信号变化时到达的时间有先有后,因此在最终结果形成前出现了脉冲尖峰和低谷;另外也可能部分原因由于电路结构优化的不到位所致

FPGA一位全加器设计实验报告

题目:1位全加器的设计 一.实验目的 1.熟悉QUARTUSII软件的使用; 2.熟悉实验硬件平台的使用; 3.掌握利用层次结构描述法设计电路。 二.实验原理 由于一位全加器可由两个一位半加器与一个或门构成,首先设计半加器电路,将其打包为半加器模块;然后在顶层调用半加器模块组成全加器电路;最后将全加器电路编译下载到实验箱,其中ain,bin,cin信号可采用实 验箱上SW0,SW1,SW2键作为输入,并将输 入的信号连接到红色LED管 LEDR0,LEDR1,LEDR2上便于观察,sum,cout 信号采用绿色发光二极管LEDG0,LEDG1来 显示。 三.实验步骤 1.在QUARTUSII软件下创建一工程,工程名为full_adder,芯片名为EP2C35F672C6; 2.新建Verilog语言文件,输入如下半加器Verilog语言源程序; module half_adder(a,b,s,co); input a,b; output s,co; wire s,co; assign co=a & b; assign s=a ^ b; Endmodule 3.保存半加器程序为,进行功能仿真、时序仿真,验证设计的正确性。 其初始值、功能仿真波形和时序仿真波形分别如下所示

4.选择菜单File→Create/Update→Create Symbol Files for current file,创建半加器模块; 5.新建一原理图文件,在原理图中调用半加器、或门模块和输入,输出引脚,按照图1所示连接电路。并将输入ain,bin,cin连接到FPGA的输出端,便于观察。完成后另保存full_adder。 电路图如下 6.对设计进行全编译,锁定引脚,然后分别进行功能与时序仿真,验证全加器的逻辑功能。其初始值、功能仿真波形和时序仿真波形分别如下所示

32位浮点数加法设计仿真实验报告

32位浮点数加法设计仿真实验报告 名字:李磊学号:10045116 班级:10042211 32位浮点数的IEEE-754格式 单精度格式 IEEE.754标准规定了单精度浮点数共32位,由三部分组成:23位尾数f,8位偏置指数e,1位符号位s。将这三部分由低到高连续存放在一个32位的字里,对其进行编码。其中[22:0]位包含23位的尾数f;[30:23]位包含8位指数e;第31位包含符号s {s[31],e[30:23],f[22:0]} 其中偏置指数为实际指数+偏置量,单精度浮点数的偏置量为128,双精度浮点数的偏置量为1024。 规格化的数:由符号位,偏置指数,尾数组成,实际值为1.f乘2的E-128次方 非规格化的数:由符号位,非偏置指数,尾数组成,实际值为0.f乘2的E次方 特殊的数:0(全为零),+无穷大(指数全为1,尾数为0,符号位为0),-无穷大(指数 全为1,尾数为0,符号位为1),NAN(指数全为1,尾数为不全为0) 浮点数加法器设计 设计思路: 1.前端处理,还原尾数 2.指数处理,尾数移位,使指数相等 3.尾数相加 4.尾数规格化处理 5.后端处理,输出浮点数 具体设计: 设计全文: module flowadd(ix, iy, clk, a_en, ost,oz); input ix, iy, clk, a_en; output oz, ost; wire[31:0] ix,iy; reg[31:0] oz;

wire clk,ost,a_en; reg[25:0] xm, ym, zm; reg[7:0] xe, ye, ze; reg[2:0] state; parameter start = 3'b000, //设置状态机 zerock = 3'b001, exequal = 3'b010, addm = 3'b011, infifl = 3'b100, over = 3'b110; assign ost = (state == over) ? 1 : 0; /*后端处理,输出浮点数*/ always@(posedge ost) begin if(a_en) oz <= {zm[25],ze[7:0],zm[22:0]}; end always@(posedge clk) //状态机 begin case(state) start: //前端处理,分离尾数和指数,同时还原尾数 begin xe <= ix[30:23]; xm <= {ix[31],1'b0,1'b1,ix[22:0]}; ye <= iy[30:23]; ym <= {iy[31],1'b0,1'b1,iy[22:0]}; state <= zerock; end zerock: begin if(ix == 0) begin {ze, zm} <= {ye, ym}; state <= over; end else if(iy == 0) begin {ze, zm} <= {xe, xm}; state <= over; end else

设计示例432位先行进位加法器的设计

设计示例4:32位先行进位加法器的设计 1、功能概述: 先行进位加法器是对普通的全加器进行改良而设计成的并行加法器,主要是针对普通全加器串联时互相进位产生的延迟进行了改良。超前进位加法器是通过增加了一个不是十分复杂的逻辑电路来做到这点的。 设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i (1-1) C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2) 令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i 当A i和B i都为1时,G i = 1,产生进位C i+1 = 1 当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i 因此G i定义为进位产生信号,P i定义为进位传递信号。G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。 下面推导4位超前进位加法器。设4位加数和被加数为A和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。于是这各级进位输出,递归的展开Ci,有: C0 = C in C1=G0 + P0·C0 C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0?C0 C3=G2 + P2·C2 = G2 + P2·G1 + P2·P1·G0 + P2·P1·P0·C0 C4=G3 + P3·C3 = G3 + P3·G2 + P3·P2·G1 + P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3) C out=C4 由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关,将各级间的进位级联传播给去掉了,因此减小了进位产生的延迟。每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。实现上述逻辑表达式(1-3)的电路称为超前进位部件(Carry Lookahead Unit),也称为CLA 部件。通过这种进位方式实现的加法器称为超前进位加法器。因为各个进位是并行产生的,所以是一种并行进位加法器。 从公式(1-3)可知,更多位数的CLA部件只会增加逻辑门的输入端个数,而不会增加门的级数,因此,如果采用超前进位方式实现更多位的加法器,从理论上讲,门延迟不变。但是由于CLA部件中连线数量和输入端个数的增多,使得电路中需要具有大驱动信号和大扇入门,这会大大增加门的延迟,起不到提高电路性能的作用。因此更多位数的加

微机原理与接口技术复习提纲

1、简述中断源的分类和它们之间的优先顺序如何?并分别简述CPU响应各类中断源的条件? 答:按中断源与CPU的位置关系,可分为外部中断和内部中断两大类: 外部中断是指有外部设备通过硬件触发请求的方式产生的中断,又称为硬件中断,外部中断有分为非屏蔽中断和可屏蔽中断 内部中断是由CPU运行程序错误或执行内部程序调用引起的一种中断,亦称软件中断。 它们之间的优先顺序是内部中断、非屏蔽中断、可屏蔽中断和单步(跟踪)中断。 CPU响应内部中断、非屏蔽中断、可屏蔽中断和单步(跟踪)中断等四类中断的相同条件是:(1)必须要有中断请求,(2)CPU当前正在执行的指令必须结束,而对于可屏蔽中断,还必须满足IF=1,即CPU处于开中断状态的条件。 2、简述动态存储器(DRAM)的特点? 答; (1) CPU对RAM中的每一单元能读出又能写入。 (2) 读/写过程先寻找存储单元的地址再读/写内容。 (3) 读/写时间与存储单元的物理地址无关。 (4) 失电后信息丢失。现已开发出带电池芯片的RAM,称为非易失性RAM(NVRAM),做到失电后信息不丢失。(5) 作Cache和主存用 3、8086 CPU中地址加法器的重要性体现在哪里? 答:地址加法器是8086 CPU的总线接口单元中的一个器件,在8086存储器分段组织方式中它是实现存储器寻址的一个关键器件,地址加法器将两个16位寄存器中的逻辑地址移位相加,得到一个20位的实际地址,把存储器寻址空间从64K扩大到1M,极大地扩大了微型计算机的程序存储空间,从而大大提高了程序运行效率。 4、8086 CPU中有哪些寄存器?分组说明用途。哪些寄存器用来指示存储器单元的偏移地址? 答:8086 CPU中有8个通用寄存器AX、BX、CX、DX、SP、BP、SI、DI;两个控制寄存器IP、FL;四个段寄存器CS、DS、SS、ES。8个通用寄存器都可以用来暂存参加运算的数据或中间结果,但又有各自的专门用途。例如,AX专用做累加器,某些指令指定用它存放操作数和运算结果;CX为计数寄存器,在某些指令中做计数器使用;DX为数据寄存器;BX为基址寄存器,BP为基址指针,SI为源变址寄存器,DI为目的变址寄存器,这4个寄存器在数据寻址中用来存放段内偏移地址(有效地址)或段内偏移地址的一部分;SP为堆栈指示器,用来存放栈顶有效地址。两个控制寄存器用来存放有关的状态信息和控制信息。例如,标志寄存器FL用来存放状态标志和控制标志;而指令指针用来存放下一条要取指令的有效地址。四个段寄存器用来存放段地址。例如,CS寄存器用来存放代码段的段地址;DS寄存器用来存放数据段的段地址;SS寄存器用来存放堆栈段的段地址;ES寄存器用来存放扩展段的段地址。 5、DRAM为什么要刷新,存储系统如何进行刷新? DRAM以单个MOS管为基本存储单元,以极间电容充放电表示两种逻辑状态。由于极间电容的容量很小,充电电荷自然泄漏会很快导致信息丢失,所以要不断对它进行刷新操作、即读取原内容、放大再写入。 存储系统的刷新控制电路提供刷新行地址,将存储DRAM芯片中的某一行选中刷新。实际上,刷新控制电路是将刷新行地址同时送达存储系统中所有DRAM芯片,所有DRAM芯片都在同时进行一行的刷新操作。 刷新控制电路设置每次行地址增量,并在一定时间间隔内启动一次刷新操作,就能够保证所有DRAM芯片的所有存储单元得到及时刷新。 6、计算机I/O接口有何用途?试列出8个I/O接口。