xilinx原语的使用方法

Xilinx原语的使用方法1

3.4 Xilinx公司原语的使用方法

原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。

Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的使用方法是类似的。

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM 组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

3.4.1 计算组件

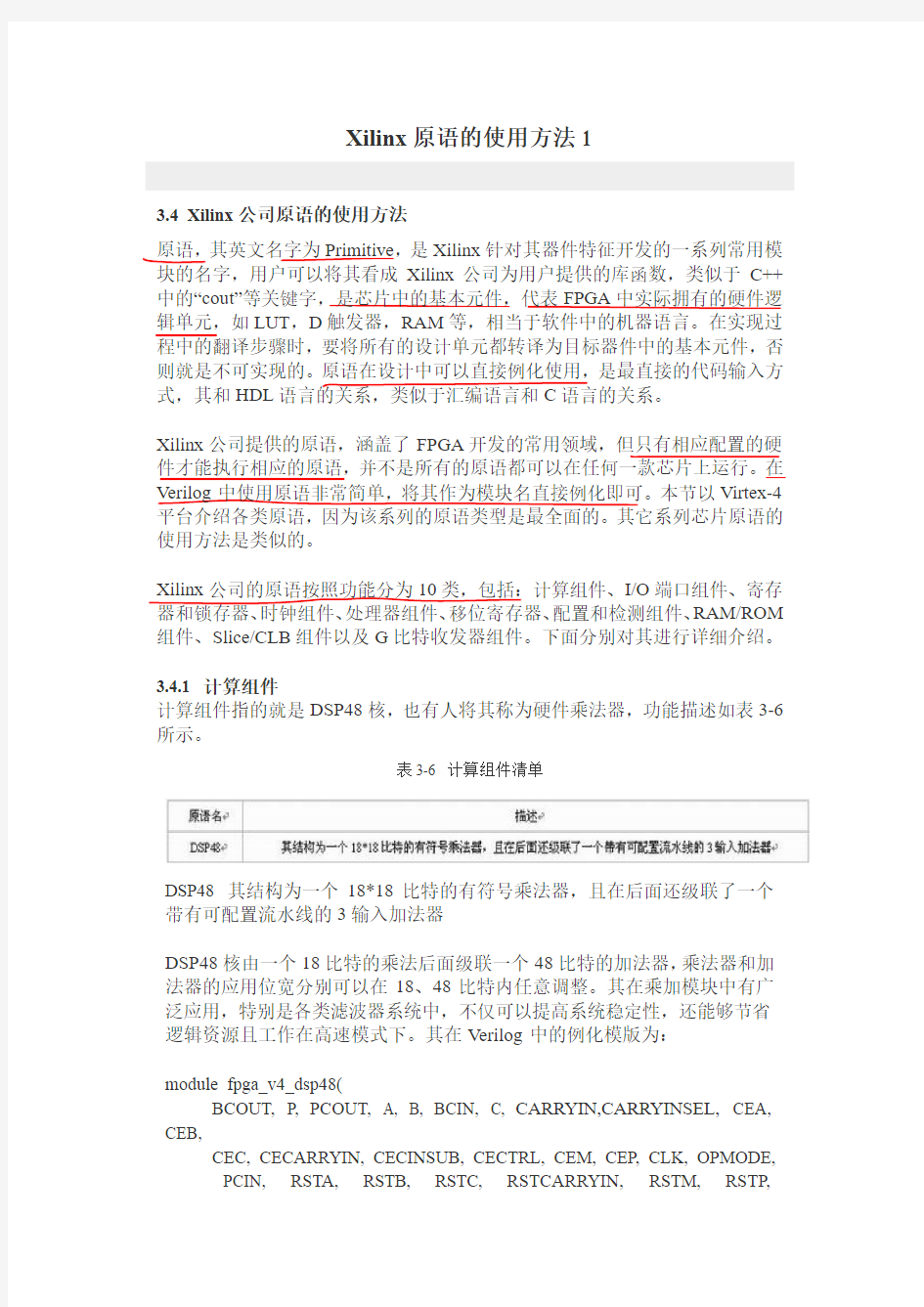

计算组件指的就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。

表3-6 计算组件清单

DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器

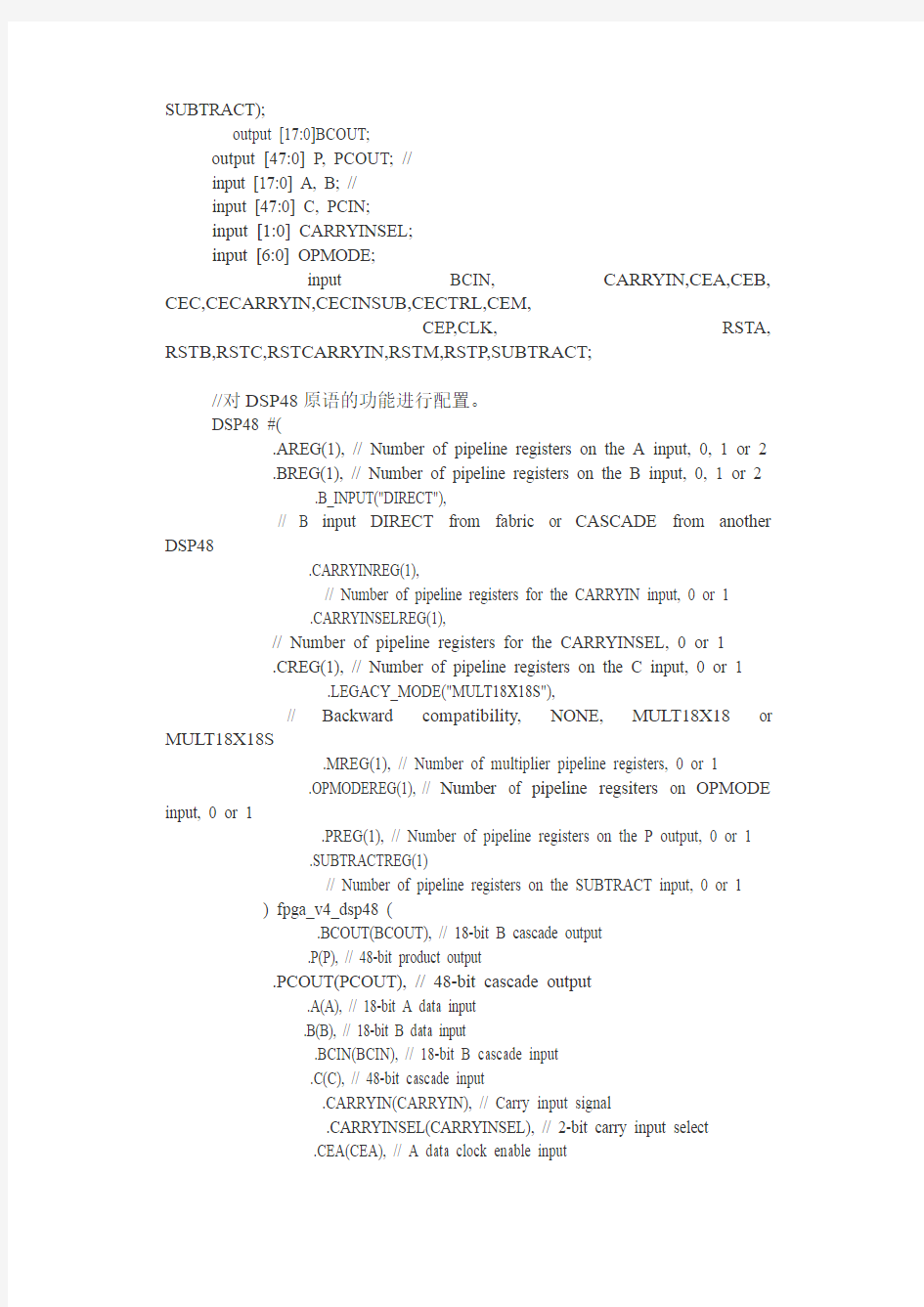

DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。其在Verilog中的例化模版为:

module fpga_v4_dsp48(

BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB,

CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE,

PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP,

SUBTRACT);

output [17:0]BCOUT;

output [47:0] P, PCOUT; //

input [17:0] A, B; //

input [47:0] C, PCIN;

input [1:0] CARRYINSEL;

input [6:0] OPMODE;

input BCIN, CARRYIN,CEA,CEB, CEC,CECARRYIN,CECINSUB,CECTRL,CEM,

CEP,CLK, RSTA, RSTB,RSTC,RSTCARRYIN,RSTM,RSTP,SUBTRACT;

//对DSP48原语的功能进行配置。

DSP48 #(

.AREG(1), // Number of pipeline registers on the A input, 0, 1 or 2

.BREG(1), // Number of pipeline registers on the B input, 0, 1 or 2 .B_INPUT("DIRECT"),

// B input DIRECT from fabric or CASCADE from another DSP48

.CARRYINREG(1),

// Number of pipeline registers for the CARRYIN input, 0 or 1

.CARRYINSELREG(1),

// Number of pipeline registers for the CARRYINSEL, 0 or 1

.CREG(1), // Number of pipeline registers on the C input, 0 or 1 .LEGACY_MODE("MULT18X18S"),

// Backward compatibility, NONE, MULT18X18 or MULT18X18S

.MREG(1), // Number of multiplier pipeline registers, 0 or 1

.OPMODEREG(1), // Number of pipeline regsiters on OPMODE input, 0 or 1

.PREG(1), // Number of pipeline registers on the P output, 0 or 1

.SUBTRACTREG(1)

// Number of pipeline registers on the SUBTRACT input, 0 or 1 ) fpga_v4_dsp48 (

.BCOUT(BCOUT), // 18-bit B cascade output

.P(P), // 48-bit product output

.PCOUT(PCOUT), // 48-bit cascade output

.A(A), // 18-bit A data input

.B(B), // 18-bit B data input

.BCIN(BCIN), // 18-bit B cascade input

.C(C), // 48-bit cascade input

.CARRYIN(CARRYIN), // Carry input signal

.CARRYINSEL(CARRYINSEL), // 2-bit carry input select

.CEA(CEA), // A data clock enable input

.CEB(CEB), // B data clock enable input

.CEC(CEC), // C data clock enable input

.CECARRYIN(CECARRYIN), // CARRYIN clock enable input

.CECINSUB(CECINSUB), // CINSUB clock enable input

.CECTRL(CECTRL), // Clock Enable input for CTRL regsiters

.CEM(CEM), // Clock Enable input for multiplier regsiters

.CEP(CEP), // Clock Enable input for P regsiters

.CLK(CLK), // Clock input

.OPMODE(OPMODE), // 7-bit operation mode input

.PCIN(PCIN), // 48-bit PCIN input

.RSTA(RSTA), // Reset input for A pipeline registers

.RSTB(RSTB), // Reset input for B pipeline registers

.RSTC(RSTC), // Reset input for C pipeline registers

.RSTCARRYIN(RSTCARRYIN), // Reset input for CARRYIN registers

.RSTCTRL(RSTCTRL), // Reset input for CTRL registers

.RSTM(RSTM), // Reset input for multiplier registers

.RSTP(RSTP), // Reset input for P pipeline registers

.SUBTRACT(SUBTRACT) // SUBTRACT input

);

endmodule

3.4.2 时钟组件

时钟组件包括各种全局时钟缓冲器、全局时钟复用器、普通I/O本地的时钟缓冲器以及高级数字时钟管理模块,如表3-7所示。

表3-7 时钟组件的清单

下面对几个常用时钟组件进行简单介绍,其余组件的使用方法是类似的。

1.BUFG

BUFG是具有高扇出的全局时钟缓冲器,一般由综合器自动推断并使用,其和同类原语的RTL结构如图3-28所示。全局时钟是具有高扇出驱动能力的缓冲器,可以将信号连到时钟抖动可以忽略不计的全局时钟网络,BUFG组件还可应用于典型的高扇出信号和网络,如复位信号和时钟使能信号。如果要对全局时钟实现PLL或DCM等时钟管理,则需要手动例化该缓冲器。其例化的代码模板如下所示:

// BUFG: 全局时钟缓存(Global Clock Buffer),只能以内部信号驱动

// Xilinx HDL库向导版本,ISE 9.1

BUFG BUFG_inst (

.O(O), //时钟缓存输出信号

.I(I) // /时钟缓存输入信号

);

// 结束BUFG_ins模块的例化过程

在综合结果分析中,其和同类原语的RTL结构如图3-32所示。

图3-32 全局时钟原语的RTL级结构示意图

2. BUFMUX

BUFMUX是全局时钟复用器,选择两个输入时钟I0或I1中的一个作为全局时钟,其和同类原语BUFMUX1的RTL级结构如图M所示。当选择信号S 为低时,选择I0;否则输出I1,其真值表如表M所示。BUFMUX原语和BUFMUX1原语的功能一样,只是选择逻辑不同,对于BUFMUX1,当选择信号S为低时,选择I1;否则输出I0。

BUFMUX原语的例化代码模板如下所示:

// BUFGMUX: 全局时钟的2到1复用器(Global Clock Buffer 2-to-1 MUX)// 适用芯片:Virtex-II/II-Pro/4/5, Spartan-3/3E/3A

// Xilinx HDL库向导版本,ISE 9.1

BUFGMUX BUFGMUX_inst (

.O(O), //时钟复用器的输出信号

.I0(I0), // 0时钟输入信号

.I1(I1), //1时钟输入信号

.S(S) // 时钟选择信号

);

// 结束BUFGMUX_inst模块的例化过程

需要注意的是:该原语只用用全局时钟处理,不能作为接口使用。在综合结果分析时,它和同类原语BUFMUX1的RTL级结构如图3-33所示。

图3-33 全局时钟复用器的RTL级结构示意图

3. BUFIO

BUFIO是本地I/O时钟缓冲器,其RTL结构如图M所示,只有一个输入与输出,非常简单。BUFIO使用独立于全局时钟网络的专用时钟网络来驱动纵向I/O管脚,所以非常适合同步数据采集。BUFIO要求时钟和相应的I/O 必须在同一时钟区域,而不同时钟网络的驱动需要BUFR原语来实现。需要注意的是,由于BUFIO引出的时钟只到达了I/O列,所以不能来驱动逻辑资源,如CLB和块RAM。

BUFIO的例化代码模板如下:

// BUFIO: 本地I/O时钟缓冲器(Local Clock Buffer)

// 适用芯片:Virtex-4/5

// Xilinx HDL库向导版本,ISE 9.1

BUFIO BUFIO_inst (

.O(O), //本地I/O时钟缓冲器的输出信号

.I(I) //本地I/O时钟缓冲器的输入信号

);

// 结束BUFIO模块的例化过程

在综合结果分析时,其RTL级结构如图3-34所示。

图3-34 本地I/O时钟缓冲器的RTL级结构示意图

4. BUFR

BUFR是本地I/O时钟、逻辑缓冲器,其RTL结构如图M所示。BUFR和BUFIO都是将驱动时钟引入某一时钟区域的专用时钟网络,而独立于全局时钟网络;不同的是,BUFR不仅可以跨越不同的时钟区域(最多3个),还能够驱动I/O逻辑以及自身或邻近时钟区域的逻辑资源。BUFIO的输出和本地内部互联都能驱动BUFR组件。此外,BUFR能完成输入时钟1~8的整数分频。因此,BUFR是同步设计中实现跨时钟域以及串并转换的最佳方式。

BUFIO的例化代码模板如下:

// BUFR: 本地I/O时钟、逻辑缓冲器(Regional Clock Buffer)

// 适用芯片:Virtex-4/5

// Xilinx HDL库向导版本,ISE 9.1

BUFR #(

.BUFR_DIVIDE("BYPASS"),

//分频比,可选择"BYPASS", "1", "2", "3", "4", "5", "6", "7", "8"。

.SIM_DEVICE("VIRTEX4")

// 指定目标芯片, "VIRTEX4" 或者"VIRTEX5"

) BUFR_inst (

.O(O), //时钟缓存输出信号

.CE(CE), //时钟使能信号,输入信号

.CLR(CLR), //时钟缓存清空信号

.I(I) // 时钟缓存输入信号

);

// 结束BUFR模块的例化过程

需要注意的是:BUFIO和BUFR只能在Virtex-4系列以及更高系列芯片中使用。在综合结果分析时,其RTL结构如图3-35所示。

图3-35 本地I/O时钟、逻辑缓冲器的RTL级结构示意图

5. DCM_BASE

DCM_BASE是基本数字时钟管理模块的缩写,是相位和频率可配置的数字锁相环电路,常用于FPGA系统中复杂的时钟管理。如果需要频率和相位动态重配置,则可以选用DCM_ADV原语;如果需要相位动态偏移,可使用DCM_PS原语。DCM系列原语的RTL结构如图3-8所示。

模块接口信号的说明如表3-8所列

DCM_BASE组件可以通过Xilinx的IP Wizard向导产生,也可以直接通过下面的例化代码直接使用。其Verilog的例化代码模板为:

// DCM_BASE: 基本数字时钟管理电路(Base Digital Clock Manager Circuit)// 适用芯片:Virtex-4/5

// Xilinx HDL库向导版本,ISE 9.1

DCM_BASE #(

.CLKDV_DIVIDE(2.0),

// CLKDV分频比可以设置为: 1.5,2.0,2.5,3.0,3.5,4.0,4.5,5.0,5.5,6.0,6.5

// 7.0,7.5,8.0,9.0,10.0,11.0,12.0,13.0,14.0,15.0 or 16.0

.CLKFX_DIVIDE(1), // Can be any integer from 1 to 32

// CLKFX信号的分频比,可为1到32之间的任意整数

.CLKFX_MULTIPLY(4),

// CLKFX信号的倍频比,可为2到32之间的任意整数

.CLKIN_DIVIDE_BY_2("FALSE"),

// 输入信号2分频的使能信号,可设置为TRUE/FALSE

.CLKIN_PERIOD(10.0),

// 指定输入时钟的周期,单位为ns,数值范围为1.25~1000.00。

.CLKOUT_PHASE_SHIFT("NONE"),

// 指定移相模式,可设置为NONE或FIXED

.CLK_FEEDBACK("1X"),

// 指定反馈时钟的频率,可设置为NONE、1X或2X。相应的频率关系都是针对CLK0而言的。

.DCM_PERFORMANCE_MODE("MAX_SPEED"),

// DCM模块性能模式,可设置为MAX_SPEED 或MAX_RANGE

.DESKEW_ADJUST("SYSTEM_SYNCHRONOUS"),

// 抖动调整,可设置为源同步、系统同步或0~15之间的任意整数

.DFS_FREQUENCY_MODE("LOW"),

// 数字频率合成模式,可设置为LOW或HIGH 两种频率模式

.DLL_FREQUENCY_MODE("LOW"),

// DLL的频率模式,可设置为LOW、HIGH或HIGH_SER

.DUTY_CYCLE_CORRECTION("TRUE"),

// 设置是否采用双周期校正,可设为TRUE或FALSE

.FACTORY_JF(16'hf0f0),

// 16比特的JF因子参数

.PHASE_SHIFT(0),

// 固定相移的数值,可设置为-255 ~ 1023之间的任意整数

.STARTUP_WAIT("FALSE")

// 等DCM锁相后再延迟配置DONE管脚,可设置为TRUE/FALSE

) DCM_BASE_inst (

.CLK0(CLK0), // 0度移相的DCM时钟输出

.CLK180(CLK180), // 180度移相的DCM时钟输出

.CLK270(CLK270), // 270度移相的DCM时钟输出

.CLK2X(CLK2X), // DCM模块的2倍频输出

.CLK2X180(CLK2X180), // 经过180度相移的DCM模块2倍频输出

.CLK90(CLK90), // 90度移相的DCM时钟输出

.CLKDV(CLKDV), // DCM模块的分频输出,分频比为CLKDV_DIVIDE .CLKFX(CLKFX), // DCM合成时钟输出,分频比为(M/D)

.CLKFX180(CLKFX180), // 180度移相的DCM合成时钟输出

.LOCKED(LOCKED), // DCM锁相状态输出信号

.CLKFB(CLKFB), // DCM模块的反馈时钟信号

.CLKIN(CLKIN), // DCM模块的时钟输入信号

.RST(RST) // DCM 模块的异步复位信号

);

// 结束DCM_BASE模块的例化过程

在综合结果分析时,DCM系列原语的RTL结构如图3-36所示。

图3-36 DCM模块的RTL级结构示意图

3.4.3 配置和检测组件

配置和检测组件提供了FPGA内部逻辑和JTAG扫描电路之间的数据交换以及控制功能,只要由6个原语组成,如表3-9所示。

表3-9 配置和检测原语列表

下面对BSCAN_VIRTEX4组件进行简单介绍,其余组件的使用方法是类似的。

1.BSCAN_VIRTEX4

当JTAG USER1/2/3/4指令被加载后,BSCAN_VIRTEX4允许设计人员来检测TCK、TMS以及TDI等专用JTAG管脚的数据,并且可以将用户数据写入到TDO管脚上,这样可以在PC上通过JTAG链读取芯片内部的用户数据。

BSCAN_VIRTEX4的管脚信号说明如下:

CAPTURE:位宽为1的输出信号,用于指示是否加载了用户指令,当JTAG 接口处于CAPTURE-DR状态时,输出为高。

DRCK:位宽为1的输出信号,用于监测JTAG电路的TCK信号。当JTAG 链路处于用户指令模式或者JTAG接口为SHIFT-DR状态时,才有信号输出。

RESET:位宽为1的输出信号,在加载用户指令时有效。当JTAG接口控制器处于TEST-LOGIC-RESET状态时置高。

SEL:位宽为1的输出信号,高有效。用于指示USER1数据是否加载到JTAG 指令寄存器中。在UPDATE-IR状态时有效,直到加载新的指令之前,一直保持有效电平。

SHIFT:位宽为1的输出信号,加载用户指令时有效。当JTAG接口控制器处于SHIFT-DR状态时置高。

TDI:位宽为1的输出信号,用于检测JTAG链的TDI信号。

UPDATE:位宽为1的输出信号,加载USER1指令和USER2指令时有效。当JTAG接口控制器处于UPDATE-DR状态时置高。

TDO:位宽为1的输入信号,可以将外部JTAG链的TDO信号直接连到该管脚上。

在Virtex-4芯片中,有4个BSCAN_VIRTEX4硬件原语可用。因此,其属性JTAG_CHAIN的有效值为1~4,默认值为1。

BSCAN_VIRTEX4原语的例化代码模板如下所示:

// BSCAN_VIRETX4: 完成内部逻辑和JTAG接口连接的边界扫描原语(Boundary Scan primitive for connecting internal logic to JTAG interface.)

// 适用芯片:Virtex-4/5

// Xilinx HDL库向导版本,ISE 9.1

BSCAN_VIRETX4 #(

.JTAG_CHAIN(1)

// 指定JTAG链用户指令,必须为1, 2, 3, 或4中的任何一个正整数

) BSCAN_VIRETX4_inst (

.CAPTURE(CAPTURE), // 捕获到的从TAP控制器的输出

.DRCK(DRCK), // 用户函数服务的数据寄存器输出

.RESET(RESET), // TAP控制器输出的复位信号

.SEL(SEL), // 用户激活输出

.SHIFT(SHIFT), // TAP控制器的移位输出

.TDI(TDI), // TAP控制器的TDI输出信号

.UPDATE(UPDATE), // TAP控制器的UPDATE输出信号

.TDO(TDO) // 用户函数的数据输入信号

);

// 结束BSCAN_VIRETX4:模块的例化过程

在综合结果分析时,BSCAN_VIRTEX4的RTL结构图如图3-37所示。

图3-37 BSCAN_VIRTEX4原语的RTL图

3.4.4 吉比特收发器组件

吉比特收发器组件用于调用RocketIO千兆位级收发器,支持从622 Mbps 到6.5 Gbps的多速率应用,符合最广泛的芯片、背板和光学器件的标准及协议,具有高级Tx/Rx均衡技术,收发器最多可达24个,提供了完整的串行I/O 解决方案。具体包括4个组件,如表3-10所示。

表3-10 吉比特收发器组件

由于吉比特收发器操作复杂,使用原语很容易出错,不易配置,因此需要在ISE中通过结构向导完成。有关吉比特收发器的原理和使用方法,将在第11章详细介绍。

3.4.5 I/O端口组件

I/O组件提供了本地时钟缓存、标准单端I/O缓存、差分I/O信号缓存、DDR 专用I/O信号缓存、可变抽头延迟链、上拉、下拉以及单端信号和差分信号之间的相互转换,具体包括了21个原语,如表3-11所示。

表3-11 I/O端口组件

下面对几个常用I/O组件进行简单介绍,其余组件的使用方法是类似的。1. BUFIO

BUFIO是FPGA芯片内部简单的时钟输入、输出缓存器,其RTL结构如图3-38所示。BUFIO使用独立于全局时钟网络的专用时钟网络来驱动I/O列,因此非常适合用于源同步的数据采集。但要注意的是:BUFIO只能在单一的时钟区域内使用,不能跨时钟域操作。此外,BUFIO也不能用于驱动逻辑资源(CLB、块RAM等),因此其只能到达I/O列。

图3-38 BUFIO的RTL结构图

2. IBUFDS

IBUFDS原语用于将差分输入信号转化成标准单端信号,且可加入可选延迟。在IBUFDS原语中,输入信号为I、IB,一个为主,一个为从,二者相位相反。

IBUFDS的逻辑真值表如表3-12所列,其中“-*”表示输出维持上一次的输出值,保持不变。

表3-12 IBUFDS原语的输入、输出真值表

BUFDS原语的例化代码模板如下所示:

// IBUFDS: 差分输入缓冲器(Differential Input Buffer)

// 适用芯片:Virtex-II/II-Pro/4, Spartan-3/3E

// Xilinx HDL库向导版本,ISE 9.1

IBUFDS #(

.DIFF_TERM("FALSE"),

// 差分终端,只有Virtex-4系列芯片才有,可设置为True/Flase

.IOSTANDARD("DEFAULT")

// 指定输入端口的电平标准,如果不确定,可设为DEFAULT

) IBUFDS_inst (

.O(O), // 时钟缓冲输出

.I(I), // 差分时钟的正端输入,需要和顶层模块的端口直接连接

.IB(IB) // 差分时钟的负端输入,需要和顶层模块的端口直接连接

);

// 结束IBUFDS模块的例化过程

在综合结果分析时,IBUFDS的RTL结构如图3-39所示。

图3-39 IBUFDS原语的RTL结构图

3. IDELAY

在Virtex-4系列芯片中,每个用户I/O管脚的输入通路都有一个IDELAY模块,可用于数据信号或时钟信号,以使二者同步,准确采集输入数据。IDELAY 具有可控的64抽头延迟线,每个抽头的延迟都是经过精密校准的78ps,且与进程、电压和温度特性无关,其内部结构如图3-40所示。

图3-40 IDELAY模块的RTL级结构图

IDELAY原语的信号说明如下:

I:单比特输入信号,来自于IOB的串行输入数据;

C:单比特输入信号,时钟输入信号;

INC:单比特输入信号,用于增加或减少延迟抽头数;

CE:单比特输入信号,使能延迟抽头数增加或减少的功能;

RST:单比特输入信号,复位延迟链的延迟抽头数,如果没有编程输入,则为0;

O:单比特输出信号。

IDELAY原语的例化代码模板如下所示:

// IDELAY: 输入延迟单元(Input Delay Element)

// 适用芯片:Virtex-II/II-Pro/4, Spartan-3/3E

// Xilinx HDL库向导版本,ISE 9.1

IDELAY #(

.IOBDELAY_TYPE("DEFAULT"),

// 输入延迟类型,可设置为"DEFAULT", "FIXED" 或者"VARIABLE"

.IOBDELAY_VALUE(0)

// 输入延迟周期数,可设置为0~63之间的任意整数

) IDELAY_inst (

.O(O), //1比特输出信号

.C(C), // 1比特时钟输入信号

.CE(CE), // 1比特时钟使能信号

.I(I), // 1比特数据输入信号

.INC(INC), // 1比特增量输入信号

.RST(RST) //1比特复位输入信号

);

// 结束IDELAY模块的例化过程

在综合结果分析时,IDELAY原语的RTL结构如图3-41所示。

图3-41 IDELAY原语的RTL结构图

4. OBUFDS原语

OBUFDS将标准单端信号转换成差分信号,输出端口需要直接对应到顶层模块的输出信号,和IBUFDS为一对互逆操作。OBUFDS原语的真值表如表3-13所列。

表3-13 OBUFDS原语的真值表

OBUFDS原语的例化代码模板如下所示:

// OBUFDS: 差分输出缓冲器(Differential Output Buffer)

// 适用芯片:Virtex-II/II-Pro/4, Spartan-3/3E

// Xilinx HDL库向导版本,ISE 9.1

OBUFDS #(

.IOSTANDARD("DEFAULT")

// 指名输出端口的电平标准

) OBUFDS_inst (

.O(O), // 差分正端输出,直接连接到顶层模块端口

.OB(OB), // 差分负端输出,直接连接到顶层模块端口

.I(I) // 缓冲器输入

);

// 结束OBUFDS模块的例化过程

在综合结果分析时,OBUFDS原语的RTL结构如图3-42所示。

图3-42 OBUFDS的RTL结构图

5. IOBUF原语

IOBUF原语是单端双向缓冲器,其I/O接口必须和指定的电平标准相对应,支持LVTTL、LVCMOS15、LVCMOS18、LVCMOS25以及LVCMOS33等信号标准,同时还可通过DRIVE、FAST 以及SLOW等约束来满足的不同驱动和抖动速率的需求。默认的驱动能力为12mA,低抖动。IOBUF由IBUF 和OBUFT两个基本组件构成,当I/O端口为高阻时,其输出端口O为不定态。IOBUF原语的功能也可以通过其组成组件的互联来实现。

IOBUF原语的输入输出真值表如表3-14所列。

表3-14 IOBUF原语的真值表

IOBUF原语的例化代码模板如下所示:

// IOBUF: 单端双向缓冲器(Single-ended Bi-directional Buffer)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

IOBUF #(

.DRIVE(12),

// 指定输出驱动的强度

.IOSTANDARD("DEFAULT"),

// 指定I/O电平的标准,不同的芯片支持的接口电平可能会有所不同

.SLEW("SLOW")

// 制定输出抖动速率

) IOBUF_inst (

.O(O), // 缓冲器的单元输出

.IO(IO), // 缓冲器的双向输出

.I(I), // 缓冲器的输人

.T(T) // 3态使能输入信号

);

// 结束IOBUF模块的例化过程

在综合结果分析时,IOBUF原语的RTL结构如图3-43所示。

图3-43 OBUFDS的RTL结构图

6. PULLDOWN和PULLUP原语

数字电路有三种状态:高电平、低电平、和高阻状态。有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使其处于稳定状态,如图3-44所示。FPGA的I/O端口,可以通过外接电阻上下拉,也可以在芯片内部,通过配置完成上下拉。上拉电阻是用来解决总线驱动能力不足时提供电流的,而下拉电阻是用来吸收电流。通过FPGA内部配置完成上下拉,能有效节约电路板面积,是设计的首选方案。

图3-44 上、下拉电路示意图

上、下拉的原语分别为PULLUP和PULLDOWN。

1)PULLUP原语的例化代码

// PULLUP: 上拉原语(I/O Buffer Weak Pull-up)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

PULLUP PULLUP_inst (

.O(O),

//上拉输出,需要直接连接到设计的顶层模块端口上);

// 结束PULLUP模块的例化过程

2)PULLDOWN原语的例化代码

// PULLDOWN:下拉原语(I/O Buffer Weak Pull-down)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

PULLDOWN PULLDOWN_inst (

.O(O),

// 下拉输出,需要直接连接到设计的顶层模块端口上

);

// 结束PULLDOWN模块的例化过程

3.4.6 处理器组件

处理器组件主要包括高速以太网MAC控制器和PowerPC硬核,如表3-15所示。

表3-15处理器组件列表

处理器组件是Xilinx的嵌入式解决方案,涉及软、硬件调试以及系统设计,将在第8章详细介绍。

Xilinx公司原语的使用方法2

3.4.7 RAM/ROM组件

RAM/ROM组件可用于例化FIFO、分布式RAM、分布式RAM、块ROM以及块ROM,具体包括12个组件,如表3-16所示。

表3-16 RAM/ROM原语列表

下面主要介绍FIFO、分布式双口RAM以及块双口RAM原语的使用,单口RAM和ROM原语的用法类似,限于篇幅,就不再介绍。

1.RAM16X1S

RAM16X1S是深度为16比特,位宽为1的同步RAM。当写使能信号WE

为低时,写端口的数据操作无效,RAM内部的数据不会改变;当WE为高时,可以在任意地址中写入比特。为了保证数据的稳定性,地址和数据应该在WCLK的上升沿前保持稳定。输出信号O为RAM中由读地址信号所确定的地址中所存数据的值。此外,还可通过属性指定RAM的初始值。

RAM16X1S原语的例化代码模版如下所示:

// RAM16X1S: 16比特1深度同步RAM(16 x 1 posedge write distributed (LUT) RAM)

// 适用芯片:所有芯片

// Xilinx HDL库向导版本,ISE 9.1

RAM16X1S #(

.INIT(16'h0000)

//对RAM的内容进行初始化,这里初始化为全1

) RAM16X1S_inst (

.O(O), // RAM output

.A0(A0), // RAM address[0] input

.A1(A1), // RAM address[1] input

.A2(A2), // RAM address[2] input

.A3(A3), // RAM address[3] input

.D(D), // RAM data input

.WCLK(WCLK), // Write clock input

.WE(WE) // Write enable input

);

// 结束RAM16X1S模块的例化过程

需要注意的是,RAM16X1S原语是Xilinx独有的一类结构,在小数据量存储方面非常节省资源。在综合结果分析时,RAM16X1S原语的RTL结构如图3-45所示。

图3-45 原语RAM16X1S的RTL结构图

2.RAMB16

RAMB16是FPGA芯片中内嵌的双口块RAM,数据位宽可配置成1、2、4、9、18以及36比特,每个块RAM的大小为18 1024比特,所以位宽越大,深度越小。块RAM在FPGA中按照矩阵的方式排列,其数量完全取决于芯片容量的大小。在使用中,可以添加坐标来约束块RAM的位置。例如:LOC = RAMB16_X#Y#;

同样,也可以对块RAM完成初始化。块RAM是以硬核的方式内嵌到FPGA 芯片中,不占用芯片的逻辑资源,是FPGA芯片内部非常宝贵的一种资源。在工作时,要尽量使用芯片的块RAM资源,不仅能保证较高的工作频率,还具有很低的动态功耗。

RAMB16的Verilog例化代码如下所示。

// RAMB16: 块RAM(Virtex-4 16k+2k Parity Paramatizable BlockRAM

// 适用芯片:Virtex-4芯片

// Xilinx HDL库向导版本,ISE 9.1

RAMB16 #(

.DOA_REG(0),

// A端口可选的输出寄存器,可设置为0或1,分别表示输出不寄存/寄存.DOB_REG(0),

// B端口可选的输出寄存器,可设置为0或1,分别表示输出不寄存/寄存.INIT_A(36'h000000000),

// 初始化A端口的输出初始值

.INIT_B(36'h000000000),

// 初始化A端口的输出初始值

.INVERT_CLK_DOA_REG("FALSE"),

// 反转A端口寄存器的时钟,可设置为"TRUE"或"FALSE",分别表示不反转/反转

.INVERT_CLK_DOB_REG("FALSE"),

// 反转B端口寄存器的时钟,可设置为"TRUE"或"FALSE",分别表示不反转/反转

.RAM_EXTENSION_A("NONE"),

// RAM的A端口扩展选项,可设置为"UPPER"、"LOWER"或"NONE",分别表示作为// 高字节、低字节级联,或者不扩展

.RAM_EXTENSION_B("NONE"),

// RAM的B端口扩展选项.READ_WIDTH_A(0),同A端口

.READ_WIDTH_A(0),

// A端口的数据读取宽度,有效值为1, 2, 4, 9, 18, 或36

.READ_WIDTH_B(0),

// B端口的数据读取宽度,有效值为1, 2, 4, 9, 18, 或36

.SIM_COLLISION_CHECK("ALL"),

// 碰撞检测使能信号,可设置为"ALL"、"WARNING_ONLY"、"GENERATE_X_ONLY" // 或者"NONE"

.SRVAL_A(36'h000000000),

// 复位后A端口的输出值

.SRVAL_B(36'h000000000),

//复位后A端口的输出值

.WRITE_MODE_A("WRITE_FIRST"),

// A端口的写模式,可设置为"WRITE_FIRST", "READ_FIRST", 或

"NO_CHANGE"

.WRITE_MODE_B("WRITE_FIRST"),

// B端口的写模式,可设置为"WRITE_FIRST", "READ_FIRST", 或

"NO_CHANGE"

.WRITE_WIDTH_A(2),

// A端口的数据写入宽度,有效值为1, 2, 4, 9, 18, 或36

.WRITE_WIDTH_B(0),

// B端口的数据写入宽度,有效值为1, 2, 4, 9, 18, 或36

// 下列INIT_xx 声明用于指定RAM的初始化内容

.INIT_00(256'h0000000000000000000000000000000000000000000000000000 000000000000),

文件后缀名大全

文件后缀名大全(新手必看) 什么是文件名后缀说起来Windows工作界面下的文件名简直是随心所欲,比如:某编辑部的2000年工作计划。文件名即可用中文直接表达,而且长度最长可达256个字符,让人看起来真是一目了然。然而在Windows环境中,安装的软件中却大量存在着类似CALENDAR.EXE、GAMES.GRP等等的文件名,这又是为什么呢?原来这些文件名都是根据DOS环境的文件名命名规则而定的。DOS环境下的文件名在DOS 下,文件名采用8+3结构,即:最长8位的文件名,由小数点分隔后再跟上最长3位的后缀名,如:READ.ME、SETUP.EXE,一般情况下文件名不允许使用汉字,只能由字母、数字和一些符号组成。如READ.ME用中文理解就是“读我”,即提示用户在使用软件前先看看这个文件的内容,以获取更多的提示信息。而更重要的是,DOS下规定用后缀名来区分各种不同的文件。在DOS下最容易遇到的首先是可执行文件,后缀名有两类:*.exe、*.com(此处的*表示文件名任意),它们是由汇编语言或其它高级语言编出的程序经过编译后直接在DOS下运行的文件。有时由于软件功能多、内存偏小,不能一次性全部调入内存还可能有同文件名的ov l文件,如ws.exe、ws.ov l。另外还有一种文件可以直接运行,*.bat,即批处理文件,其中有许多命令或可执行文件名,主要用于提高工作效率,其中最有用的是Autoexec.bat,这个文件在开机时会被自动执行(自动执行在英文中就是Automatically execute)。而另外一种可以加载但不能直接运行的文件即是系统扩展管理文件*.sys(sy s即系统system),它主要提供某些非标准设备如鼠标、扩充内存等的驱动程序,如mouse.sy s、himem.sy s。为了统一管理还专门规定了一个conf ig.sy s的文本文件来一次性地在开机时自动调入这些必需的设备驱动程序,这些文件一旦被误删或换名或被病毒侵袭则将直接导致系统工作不正常。DOS下字处理产生的文件原本是可以不用后缀的,但人们常用*.txt表示(txt即文本text)。被所有的平台和所有应用程序支持。而为了管理方便,人们也可以用自己的名字做后缀来表示是自己建的文本文件,如我输入的很多文章即为*.mcj,为了便于用户在意外删掉原文件的情况下能尽快恢复原文件,许多字处理系统都提供了一种自动备份的功能,如我第二次编辑JIHUA.MCJ时(JIHUA:计划的汉语拼音),系统会先拷贝一份原文件为JIHUA.BAK。使用具有特殊格式功能的字处理软件,如求伯君先生早年推出的WPS,就会规定其后缀为.wps,用以标识是用WPS生成的文本文件。当使用字处理软件编辑高级语言程序时,后缀通常为相应语言的前三个字母(如:*.BAS即BASIC语言源程序,*.PAS为PASCAL语言程序,*.FOR为Fortran 语言程序,*.C即为C语言,*.ASM即为汇编语言程序)。伴随着可执行文件常附有以下几类文件:*.HLP 即帮助文件(help)、*.CFG即配置文件(conf ig)、*.DAT即数据文件(data)、*.LOG即日志文件(log)、*.TMP 为临时文件(temporal)。

xilinx FPGA SelectIO模块资料

5.1.6 SelectIO模块 Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。 图5-24 I/O 片结构图 本小节就以下几个方面介绍Virtex-6 的SelectIO 资源。 (1) SelectIO 的电气特性。 (2) SelectIO 的逻辑资源——ILOGIC 资源和OLOGIC 资源。 (3) SelectIO 的高级逻辑资源——ISERDES 资源、OSERDES 资源和Bitslip。 一、SelectIO IO 的电气特性 所有的Virtex-6 FPGA 有高性能的可配置SelectIO 驱动器与接收器,支持非常广泛的接口标准。强大的功能SelectIO 包括输出强度和斜率的可编程控制以及使用数控阻抗(DCI)的片上终端。

IOB 包含输入、输出和三态SelectIO 驱动器。支持单端I/O 标准(LVCMOS、 HSTL、SSTL)和差分I/O 标准(LVDS、HT、LVPECL、BLVDS、差分HSTL 和SSTL)。 注意:差分输入和VREF 相关输入由VCCAUX 供电。 IOB、引脚及内部逻辑的连接如图5-25 所示。 图5-25 IOB、引脚及内部逻辑连接图 IOB 直接连接ILOGIC/OLOGIC 对,该逻辑对包含输入和输出逻辑资源,可实现数据和三态控制。ILOGIC和OLOGIC可分别配置为ISERDES和OSERDES。Xilinx软件库提供了大量与I/O相关的原语,在例化这些原语时,可以指定I/O 标准。与单端I/O相关的原语包括IBUF(输入缓冲器)、IBUFG(时钟输入缓冲器)、OBUF(输出缓冲器)、OBUFT(三态输出缓冲器)和IOBUF(输入/输出缓冲器)。与差分I/O相关的原语包括IBUFDS(输入缓冲器)、IBUFGDS (时钟输入缓冲器)、OBUFDS(输出缓冲器)、OBUFTDS(三态输出缓冲器)、IOBUFDS(输入/输出缓冲器)、IBUFDS_DIFF_OUT(输入缓冲器)和IOBUFDS_DIFF_OUT(输入/输出缓冲器)。 二、SelectIO的逻辑资源 SelectIO的逻辑资源主要是指ILOGIC和OLOGIC资源,它们完成了FPGA引脚到内部逻辑的连接功能,包括组合输入/输出、三态输出控制、寄存器输入/输出、寄存器三态输出控制、DDR输入/输出、DDR输出三态控制、IODELAYE1高分辨率可调整延迟单元及其控制模块。 下面简要介绍ILOGIC和OLOGIC功能。

常用电脑文件名后缀

常用电脑文件名后缀标准化管理部编码-[99968T-6889628-J68568-1689N]

什么是文件后缀名? 我们使用电脑的时候,常会看到文件名(中文或英文最长8位)的后面有一个点,这点后面有几个英文字(最长3位数)例如:某某.zip、某某.txt,那么这点后面的英文字是什么意思呢?这个就是后缀名,表示这个文件的格式,就像.zip就是解压缩格式的文件。比如READ.ME用中文理解就是“读我”,即提示用户在使用软件前先看看这个文件的内容,以获取更多的提示信息。相应的格式必需要相应的程序来打开,这就是我们有时打开下载好的电影、歌曲或图片等,却出现了一个打开方式的选择框,其表示系统内没有安装打开此类文件的程序或者是程序没有自动关联。因此,认识一些常用后缀名,对我们找到正确的运行程序和判别木马等恶意程序有着重要的作用。 首先,我们可以将电脑设置其显示文件的后缀名,方便我们平时认识学习。 打开“我的电脑”→选择菜单栏“工具”→文件夹选项“查看”→给高级设置框内的“隐藏已知文件类型的扩展名”的勾取消→“确定”。 下面将常用后缀名分类说明如下。(*表示任意文件名) 一.系统文件类 *.exe、*.com 可执行文件 *.bat即批处理文件如Autoexec.bat,这个文件在开机时会被自动执行 *.sys系统扩展管理文件如config.sys一次性在开机时自动调入 *.CFG即配置文件(config) *.dll动态链接文件,起到软件与系统桥梁的作用有时候,如损坏会提示找不到某某.dll文件。 *.ini为初始化信息文件(Initiation) *.pif为DOS环境下的可执行文件在Windows下执行时所需要的文件格式 *.grp为分组文件(Group) *.rec即记录器宏文件(Record) *.txt文本文档文件(txt即文本text) *.clp是剪贴板中的文件格式 *.wri即文本文件(Write),它是字处理write.exe生成的文件 *.ttf字体格式文件。 *.ime输入法文件 *.fon、*.fot都是字库文件 *.crd即卡片文件(Card) *.cal为日历文件 *.DAT即数据文件(data) *.HLP即帮助文件(help) *.LOG即日志文件(log)

Xilinx-XADC的使用中文介绍doc资料

Zynq器件XADC的使用(原创) 1.前言 赛灵思的7系列FPGA和Zynq器件创造性地在片上集成了模数转换器和相关的片上传感器(内置温度传感器和功耗传感器),这是相比赛灵思前一代产品来新增加的特性,可在系统设计中免去外置的ADC器件,有力地提高了系统的集成度。本文就这一新模块的使用进行简单介绍,希望对大家有所帮助,当然如有不当之处还请高手指正,以免误导大家,欢迎大家补充。 2.XADC模块介绍 2.1 XADC模块概述 Zynq器件XADC模块包括2个12比特1 MIPS的模数转换器和相关的片上传感器,模数转换器能为系统应用提供通用目的的高精度的模拟接口,下图是XADC模块的框图: XADC模块支持不同的操作模式,如外步触发同步采样模式;可接受不同类型的模拟输入信号,如单端或差分信号;最多能接受17路外部的模拟输入信号。XADC模块也包括一定数量的片上传感器用来测量片上的供电电压和芯片温度,这些测量转换数据存储在一个叫状态寄存器(status registers)的专用寄存器内,可由FPGA内部叫动态配置端口(Dynamic

Reconfiguration Port (DRP))的16位的同步读写端口访问。ADC转换数据也可以由JTAG TAP访问,这种情况下并不需要去直接例化XADC模块,因为这是一个已经存在于FPGA JTAG结构的专用接口,此时因为没有在设计中直接例化XADC模块,XADC模块就工作在一种预先定义好的模式叫缺省模式,缺省模式下XADC模块专用于监视芯片上的供电电压和芯片温度。XADC模块的操作模式是由用户通过DRP或JTAG接口写控制寄存器来选择的,控制寄存器的初始值有可能在设计中例化XADC模块时的块属性(block attributes)指定。 2.2 XADC模块管脚需求 所有的XADC模块专用管脚都位于bank0, 所以都加有_0的后缀。下图表示了XADC的基本输入输出需求: 这有两种推荐配置:图中左边XADC由Vccaux(1.8V)供电,并且用一个外部的1.25V参考源。用外部参考源在精度和热飘移方面可以获得更好的性能,一个磁珠用隔离模拟地和数字地,这可避免较常用的模拟和数字电路共地而把噪声带入模拟电路的缺点;图中右边XADC是用片内的参考源,这时VREFP脚必须按图中所示连接到地。

常用文件格式大全

常用文件格式大全 不同的文件,有不同的文件格式,区别这些文件格式常常是文件名的后缀名不同,现统计常用文件后缀名如下,供读者参考和查阅。 BAT DOS下的批处理文件。Autoexec.bat为自动批处理文件,它是特殊的批处理文件。 EXE 可执行的程序文件,与COM内部结构不相同,最突出是长度没有限制。 COM 可执行的二进制代码系统程序文件,特点非常短小精焊,长度有限制。 ASM 汇编程序文件为二进制代码文件,可以打个比方,它就像BASIC中的.BAS程序文件一样,为不可执行文件。 ASC 代码文件。 BAK 备份文件 LIB 程序库文件 CHK 检查磁盘命令CHKDSK发现的目录或文件分配表中的错误,校正系统后的文件。 TMP 临时文件 SYS 系统配置文件,最典型的如config.sys,一般可以用EDIT进行编辑。 OBJ 目标文件,源程序编译输出的目标代码。 OLD 备份文件,一般是一些程序对系统配置修改后将原文件复制一份存储为该文件格式。 INI 配置文件,不要以为这个文件只有Windows程序需要,DOS下程序也有不少需要它,如3DS与AutoCAD。 INF 安装配置文件,这在WIN95下使用较多。 HLP HELP帮助文件,这个文件一定要重视,因为它是你每使用一个新软件的最好的说明书,几乎99% 的软件都有这个文件,另外,DOS下的一些帮助放在README以后,帮助便没有了,如UCDOS中的REAME.EXE;有单独DOS的命令,若不知道怎么使用,可以试试以下的命令格式:“DIR?或DIR/?”。 DDI 早期映象文件,由DiskDUP IMGDRIVE IMG.EXE展开 IMG 这个文件要注意,有时它是一个图象文件,但更多的时候,它是映象文件,在早期光盘上,此文件使用最多,能常用HD-COPY IMG UNIMG都软件进行解压(注:IMG这个软件为什么一闪就没了呢,这个软件需要热键激活,按下Ctrl+Alt+S+D+X),如果要安装的软件压缩文件由和几个IMG分开压缩,那最好用UNIMG 将它们全部解压缩,然后安装,它安装时提示你“请插入X序列盘”。 ARJ ARJ(ARJ这个以前风眯一时的压缩软件谁人不晓)软件压缩的文件,它的压缩比较高,使用也特方便顺手,只需要“ARJ a -r -v……” RAR 这也是一个压缩文件,传说比ARJ压缩比更高,笔者没有亲手做试验,故不敢下空此结论。 ZIP 当前最流行的压缩文件,谁不知道ZIP呀,WINZIP,再也不是DOS下的那个UNZIG或PKZIP了,兼容,向下兼容,从游戏到软件,差不多都是它压缩的了。 IMD UCDOS中输法的编码字典文件。 PDV UCDOS中的自由表格UCTAB生成的表格文件,它生成的文件可以被WPS调用,也挺方便的。 BAS BASIC中的源程序文件,BASIC可为初学者最为熟悉的编辑语言,它的优点笔者就不在累赘了,注意QBASIC与QUICK BASIC和GW BASIC是有区别。 C C语言中的源程序文件,它不但造就了我们常常为之日夜奋战的精彩电脑游戏,还创造出UNIX操作系统,有口皆碑的好编程软件。 MAK C语言中的工程文件。 COB COBOL语言源程序文件。 PAS PASCAL语言源程序文件。 FOR FORTRAN语言源程序文件。 FOX FOXBASE伪编译程序文件,比PRG短小运行速度快。

电脑文件后缀名含义大全

电脑文件后缀名含义大全 .386 虚拟驱动程序 .3rg 基于dos的屏幕捕捉器 .368 Vxd文件 .8b? photoshop的各种插件 .ACA Microsoft的代理使用的角色文档 .ace 一种压缩格式文档,压缩率甚至超过WinRAR,可以使用WINACE 等工具打开 .acf 系统管理配置 .acm 音频压缩管理驱动程序,为Windows系统提供各种声音格式的编码和解码功能 .acs 同.acm,但保存于本地 .ADE Microsoft Access项目扩展 .ADN Microsoft Access的空白项目模板 .ADP Microsoft Access的项目 .aif

声音文件,支持压缩,可以使用Windows Media Player和QuickTime Player播放 .AIF 音频文件,使用Windows Media Player播放 .AIFC 音频文件,使用Windows Media Player播放 .AIFF 音频文件,使用Windows Media Player播放 .ani 动画光标文件扩展名,例如动画沙漏。 .ans ASCII字符图形动画文件 .ap 应用文件,存在于Dbase,Foxbase,Foxpro系统软件的环境下.app 应用文件,存在于Dbase,Foxbase,Foxpro系统软件的环境下.arc 一种较早的压缩文件,可以使用WinZip,WinRAR,PKARC等软件打开 .arj 压缩文件。可以使用WinZip,WinRAR,PKARC等软件打开 .art 是美国在线最常使用的映象格式,如果使用Windows 2000必须安装补丁才能查看 .asc ASCII文本文件,这些文本可以被所有类型的字处理构件处理。有些系统中也可能会使用这些文件扩展名来表示文件中包含图象

第4节 Xilinx公司原语的使用方法1

第4节Xilinx公司原语的使用方法1 Xilinx 原语 3.4 Xilinx公司原语的使用方法 原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM 等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。 Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的使用方法是类似的。 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB 组件以及G比特收发器组件。下面分别对其进行详细介绍。 3.4.1 计算组件 计算组件值得就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。 表3-6 计算组件清单 DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器 DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。 其在Verilog中的例化模版为: module fpga_v4_dsp48( BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB, CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE, PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP, SUBTRACT); output [17:0]BCOUT; output [47:0] P, PCOUT; //

DC综合全过程及使用的命令

DC综合全过程及使用的命令 DC的初始化文件.synopsys.dc.setup,该文件是隐藏文件,需要用ls –a显示 读取文件 DC支持多种硬件描述格式,.db .v .vhd等 对于dcsh工作模式来说,读取不同的文件格式需要不同的参数 Read -format Verilog[db\vhdl ect] file //dcsh工作模式 对于tcl工作模式来说,读取不同文件格式使用不同的命令。

Read_db file.db //tcl工作模式读取db格式 Read_verilog file.v //tcl工作模式读取verilog格式 Read_vhdl file.v //tcl工作模式读取vhdl格式 读取源程序的另外一种方式是配合使用analyzer命令和elaborate命令; Analyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下 Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体 缺省情况下,elaborate读取的是work目录中的文件 当读取完所要综合的模块后,需要使用link命令将读到DC存储区中的模块或实体连接起来 注意:如果在使用link命令后,出现unresolved design reference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录 Link命令执行后,DC就将模块按照RTL级或者门级的描述将电路连接起来,之后的各种限制条件就可以对该电路的顶层模块施加 DC限制条件施加的对象 针对以下电路成分:输入输出端口、模块、子模块的实例化、单元电路、连线及电路的引脚。在使用DC命令的时候,不要使用模糊的对象,例如,如下面的电路: Set_load 3 Clk 由于在电路中含有名称为CLK的pin、port和net,因此,DC无法知道该处的load是施加在哪个对象上,注意到一般连线会驱动负载,该命令就改为: Set_load 3 [get_nets Clk] TCL mode Set_load 3 find(net,”Clk”)dc_shell mode 路径的划分与合法路径 DC综合的时候是基于路径的优化,对于DC来说,合法的路径必须满足以下条件 路径的起点为输入端口或者是触发器的数据端 路径终点为输出端口或者是触发器的时钟端 DC设定的限制条件的值都是无单位的,这些单位都是由工艺库中给定的 可以用report_lib lib_name来查看所有在工艺库中设定的各个参数的单位 定义电路的工作环境和综合环境

文件扩展名大全

Windows系统文件的扩展名及其分 类对照表 1. "323""H.323 Internet 电话技术" 2. "386""虚拟设备驱动程序" 3. "ACA""Microsoft Agent Character File (HTTP format)" 4. "ACF""Microsoft Agent Character File (HTTP format)" 5. "ACG""Microsoft Agent 预览文件" 6. "ACL""自动更正列表文件" 7. "ACS""Microsoft Agent Character File" 8. "ACW""辅助功能向导设置" 9. "ADE""Microsoft Access 项目扩展" 10. "ADN""Microsoft Access 空白项目模板" 11. "ADP""Microsoft Access 项目" 12. "AIF""AIFF 格式声音" 13. "AIFC""AIFF 格式声音" 14. "AIFF""AIFF 格式声音" 15. "ANI""动画光标" 16. "ASA""活动服务器文档" 17. "ASD""ASF Stream Description File" 18. "ASF""Windows Media 音频/视频文件" 19. "ASP""活动服务器文档" 20. "ASX""Windows Media 音频/视频快捷方式" 21. "AU""AU 格式声音" 22. "AUDIOCD""AudioCD" 23. "A VI""视频剪辑" 24. "A W""应答向导文件" 25. "BKF""Windows 备份文件" 26. "BLG""性能监视器文件" 27. "BMP""BMP 图像" 28. "CA T""安全编录" 29. "CDA""CD 音频曲目" 30. "CDF""频道文件" 31. "CDX""活动服务器文档" 32. "CER""安全证书" 33. "CHK""还原了文件碎片" 34. "CHM""已编译的HTML 帮助文件" 35. "CLP""剪贴板剪贴" 36. "CNF""快速拨号" 37. "COL""HTML 帮助文件" 38. "CPL""控制面板扩展" 39. "CRL""证书吊销列表" 40. "CRT""安全证书" 41. "CSS""级联样式表文档" 42. "CSV""Microsoft Excel 逗号分隔值文件" 43. "CUR""光标" 44. "DB""数据库文件" 45. "DCS""数据库内容源" 46. "DER""安全证书" 47. "DESKLINK""DESKLINK 文件" 48. "DET""Office Data File" 49. "DIB""BMP 图像" 50. "DIC""文本文档" 51. "DIF""Microsoft Excel 数据交换格式" 52. "DOC""Microsoft Word 文档" 53. "DOCHTML""Microsoft Word HTML 文档" 54. "DOCMHTML""DOCMHTML 文件" 55. "DOT""Microsoft Word 模板" 56. "DOTHTML""Microsoft Word HTML 模板" 57. "DQY""Microsoft Excel ODBC 查询文件" 58. "DRV""设备驱动程序" 59. "DSN""数据源名称" 60. "DUN""拨号网络文件" 61. "DVD""DVD" 62. "ECS""Exchange Server 内容源" 63. "ELM""Microsoft Office 主题文件" 64. "EMF""EMF 图像" 65. "EML""Outlook Express 邮件消息" 66. "EXC""文本文档" 67. "FAD""Office 数据文件" 68. "FA V""FA V 文件" 69. "FCS""文件共享内容源" 70. "FFA""文件检索索引" 71. "FFL""文件检索索引" 72. "FFT""文件检索索引" 73. "FFX""文件检索索引" 74. "FON""字体文件" 75. "FPDOCLIB""Microsoft FrontPage Document Library" 76. "FPHOMEOP""Microsoft FrontPage Home Page Open" 77. "FPHOMEPG""Microsoft FrontPage 主页" 78. "FPHTML""Microsoft FrontPage HTML 文档" 79. "FPLIST""Microsoft FrontPage List" 80. "FPNOPUB""Microsoft FrontPage Dont Publish" 81. "FPOPEN""Microsoft FrontPage 打开文件" 82. "FPSURVEY""Microsoft FrontPage Survey" 83. "FPWEB""FPWEB 文件" 84. "FRG""FRG 文件" 85. "GIF""GIF 图像"

synopsys DC10.03图文安装配置详解

喾林原创 Synopsys DC10.03安装配置 1、需准备安装包: 1)、Synopsys DC(design compiler)安装包 2)、SCL 安装包(注:此包为synopsys license 管理)。 3)、Synopsys 图像安装工具:installer2.0及以上均可。 (注:图形安装操作简单,不易出错,故采用图形安装界面) 4)、Synopsys license 制作工具( EFA LicGen 0.4b 和Synopsys SSS Feature Keygen )。 2、开始安装DC : 1)、启动图形安装界面 于linux 系统下解压installer2.0包(在windows 下解压文件易损坏)。解压后运行setup.sh 得如图(一)所示界面。 图 (一)

喾林原创点击“start ”有如图(二)所示界面开始安装。在“Source ”栏选中DC 安装文件所在上层目录。“Done ”后“Next ”(此次“Next ”时间较长,耐心等待)。 图 (二) 之后可一直“NEXT ”到如图(三)所示。 图 (三)

在该界面勾选linux选项即可,继续下一步到如图(四)所示。选择安装路径后继续下一步直到结束。 喾林原创 图(四) 至此DC安装结束。 3、开始安装SCL: 此安装与DC安装步骤一直,几乎没有差别,唯一不同的就是安装路径不同。 4、license的制作: License的制作是在windows下制作的。

1)、打开EFA LicGen 0.4b文件夹运行LicGen.exe程序出现如图(五)所示界面。 喾林原创 图(五) 点击“OPEN”选择Synopsys.lpd文件,“打开”。回到图(五)所示界面。勾选上Custon、Use Daemon及最后一个Custon。

常见文件扩展名大全

常见文件扩展名大全

常见文件扩展名大全 2004-4-30 伟网动力 A 对象代码库文件 AAM Authorware shocked文件 AAS Authorware shocked包 ABF Adobe二进制屏幕字体 ABK CorelDRAW自动备份文件 ABS 该类文件有时用于指示一个摘要(就像在一篇有关科学方面的文章的一个摘要或概要,取自abstract)ACE Ace压缩档案格式 ACL CorelDRAW 6键盘快捷键文件 ACM Windows系统目录文件 ACP Microsoft office助手预览文件 ACR 美国放射医学大学文件格式 ACT Microsoft office助手文件 ACV OS/2的驱动程序,用于压缩或解压缩音频数据 AD After Dark屏幕保护程序 ADA Ada源文件(非-GNAT) ADB Ada源文件主体(GNAT);HP100LX组织者的约定数据库 ADD OS/2用于引导过程的适配器驱动程序 ADF Amiga磁盘文件 ADI AutoCAD设备无关二进制绘图仪格式 ADM After Dark多模块屏幕保护;Windows NT策略模板 ADP FaxWork用于传真调制解调器的交互安装文件;Astound Dynamite文件 ADR After Dark随机屏幕保护;Smart Address的地址簿 ADS Ada源文件说明书(GNAT) AFM Adobe的字体尺度 AF2,AF3 ABC的FlowChat文件 AI Adobe Illustrator格式图形 AIF,AIFF 音频互交换文件,Silicon Graphic and Macintosh应用程序的声音格式 AIFC 压缩AIF AIM AOL即时信息传送 AIS ACDSee图形序列文件;Velvet Studio设备文件 AKW RoboHELP的帮助工程中所有A-关键词 ALAW 欧洲电话音频格式 ALB JASC Image Commander相册 ALL 艺术与书信库 AMS Velvet Studio音乐模块(MOD)文件;Extreme的Tracker模块文件 ANC Canon Computer的调色板文件,包含一系列可选的颜色板 ANI Windows系统中的动画光标 ANS ANSI文本文件 ANT SimAnt For Windows中保存的游戏文件 API Adobe Acrobat使用的应用程序设计接口文件 APR Lotus Approach 97文件

使用Xilinx CORE Generator

使用Xilinx CORE Generator心得 初步使用Xilinx CORE Generator: 参考书籍:《Xilinx ISE 5.x 使用详解》EDA先锋工作室 P63-P72:IP核生成工具——CORE Generator 1. 对于如何在工程中加入IP核,是很简单的,我在未看书之前,就可根据提示挑选适当的核,对核进行参数设置,将核加入工程。 2. 接下来是如何使用,在这里,由于我主要使用VHDL语言,仿真工具用ModelSim6.0,综合工具主要使用Synplify7.7,我就只说在这样的环境下如何对该IP核进行元件例化,进行项目配置,并进行仿真与综合。 2.1 元件例化 可使用ISE的Laguage Template,也就是Xilinx 6.2 ISE中工具栏右上角的小灯泡,在COREGEN目录下,你会发现,你所用到的IP核的例化语句已经出现在模板里,拷过去就可以直接用了(当然你可能也要视情况进行必要的改动)。 3. 仿真 这里,最主要的问题是库,由于使用了IP核,所以要把XilinxCroeLib加入ModelSim库中。我的经验是:先在当前工程的目录下创建一个xilinxcorelib库,然后把该库文件剪切到modelsim根目录下,最后在modelsim下,选中该库,点击右键选择Edit,将路径高到modelsim下。然后将xilinx\vhdl\src\xilinxcorelib编译到该库中。此时要注意,由于库文件的关联性,第一次不可能全部编译通过,连续三次后,大多数核就在库中,只有少数几个不能通过编译。 4. 综合 由于综合过程中,提示如下(下面是我在comp.arch.fpga上所发的问题): In my project,there's a xilinx IP core. I want to use the synplify7.7 to synthesize it, but there's a warning when synthesize . The warning is : @W: CD280 :"G:\project\itu656_dec\itu656_Decoder.vhd":29:10:29:19|Unbound component counter_11 mapped to black box @W: CD280 :"G:\project\itu656_dec\itu656_Decoder.vhd":37:10:37:18|Unbound component counter_4 mapped to black box my project nane is itu656_dec : a decoder for itu 656 video The following code has been used in my project: component counter_11 port ( Q: OUT std_logic_VECTOR(10 downto 0); CLK: IN std_logic; CE: IN std_logic; ACLR: IN std_logic); end component; component counter_4

synopsys简易教程

以.cshrc 及用户根目录下的.synopsys_vss.setup .synopsys_dc.setup 已经配置为前提)1.创建工作目录; 2.编写vhdl源程序; 3.编写.synopsys_vss.setup 和.synopsys_dc.setup文件; 4.编译vhdl源程序; 5.运行vhdldbx 仿真器; 6.运行synopsys的综合器; 7.完成综合后的门级仿真; 以一个一位加法器为例,进行具体说明(用户界面为CDE): 1)创建adder 目录: 可以在资源管理器中完成,也可以在unix环境下完成:mkdir adder; 2)在adder目录下创建work目录; 3)编写.synopsys_vss.setup文件并存入adder目录;.synopsys_vss.setup的内容如下:WORK >DEFAULT DEFAULT:work TIMEBASE = NS 4)编写一位加法器的源程序(adder1.vhd)并存入adder目录下: library ieee; use ieee.std_logic_1164.all; entity adder1 is port(din1 : in std_logic; din2 : in std_logic; cin : in std_logic; dout: out std_logic; cout: out std_logic); end adder1; architecture rtl of adder1 is begin dout <= din1 xor din2 xor cin; cout <= (din1 and din2) or (cin and (din1 xor din2)); end rtl; 5)编写一位加法器的测试基准(即test_bench)并存入adder目录下:(tb_adder1.vhd)library ieee; use ieee.std_logic_1164.all; entity tb_adder1 is end tb_adder1; architecture rtl of tb_adder1 is component adder1 is port(din1 : in std_logic; din2 : in std_logic; cin : in std_logic;

Xilinx原语的使用方法1

Xilinx原语的使用方法1 3.4 Xilinx公司原语的使用方法 原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C++中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。在实现过程中的翻译步骤时,要将所有的设计单元都转译为目标器件中的基本元件,否则就是不可实现的。原语在设计中可以直接例化使用,是最直接的代码输入方式,其和HDL语言的关系,类似于汇编语言和C语言的关系。 Xilinx公司提供的原语,涵盖了FPGA开发的常用领域,但只有相应配置的硬件才能执行相应的原语,并不是所有的原语都可以在任何一款芯片上运行。在Verilog中使用原语非常简单,将其作为模块名直接例化即可。本节以Virtex-4平台介绍各类原语,因为该系列的原语类型是最全面的。其它系列芯片原语的使用方法是类似的。 Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM 组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。 3.4.1 计算组件 计算组件指的就是DSP48核,也有人将其称为硬件乘法器,功能描述如表3-6所示。 表3-6 计算组件清单 DSP48 其结构为一个18*18比特的有符号乘法器,且在后面还级联了一个带有可配置流水线的3输入加法器 DSP48核由一个18比特的乘法后面级联一个48比特的加法器,乘法器和加法器的应用位宽分别可以在18、48比特内任意调整。其在乘加模块中有广泛应用,特别是各类滤波器系统中,不仅可以提高系统稳定性,还能够节省逻辑资源且工作在高速模式下。其在Verilog中的例化模版为: module fpga_v4_dsp48( BCOUT, P, PCOUT, A, B, BCIN, C, CARRYIN,CARRYINSEL, CEA, CEB, CEC, CECARRYIN, CECINSUB, CECTRL, CEM, CEP, CLK, OPMODE, PCIN, RSTA, RSTB, RSTC, RSTCARRYIN, RSTM, RSTP,

文件名后缀大全(肯定用的上)

后缀名大全 A: 1.ace:ace.exe或winace生成的压缩文件 2.ain:ain是一种压缩文件格式,解开ain需要用ain.exe。在网上可以找到。 可以在各大的FTP pub/msdos utility之类地方寻找ain.exe 3.arj,a01,a02...: arj是一种非常常见的压缩文件格式,它可以支持带目录,多文件压缩, 一般FTP中DOSutility目录下都可以找到arj.exe,一般的版本有2.4 2,2.382.50等,其文件格式是通用的,不存在格式不认问题。 a01,a02,a03是arj在多文件压缩时后面文件的缺省文件名。 展开arj文件可以用arj x-va-y filename.arj 在windows下可以试试用winzip展开。 4.asp: .asp文件通常指的是Active Server Pages文件,这个文本文件可以 包括下列部分的任意组合:文本/HTML标记/ASP脚本命令,可以用 ie浏览器直接打开,也可以用记事本打开编辑。 .asp文件也可能是一种文档格式的文件,可以用cajviewer打开。 5.avi: 一般用windows自带的媒体播放器就可以播放。 如果没有图象只有声音,则可能是mpeg4格式,需要装插件。 如果有单独的字幕文件,则可以用其它播放器。 B: 1.BHX(BINHEX): BinHex是苹果机器的一种编码方式. WinZip可以解码.将email以文本方式存盘,扩展名为.BHX, 就可以直接用WinZip解压了. 2..bin 光盘映象文件,可以: a.用Bin2ISO将bin转成ISO文件,然后用WinImage解开. 注意:有些BIN文件实际上就是ISO文件如果上面的办法有问题 可以直接将后缀改成iso,然后用WinImage解解看 b.用ISOBuster直接解BIN. c.用daemon直接将BIN文件虚拟成光驱 C: 1.caj:cajviewer,CAJ文件浏览器是中国学术期刊(光盘版)电子杂志社(CAJEJPH)的产品。它是为中国期刊网(https://www.360docs.net/doc/e64038652.html,)的全文检索,浏览开发的。 2.cdi:光盘映像文件,用DISKJuggle就可以打开 3.cdr:CorelDraw 4.cdp:Nti CdMaker做的光盘Image.用Nti CdMaker的FileCopy刻. 5.cfm: www浏览器(服务器支持,类似asp,php,jsp)or文本编辑器看源码 6.chi:chm(html help)的索引,和chm文件一起使用 7.chm: 基于Html文件格式的帮助文档,在IE4.0以上可以双击直接打开。

启动dc_shell工具的.synopsys.setup文档

设置启动dc_shell-t工具的 .synopsys.setup文件 Author:周建伟 Company:西安邮电大学SOC组 Date:2013.10.30 摘要:若你在读不进你的库,即在你的运行报告中总是有:warning:Can?t read link_library file …your_library.db?,这边文档会对你有一定的帮助

逻辑综合环境 启动文件 启动文件用来指定综合工具所需要的一些初始化信息。DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。启动时,DC会以下述顺序搜索并装载相应目录下的启动文件: DC安装目录($DC_PATH/admin/setup) 用户主目录 工具启动目录 注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置 本文档重在讲述怎么设置工具启动目录 1、把inst_dir/admin/setup/.synopsys_dc.setup文件拷贝到你DC脚本目录下(也就是和你 脚本在同个目录下) 2、在.synopsys_dc.setup文件的第92行,即set link_force_case “check_reference”命令下 修改内容如下: A、set lib_path /library/smic18/feview~2/version2.2(注:lib_path为你smic18库安装 目录,不同于DC安装目录) B、set link_library [list * $lib_path/STD/Synopsys/smic18_ss.db \ $lib_path/IO/Synopsys/smic18IO_line_ss.db \ $lib_path/IO/Synopsys/smic18IO_stagger_ss.db ] C、set search_path [list . ${synopsys_root}/libraries/syn ${synopsys_root}/dw/syn_ver \ ${synopsys_root}/dw/sim_ver \ $lib_path/STD/Synopsys $lib_path/IO/Synopsys ] D、set target_library [list $lib_path/STD/Synopsys/smic18_ss.db \ $lib_path/IO/Synopsys/smic18IO_line_ss.db \ $lib_path/IO/Synopsys/smic18IO_stagger_ss.db ] E、set synthetic_library “” set command_log_file “./command.log” set designer “zjw” set company “soc of xupt”