千兆以太网卡芯片A_D转换电路的设计与实现

收稿日期:2005211230; 定稿日期:2006204219基金项目:华中科技大学博士后基金资助项目

千兆以太网卡芯片A/D 转换电路的设计与实现

朱全庆1,李海华2,张道礼1

(1.华中科技大学电子科学与技术系,湖北武汉 430074;2.上海交通大学微纳科学技术研究院,上海 200030)

摘 要: 介绍了一种用于千兆以太网卡芯片的8位125MS/s CMOS 流水线A/D 转换电路的设计,包括体系结构设计、电路设计与仿真、版图设计。该A/D 转换电路经过TSMC 0.13μm 1P8M CMOS 工艺验证,工作电压为1.5V/2.7V 。芯片测试结果表明,设计的A/D 转换电路能够满足千兆以太网卡芯片的性能要求。关键词: A/D 转换电路;流水线结构;千兆以太网

中图分类号: TN432 文献标识码: A 文章编号:100423365(2006)0420403204

Design and Implementation of an A/D Converter for Gigabit Ethernet

ZHU Quan 2qing 1,L I Hai 2hua 2,ZHAN G Dao 2li 1

(1.Dept.of Elect ronic Science and Technology ,H uaz hong Uni versit y of S cience and Technolog y ,W uhan ,H ubei 430074;

2.Research I nstit ute of Micro/N ano S cience and Technology ,S hanghai J iaotong Universit y ,S hanghai 200030,P.R.China )

Abstract :

An 82bit ,125mega 2sample/s CMOS A/D converter was designed for gigabit Ethernet chip.The sys 2tem architecture ,circuit design and simulation ,and chip layout design are described.Verified with TSMC ’s 0.13

μm 1P8M process ,the A/D converter circuit can operate at 1.5V/2.7V supply voltage.Test results show that the circuit can meet the performance requirement of the gigabit Ethernet IC.

K ey w ords : A/D converter ;Pipeline structure ;G igabit Ethernet

EEACC :

1265H ;2570D

1 引 言

IEEE 802.3标准,通常称之为以太网,是由施

乐公司首先提出的一种数字媒体接口,后被IEEE 接受。1985年,IEEE 发布了第一版802.3标准,其核心内容是CSMA/CD (载波监听冲突检测)协议。它支持传输速率10Mb/s 的同轴电缆,最大传输电缆小于100m 。1990年,IEEE 颁布了802.3i 标准,即10BASE 2T ,传输速率达到10Mb/s 。1995年3月,IEEE 802.3u 规范正式通过,预示快速以太网时代来临。IEEE 802.3u 支持100BASE 2T4、100BASE 2TX 和100BASE 2FX ,使通讯速率达到100Mb/s 。1998年6月,IEEE 正式通过千兆以太网标准802.3z [1]。

本文主要研究千兆以太网卡芯片A/D 转换电路的设计与实现,包括体系结构设计、电路设计与仿

真,以及芯片版图设计。

2 体系结构设计

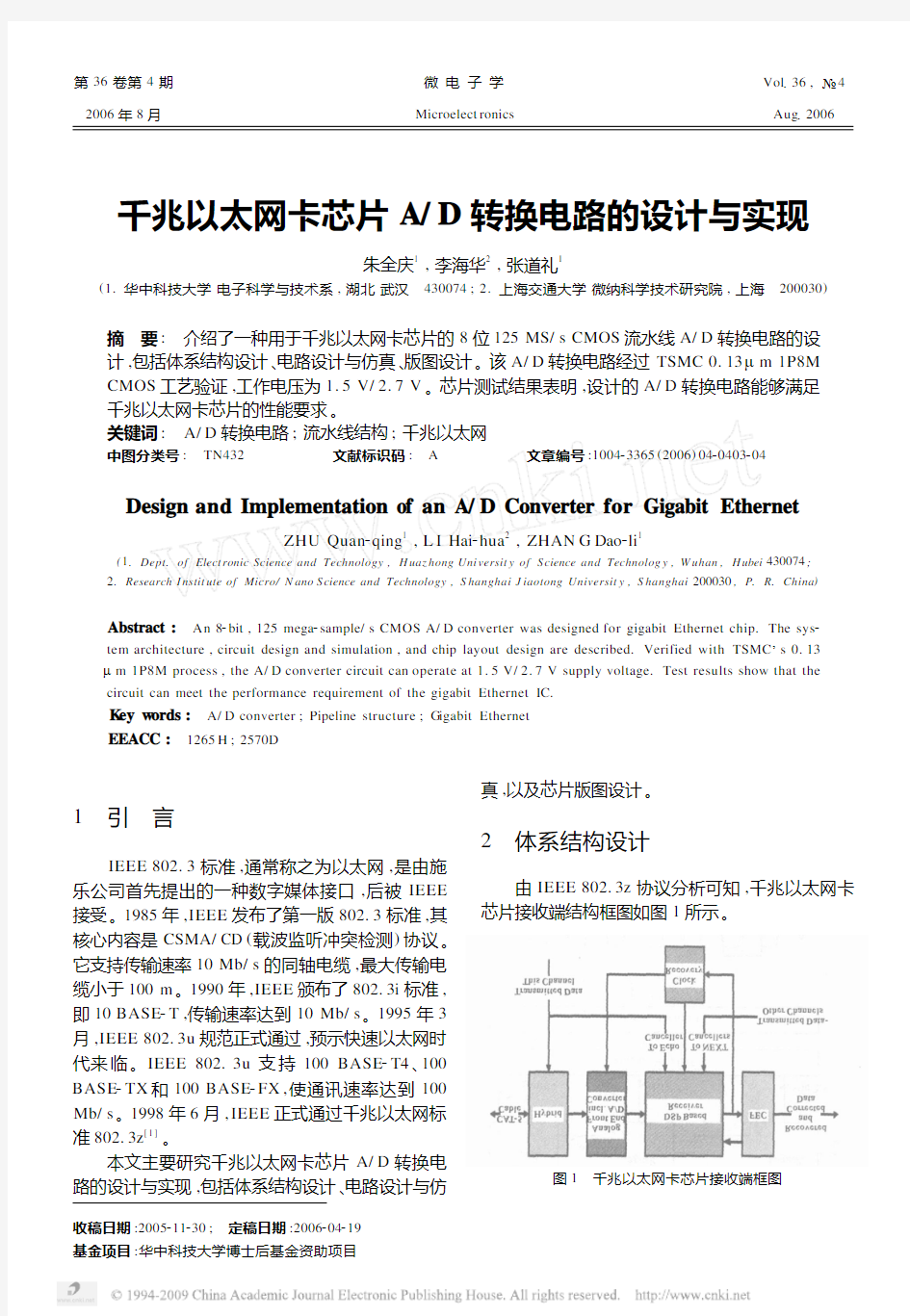

由IEEE 802.3z 协议分析可知,千兆以太网卡

芯片接收端结构框图如图1所示

。

图1 千兆以太网卡芯片接收端框图

第36卷第4期

2006年8月

微电子学

Microelect ronics

Vol 136,№4Aug 12006

从第五类双绞线传输过来的数据,通过Hybrid 接口(支持同时发送和接收数据),采用模拟前端电路,如A/D 转换器,转换成数字信号;经过数字信号处理,如自适应均衡、时钟回复、回波消除(Echo Canceller )、近端串扰消除(N EXT Canceller )等,恢

复出数据和时钟信号。采用前向纠错编码(FEC ),在强干扰和串扰影响下,纠正接收信号中的误码,找回6dB 的信噪比[2]。其中,数字信号处理要求A/D 转换器的精度必须大于6.5比特,以正确实现信号均衡、回波消除、时钟恢复等功能。考虑到工艺漂移、电源噪声等因素的影响,设定A/D 转换器的精度为8比特,速率125Msample/s 。

目前常用的A/D 转换器架构有:Flash A/D 转换器、流水线型A/D 转换器、逐次逼近型A/D 转换器,等等。与其他结构A/D 转换器相比,流水线型A/D 转换器具有高吞吐量、对运放失调要求较低、

功耗和硬件与转换位数线性相关等优点,适合用于高速率、高精度的应用。基于以上考虑,我们选用流水线型结构设计A/D 转换器。

由于流水线型A/D 转换器对第一级模拟电路的要求最为苛刻(如增益准确度、失调电压等),综合考虑数据信号延时,所设计的A/D 转换器采用两级2.5比特级(3比特减去一个水准)接一个4比特Flash 级。电路结构框图如图2所示。每一2.5比

特级包含一个乘法D/A 转换器(MDAC )和一个子A/D 转换器,以及一些解码电路。每一级输出的比

特经过延迟,用于冗余符号数字(RSD )纠正电路。最后,采用缓冲器并行输出

。

图2 流水线A/D 转换器结构框图及时序

3 电路设计与仿真

2.5比特流水线级中,电容乘法D/A 转换器结

构(MDAC )如图3所示

。

图3 2.5比特乘法D/A 转换器(MDAC )

为了简化,采用单端结构进行说明。在采样阶段(φS ),输入信号被采样到4个相同的电容,这时运放被断开。在保持阶段(φH ),其中一个电容联入反馈,其他三个电容根据子A/D 转换器输出,分别连到基准电平-V ref ,0,+V ref 上。相应传递函数为:

V out =43V in -D sub 3V ref

(1)式中,D sub 为-3到3之间的整数,与子A/D 转换器输出的000,001,…,110相对应。

乘法D/A 转换器中,运算放大器采用两级CMOS 运放,采用RC (电路电容)进行米勒补偿,如图4所示(差分电路一端)。功耗,如图5所示

。

图4 MDAC 中的运算放大器电路结构

第一级为Fold Cascade (反转层叠)电路结构。

其共模反馈电路使用开关电容(SC )电路实现。采

用这种结构,能够实现高直流增益、大带宽和低电流。设计中

,运放的具体指标为开环增益65dB ,增益带宽积1.4GHz ,V pp 差分信号摆幅1.5V [3]。

2.5比特流水线级中的子A/D 转换器采用Flash 架构,包含6个比较器。比较器输出驱动MDAC 开关和一些解码逻辑,将热温度计编码转换成二进制编码输出。由于每级精度低,加上采用RSD 纠正电路,放松了比较器失调电压的要求。这样可以采用动态比较器,不消耗直流功耗,如图5

所示。图5 动态比较器

比较器的开关阈值由晶体管宽度W 1、W 2决定:

V threshol d =

W 2W 1V ref =

W 2

W 1

(V ref p -V r ef n )(2)

用于A/D 转换和D/A 转换所需的17个参考

电压(V r ef p 、V r ef p 7、V r ef p 6、V r ef p 5、V r ef p 4、V r ef p 3、V r ef p 2、V ref p 1、V com 、V r ef n 1、V r ef n 2、V r ef n 3、V r ef n 4、V ref n 5、V ref n 6、

V ref n 7、V r ef n )采用电阻串联生成,电路如图6所示[4]

。

图6 参考电压生成电路

4 版图设计与硅片验证

采用Cadence 公司V IR TU RSO ,设计A/D 转

换电路的版图。对于ADC 版图设计,匹配性和对称性至关重要。同时,ADC 是一个数字模拟混合系统,版图设计中需要考虑电源噪声和衬底噪声的影响。在版图设计过程中,采用了如下方法:将匹配的器件尽可能放在一起;器件与其电流方向一致;采用Dummy 器件;保持器件对称性;相同的差分信号线;模拟电路版图外围双层保护环;模拟模块、数字模块单独接相应电源;采用片内电源与地之间解耦电容。设计的A/D 转换器的最终版图如图7所示

。

图7 设计的A/D

转换电路版图

图8 975.5k Hz 输入信号ADC 输出频谱

本文提出的A/D 转换电路已用于千兆以太网

卡芯片设计中,并通过硅片验证,采用TSMC 0.13μm 单层多晶硅8层金属(1P8M )工艺实现。该A/D 转换器的芯片面积为0.0745mm 2。测试时采用惠普公司8111A 函数脉冲信号发生器产生正弦输入信号,使用安捷伦公司16702A 逻辑分析仪,观测输出的数字信号。输入信号为975.5k Hz ,采样率

为125M Hz的频谱如图8所示。该A/D转换器的无杂散动态范围(SFDR)为47.9dB。表1列出千兆以太网A/D转换器的主要性能指标。

表1 A/D转换电路性能指标

参数/单位数值参数/单位数值

电源电压/V 1.5/2.7SFDR/dB47.9

精度/bit7.4SNDR/dB46.5

芯片面积/μm272×274

0.13μm N阱1P8M CMOS工艺

5 结束语

本文根据IEEE802.3协议和千兆以太网卡芯片的系统需要,确定了A/D转换电路的体系结构,进而进行电路设计与仿真、版图设计与硅片验证。测试结果表明,该A/D转换电路能够满足千兆以太网卡芯片的要求。本文对设计千兆以太网网卡芯片以及其他通讯系统芯片具有重要的指导意义。

参考文献:

[1]Carrier sense multiple access with collision detection

(CSMA/CD)access method and physical layer specifi2

cations[S].IEEE802.3.2002.

[2]Hatamian M,Agazzi O E,Creigh J,et al.Design

considerations for gigabit Ethernet1000BASE2T

twisted pair transceivers[A].IEEE Custom Integrat2

ed Circuit Conf[C].Santa Clara,CA,USA.1998.

3352342.

[3]Baker R J,Li H W,Boyce D E.CMOS circuit design,

layout,and simulation[M].United States of Ameri2 ca,Wiley2IEEE Press,1998.

[4]Sumanen L.Pipeline analog2to2digital converters for

wideband wireless communications[D].Ph D Thesis,

Helsinki University of Technology,Department of

Electrical and Communication Engineering,Finland,

ISSN9512222622321,2002.1082109

作者简介:朱全庆(1974-),男,四川省成

都市人,1997年获华中理工大学电子材料

与元器件专业学士学位;2000年获华中科

技大学微电子学与固体电子学专业硕士学

位;2003年获华中科技大学模式识别与智

能系统专业博士学位,现在华中科技大学

电子科学与技术系进行博士后研究,主要

研究方向为数模混合集成电路设计。

(上接第402页)

尺寸的三栅MOS器件,栅氧化层厚度t ox的变化范围很小,对于阈值电压的影响也很小。因此,在设计器件参数时,不必考虑t ox和H对阈值电压的影响。

4 结 论

本文给出了一个解析的T G MOSFET阈值电压模型。从该模型可以看出,对三栅MOSFET阈值电压影响最为显著的是多晶硅栅的掺杂浓度、硅体宽度W和沟道掺杂浓度N A;阈值电压将随硅体宽度W的增大而减小,随沟道掺杂浓度N A的减小而降低,而对器件参数t ox和H则不敏感。

参考文献:

[1]Doris B,Ieong M,Kanarsky T,et al.Extreme scaling

with ultrathin Si channel MOSFET’s[M].IEDM

Tech Dig[C].San Francisco,CA,USA.2002.2672

270.

[2]K im K,Fossum J G.Double2gate CMOS:symmetri2

cal2versus asymmertrical2gate devices[J].IEEE

Trans Elec Dev,2001,48(1):2942299.

[3]Huang X,Lee W C,Kuo C,et al.Sub250nm Fin2

FET:PMOS[A].IEDM Tech Dig[C].Piscataway,

USA.1999.67270.[4]Trivedi V P,Fossum J G.Scaling f ully depleted SOI

CMOS[J].IEEE Trans Elec Dev,2003,50(10): 209522103.

[5]Chau R,Doyle B,Kavalieros J,et al.Advanced de2

pleted2substrate transistors:single2gate,double2gate,

and tri2gate[A].Proc Int Conf Sol Sta Dev and Mater

[C].Nagoya,Japan.2002.68269.

[6]Doyle B,Boyanov B,Datta S,et al.Tri2gate f ully de2

pleted CMOS transistors:fabrication,design,and lay2 out[A].Proc VL SI Tech Symp[C].Kyoto,Japan.

2003.1332134.

[7]Zeng C,Barlage D W.Analytical threshold voltage

model for design and evaluation of tri2gate MOSFETs

[A].Int Semicond Dev Res Symp[C].Washington D

C,USA.2003.2322233.

[8]夏志良,刘晓彦,刘恩峰,等.亚100nm多栅MOSFET

的三维模拟[J].半导体学报,2003,24(5):1402143.

[9]Suzuki K,Tanaka T,Tosaka Y,et al.Analytical sur2

face potential expression for thin2film double2gate SOI MOSFETs[J].Sol Sta Elec,1994,37(2):3272332.

作者简介:刘 建(1981-),男(汉族),湖

北荆州人,硕士研究生,2003年毕业于武

汉大学应用物理系,获理学学士学位,现从

事新型半导体器件模型的研究。

电子技术课程设计报告_波形产生及变换

电子技术课程设计报告 ——波形产生及变换 姓名:Frege 专业班级:电气合1402 所属学院:电气工程与自动化学院 指导老师:王允建 2016 年 7 月 1 日

波形产生与变换电路的设计 摘要 波形发生器广泛地应用于各大院校和科研场所。随着科技的进步,社会的发展,单一的波形发生器已经不能满足人们的需求。本文利用555定时器构成多谐振荡器产生方波,然后分别通过积分、滤波电路输出三角波、正弦波、三倍频率正弦波。放大器件为LM324N四路放大器,以积分、傅立叶分解等为理论基础,通过运放构成的各种滤波电路对方波进行各种波形变换。它的制作成本不高,电路简单,使用方便,有效的节省了人力,物力资源,具有实际的应用价值。实验包括仿真与实际连线两步,仿真采用Multisim仿真软件,连线采用面包板。 关键词:555定时器;LM324N四路放大器;Multisim仿真;面包板接线

The design of the signal and conversion circuit Abstract Waveform generators are widely used in major universities and research establishments. With advances in technology, social development, a single waveform generator already cannot satisfy people's needs. In this paper constitutes a 555 timer multivibrator generating a square wave, then respectively through integral, filter circuit and output triangle wave, sine wave, triple frequency sine wave. Amplifying device is LM324N, based on the theory of integral, Fourier decomposition and so on, through the op-amp composition of various filter circuit wave for the various waveform transformation. Its production cost is not high, the circuit is simple, easy to use, effectively saving manpower, material resources, have practical value. Experiments include simulation and actual connection step, simulation using Multisim simulation software, connect using breadboard. Keywords:555 timer; LM324N four-way amplifier; Multisim simulation; breadboard connection

电子竞赛常用CD40系列芯片资料

例:CD4001/74LS02(四双输入或非门)1、简要功能介绍 2、引脚功能图 3、应用实例电路图 图* 4001构成视力保护器

例:CD4011/74LS08(四2输入端与非门) 1、引脚功能图 逻辑表达式:Y = A.B (1)当X=0、Y=0时,将使两个NAND门之输出均为1,违反触发器之功用,故禁止使用。如真值表第一列。 (2)当X=0、Y=1时,由于X=1导致NAND-A的输出为”1”,使得NAND-B的两个输入均为”1”,因此NAND-B的输出为”0”,如真值表第二列。 (3)当X=1、Y=0时,由于Y=0导致NAND-B的输出为”1”,使得NAND-1的两个输入均为””1,因此NAND-A的输出为”0”,如真值表第三列。 (4)当X=1、Y=1时,因为一个””1不影响NAND门的输出,所以两个NAND门的输出均不改变状态,如真值表第四列。 3、应用实例电路图

例:CD4012/74LS20(双4输入端与非门)

例:CD4017/CD4022(十进制计数/分配器) 1、简要功能介绍 CD4017 是5 位Johnson 计数器,具有10 个译码输出端,CP、CR、INH 输入端。时钟输cd4017入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH 为低电平时,计数器在时钟上升沿计数;反之,计数功能无效。CR 为高电平时,计数器清零。 2、引脚功能图 CO:进位脉冲输出 CP:时钟输入端 CR:清除端 INH:禁止端 Q0-Q9 计数脉冲输出端 VDD:正电源 VSS:地 3、应用实例电路图

简易波形发生器设计报告

电子信息工程学院 硬件课程设计实验室课程设计报告题目:波形发生器设计 年级:13级 专业:电子信息工程学院学号:201321111126 学生姓名:覃凤素 指导教师:罗伟华 2015年11月1日

波形发生器设计 波形发生器亦称函数发生器,作为实验信号源,是现今各种电子电路实验设计应用中必不可少的仪器设备之一。 波形发生器一般是指能自动产生方波、三角波、正弦波等电压波形的电路。产生方波、三角波、正弦波的方案有多种,如先产生正弦波,再通过运算电路将正弦波转化为方波,经过积分电路将其转化为三角波,或者是先产生方波-三角波,再将三角波变为正弦波。本课程所设计电路采用第二种方法,利用集成运放构成的比较器和电容的充放电,实现集成运放的周期性翻转,从而在输出端产生一个方波。再经过积分电路产生三角波,最后通过正弦波转换电路形成正弦波。 一、设计要求: (1) 设计一套函数信号发生器,能自动产生方波、三角波、正弦波等电压波形; (2) 输出信号的频率要求可调; (3) 根据性能指标,计算元件参数,选好元件,设计电路并画出电路图; (4) 在面包板上搭出电路,最后在电路板上焊出来; (5) 测出静态工作点并记录; (6) 给出分析过程、电路图和记录的波形。 扩展部分: (1)产生一组锯齿波,频率范围为10Hz~100Hz , V V 8p -p =; (2)将方波—三角波发生器电路改成矩形波—锯齿波发生器,给出设计电路,并记录波形。 二、技术指标 (1) 频率范围:100Hz~1kHz,1kHz~10kHz ; (2) 输出电压:方波V V 24p -p ≤,三角波V V 6p -p =,正弦波V V 1p -p ≥; (3) 波形特性:方波s t μ30r < (1kHz ,最大输出时),三角波%2V <γ ,正弦波y~<2%。 三、选材: 元器件:ua741 2个,3DG130 4个,电阻,电容,二极管 仪器仪表: 直流稳压电源,电烙铁,万用表和双踪示波器 四、方案论证 方案一:用RC 桥式正弦波振荡器产生正弦波,经过滞回比较器输出方波,方波在经过积分器得到三角波。

波形转换电路的设计

学号: 课程设计 题目波形转换电路的设计 学院理学院 专业电子信息科学与技术 班级 姓名 指导教师 2012 年 1 月23 日

课程设计任务书 学生姓名:专业班级:电信科xxx班 指导老师:工作单位:武汉理工大学理学院 题目:波形转换电路的设计 初始条件:直流稳压电源一台、万用表一块、面包板一块、元器件若干、剪刀、镊子等必备工具 要求完成的主要任务:(包括课程设计工作量及其技术要求以及说明书撰写等具体要求)1、技术要求: 设计一种波形转换电路,要求产生频率可调的方波,并且能够实现方波转换为三角波。 测试并且记录下不同频率下的方波和三角波的波形图,以及输出电压值。 2、主要任务: (一)设计方案 (1)按照技术要求,提出自己的设计方案(多种)并进行比较; (2)以集成电路运算放大器LF353为主,设计一种波形转换电路(实现方案); (3)依据设计方案,进行预答辩; (二)实现方案 (4)根据设计的实现方案,画出电路图; (5)查阅资料,确定所需各元器件型号和参数; (6)在面包板上组装电路; (7)自拟调整测试方法,并调试电路使其达到设计指标要求; (8)撰写设计说明书,进行答辩。 3、撰写课程设计说明书: 封面:题目,学院,专业,班级,姓名,学号,指导教师,日期 任务书 目录(自动生成) 正文:1、技术指标;2、设计方案及其比较;3、实现方案; 4、调试过程及结论; 5、心得体会; 6、参考文献 成绩评定表 时间安排: 课程设计时间:20周-21周 20周:明确任务,查阅资料,提出不同的设计方案(包括实现方案)并答辩; 21周:按照实现方案进行电路布线并调试通过;撰写课程设计说明书。 指导教师签名:年月日 系主任(或负责老师)签名:年月日

运放组成的波形发生器电路设计

运放组成的波形发生器电 路设计 This model paper was revised by the Standardization Office on December 10, 2020

运放组成的波形发生器电路设计、装配与调试 1. 运放组成的波形发生器的单元电路 运放的二个应用:⑴ 线性应用-RC 正弦波振荡器 ⑵ 非线性应用-滞回比较器 ⑴ RC 正弦波振荡器 RC 桥式振荡电路如图3-9所示。 图3-9 RC 桥式振荡电路 RC 桥式振荡电路由二部分组成: ① 同相放大器,如图3-9(a )所示。 ② RC 串并联网络,如图3-9(b )所示。 或图3-9(c )所示,RC 串并联网络与同相放大器反馈支路组成桥式电路。 同相放大器的输出电压uo 作为RC 串并联网络的输入电压,而将RC 串并联网络的输出电压作为放大器的输入电压,当f=f 0时, RC 串并联网络的相位移为零,放大器是同相放大器,电路的总相位移是零,满足相位平衡条件,而对于其他频率的信号,RC 串并联网络的相位移不为零,不满足相位平衡条件。由于RC 串并联网络在 f=f 0 时的传输系数F =1/3,因此要求放大器的总电压增益Au 应大于3,这对于集成运放组成的同相放大器来说是很容易满足的。由R 1、R f 、V 1、V 2及R 2构成负反馈支路,它与集成运放形成了同相输入比例运算放大器。 只要适当选择R f 与R 1的比值, 就能实现Au>3的要求。其中,V1、V2和R 2是实现自动稳幅的限幅电路。 1 1R R A f u + =RC f π210=

① 振荡原理 RC 桥式振荡电路如图3-9所示。根据自激振荡的条件,φ=φa+Φf=2πn ,其中RC 串并联网络作为反馈电路,当f=fo 时,φf=0°,所以放大器的相移应为φa=0°,即可用一个同相输入的运算放大器组成。又因为当f=fo 时,F=1/3,所以放大电路的放大倍数A ≥3。起振时A>3,起振后若只依靠晶体管的非线性来稳幅,波形顶部容易失真。为了改善输出波形,通常引入负反馈电路。其振荡频率由RC 串并联网络决定,图3-9(c )为RC 桥式振荡电路的桥式画法。RC 串并联网络及负反馈电路中的Rf+'2 R 、R1正好构成电桥四臂,这就是桥式振荡器名称的由来。在RC 串并联网络中, 取C C C R R R ====2121, 当虚部为零,即)/(11221C R C R ωω=时,3/1=F ② 稳幅原理 V 1、V 2和R 2是实现自动稳幅的限幅电路。V 1、V 2仅一只导通,导通的二极管和R 2并联等 效电阻为'2R 。根据同相放大器的放大倍数计算公式:1 ' 2 1R R R A f ++=可知输出电压幅度与 '2 R 有关。 )1()1(1 11111// 1 2 121211222211 222 2122 22 2221 11C R C R j R R C C C R j R C j R C R j R Z Z Z U U F C R j R C j R Z C j R Z o f ωωωωωωωω-+++ =++ ++= +==+= =+=?? ?

波形变换电路.

目录 摘要................................................................................................................................................ 1概述. (1) 2设计原理 (2) 2.1 555定时器简介 (2) 2.2用555定时器构成的施密特触发器 (3) 2.3电路原理图 (5) 3 Proteus仿真 (6) 4调试过程及结论 (9) 5心得体会 (17) 参考文献 (18)

摘要 施密特触发器也有两个稳定状态,但与一般触发器不同的是,施密特触发器采用电位触发方式,其状态由输入信号电位维持;对于负向递减和正向递增两种不同变化方向的输入信号,施密特触发器有不同的阀值电压。因此,施密特触发器有三个大的特点:1、波形变换。可将三角波、正弦波等变成矩形波;2、脉冲波的整形,数字系统中,矩形脉冲在传输中经常发生波形畸变,出现上升沿和下降沿不理想的情况,可用施密特触发器整形后,获得较理想的矩形脉冲;3、脉冲鉴幅。幅度不同、不规则的脉冲信号时加到施密特触发器的输入端时,能选择幅度大于欲设值的脉冲信号进行输出。 主要功能和特色简介: 1、将给定频率的三角波变成脉冲波,脉冲波占空比不是50% 2、将给定频率的三角波变成脉冲波,脉冲波占空比是50% 3、将给定频率的正弦波变成脉冲波,脉冲波占空比是50% 4、将给定频率的三角波(正弦波)转换成间断式方波 5、将给定频率的三角波(正弦波)进行分频 关键词:Proteus仿真,施密特触发器,555定时器,波形变换

电子设计常用芯片

741 运算放大器 2063A JRC杜比降噪 20730 双功放 24C01AIPB21 存储器 27256 256K-EPROM 27512 512K-EPROM 2SK212 显示屏照明 3132V 32V三端稳压 3415D 双运放 3782M 音频功放 4013 双D触发器 4017 十进制计数器/脉冲分配器4021 游戏机手柄 4046 锁相环电路 4067 16通道模拟多路开关 4069 游戏机手柄 4093 四2输入施密特触发器 4098 41256 动态存储器 52432-01 可编程延时电路 56A245 开关电源 5G0401 声控IC 5G673 八位触摸互锁开关 5G673 触摸调光 5G673 电子开关 6116 静态RAM 6164 静态RAM 65840 单片数码卡拉OK变调处理器7107 数字万用表A/D转换器74123 单稳多谐振荡器 74164 移位寄存器 7474 双D触发器 7493 16分频计数器 74HC04 六反相器 74HC157 微机接口 74HC4053 74HCU04 六反相器 74LS00 与门 74LS00 4*2与非门 74LS00 四2与非门 74LS00 与门 74LS04 6*1非门 74LS08 4*2与门 74LS11 三与门 74LS123 双单稳多谐振荡器 74LS123 双单稳多谐振荡器 74LS138 三~八译码器 74LS142 十进制计数器/脉冲分配器74LS154 4-16线译码器 74LS157 四与或门74LS161 四2计数器 74LS161 十六进制同步计数器 74LS161 四~二计数器 74LS164 数码管驱动 74LS18 射频调制器 74LS193 加/减计数器 74LS193 四2进制计数器 74LS194 双向移位寄存器 74LS27 4*2或非门 74LS32 四或门 74LS32 4*2或门 74LS374 八位D触发器 74LS374 三态同相八D触发器 74LS377 74LS48 7位LED驱动 74LS73 双J-K触发器 74LS74 双D触发器 74LS85 四位比较器 74LS90 计数器 75140 线路接收器 75141 线路接收器 75142A 线路接收器 75143A 线路接收器 7555 时钟发生器 79MG 四端负稳压器 8051 空调单片机 8338 六反相器 A1011 降噪 ACVP2205-26 梳状滤波视频处理 AD536 专用运放 AD558 双极型8位D-A(含基准电压)变换器AD558 双极型8位D-A(含基准电压)变换器AD574A 12比特A/D变换器 AD650 AD670 8比特A/D变换器(单电源)1995s-2、15 AD7523 D-A变换器1994x-125 AD7524 D-A变换器1994x-126 AD7533 模数转换器1994x-141 AD7533 模数转换器1995s-184 ADC0804 8比特A/D变换器1995s-2、20 ADC0809 8CH8比特A/D 1995s-2、23 ADC0833 A/D变换4路转换器1995s-2 ADC80 12比特A/D变换器1995s-2、8 ADC84/85 高速12比特A/D变换器1995s-2 AG101 手掌游戏机1993x-155 AM6081 双极型8位D-A变换器1994x-127 AMP1200 音频功放皇后1993s-104 AN115 立体声解码1991-135 AN2510S 摄象机寻象器1994x-109 AN2661NK 影碟机视频1995s-45

多种波形发生器的设计与制作

课题三 多种波形发生器的设计与制作 方波、三角波、脉冲波、锯齿波等非正弦电振荡信号是仪器仪表、电子测量中最常用的波形,产生这些波形的方法较多。本课题要求设计的多种波形发生器是一种环形的波形发生器,方波、三角波、脉冲波、锯齿波互相依存。电路中应用到模拟电路中的积分电路、过零比较器、直流电平移位电路和锯齿波发生器等典型电路。通过对本课题的设计与制作,可进一步熟悉集成运算放大器的应用及电路的调试方法,提高对电子技术的开发应用能力。 1、 设计任务 设计并制作一个环形的多种波形发生器,能同时产生方波、三角波、脉冲波和锯齿波,它们的时序关系及幅值要求如图3-3-1所示。 图3-3-1 波形图 设计要求: ⑴ 四种波形的周期及时序关系满足图3-3-1的要求,周期误差不超过%1±。 ⑵ 四种波形的幅值要求如图3-3-1所示,幅值误差不超过%10±。 ⑶ 只允许采用通用器件,如集成运放,选用F741。

要求完成单元电路的选择及参数设计,系统调试方案的选取及综合调试。 2、设计方案的选择 由给定的四种波形的时序关系看:方波决定三角波,三角波决定脉冲波,脉冲波决定锯齿波,而锯齿波又决定方波。属于环形多种波形发生器,原理框图可用3-3-2表示。 图3-3-2 多种波形发生器的方框图 仔细研究时序图可以看出,方波的电平突变发生在锯齿波过零时刻,当锯齿波的正程过零时,方波由高电平跳变为低电平,故方波发生电路可由锯齿波经一个反相型过零比较器来实现。三角波可由方波通过积分电路来实现,选用一个积分电路来完成。图中的u B电平显然上移了+1V,故在积分电路之后应接一个直流电平移位电路,才能获得符合要求的u B波形。脉冲波的电平突变发生在三角波u B的过零时刻,三角波由高电平下降至零电位时,脉冲波由高电平实跳为低电平,故可用一个同相型过零比较器来实现。锯齿波波形仍是脉冲波波形对时间的积分,只不过正程和逆程积分时常数不同,可利用二极管作为开关,组成一个锯齿波发生电路。由上,可进一步将图3-3-2的方框图进一步具体化,如图3-3-3所示。 图3-3-3 多种波形发生器实际框图 器件选择,设计要求中规定只能选用通用器件,由于波形均有正、负电平,应选择由正、负电源供电的集成运放来完成,考虑到重复频率为100Hz(10ms),故选用通用型运放F741(F007)或四运放F324均可满足要求。本设计选用F741。其管脚排列及功能见附录三之三。

波形转换电路的设计

课程设计任务书 学生姓名:专业班级:电信科xxx班 指导老师:工作单位:武汉理工大学理学院 题目:波形转换电路的设计 初始条件:直流稳压电源一台、万用表一块、面包板一块、元器件若干、剪刀、镊子等必备工具 要求完成的主要任务:(包括课程设计工作量及其技术要求以及说明书撰写等具 体要求) 1、技术要求: 设计一种波形转换电路,要求产生频率可调的方波,并且能够实现方波转换为三角波。测试并且记录下不同频率下的方波和三角波的波形图,以及输出电压值。 2、主要任务: (一)设计方案 (1)按照技术要求,提出自己的设计方案(多种)并进行比较; (2)以集成电路运算放大器LF353为主,设计一种波形转换电路(实现方案); (3)依据设计方案,进行预答辩; (二)实现方案 (4)根据设计的实现方案,画出电路图; (5)查阅资料,确定所需各元器件型号和参数; (6)在面包板上组装电路; (7)自拟调整测试方法,并调试电路使其达到设计指标要求; (8)撰写设计说明书,进行答辩。 3、撰写课程设计说明书: 封面:题目,学院,专业,班级,姓名,学号,指导教师,日期 任务书 目录(自动生成) 正文:1、技术指标;2、设计方案及其比较;3、实现方案; 4、调试过程及结论; 5、心得体会; 6、参考文献 成绩评定表 时间安排:

课程设计时间:20周-21周 20周:明确任务,查阅资料,提出不同的设计方案(包括实现方案)并答辩; 21周:按照实现方案进行电路布线并调试通过;撰写课程设计说明书。指导教师签名:年月日系主任(或负责老师)签名:年月日 目录 1 技术指标 (1) 2 设计方案及其比较 (1) 2.1 方案一 (1) 2.1.1 设计RC文式桥振荡器 (2) 2.1.2 设计过零比较器 (3) 2.2 方案二 (4) 2.3 方案比较 (5) 3 实现方案 (5) 3.1 实验原理图 (5) 3.2 工作原理 (6) 3.2.1 设计方波发生器 (6) 3.2.2 设计积分器 (7) 3.3 各元器件功能 (9) 3.4 测试线路布线图 (9) 4 调试过程及结论 (10)

常用的AD芯片

常用的A/D芯片 1. AD公司AD/DA器件 AD公司生产的各种模数转换器(ADC)和数模转换器(DAC)(统称数据转换器)一直保持市场领导地位,包括高速、高精度数据转换器和目前流行的微转换器系统(MicroConvertersTM )。 1.1带信号调理、1mW功耗、双通道16位AD转换器:AD7705 AD7705是AD公司出品的适用于低频测量仪器的AD转换器。它能将从传感器接收到的很弱的输入信号直接转换成串行数字信号输出,而无需外部仪表放大器。采用Σ-Δ的ADC,实现16位无误码的良好性能,片内可编程放大器可设置输入信号增益。通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置数字滤波器的第一个凹口。在+3V电源和1MHz主时钟时, AD7705 功耗仅是1mW。AD7705是基于微控制器(MCU)、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。应用于微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据采集系统。 1.2 3V/5V CMOS信号调节AD转换器:AD7714 AD7714是一个完整的用于低频测量应用场合的模拟前端,用于直接从传感器接收小信号并输出串行数字量。它使用Σ-Δ转换技术实现高达24位精度的代码而不会丢失。输入信号加至位于模拟调制器前端的专用可编程增益放大器。调制器的输出经片内数字滤波器进行处理。数字滤波器的第一次陷波通过片内控制寄存器来编程,此寄存器可以调节滤波的截止时间和建立时间。AD7714有3个差分模拟输入(也可以是5个伪差分模拟输入)和一个差分基准输入。单电源工作(+3V或+5V)。因此,AD7714能够为含有多达5个通道的系统进行所有的信号调节和转换。AD7714很适合于灵敏的基于微控制器或DSP的系统,它的串行接口可进行3线操作,通过串行端口可用软件设置增益、信号极性和通道选择。AD7714具有自校准、系统和背景校准选择,也允许用户读写片内校准寄存器。CMOS结构保证了很低的功耗,省电模式使待机功耗减至15μW(典型值)。 1.3微功耗8通道12位AD转换器:AD7888 AD7888是高速、低功耗的12位AD转换器,单电源工作,电压范围为2.7V~5.25V,转换速率高达125ksps,输入跟踪-保持信号宽度最小为500ns,单端采样方式。AD7888包含有8个单端模拟输入通道,每一通道的模拟输入范围均为0~Vref。该器件转换满功率信号可至3MHz。AD7888具有片内2.5V电压基准,可用于模数转换器的基准源,管脚REF in/REF out允许用户使用这一基准,也可以反过来驱动这一管脚,向AD7888提供外部基准,外部基准的电压范围为1.2V~VDD。CMOS结构确保正常工作时的功率消耗为2mW(典型值),省电模式下为3μW。 1.4 微功耗、满幅度电压输出、12位DA转换器:AD5320 AD5320是单片12位电压输出D/A转换器,单电源工作,电压范围为+2.7V~5.5V。片内高精度输出放大器提供满电源幅度输出,AD5320利用一个3线串行接口,时钟频率可高达30MHz,能与标准的SPI、QSPI、MICROWIRE和DSP接口标准兼容。AD5320的基准来自电源输入端,因此提供了最宽的动态输出范围。

LM324的波形变换电路(DIY)

集成运放LM324的波形变换电路设计 一、设计目的 1、掌握LM324的应用 2、掌握三角波产生器、加法器、滤波器、比较器的设计 二、设计原理 1、原理:LM324内部包括有四个独立的、高增益、内部频率补偿的运算放大器,适合于电源电压范围很宽的单电源使用,也适用于双电源工作模式,在推荐的工作条件下,电源电流与电源电压无关。它的使用范围包括传感放大器、直流增益模块和其他所有可用单电源供电的使用运算放大器的场合。 2、LM324的特点: 1、内部频率补偿 2、直流电压增益高(约100dB) 3、单位增益频带宽(约1MHz) 4、电源电压范围宽:单电源(3—32V)、双电源(±1.5—±16V) 5、低功耗电流,适合于电池供电 6、低输入偏流、低输入失调电压和失调电流 7、共模输入电压范围宽,包括接地 8、差模输入电压范围宽,等于电源电压范围 9、输出电压摆幅大(0至VCC-1.5V) 3、LM324引脚图 4、LM324内部电路图

三、实验设备与器件 1、基本元件清单 LM324芯片、导线若干、铁丝、14脚插槽、二极管(IN4700A) 电阻: 680、1K 、2K 、3K 、10K 、47K 、20K 、30K 、100K 、1M 电位器 :2K 、10K 、20K 、50K 电容:0.3uF 、0.001uF 、0.1uF 、10uF 电路板 1块 2、实验仪器 直流电源、双踪示波器、数字万用表、信号发生器。 四、设计要求 使用一片通用四运放芯片 LM324组成电路框图见图1(a),实 现下述功能: 使用低频信号源产生)V (2sin 1.001t f u i π=,z f H 5000=的正弦波信号,加至加法器的输入端,加法器的另一输入端加入由自制振荡器产生的信号1o u ,1o u 如图1(b)所示,ms T 5.01=,允许1T 有±5%的误差。

电子设计大赛常用电路图

错误 !未定义书签。 图2 L293D 的电机驱动电路 图3 电源稳压电路 图4 降压电路

图3 降压斩波电路原理图 图4 电流检测模块

OS CI ICE_SDA ICE_SCK ICE_EN AV SS1OP I AGC M ICOUT DA C2DA C IOB12IOB11IOB15IOB13SLE EP IOB14VS S IOA12IOA14IOA11IOA10IOA15IOA13I O B 9I O B 10IOA9 I O B 5I O B 8I O B 7V C P I O A 8 V D D H I O A 6I O A 7V S S VS S V D D H VS S V R T A V S S 1 V D D _P I O B 2V C M I O A 3I O B 6I O B 1I O A 1V M I C I O B 0I O A 2M I C P R E S _B I O B 4 I O A 4 I O B 3I O A 0I O A 5VREF2V S S V D D H SPCE061A DA C1M ICN AV SS1VDD VS S VS S VS S OS CO +C29100u C31104 U1 OS C32O 12OS C32I 13XT EST 14VDD 15XICE 16XICECLK 17XICES DA 18VS S 19PV IN 20DA C121DA C222VREF223VS S 24AGC 25OP I 26M ICOUT 27M ICN 28PFUSE 29M I C P 33V C M 34V R T P A D 35V D D 36V M I C 37V S S 38I O A 041I O A 142I O A 243I O A 344I O A 445I O A 546I O A 647I O A 748V S S 49V S S 50V D D H 51V D D H 52I O A 8 53 N C 39N C 40NC 30NC 31NC 32 IOA9 54 IOA1055IOA1156IOA1257IOA1358IOA1459IOA1560XROM T 61VS S 62XS LEEP 63IOB1564IOB1465IOB1366IOB1267IOB1168PV PP 69V D D H 75 I O B 1076I O B 977NC 70NC 71NC 72NC 73NC 74I O B 878I O B 779I O B 680I O B 581I O B 41I O B 32I O B 23N C 82N C 83N C 84I O B 14I O B 05X R E S B 6V D D 7V C P 8V S S 9N C 10N C 11C8104C7104C18104 +C5 100u C28104 + C27100u +C17100u + C4100u V D D _A SPCE061A 芯片引脚电路图 电机驱动电路 图5 电源变换电路图

简易波形发生器的设计

目录 第一章单片机开发板 (1) 1.1 开发板制作 (1) 1.1.1 89S52单片机简介 (1) 1.1.2 开发板介绍 (2) 1.1.3 89S52的实验程序举例 (3) 1.2开发板焊接与应用 (4) 1.2.1开发板的焊接 (4) 1.2.2开发板的应用 (5) 第二章函数信号发生器 (7) 2.1电路设计 (7) 2.1.1电路原理介绍 (7) 2.1.2 DAC0832的工作方式 (9) 2.2 波形发生器电路图与程序 (10) 2.2.1应用电路图 (10) 2.2.2实验程序 (11) 2.2.3 调试结果 (15) 第三章参观体会 (16) 第四章实习体会 (17) 参考文献 (18)

第一章单片机开发板 1.1 开发板制作 1.1.1 89S52单片机简介 图1.1 89s52 引脚图 如果按功能划分,它由8个部件组成,即微处理器(CPU)、数据存储器(RAM)、程序存储器(ROM/EP ROM)、I/O口(P0口、P1口、P2口、P3口)、串行口、定时器/计数器、中断系统及特殊功能寄存器(SF R)的集中控制方式。 各功能部件的介绍: 1)数据存储器(RAM):片内为128个字节单元,片外最多可扩展至64K字节。 2)程序存储器(ROM/EPROM):ROM为4K,片外最多可扩展至64K。 3)中断系统:具有5个中断源,2级中断优先权。 4)定时器/计数器:2个16位的定时器/计数器,具有四种工作方式。 5)串行口:1个全双工的串行口,具有四种工作方式。 6)特殊功能寄存器(SFR)共有21个,用于对片内各功能模块进行管理、监控、监视。 7)微处理器:为8位CPU,且内含一个1位CPU(位处理器),不仅可处理字节数据,还可以进行位变量的处理。 8)四个8位双向并行的I/O端口,每个端口都包括一个锁存器、一个输出驱动器和一个输入缓冲器。这四个端口的功能不完全相同。 A、P0口既可作一般I/O端口使用,又可作地址/数据总线使用; B、P1口是一个准双向并行口,作通用并行I/O口使用; C、 P2口除了可作为通用I/O使用外,还可在CPU访问外部存储器时作高八位地址线使用; D、P3口是一个多功能口除具有准双向I/O功能外,还具有第二功能。 控制引脚介绍: 1)电源:单片机使用的是5V电源,其中正极接40引脚,负极(地)接20引脚。 2)时钟引脚XTAL1、XTAL2时钟引脚外接晶体与片内反相放大器构成了振荡器,它提供单片机的时钟控制信号。时钟引脚也可外接晶体振荡器。 振蒎电路:单片机是一种时序电路,必须提供脉冲信号才能正常工作,在单片机内部已集成了振荡器,

最新常用AD芯片介绍

常用A D芯片介绍

目前生产AD/DA的主要厂家有ADI、TI、BB、PHILIP、MOTOROLA等,武汉力源公司拥有多年从事电子产品的 经验和雄厚的技术力量支持,已取得排名世界前列的模拟IC生产厂家ADI、TI 公司代理权,经营全系列适用各 种领域/场合的AD/DA器件。 1. AD公司AD/DA器件 AD公司生产的各种模数转换器(ADC)和数模转换器(DAC)(统称数据转换器)一直保持市场领导地位,包括 高速、高精度数据转换器和目前流行的微转换器系统(MicroConvertersTM )。 1)带信号调理、1mW功耗、双通道16位AD转换器:AD7705 AD7705是AD公司出品的适用于低频测量仪器的AD转换器。它能将从传感器接收到的很弱的输入信号直接 转换成串行数字信号输出,而无需外部仪表放大器。采用Σ-Δ的ADC,实现16位无误码的良好性能,片内可 编程放大器可设置输入信号增益。通过片内控制寄存器调整内部数字滤波器的关闭时间和更新速率,可设置 数字滤波器的第一个凹口。在+3V电源和1MHz主时钟时, AD7705功耗仅是 1mW。AD7705是基于微控制器(MCU )、数字信号处理器(DSP)系统的理想电路,能够进一步节省成本、缩小体积、减小系统的复杂性。应用于 微处理器(MCU)、数字信号处理(DSP)系统,手持式仪器,分布式数据采集系统。 2)3V/5V CMOS信号调节AD转换器:AD7714 AD7714是一个完整的用于低频测量应用场合的模拟前端,用于直接从传感器接收小信号并输出串行数字 量。它使用Σ-Δ转换技术实现高达24位精度的代码而不会丢失。输入信号加至位于模拟调制器前端的专用可 编程增益放大器。调制器的输出经片内数字滤波器进行处理。数字滤波器的第一次陷波通过片内控制寄存器 来编程,此寄存器可以调节滤波的截止时间和建立时间。AD7714有3个差分模拟输入(也可以是5个伪差分模 拟输入)和一个差分基准输入。单电源工作(+3V或+5V)。因此,AD7714能够为含有多达5个通道的系统进行 所有的信号调节和转换。AD7714很适合于灵敏的基于微控制器或DSP的系统,它的串行接口可进行3线操作, 通过串行端口可用软件设置增益、信号极性和通道选择。AD7714具有自校准、系统和背景校准选择,也允许 用户读写片内校准寄存器。CMOS结构保证了很低的功耗,省电模式使待机功耗减至15μW(典型值)。 3)微功耗8通道12位AD转换器:AD7888 AD7888是高速、低功耗的12位AD转换器,单电源工作,电压范围为2.7V~5.25V,转换速率高达125ksps ,输入跟踪-保持信号宽度最小为500ns,单端采样方式。AD7888包含有8个单端模拟输入通道,每一通道的模

课程设计——波形发生器要点

1.概述 波形发生器是一种常用的信号源,广泛地应用于电子电路、自动控制系统和教学实验等领域。函数信号发生器是一种能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路。函数信号发生器在电路实验和设备检测中具有十分广泛的用途。通过对函数波形发生器的原理以及构成分析,可设计一个能变换出三角波、正弦波、方波的函数波形发生器。本课程采用采用RC正弦波振荡电路、电压比较器、积分电路共同组成的正弦波—方波—三角波函数发生器的设计方法。先通过RC正弦波振荡电路产生正弦波,再通过电压比较器产生方波,最后通过积分电路形成三角波。

2.设计方案 采用RC正弦波振荡电路、电压比较器、积分电路共同组成的正弦波—方波—三角波函数发生器的设计方法。先通过RC正弦波振荡电路产生正弦波,再通过电压比较器产生方波,最后通过积分电路形成三角波。文氏桥振荡器产生正弦波输出,其特点是采用RC串并联网络作为选频和反馈网络,其振荡频率f=1/2πRC.改变RC的值,可得到不同的频率正弦波信号输出。用集成运放构成电压比较器,将正弦波变换成方

3. 设计原理 3.1正弦波产生电路 正弦波由RC 桥式振荡电路(如图3-1所示),即文氏桥振荡电路产生。文氏桥振荡器具有电路简单、易起振、频率可调等特点而大量应用于低频振荡电路。正弦波振荡电路由一个放大器和一个带有选频功能的正反馈网络组成。其振荡平衡的条件是AF =1以及ψa+ψf=2n π。其中A 为放大电路的放大倍数,F 为反馈系数。振荡开始时,信号非常弱,为了使振荡建立起来,应该使AF 略大于1。 放大电路应具有尽可能大的输入电阻和尽可能小的输出电阻以减少放大电路对选频特性的影响,使振荡频率几乎仅决定于选频网络,因此通常选用引入电压串联负反馈的放大电路。正反馈网络的反馈电压U f 是同相比例运算电路的输入电压,因而要把同相比例运算电路作为整体看成电路放大电路,它的比例系数是电压放大倍数,根据起振条件和幅值平衡条件有 31 1≥+ =R Rf Av (Rf=R2+R1//D1//D2) 且振荡产生正弦波频率 Rc f π210= 图中D1、D2的作用是,当Vo1幅值很小时,二极管D1、D2接近开路,近似有Rf =9.1K +2.7K =11.8K ,,Av=1+Rf/R1=3.3>=3,有利于起振;反之当Vo 的幅值较大时,D1或D2导通,Rf 减小,Av 随之下降,Vo1幅值趋于稳定。

波形发生器课程设计

波形发生器设计 设计总说明 本系统采用AT89C51单片机作为控制核心,外围采用数字/模拟转换电路(DAC0832)运算放大器、按键等。采用AT89C51单片机和DAC0832芯片,直接连接键盘和显示。该种方案主要对AT89C51单片机的各个I/O口充分利用. P1口是连接键盘以及接显示电路,P2口连接DAC0832输出波形.这样总体来说,能对单片机各个接口都利用上,而不在多用其它芯片,从而减小了系统的成本.也对按照系统便携式低频信号发生器的要求所完成.占用空间小,使用芯片少,低功耗。 通过按键控制可产生方波、三角波、正弦波、梯形波、锯齿波。其设计简单、性能优好,具有一定的实用性。正弦波、三角波、方波、梯形波、锯齿波是较为常见的信号。在科学研究及教学实验中常常需要这几种信号的发生装置。 关键字:AT89C5,DAC0832,运算放大器

目录 1绪论 (1) 1.1设计目的 (1) 1.2设计容 (1) 2系统设计方案 (3) 2.1系统组成 (3) 2.2系统工作原理 (3) 3系统硬件电路设计 (4) 3.1单片机最小系统设计 (4) 3.2其他硬件模块电路设计 (4) 3.2.1 DAC0832芯片介绍 (4) 3.2.2单片机AT89C51介绍 (6) 4系统软件程序设计 (10) 4.1主程序设计 (10) 4.2其他子程序设计 (11) 4.2.1锯齿波流程设计 (11) 4.2.2梯形波流程设计 (12) 4.2.3三角波流程设计 (13) 4.2.4方波流程设计 (14) 4.2.5正弦波流程设计 (15)

5 调试与仿真 (18) 6 总结 (19) 致 (21) 参考文献 (22)

数模及模数转换电路设计问答

ADC/DAC设计经典问答 (上) 1. 什么是小信号带宽(SSBW)? 小信号带宽(Small Signal Bandwidth (SSBW))是指在指定的幅值输入信号及特定的频率下,它的输出幅值比低频时的输出幅值下降指定值时,该特定频率为小信号带宽。 2. 什么是共模电压(VCM)? 共模电压(Common Mode Voltage (VCM ))是差动输入的两个引脚上相同的直流输入电压。 3. 什么是MSB(最高有效位)? MSB(最高有效位(Most Significant Bit)),是具有最大的值或权重的位。它的值是满量程的一半。 4. 什么是采样(孔径)延时? 采样(孔径)延时(Sampling (Aperture) Delay)是时钟输入的后边缘到采样开关打开所需的时间。采样/保持电路有效地停止输入信号捕获,并进入“保持”模式,确定时钟延时后的采样。 5. 什么是满量程(FS)输入范围? 满量程输入范围(Full Scale Input Range),是指模数转换器上数字化的输入电压的输入范围,既不低于这个范围也不超过这个范围。比如V REF + = 3.5V 和VREF - = 1.5V, FS = (VREF + )-(VREF - ) = 2.0V。 6. 什么是时钟占空比? 时钟占空比(Clock Duty Cycle)是时钟波形高电平时间和一个时钟周期总时间的比值。 7. 什么是位的有效数(ENOB ,或有效位)? 位的有效数(ENOB ,或有效位)(Effective Number of Bits (ENOB, 或Effective Bits))是信噪比和失真的比率,或SINAD的另一种表达方法。ENOB定义为(SINAD -1.76)/ 6.02,这个位数(ENOB)表示转换器是与理想的模数转换器等效。 8. 什么是增益误差? 增益误差是在第一个代码和最后一个代码发生转换时,实际输人电压与理想输人电压之差。即,这个差值是:满量程- 2 LSB。 9. 许多模数转换器在数据手册中提供的应用,在Va, Vd 和Vref引脚上出现了三个电容。这三个电容器都是必须的吗?

毕业设计169邵阳学院基于模拟电路的波形发生器设计

前言 波形发生器是一种常用的信号源,广泛用于科学研究、生产实践和教学实践等领域。如设计和测试、汽车制造、生物医药、传感器仿真、制造模型等。 传统的信号发生器采用模拟电子技术,由分立元件构成振荡电路和整形电路,产生各种波形。它在电子信息、通信、工业等领域曾发挥了很大的作用。但是采用这种技术的波形发生器电路结构复杂、体积庞大、稳定度和准确度较差,而且仅能产生正弦波、方波、三角波等几种简单波形,难以产生较为复杂的波形信号。随着微处理器性能的提高,出现了由微处理器、D/A以及相关硬件、软件构成的波形发生器。它扩展了波形发生器的功能,产生的波形也比以往复杂。实质上它采用了软件控制,利用微处理器控制D/A,就可以得到各种简单波形。但由于微处理器的速度限制,这种方式的波形发生器分辨率较低,频率切换速度较慢。 从2007年2月到2007年4月,在系统研究国内外波形发生器的基础上提出了基于Matlab和FPGA技术的波形发生器,在FPGA内开辟高速存储器ROM做查询表,通过Matlab获得波形数据存入ROM中,波形数据不断地,有序地从ROM 中送到高速D/A转换器对存储器的波形数据进行转换。因此只要改变FPGA中查找表数据就可以产生任意波形,因此该研究方法可以产生任意波形。 随着我国四个现代化和经济发展,我国在科技和生产各领域都取得了飞速的发展和进步,同时这也对相应的测试仪器和测试手段提出了更高的要求,而波形发生器已成为测试仪器中至关重要的一类,因此在国内发展波形发生器具有重大意义和实际价值。例如,它能模拟编码雷达信号、潜水艇特征信号、磁盘数据信号、机械振动瞬变过程、电视信号以及神经脉冲之类的波形,也能重演由数字示波器捕获的波形等。 在本次设计中,我通过Matlab获取了波形数据,在FPGA中开辟了ROM区域,在MaxplusⅡ开发平台上,实现了电路的VHDL硬件描述和仿真,电路功能在EDA平台上得到了验证,但由于我的能力和水平有限,论文中肯定会有不妥之处和错误,恳请老师和同学提出批评和改进意见,在此表示由衷的感谢。