CVBS电路设计

CVBSOUT电路参数设计

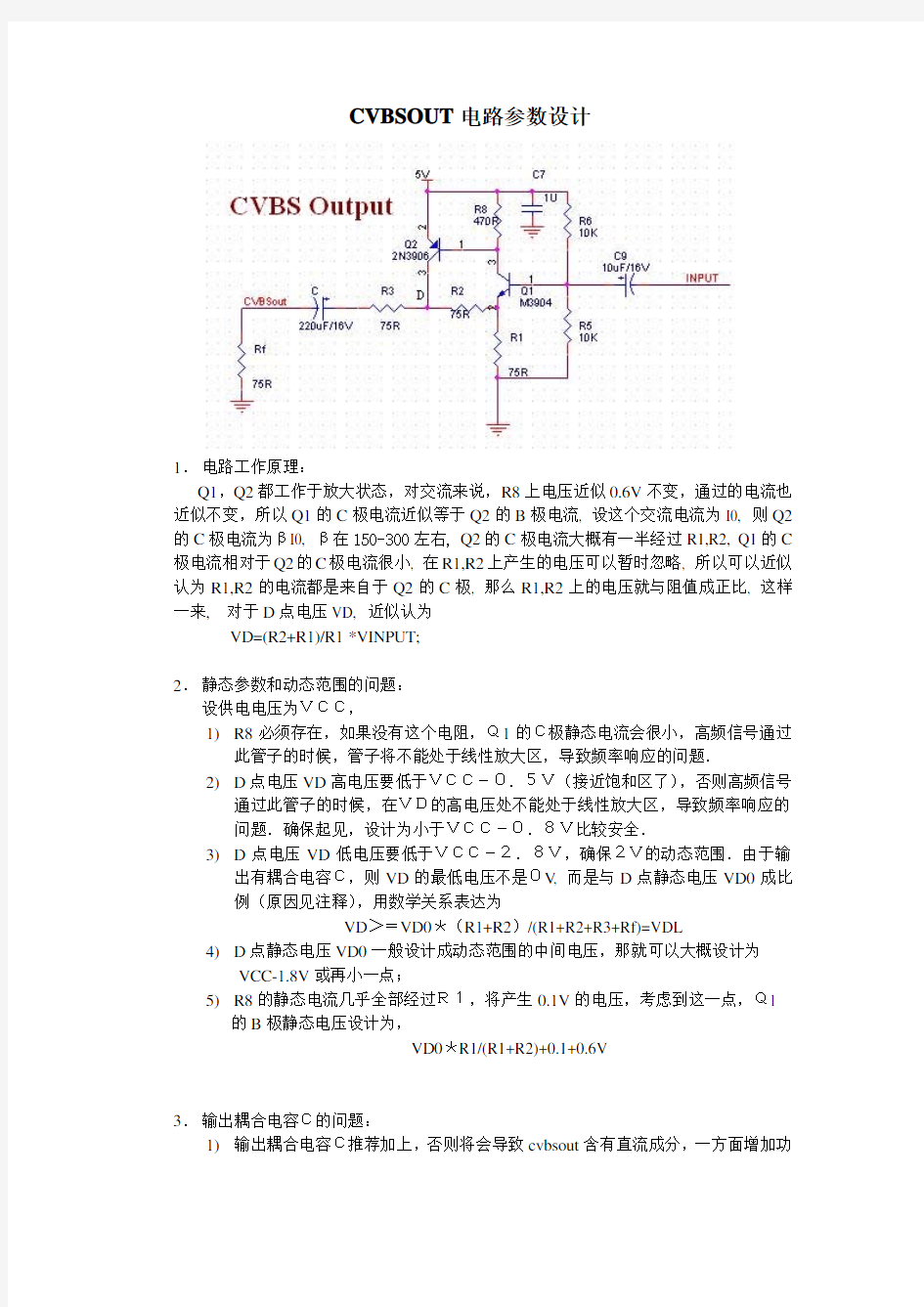

1.电路工作原理:

Q1,Q2都工作于放大状态,对交流来说,R8上电压近似0.6V不变,通过的电流也近似不变,所以Q1的C极电流近似等于Q2的B极电流, 设这个交流电流为I0, 则Q2的C极电流为βI0, β在150-300左右, Q2的C极电流大概有一半经过R1,R2, Q1的C 极电流相对于Q2的C极电流很小, 在R1,R2上产生的电压可以暂时忽略, 所以可以近似认为R1,R2的电流都是来自于Q2的C极, 那么R1,R2上的电压就与阻值成正比, 这样一来,对于D点电压VD, 近似认为

VD=(R2+R1)/R1 *VINPUT;

2.静态参数和动态范围的问题:

设供电电压为VCC,

1)R8必须存在,如果没有这个电阻,Q1的C极静态电流会很小,高频信号通过

此管子的时候,管子将不能处于线性放大区,导致频率响应的问题.

2)D点电压VD高电压要低于VCC-0.5V(接近饱和区了),否则高频信号

通过此管子的时候,在VD的高电压处不能处于线性放大区,导致频率响应的问题.确保起见,设计为小于VCC-0.8V比较安全.

3)D点电压VD低电压要低于VCC-2.8V,确保2V的动态范围.由于输

出有耦合电容C,则VD的最低电压不是0V, 而是与D点静态电压VD0成比例(原因见注释),用数学关系表达为

VD>=VD0*(R1+R2)/(R1+R2+R3+Rf)=VDL

4)D点静态电压VD0一般设计成动态范围的中间电压,那就可以大概设计为

VCC-1.8V或再小一点;

5)R8的静态电流几乎全部经过R1,将产生0.1V的电压,考虑到这一点,Q1

的B极静态电压设计为,

VD0*R1/(R1+R2)+0.1+0.6V

3.输出耦合电容C的问题:

1)输出耦合电容C推荐加上,否则将会导致cvbsout含有直流成分,一方面增加功

耗和Q2的发热,一方面异常的供电有可能导致接收设备出问题(比如冷开机不能复位,烧esd器件等等);

2)输出耦合电容C的大小问题,业内以220uF居多,一般地说大于100uF就可以

了,但是如果电性能指标转从cvbsout上测试,则推荐470uF以上,否则会测不准.

注释1:Q1的C极电流影响和Q1,Q2的线性不理想,会导致实际放大倍数比(R2+R1)/R1小,所以可以调整以下R1,R2的大小解决这个问题.

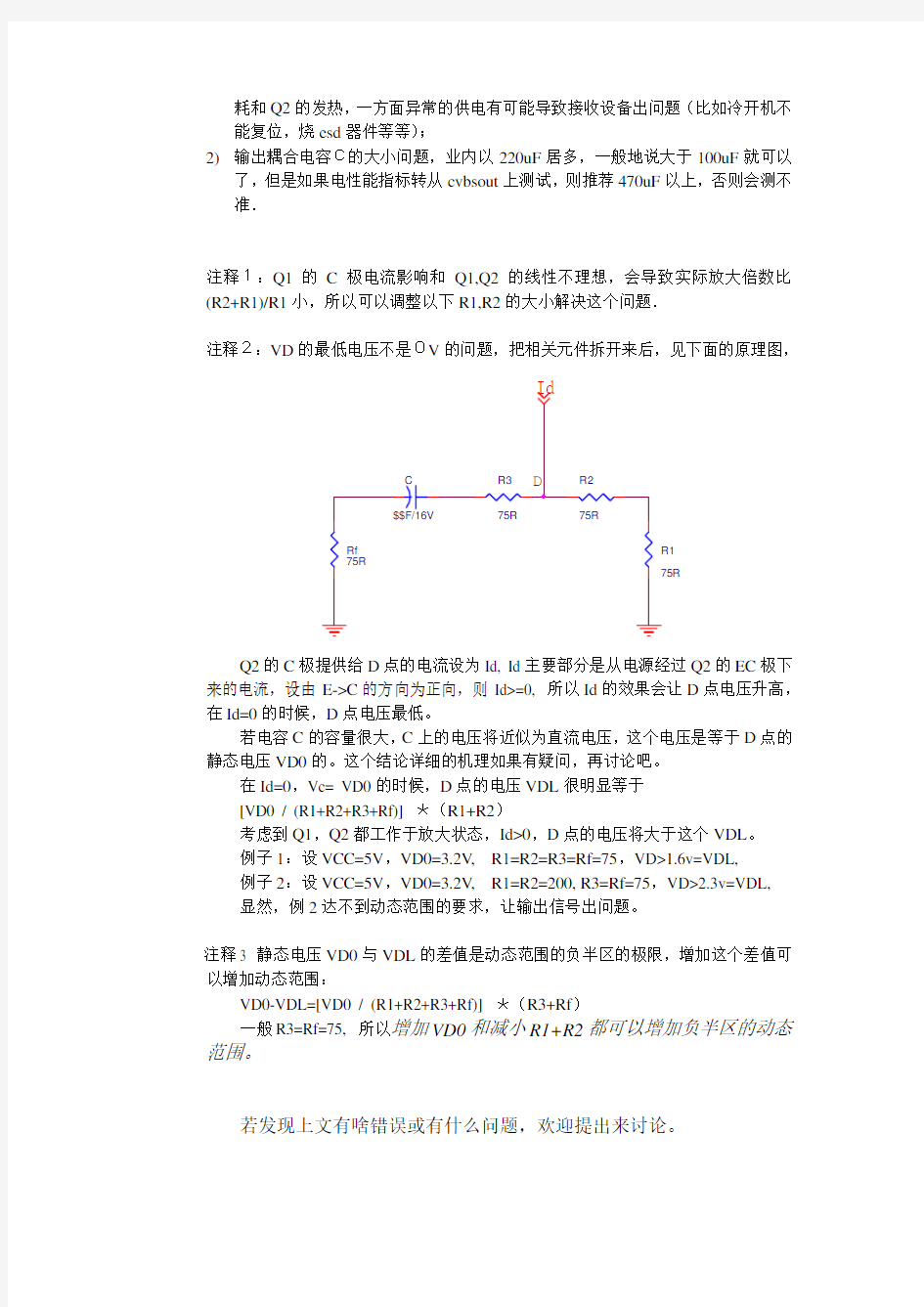

注释2:VD的最低电压不是0V的问题,把相关元件拆开来后,见下面的原理图,

Q2的C极提供给D点的电流设为Id, Id主要部分是从电源经过Q2的EC极下来的电流,设由E->C的方向为正向,则Id>=0, 所以Id的效果会让D点电压升高,在Id=0的时候,D点电压最低。

若电容C的容量很大,C上的电压将近似为直流电压,这个电压是等于D点的静态电压VD0的。这个结论详细的机理如果有疑问,再讨论吧。

在Id=0,Vc= VD0的时候,D点的电压VDL很明显等于

[VD0 / (R1+R2+R3+Rf)] *(R1+R2)

考虑到Q1,Q2都工作于放大状态,Id>0,D点的电压将大于这个VDL。

例子1:设VCC=5V,VD0=3.2V, R1=R2=R3=Rf=75,VD>1.6v=VDL,

例子2:设VCC=5V,VD0=3.2V, R1=R2=200, R3=Rf=75,VD>2.3v=VDL, 显然,例2达不到动态范围的要求,让输出信号出问题。

注释3 静态电压VD0与VDL的差值是动态范围的负半区的极限,增加这个差值可以增加动态范围:

VD0-VDL=[VD0 / (R1+R2+R3+Rf)] *(R3+Rf)

一般R3=Rf=75, 所以增加VD0和减小R1+R2都可以增加负半区的动态范围。

若发现上文有啥错误或有什么问题,欢迎提出来讨论。

福州大学集成电路应用实验一

《集成电路应用》课程实验实验一 4053门电路综合实验 学院:物理与信息工程学院 专业: 电子信息工程 年级: 2015级 姓名:张桢 学号: 指导老师:许志猛

实验一 4053门电路综合实验 一、实验目的: 1.掌握当前广泛使用的74/HC/HCT系列CMOS集成电路、包括门电路、反相 器、施密特触发器与非门等电路在振荡、整形、逻辑等方向的应用。 2.掌握4053的逻辑功能,并学会如何用4053设计门电路。 3.掌握多谐振荡器的设计原理,设计和实现一个多谐振荡器,学会选取和 计算元件参数。 二、元件和仪器: 1.CD4053三2通道数字控制模拟开关 2.万用表 3.示波器 4.电阻、电容 三、实验原理: 1.CD4053三2通道数字控制模拟开关 CD4053是三2通道数字控制模拟开关,有三个独立的数字控制输入端A、B、C和INH输入,具有低导通阻抗和低的截止漏电流。幅值为4.5~20V的数字信号可控制峰-峰值至20V的数字信号。CD4053的管脚图和功能表如下所示 4053引脚图

4053的8种逻辑功能 CD4053真值表 根据CD4053的逻辑功能,可以由CD4053由4053电路构成如下图所示8种逻辑门(反相器与非门或非门、反相器、三态门、RS 触发器、——RS 触发器、异或门等)。 输入状态 接通通道

]) 2)(()(ln[ T DD T DD T DD T V V V V V V V RC T -+--=2.多谐振荡器的设计 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 可以利用反相器设计出如下图所示的多谐振荡器 这样的多谐振荡器输出的信号周期计算公式为: 当R S ≈2R 时,若:VT=0.5VDD ,对于HC 和HCU 型器件,有 T ≈2.2RC 对于HCT 型器件,有 T ≈2.4RC 四、实验内容: 1. 验证CD4053的逻辑功能,用4053设计门电路,并验证其逻辑功能: (1)根据实验原理设计如下的反相器电路图: CD4053构成反相器电路

EMC滤波电路的原理与设计---整理【WENDA】

第一章开关电源电路—EMI滤波电路原理 滤波原理:阻抗失配;作为电感器就是低通(更低的频率甚至直流能通过)高阻(超过一定频率后就隔断住难于通过)(或者是损耗成热消散掉),因此电感器滤波靠的是阻抗 Z=(R^2+(2ΠfL)^2)^1/2。也就是分成两个部分,一个是R涡流损耗,频率越高越大,直接把杂波转换成热消耗掉,这种滤波最干净彻底;一个是2ΠfL 这部分是通过电感量产生的阻挡作用,把其阻挡住。实际都是两者的结合。但是要看你要滤除的杂波的频率,选择合适的阻抗曲线。因为电感器是有截止频率的,超过这个频率就变成容性,也就失去电感器的基本特性了,而这个截止频率和磁性材料的特性和分布电容关系最大,因此要滤波更高的频率的干扰,就需要更低的磁导率,更低的分布电容。因此一般我们滤除几百K以下的共模干扰,一般使用非晶做共模电感器,或者10KHZ以上的高导铁氧体来做,这样主要使用阻抗的WL这一方面的特性,主要发挥阻挡作用。电感器滤波器是通过串联在电路里实现。撒旦谁打死多少次顺风车安顺场。 因此:共模滤波电感器不是电感量越大越好主要看你要滤除的共模干扰的频率范围。先说一下共模电感器滤波原理共模电感器对共模干扰信号的衰减或者说滤除有两个原理,一是靠感抗的阻挡作用,但是到高频电感量没有了,然后靠的是磁心的损耗吸收作用;他们的综合效果是滤波的真实效果。当然在低频段靠的是电感量产生的感抗.同样的电感器磁心材料绕制成的电感器,随着电感量的增加,Z阻抗与频率曲线变化的趋势是随着你绕制的电感 器的电感量的增加,Z 阻抗峰值电时的频率就会下降,也就是说电感量越高所能滤除的共模干扰的频率越低,换句话说对低频共模干扰的滤除效果越好,对高频共模信号的滤除效果越差甚至不起作用。这就是为什么有的滤波器使用两级滤波共模电感器的原因一级是用低磁导率(磁导率7K以下铁氧体材料甚至可以使用1000的NiZn材料) 材料作成共模滤波电感器,滤出几十MHz或更高频段的共模干扰信号,另一级采用高导磁材料(如磁导率10000\15000 的铁氧体材料或着非晶体材料)来滤除1MHz以下或者几百kHz的共模干扰信号。因此首先要确认你要滤除共模干扰的频率范围然后再选择合适的滤波电感器材料. 电容的阻抗是Z=-1/2ΠfL那么也就是频率越高阻抗绝对值越小,那么就是高通低阻,就是频率越高越能通过,所以电容滤波是旁路,也就是采用并联方式,把高频的干扰通过电容旁路给疏导回去。

电路设计实验报告

电子技术课程设计 题目: 班级: 姓名: 合作者:

数字电子钟计时系统 一、设计要求 用中、小规模集成电路设计一台能显示时、分、秒的数字电子钟,基本要求如下: 1、采用LED显示累计时间“时”、“分”、“秒”。 2、具有校时功能。 二、设计方案 数字电子钟主要由振荡器、分频器、计数器、译码器、显示器等几部分组成,其整体框图为 其中,秒信号发生器为:

由石英晶体发出32768Hz的振荡信号经过分频器,即CD4060——14级串行二进制计数器/分频器和振荡器,输出2Hz 的振荡信号传入D触发器,经过2分频变为秒信号输出。 校时电路为: 当K1开启时,与非门一端为秒信号另一端为高电位,输出即为秒信号秒计数器正常工作,当K1闭合,秒信号输出总为0,实现秒暂停。 当K2/K3开启时,分信号/时信号输入由秒计数器输出信号及高电平决定,所以输出信号即为分信号/时信号,当K2/K3闭合时,秒信号决定分信号/时信号输出,分信号/时信号输出与秒信号频率一致, 以实现分信号/时信号的加速校时。 秒、分计数器——60进制

首先,调节CD4029的使能端,使其为十进制加法计数器。将输入信号脉冲输入第一个 计数器(个位计数器)计十个数之后将,进位输出输给下一个计数器(十位计数器)的进位 输入实现十秒计数。当计数器的Q1,Q2输出均为1时经过与门电路,输出高电平,作为分 脉冲或时脉冲并同时使两计数器置零。 时计数器——24进制 时脉冲 首先,调节CD4029的使能端,使其为十进制加法计数器。将输入信号脉冲输入第一个 计数器(个位计数器)计十个数之后将,进位输出输给下一个计数器(十位计数器)的进位 输入实现十秒计数。当十位计数器Q1和个位计数器Q2输出均为1时经过与门电路,输出 高电平使两计数器置零。 译码显示电路

数字电路及设计实验

常用数字仪表的使用 实验内容: 1.参考“仪器操作指南”之“DS1000操作演示”,熟悉示数字波器的使用。 2.测试示波器校正信号如下参数:(请注意该信号测试时将耦合方式设置为直流耦合。 峰峰值(Vpp),最大值(Vmax),最小值(Vmin), 幅值(Vamp),周期(Prd),频率(Freq) 顶端值(Vtop),底端值(Vbase),过冲(Overshoot), 预冲(Preshoot),平均值(Average),均方根值(Vrms),即有效值 上升时间(RiseTime),下降时间(FallTime),正脉宽(+Width), 负脉宽(-Width),正占空比(+Duty),负占空比(-Duty)等参数。 3.TTL输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低 电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V。 请采用函数信号发生器输出一个TTL信号,要求满足如下条件: ①输出高电平为3.5V,低电平为0V的一个方波信号; ②信号频率1000Hz; 在示波器上观测该信号并记录波形数据。

集成逻辑门测试(含4个实验项目) (本实验内容选作) 一、实验目的 (1)深刻理解集成逻辑门主要参数的含义和功能。 (2)熟悉TTL 与非门和CMOS 或非门主要参数的测试方法,并通过功能测试判断器件好坏。 二、实验设备与器件 本实验设备与器件分别是: 实验设备:自制数字实验平台、双踪示波器、直流稳压电源、数字频率计、数字万用表及工具; 实验器件:74LS20两片,CC4001一片,500Ω左右电阻和10k Ω左右电阻各一只。 三、实验项目 1.TTL 与非门逻辑功能测试 按表1-1的要求测74LS20逻辑功能,将测试结果填入与非门功能测试表中(测试F=1、0时,V OH 与V OL 的值)。 2.TTL 与非门直流参数的测试 测试时取电源电压V CC =5V ;注意电流表档次,所选量程应大于器件电参数规范值。 (1)导通电源电流I CCL 。测试条件:输入端均悬空,输出端空载。测试电路按图1-1(a )连接。 (2)低电平输入电流I iL 。测试条件:被测输入端通过电流表接地,其余输入端悬空,输出空载。测试电路按图1-1(b )连接。 (3)高电平输入电流I iH 。测试条件:被测输入端通过电流表接电源(电压V CC ),其余输入端均接地,输出空载。测试电路按图1-1(c )连接。 (4)电压传输特性。测试电路按图1-2连接。按表1-2所列各输入电压值逐点进行测量,各输入电压值通过调节电位器W 取得。将测试结果在表1-2中记录,并根据实测数据,做出电压传输特性曲线。然后,从曲线上读出V OH ,V OL ,V on ,V off 和V T ,并计算V NH ,V NL 等参数。 表1-1 与非门功能测试表

电路辅助设计上.

实验一:功率的测定以及仿真 1.仿真实验目的 (1)验证各电阻的功率和电压源的功率,并且验证整个电路输出功率和吸收功率相等,即整个电路功率守恒; (2)、学习利用仿真仪表分析检验各电阻功率和对电压表电流表的运用。 2.实验原理及说明 A. 本次实验的电路图以及连接方式如图1.1所示:利用环路电流法可列出方程 B. )(36_)(31234232131=?-?++=??+R R R R V R R R i i i i l l i l 图1.1 C .电路连接好之后,按照电流表和电压表的示数,根据I U P ?=可以算出电压源的功率,再根据连接在各电阻上的功率表,读出各电阻的功率 321,,P P P ,根据4321P +++=P P P P 吸收可以算出电路吸收的功 率;根据I U P P ?==电源释放可以算出电路释放的功率。 .若释放吸收P P =,则说明整个电路吸收与释放的功率相等。 3.仿真实验的步骤与内容 按照原理图1.1所示,连接电路,如下图1.2所示 读数,如下图1.3所示我们可以得到:U=36.0V,I=9.0A,又由0 )(36_)(31234232131=?-?++=??+R R R R V R R R i i i i l l i l 计算出实 验一致。

36V I U =?=释放P ; 4321P +++=P P P P 吸收=424323222121I R I R I R I R +++=162+18+108+36=324W 由上可得,释放 吸收P P =,所以整个电路是功率守恒的R12Ω XMM1 R2 2Ω V136 V XWM1 V I XWM2 V I XWM3 V I R3 3Ω XWM4 V I R44Ω U1 DC 1e-009Ohm 0.000 A + - 图1.2 图1.3

电子科技大学集成电路原理实验CMOS模拟集成电路设计与仿真王向展

实验报告 课程名称:集成电路原理 实验名称: CMOS模拟集成电路设计与仿真 小组成员: 实验地点:科技实验大楼606 实验时间: 2017年6月12日 2017年6月12日 微电子与固体电子学院

一、实验名称:CMOS模拟集成电路设计与仿真 二、实验学时:4 三、实验原理 1、转换速率(SR):也称压摆率,单位是V/μs。运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。 2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。 3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。 4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。 5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。 6、输出电压摆幅:一般指输出电压最大值和最小值的差。 图 1两级共源CMOS运放电路图 实验所用原理图如图1所示。图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。M6、M7为二级放大电路,Cc为引入的米勒补偿电容。 其中主要技术指标与电路的电气参数及几何尺寸的关系:

转换速率:SR=I5 I I 第一级增益:I I1=?I I2 I II2+I II4=?2I I1 I5(I2+I3) 第二级增益:I I2=?I I6 I II6+I II7=?2I I6 I6(I6+I7) 单位增益带宽:GB=I I2 I I 输出级极点:I2=?I I6 I I 零点:I1=I I6 I I 正CMR:I II,III=I II?√5 I3 ?|I II3|(III)+I II1,III 负CMR:I II,III=√I5 I1+I II5,饱和 +I II1,III+I II 饱和电压:I II,饱和=√2I II I 功耗:I IIII=(I8+I5+I7)(I II+I II) 四、实验目的 本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于: 根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。 学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。 五、实验内容 1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。 2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。 3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

实验一组合逻辑电路设计

实验一组合逻辑电路设计 一、实验目的 1、熟悉应用中小规模数字集成电路的工程技术; 2、掌握组合逻辑电路的设计方法。 二、设计步骤 对于某些对象的启动/停止或者打开/闭合等一类二值控制问题(电气工程称之为乒乓控制),往往可以抽象归纳成为逻辑问题。使用数字逻辑电路实现解决这一逻辑问题的电路系统,即可实现逻辑控制。使用小规模(SSI)数字集成电路进行组合逻辑电路设计的步骤是: 1、分析实际问题进行逻辑抽象:定义输入或输出变量并进行逻辑赋值,即确定True (1)或False (0)表示的含义。在此基础上列出逻辑真值表。 2、由真值表写出逻辑函数表达式并化简为最简式。 3、按照化简后的表达式画出逻辑函数原理图。 为了降低电路成本、便于系统安装和未来维修,有经验的工程师常常设法用尽可能少的数字集成电路种类和芯片数目来实现设计。因此2,3两步骤应统筹考虑。 4、查阅集成电路手册确定电路中所使用的芯片型号和具体的引脚连 接关系。 5、正确地焊接(连接)电路,在确认无误后上电试验,测试电路的逻辑关系是否实现真值表(解决逻辑问题)。当然,这需要解决全部有关逻辑变量的状态设定和输出逻辑状态的测试问题。值得说明,一种专门测试逻辑电平的常用工具是“逻辑笔”。 三、设计要求 请设计组合逻辑电路解决如下逻辑问题: 1、某竞技运动项目设主裁判一名,副裁判两名。比赛规则是:主裁判和至少一名副裁判判定某运动员胜利,则该运动员取胜。设计实现电子裁判机。 2、某储液罐设有大小各一个补液泵和高、中、低液位传感器。三个传感器都在页面低于其监测的位置时发出信号,否则没有信号输出。由于结构上的原因,高位传感器不会出故障;其余两个传感器在液面高于其监测位置时决不会产生错误的信号输出,但却可能在故障时发不出信号来。设计电路系统实现如下控制要求:液面达到或超过高位时补液泵全停;液面低于高位而高于中位时,小泵启动工作,大泵停止;液面低于中位而高于低位时,大泵启动工作,小泵停止;液面低于低位时,大小两泵同时启动工作。在实现上述控制要求的同时给出传感器发生故障的报警信号。

集成电路系统设计实验

实验一集成电路系统EDA软件使用简介 (基础性实验) 一实验目的 1、了解利用Quartus II 8.0 软件开发数字电路的基本流程以及掌握Quartus II软件 的详细操作。 2、了解使用VHDL原理图设计进行集成电路系统设计的实现方法。 3、掌握Quartus II 8.0 软件开发数字电路的基本设计思路,软件环境参数配置,时 序仿真,管脚分配,并且利用JTAG接口进行下载的常规设计流程。 二实验前的准备 1、将红色的MODUL_SEL拨码开关组合的1、 2、8拨上, 3、 4、 5、 6、7拨下,使数码 管显示当前模式为:C1. 2、检查JTAG TO USB转换接口和USB连接线的连接,并且将JTAG线连接到核心板上的 JTAG接口(核心板的第二个十针的插口)处。 三实验要求 学习使用Quartus II 8.0软件,掌握VHDL文本描述和原理图描述的RTL级描述方法。 四实验内容 (一)了解门电路元件库 1、新建原理图设计文件,并在原理图设计文件的基础上插入各种基本门电路元件,包 括与门、或门、非门、异或门等。 2、利用原理图图形编辑窗,将基本门电路元件进行连接,形成布线。 3、为连接好的门电路组合电路添加输入和输出端口。 (二)了解逻辑电路的仿真 1、保存原理图设计文件,新建时序仿真文件。 2、将各端口的信号标出,并对其实施功能仿真或时序仿真。并将仿真波形写入实验报 告。 (三)了解原理图文件的综合和下载 1、对原理图文件进行综合和引脚连结。 2、将对应FPGA端口连接至原理图电路端口中,并将原理图文件综合后的网表文件下载 到FPGA中,进行功能验证。 3、将硬件功能情况描述记录于实验报告中。

电源滤波电路滤波原理图解

电源滤波电路的滤波原理图解 滤波电路主要有下列几种:电容滤波电路,这是最基本的滤波电路;π 型 RC 滤波电路;π 型 LC 滤波电路;电子滤波器电路。 1. 单向脉动性直流电压的特点 如图 1(a)所示。是单向脉动性直流电压波形,从图中可以看出,电压的方向性无论在何时都是一致的,但在电压幅度上是波动的,就是在时间轴上,电压呈现出周期性的变化,所以是脉动性的。 但根据波形分解原理可知,这一电压可以分解一个直流电压和一组频率不同的交流电压,如图 1(b)所示。在图 1(b)中,虚线部分是单向脉动性直流电压 U。中的直流成分,实线部分是 UO 中的交流成分。 2. 电容滤波原理 根据以上的分析,由于单向脉动性直流电压可分解成交流和直流两部分。在电源电路的滤波电路中,利用电容器的“隔直通交”

的特性和储能特性,或者利用电感“隔交通直”的特性可以滤除电压中的交流成分。图 2 所示是电容滤波原理图。 图 2(a)为整流电路的输出电路。交流电压经整流电路之后输出的是单向脉动性直流电,即电路中的 UO。 图 2(b)为电容滤波电路。由于电容 C1 对直流电相当于开路,这样整流电路输出的直流电压不能通过C1 到地,只有加到负载 RL 图为 RL 上。对于整流电路输出的交流成分,因 C1 容量较大,容抗较小,交流成分通过 C1 流到地端,而不能加到负载 RL。这样,通过电容 C1 的滤波,从单向脉动性直流电中取出了所需要的直流电压 +U。 滤波电容 C1 的容量越大,对交流成分的容抗越小,使残留在负载 RL 上的交流成分越小,滤波效果就越好。 3. 电感滤波原理

图 3 所示是电感滤波原理图。由于电感 L1 对直流电相当于通路,这样整流电路输出的直流电压直接加到负载 RL 上。 对于整流电路输出的交流成分,因 L1 电感量较大,感抗较大,对交流成分产生很大的阻碍作用,阻止了交流电通过 C1 流到加到负载 RL。这样,通过电感 L1 的滤波,从单向脉动性直流电中取出了所需要的直流电压 +U。 滤波电感 L1 的电感量越大,对交流成分的感抗越大,使残留在负载 RL 上的交流成分越小,滤波效果就越好,但直流电阻也会增大。

实验三 三极管放大电路设计

东南大学电工电子实验中心 实验报告 课程名称:电子电路实验 第 3 次实验 实验名称:三极管放大电路设计 院(系):吴健雄学院专业:电类强化班 姓名:梅王智汇学号:61012215 实验室: 101 实验组别: 同组人员:实验时间:2014年 5 月 4 日评定成绩:审阅教师:

实验三 三极管放大电路设计 一、实验目的 1. 掌握单级放大电路的设计、工程估算、安装和调试; 2. 了解三极管、场效应管各项基本器件参数、工作点、偏置电路、输入阻抗、输出阻抗、 增益、幅频特性等的基本概念以及测量方法; 3. 了解负反馈对放大电路特性的影响。 4. 掌握多级放大电路的设计、工程估算、安装和调试; 5. 掌握基本的模拟电路的故障检查和排除方法,深化示波器、稳压电源 、交流毫伏表、 函数发生器的使用技能训练。 二、预习思考: 1. 器件资料: 上网查询本实验所用的三极管9013的数据手册,画出三极管封装示意图,标出每个管脚的名称,将相关参数值填入下表: 2. 偏置电路: 图3-3中偏置电路的名称是什么?简单解释是如何自动调节晶体管的电流I C 以实现稳定直流工作点的作用的,如果R 1、R 2取得过大能否再起到稳定直流工作点的作用,为什么? 答:该偏置电路是分压偏置电路,利用R1,R2对电源电压进行了分压,保证了基极电压稳定为:2 12 BQ CC R U V R R = +。这样就为电路提供了稳定的工作点。就是当环境 温度升高时,I CQ ≈I EQ 增加,U EQ =I EQ R E 增大,由于U BQ 的基本固定,U BEQ =U BQ -U EQ 减小,又使I EQ 减小,抑制I CQ 增加,通过这样的自动调节就稳定了静态工作点。 如果R1,R2取值过大,以至于接近输入电阻R i ,就会导致流入基极的电流不可忽略,工作点不稳定。 3. 电压增益:

电感滤波电路作用原理

电感滤波电路作用原理 Final revision by standardization team on December 10, 2020.

电容滤波电路电感滤波 电路作用原理 整流电路的输出电压不是纯粹的直流,从示波器观察整流电路的输出,与直流相差很大,波形中含有较大的脉动成分,称为纹波。为获得比较理想的直流电压,需要利用具有储能作用的电抗性元件(如电容、电感)组成的滤波电路来滤除整流电路输出电压中的脉动成分以获得直流电压。 常用的滤波电路有无源滤波和有源滤波两大类。无源滤波的主要形式有电容滤波、电感滤波和复式滤波(包括倒L型、LC滤波、LCπ型滤波和RCπ型滤波等)。有源滤波的主要形式是有源RC滤波,也被称作电子滤波器。直流电中的脉动成分的大小用脉动系数来表示,此值越大,则滤波器的滤波效果越差。 脉动系数(S)=输出电压交流分量的基波最大值/输出电压的直流分量。 半波整流输出电压的脉动系数为S=1.57,全波整流和桥式整流的输出电压的脉动系数S≈O.67。对于全波和桥式整流电路采用C型滤波电路后,其脉动系数S=1/(4(RLC/T-1)。(T为整流输出的直流脉动电压的周期。) 一、电阻滤波电路: RC-π型滤波电路,实质上是在电容滤波的基础上再加一级RC滤波电路组成的。如图1(B)RC滤波电路。若用S表示C1两端电压的脉动系数,则输出电压两端的脉动系数 S=(1/ωC2R)S。

由分析可知,电阻R的作用是将残余的纹波电压降落在电阻两端,最后由C2再旁路掉。在ω值一定的情况下,R愈大,C2愈大,则脉动系数愈小,也就是滤波效果就越好。而R值增大时,电阻上的直流压降会增大,这样就增大了直流电源的内部损耗;若增大C2的电容量,又会增大电容器的体积和重量,实现起来也不现实。这种电路一般用于负载电流比较小的场合。 二、电感滤波电路: 根据电抗性元件对交、直流阻抗的不同,由电容C及电感L所组成的滤波电路的基本形式如图1所示。因为电容器C对直流开路,对交流阻抗小,所以C并联在负载两端。电感器L对直流阻抗小,对交流阻抗大,因此L应与负载串联。 并联的电容器C在输入电压升高时,给电容器充电,可把部分能量存储在电容器中。而当输入电压降低时,电容两端电压以指数规律放电,就可以把存储的能量释放出来。经过滤波电路向负载放电,负载上得到的输出电压就比较平滑,起到了平波作用。若采用电感滤波,当输入电压增高时,与负载串联的电感L中的电流增加,因此电感L将存储部分磁场能量,当电流减小时,又将能量释放出来,使负载电流变得平滑,因此,电感L也有平波作用。 利用储能元件电感器L的电流不能突变的特点,在整流电路的负载回路中串联一个电感,使输出电流波形较为平滑。因为电感对直流的阻抗小,交流的阻抗大,因此能够得到较好的滤波效果而直流损失小。电感滤波缺点是体积大,成本高。

实验一 原理图输入方式设计数字逻辑电路

实验一原理图输入方式设计数字逻辑电路 一、实验目的: 1、了解基本组合逻辑电路的原理及利用Quartus II 软件进行设计的一般方法。 2、熟悉Quartus II 原理图输入法的设计流程,掌握编辑、编译和仿真的方法。 3、掌握原理图的层次化设计方法。 4、了解Quartus II 软件的编程下载及引脚锁定的方法。 5、了解Quartus II宏功能模块的使用方法。 二、实验的硬件要求: 1、EDA/SOPC实验箱。 2、计算机。 三、实验原理 见附件《Quartus设计的一般步骤》、《元件例化和调用的操作步骤》、《QuartusII基于宏功能模块的设计》 四、实验内容: 1、用原理图方式设计1位二进制半加器半加器。 新建一个工程“HalfAdder”,选择芯片“Cyclone III EP3C16Q240C8”,建立原理图如图1-1,保存为“HalfAdder.BDF”。 图1-1 半加器电路图 编译工程。 建立波形文件,对半加器电路分别进行时序仿真和功能仿真,其波形如下: 图1-2半加器时序仿真波形,注意观察输出延时,以及毛刺的产生原因 图1-3半加器功能仿真波形 2、原理图层次化设计。 新建一工程,取名“FullAdder”;将上面设计的半加器“HalfAdder.BDF”复制到当前工程目录,并生成“符号元件”HalfAdder.BSF。 建立一个原理图文件,取名“FullAdder.BDF”,利用“符号元件”HalfAdder.BSF及其它元件设计全加器电路如下图:

用功能仿真测试全加器的逻辑功能。 图1-5 全加器功能仿真波形 图1-6是输入输出信号与FPGA连接示意图,图中用到了“拨档开关”作为输入,“LED 显示模块”显示输出值。表1-1是本实验连接的FPGA管脚编号。

集成电路设计实验报告

集成电路设计 实验报告 时间:2011年12月

实验一原理图设计 一、实验目的 1.学会使用Unix操作系统 2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件 二:实验内容 使用schematic软件,设计出D触发器,设置好参数。 二、实验步骤 1、在桌面上点击Xstart图标 2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入 用户密码,在protocol:中选择telnet类型 3、点击菜单上的Run!,即可进入该用户unix界面 4、系统中用户名为“test9”,密码为test123456 5、在命令行中(提示符后,如:test22>)键入以下命令 icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。 出现的主窗口所示: 6、建立库(library):窗口分Library和Technology File两部分。Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。 7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输 入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。当然在Tool工具中还有很多别的

LC滤波电路原理及设计详解

LC滤波电路 LC滤波器也称为无源滤波器,是传统的谐波补偿装置。LC滤波器之所以称为无源滤波器,顾名思义,就是该装置不需要额外提供电源。LC滤波器一般是由滤波电容器、电抗器和电阻器适当组合而成,与谐波源并联,除起滤波作用外,还兼顾无功补偿的需要; 无源滤波器,又称LC滤波器,是利用电感、电容和电阻的组合设计构成的滤波电路,可滤除某一次或多次谐波,最普通易于采用的无源滤波器结构是将电感与电容串联,可对主要次谐波(3、5、7)构成低阻抗旁路;单调谐滤波器、双调谐滤波器、高通滤波器都属于无源滤波器。 LC滤波器的适用场合 无源LC电路不易集成,通常电源中整流后的滤波电路均采用无源电路,且在大电流负载时应采用LC电路。 有源滤波器适用场合 有源滤波器电路不适于高压大电流的负载,只适用于信号处理, 滤波是信号处理中的一个重要概念。滤波分经典滤波和现代滤波。 经典滤波的概念,是根据富立叶分析和变换提出的一个工程概念。根据高等数学理论,任何一个满足一定条件的信号,都可以被看成是由无限个正弦波叠加而成。换句话说,就是工程信号是不同频率的正弦波线性叠加而成的,组成信号的不同频率的正弦波叫做信号的频率成分或叫做谐波成分。只允许一定频率范围内的信号成分正常通过,而阻止另一部分频率成分通过的电路,叫做经典滤波器或滤波电路 电容滤波电路电感滤波电路作用原理 整流电路的输出电压不是纯粹的直流,从示波器观察整流电路的输出,与直流相差很大,波形中含有较大的脉动成分,称为纹波。为获得比较理想的直流电压,需要利用具有储能作用的电抗性元件(如电容、电感)组成的滤波电路来滤除整流电路输出电压中的脉动成分以获得直流电压。 常用的滤波电路有无源滤波和有源滤波两大类。无源滤波的主要形式有电容滤波、电感滤波和复式滤波(包括倒L型、LC滤波、LCπ型滤波和RCπ型滤波等)。有源滤波的主要形式是有源RC滤波,也被称作电子滤波器。直流电中的脉动成分的大小用脉动系数来表示,此值越大,则滤波器的滤波效果越差。 脉动系数(S)=输出电压交流分量的基波最大值/输出电压的直流分量 半波整流输出电压的脉动系数为S=1.57,全波整流和桥式整流的输出电压的脉动系数S≈O.67。对于全波和桥式整流电路采用C型滤波电路后,其脉动

电路辅助设计报告 1.

上海电力学院 本科课程设计 电路计算机辅助设计 (1) 院系:电力与自动化工程学院 专业年级(班级): 学生姓名:学号: 指导教师: 成绩: 年月日 教师评语:

目录 (一)电路模型和电路定律及功率测量,含受控源电路分析仿真-----------------------------------------------------------------------1 (二)戴维宁定理诺顿定理结点电压法及回路电流法的仿真----------------------------------------------------------------------4 (三)运算放大器电路分析仿真 ----------------------------------------------------------------------8 (四)正弦稳态电路的分析(1、谐振电路) ---------------------------------------------------------------------10(五)三相交流稳态电路辅助分析仿真 ---------------------------------------------------------------------14(六)非正弦交流电路的分析仿真 ---------------------------------------------------------------------17(七)正弦稳态电路分析仿真(2、互感电路仿真) ---------------------------------------------------------------------24

电路原理图设计及Hspice实验报告

电子科技大学成都学院 (微电子技术系) 实验报告书 课程名称:电路原理图设计及Hspice 学号: 姓名: 教师: 年06月15日 实验一基本电路图的Hspice仿真 实验时间:同组人员: 一、实验目的 1.学习用Cadence软件画电路图。 2.用Cadence软件导出所需的电路仿真网表。 3.对反相器电路进行仿真,研究该反相器电路的特点。 二、实验仪器设备 Hspice软件、Cadence软件、服务器、电脑 三、实验原理和内容 激励源:直流源、交流小信号源。 瞬态源:正弦、脉冲、指数、分线段性和单频调频源等几种形式。 分析类型:分析类型语句由定义电路分析类型的描述语句和一些控制语句组成,如直流分析(.OP)、交流小信号分析(.AC)、瞬态分析(.TRAN)等分析语句,以及初始状态设置(.IC)、选择项设置(.OPTIONS)等控制语句。这类语句以一个“.”开头,故也称为点语句。其位置可以在标题语句之间的任何地方,习惯上写在电路描述语句之后。 基本原理:(1)当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|> |UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD,即输出电平. (2)当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0<|UTP|,因此V2截止。此时UO=UOL≈0,即输出为低电平。可见,CMOS反相器实现了逻辑非的功能. 四、实验步骤

1.打开Cadence软件,画出CMOS反相器电路图,导出反相器的HSPICE网表文件。 2.修改网表,仿真出图。 3.修改网表,做电路的瞬态仿真,观察输出变化,观察波形,并做说明。 4.对5个首尾连接的反相器组成的振荡器进行波形仿真。 5.分析仿真结果,得出结论。 五、实验数据 输入输出仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos *.tran 200p 20n .dc vin 0 5 1m sweep data=w .print v(1) v(2) .param wp=10u wn=10u .data w wp wn 10u 10u 20u 10u 40u 10u 40u 5u .enddata vcc vcc 0 5 vin in 0 2.5 *pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=wp m2 out in 0 0 nch l=1u w=wn .alter vcc vcc 0 3 .end 图像: 瞬态仿真: 网表: * lab2c - simple inverter .options list node post .model pch pmos .model nch nmos .tran 200p 20n .print tran v(1) v(2) vcc vcc 0 5 vin in 0 2.5 pulse .2 4.8 2n 1n 1n 5n 20n cload out 0 .75p m1 vcc in out vcc pch l=1u w=20u

集成电路设计实验2

集成电路设计实验报告 院别:电信学院专业:电子科学与技术 班级:电子姓名:学号:组序: 实验(二)题目名称:CMOS反相器的版图设计(PMOS、NMOS) 成绩:教师签名:批改时间: 一、实验目的: 在集成电路设计当中,集成电路设计软件的介入大大的缩短了开发周期,减小了设计风险,使得我们在设计的时候可以发现并改正电路设计上的绝大多数bug。所以说学习设计软件已经成为集成电路设计工程师的必修课。而Ledit软件以其良好的人机操作界面,以及强大的设计规则检查能力而在集成电路的设计当中充当了很重要的角色。在此次试验当中我们需要独立完成CMOS反相器的版图设计,规则检查,以及排除错误工作。从而达到比较熟练的掌握Ledit 的基本功能已经操作方法。 二、实验要求: 如将设计好的电路制成实际使用的集成块,就必须利用版图工具将设计的电路采用标准工艺文件转换成可以制造的版图。然后再将版图提交给集成电路制造厂家(foundry),完成最后的集成块制造,所以画版图的本质就是画电路原理图。 在画版图时,首先要明白工艺文件的含义,每一种工艺文件代表一条工艺线所采用的光刻尺寸,以及前后各个工序等等;其次要懂得所使用的工具步骤及各个菜单及菜单栏的内容,以便熟练使用该软件;最后对所画版图进行验证,确保不发生错误。 此外,还必须了解所使用的版图设计法则,对于不同的工艺尺寸其法则有所不同,这就要求设计者在应用该软件时,必须熟悉相应的设计法则,为完成正确的版图做准备。该实验原理是画常见的CMOS反相器,画版图时要求熟悉CMOS反相器的工艺过程及设计法则。

三、实验方法: 首先在实验一的基础上进一步熟悉L-EDIT版图设计软件的工具及工艺库,比较熟练地掌握该软件画版图的方法。以CMOS反相器为例,在前面画的PMOS、NMOS 的基础上,通过调用将他们组合到一起,再完成整个CMOS反相器的设计,设计完成后运用该软件的设计规则对所画的版图进行DRC验证,并修改不正确的部分,直至设计无错误。 四、实验内容: 1.运行L-Edit程序时,L-Edit会自动将工作文件命名为Layout1.tdb并显示在窗口的标题栏上。 2.另存为新文件:选择执行File/Save As子命令,将自己的工程文件保存在C:\DocumentsandSettings\Administrator\桌面\实验相关\Tanner\Ledit90\Samples\SPR\exam ple1中,在“文件名”文本框中输入新文件名称:NOMS。保存到example目录的原因是防止后面做剖视图的时候没法进行。 3.替换设置信息:选择执行File/Replace Setup子命令打开对话框,单击“From File”栏填充框的右侧的Browser按钮,选择C:\Documents and Settings\Administrator\桌面\实验相关\Tanner\Ledit90\Samples\SPR\example1\lights.tdb文件,如图所示,单击OK就将lights.tdb文件中的格点、图层、以及设计规则等设定应用在当前工程中。 4.画出PMOS:按照实验一的步骤,设计PMOS的版图。并进行相应的规则检查,直到没有错误。画好后如图所示:

电子电路综合设计实验报告

电子电路综合设计实验报告 实验5自动增益控制电路的设计与实现 学号: 班序号:

一. 实验名称: 自动增益控制电路的设计与实现 二.实验摘要: 在处理输入的模拟信号时,经常会遇到通信信道或传感器衰减强度大幅变化的情况; 另外,在其他应用中,也经常有多个信号频谱结构和动态围大体相似,而最大波幅却相差甚多的现象。很多时候系统会遇到不可预知的信号,导致因为非重复性事件而丢失数据。此时,可以使用带AGC(自动增益控制)的自适应前置放大器,使增益能随信号强弱而自动调整,以保持输出相对稳定。 自动增益控制电路的功能是在输入信号幅度变化较大时,能使输出信号幅度稳定不变或限制在一个很小围变化的特殊功能电路,简称为AGC 电路。本实验采用短路双极晶体管直接进行小信号控制的方法,简单有效地实现AGC功能。 关键词:自动增益控制,直流耦合互补级,可变衰减,反馈电路。 三.设计任务要求 1. 基本要求: 1)设计实现一个AGC电路,设计指标以及给定条件为: 输入信号0.5?50mVrm§ 输出信号:0.5?1.5Vrms; 信号带宽:100?5KHz; 2)设计该电路的电源电路(不要际搭建),用PROTE软件绘制完整的电路原理图(SCH及印制电路板图(PCB 2. 提高要求: 1)设计一种采用其他方式的AGC电路; 2)采用麦克风作为输入,8 Q喇叭作为输出的完整音频系统。 3. 探究要求: 1)如何设计具有更宽输入电压围的AGC电路; 2)测试AGC电路中的总谐波失真(THD及如何有效的降低THD 四.设计思路和总体结构框图 AGC电路的实现有反馈控制、前馈控制和混合控制等三种,典型的反馈控制AGC由可变增益放大器(VGA以及检波整流控制组成(如图1),该实验电路中使用了一个短路双极晶体管直接进行小信号控制的方法,从而相对简单而有效实现预通道AGC的功能。如图2,可变分压器由一个固定电阻R和一个可变电阻构成,控制信号的交流振幅。可变电阻采用基极-集电极短路方式的双极性晶体管微分电阻实现为改变Q1电阻,可从一个由电压源V REG和大阻值电阻F2组成的直流源直接向短路晶体管注入电流。为防止Rb影响电路的交流电压传输特性。R2的阻值必须远大于R1。

电路辅助设计上

实验一:功率的测定以及仿真 1.仿真实验目的 (1)验证各电阻的功率和电压源的功率,并且验证整个电路输出功率和吸收功率相等,即整个电路功率守恒; (2)、学习利用仿真仪表分析检验各电阻功率和对电压表电流表的运用。 2.实验原理及说明 A. 本次实验的电路图以及连接方式如图1.1所示:利用环路电流法可列出方程 B. )(36_)(31234232131=?-?++=??+R R R R V R R R i i i i l l i l 图1.1 C .电路连接好之后,按照电流表和电压表的示数,根据I U P ?=可以算出电压源的功率,再根据连接在各电阻上的功率表,读出各电阻的功率 321,,P P P ,根据4321P +++=P P P P 吸收可以算出电路吸收的功 率;根据I U P P ?==电源释放可以算出电路释放的功率。 .若释放吸收P P =,则说明整个电路吸收与释放的功率相等。 3.仿真实验的步骤与内容 按照原理图1.1所示,连接电路,如下图1.2所示 读数,如下图1.3所示我们可以得到:U=36.0V,I=9.0A,又由0 )(36_)(31234232131=?-?++=??+R R R R V R R R i i i i l l i l 计算出实 验一致。

36V I U =?=释放P ; 4321P +++=P P P P 吸收=424323222121I R I R I R I R +++=162+18+108+36=324W 由上可得,释放 吸收P P =,所以整个电路是功率守恒的 R12Ω XMM1 R2 2Ω V136 V XWM1 V I XWM2 V I XWM3 V I R3 3Ω XWM4 V I R44Ω U1 DC 1e-009Ohm 0.000 A + - 图1.2 图1.3