超大规模集成电路课程设计报告

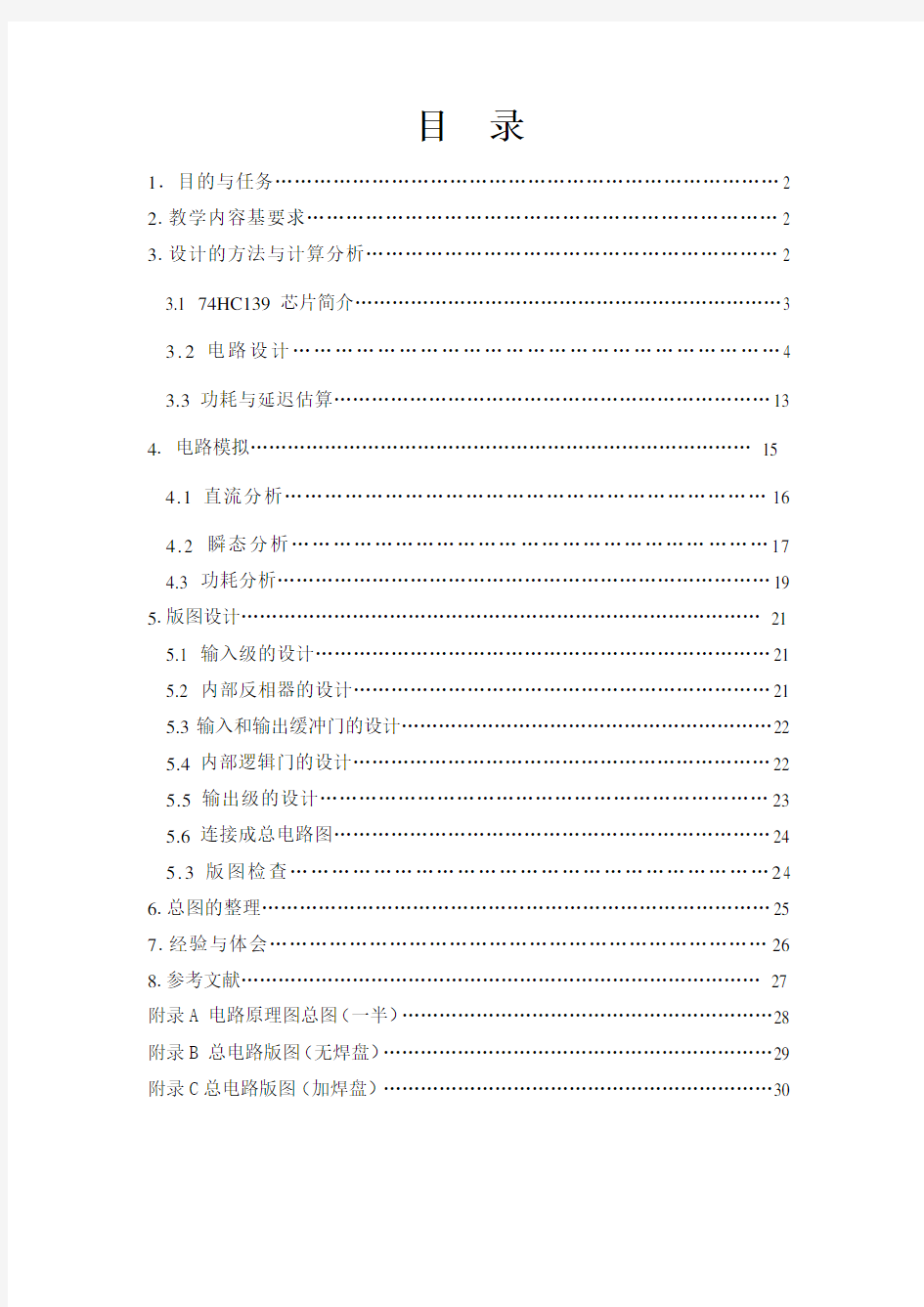

目录

1.目的与任务 (2)

2.教学内容基要求 (2)

3.设计的方法与计算分析 (2)

3.1 74HC139芯片简介 (3)

3.2电路设计 (4)

3.3功耗与延迟估算 (13)

4.电路模拟 (15)

4.1直流分析 (16)

4.2 瞬态分析 (17)

4.3 功耗分析 (19)

5.版图设计 (21)

5.1 输入级的设计 (21)

5.2 内部反相器的设计 (21)

5.3输入和输出缓冲门的设计 (22)

5.4内部逻辑门的设计 (22)

5.5输出级的设计 (23)

5.6连接成总电路图 (24)

5.3版图检查 (24)

6.总图的整理 (25)

7.经验与体会 (26)

8.参考文献 (27)

附录A 电路原理图总图(一半) (28)

附录B 总电路版图(无焊盘) (29)

附录C总电路版图(加焊盘) (30)

集成电路课程设计

1. 目的与任务

本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 教学内容基本要求

2.1课程设计题目及要求

器件名称:含两个2-4译码器的74HC139芯片 要求电路性能指标:

⑴可驱动10个LSTTL 电路(相当于15pF 电容负载); ⑵输出高电平时,OH I ≤20uA,

min

,OH V =4.4V; ⑶输出低电平时,

OL

I ≤4mA ,

man

OL V , =0.4V

⑷输出级充放电时间r t =f t ,pd t

<25ns ;

⑸工作电源5V ,常温工作,工作频率work f =30MHZ ,总功耗max P =15mW 。 2.2课程设计的内容 1. 功能分析及逻辑设计; 2. 电路设计及器件参数计算; 3. 估算功耗与延时; 4. 电路模拟与仿真; 5. 版图设计;

6. 版图检查:DRC 与LVS ;

7. 后仿真(选做);

8. 版图数据提交。

2.3课程设计的要求与数据 1. 独立完成设计74HC139芯片的全过程;

2. 设计时使用的工艺及设计规则: MOSIS:mhp_n05;

3. 根据所用的工艺,选取合理的模型库;

4. 选用以lambda(λ)为单位的设计规则;

5. 全手工、层次化设计版图;

6.

达到指导书提出的设计指标要求。 3. 设计的方法与计算分析

3.1 74HC139芯片简介

74HC139是包含两个2线-4线译码器的高速CMOS数字电路集成芯片,能与TTL集成电路芯片兼容,它的管脚图如图3-1所示,其逻辑真值表如表3-1所示

图3-1 74HC139管脚图

表3-1 74HC139真值表

由于74HC139芯片是由两个2-4译码器组成,两个译码器是独立的,所以,这里只分析其中一个译码器。由真值表可以看出,Cs为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。

分析其逻辑功能,可以得到逻辑表达式:

由逻辑表达式可以得到的逻辑图如图3-2所示

图3-2 74HC139逻辑图

3.2 电路设计

本次电路设计采用的是m12_20.md 模型的各参数。其参数如下: N 管:ox ε =3.9×8.85×12

10

-F/m N μ=605.3410-?Vs m /2

m t ox 10

10395-?= V V tn 8.0= P 管:ox ε=3.9×8.85×1210-F/m Vs m p /102192

4-?=μ

m t ox 1010395-?= V V tp 1-=

3.2.1输出级电路设计

据要求,输出级等效电路如图3-3所示,输入Vi 为前一级的输出,可认为是理想的输出,即iL V =SS V ,iH V =DD V 。

图3-3 输出级等效电路 ⑴输出级N 管N (W/L)的计算

当输入为高电平时,输出为低电平,N 管导通,后级TTL 有较大的灌电流输

入,要求

OL

I ≤4mA ,

man

OL V ,=0.4V ,依据MOS 管的理想电流统一方程式:

])()[()(2

22

1D T G S T G L

W t ds V V V V V V I ox

ox -----???

=μ

ε

可以求出N (W/L)的值。其主要计算如下:

()()[]

222d tn g S tn g n ox ox dsn N V V V V V V t I L W -----=???

??με

=()()[]

224

1210

34.08.0508.05103.6051085.89.3103951042-----?????????----

=47.27≈48 ⑵输出级P 管

()p L W /的计算

当输入为低电平时,输出为高电平,P 管导通。同时要求N 管和P 管的充放电时间f

r t t =,分别求出这两个条件下的

()min ,/P L W 极限值,然后取大者。

以

OH

I ≤20uA,

V

V O H 4.4min ,=为条件计算

()min ,/P L W 极限值,用

MOS 管理想

电流方程统一表达式:

])()[()(2

22

1

D T G S T G L

W t ds V V V V V V I ox

ox -----???

=μ

ε

可以求出

()p L W /的值。其主要计算如下:

()()

[

]222d tp g s tp g p ox ox dsp P V V V V V V t I L W -----=???

??με

=()()()()[]

224

1210

64.410510102191085.89.31039510202-------?????????----

≈0.47≈1

N 管和P 管的充放电时间r t 和

f

t 表达式分别为

()()()??

????? ??--+???--??? ????=dd tn dd tn dd tn dd dd tn n n ox ox L f V V V V V V V V V W L t C t 2019ln 1

1.022με(

)

(

)

()

??

????? ??--+???

?--??? ????=?dd tp

dd tp

dd tp dd dd tp p p ox ox L r V V V V V V V V V W L t C t 2019ln 11.022

με以

f

r t t =计算

()min ,/P L W 的值。其计算如下:

设

()()()??????? ??--+???--??? ???=

dd tn dd tn dd tn dd dd tn n n ox ox

V V V V V V V V V W L t Kn 2019ln 11.022με(

)

(

)

()

??

????? ??--+???

?--??? ???=?dd tp

dd tp

dd tp dd dd

tp p p ox ox

V V V V V V V V V W L t Kp 2019ln 11.022

με由

f

r t t =,故有

()()()??????? ??--+???--??? ???dd tn dd tn dd tn dd dd tn n n V V V V V V V V V W L 2019ln 11.0221

μ

=

(

)

(

)

()

??????? ??--+????--??? ???dd tp dd tp

dd tp dd dd

tp p p V V V V V V V V V W L 2019ln 11.022

1

μ

代入数据,化简可以得

6912.0102194?????? ??-n

W L =7395

.0103.6054

?????? ??-p W L =??? ??p W L 3382.0???? ??n

W L ,代入48=???

??n L W ,得到

140=???

??P

L W

比较两种方法的P L W ??? ??,取其中的最大值,即取140=??? ??P L W

3.2.2内部基本反相器中的各MOS 尺寸的计算

内部基本反相器如图3-4所示,它的N 管和P 管尺寸依据充放电时间r t 和

f

t 方程来求。关键点是先求出式中的L

C (即负载)。

图3-4 内部反相器

它的负载由以下内部反相器(如右图所示)的负载由CL 以下三部分电容组成:

①本级漏极的PN 结电容CPN ;②下级的栅电容Cg ;③连线杂散电容CS 。 ①本级漏极PN 结电容CPN 计算 CPN =Cja ×(Wb )+Cjp ×(2W+2b)

其中Cja 是每um2的结电容,Cjp 是每um 的周界电容,b 为有源区宽度,可从设计规则获取。在这里,最小孔为2λ×2λ,孔与多晶硅栅的最小间距为2λ,孔与有源区边界的最小间距为2,则取b =6λ。 总的漏极PN 结电容应是P 管 的和N 管的总和,即: CPN =Cja ×(WN +WP )b +Cjp ×(2WN +2WP +4b)

分析到整个电路一条支路大概有6个级,取tr=tf=0.5ns ,采用的模型参数有:

25./109m F C N j -?= m F C N j s w /10

25.510.-?= 24./10033.2m F C P j -?= m F C P jsw /10310.-?= 代入数据到PN C 的式子得

+????+??+????=-----6410651035.061033.2()10525.521035.06109(N PN W C ()

61010101035.010310525.562)1032----???+???+??P W =F W W P N 15991058.31003.110294.1---?+?+? (注意这里的N W 和P W 都用国际单位表示) ②栅电容Cg 计算

Cg =Cg.N +Cg.P =

此处N W 和

p

W 为与本级漏极相连的下一级N 管和P 管的栅极尺寸,近似取输出级的N W 和p

W 值。

这里N W 和p

W 采用输出级的大小进行计算。由设计规则,L=2λ,λ=1.0um ,

代入得到

F Cg 1410

11

2

61005.810

3951045.3)1038.0(2)28096(---?=??????+= ③连线杂散电容Cs

一般CPN +Cg ≈10CS ,可忽略CS 作用。所以,内部基本反相器的总负载电容L C 为上述各电容计算值之和。即有

????

??ox

ox

N t A ε???

?

??ox ox P t A ε+ =(W N +W P )L

F W W C C C P N g PN L 149910408.81003.110294.1---?+?+?=+=把L C 代入tr 和tf 的计算式,并根据tr=tf ≤25ns 的条件,计算出N W 和p

W 。N W 代入r t 的方程

有:

)10048.81003.11029.1(1035.02103074.1105.01499649-----?+?+??????=?P N N W W W (关系式⑴)

又有r t =f t 、以及f t

式子联立,可以解得

P

N W L

W L =?3382.0 →P N W W 3382.0=,联立关系式⑴可以解得

λλ1476.13≈=P W λλλ57.43382.014≈≈?=N W

即29≈??? ??P L W 10≈???

??N

L W

3.2.3 内部逻辑门MOS 尺寸的计算

内部逻辑门的电路如图3-5所示。根据截止延迟时间pLH t 和导通延迟时间 pHL t 的要求,在最坏情况下,必须保证等效N 管、P 管的等效电阻与内部基本反相器的相同,这样三输入与非门就相当于内部基本反相器了。因此,N 管的尺寸放大3倍,而P 管尺寸不变,即:

,内部反相器

,与非门,内部反相器,与非门==P P 3???

???

?? ?????

???

?? ??L W L W L W L W N N

代入内部反相器的宽长比,可以算出逻辑MOS 尺寸:

933=?=

7=

图3-5 内部逻辑门电路

3.2.4输入级设计

由于本电路是与TTL 兼容,TTL 的输入电平V iH 可能为2.4V ,如果按正常内部反相器进行设计,则N 1、P 1构成的CMOS 将有较大直流功耗。故采用图3-6示的电路,通过正反馈的P 2作为上提拉管,使V iH 较快上升,减小功耗,加快翻转速度。

图3-6 输入级电路

(1)提拉管P 2的(W/L )P2计算

为了节省面积,同时又能使V iH 较快上升,取(W/L )P2=1。理论上,这里取L=2λ,W=2λ。而且为了方便画图,这里就去L=6λ。

(2)CMOS 反相器P 1管(W/L )P1的计算

此P 1管应取内部基本反相器的尺寸(具体计算过程见内部基本反相器中各

MOS 尺寸的计算)。因此这里取7=??? ??P L W 3=???

??N

L W

(3)CMOS 反相器N1管(W/L )N1的计算

由于要与TTL 电路兼容,而TTL 的输出电平在0.4~2.4V 之间转换,因此要选取反相器的状态转变电平:

V V V V iH iL I 4.12

*min

,max ,=+=

又知:p n p

n tn tp dd I V V V V ββββ/1/*+++=

,代入数据,有

p

n p

n ββββ/1/8.0154.1++-=

→

33.4≈p n ββ→78.18≈p n ββ

式中:N

ox

ox n n L W t ???

??=

εμβ,P

ox

ox P P L W t ???

??=

εμβ,两式子相比,有 ()()()()p

n

p p n n p n L W L W L W L W /10395/10605//44--??=

=μμββ→

86725.1225.1260578.183951≈?=???

??=????? ??=??? ??P

P N L W L W L W

3.2.5 缓冲级设计

⑴输入缓冲级

由74HC139的逻辑图可知,在输入级中有三个信号:Cs 、A1、A0。其中Cs 经一级输入反相器后,形成S C , 用S C 去驱动4个三输入与非门,故需要缓冲级,使其驱动能力增加。同时为了用S C 驱动,必须加入缓冲门。由于A1、A0以及1A 、0A 各驱动内部与非门2个,所以可以不用缓冲级。 Cs 缓冲级的设计过程如下:

Cs 的缓冲级与输入级和内部门的关系如图3-7所示。

图3-7 Cs 的缓冲级

图中M1为输入级,M2为内部门,M3为缓冲级驱动门。M1的P 管和N 管的尺寸即为上述所述的输入级CMOS 反相器P1管和 N1管尺寸,M2的P 管和N 管的尺寸即为内部基本反相器P1管和 N1管尺寸,M3的P 管和N 管的尺寸由级间比值(相邻级中MOS 管宽度增加的倍数)来确定。如果要求尺寸或功耗最佳,级间比值为2~10。具体可取N 。N 为扇出系数,它的定义是:

积

前级等效反相器栅的面下级栅的面积=N

在本例中,前级等效反相器栅的面积为M 2的P 管和N 管的栅面积总和,下级

栅的面积为4个三输入与非门中与C s 相连的所有P 管和N 管的栅面积总和。

因此,λ

λλλλλλλ26214)

214218(4)()(42?+??+??=++M P L P L L W L W L W L W N 逻辑=

≈ 6.4

则353.2≈≈N

则有:2173933P 3P 3=?=?

??

????? ??=?=??? ????? ??,内部反相器

,内部反相器

==L W N L W

L W N L W N N ⑵缓冲输出级

由于输出级部分要驱动TTL 电路,其尺寸较大,因而必须在与非门输出与输出级之间加入一级缓冲门M 1,如图3-8所示。将与非门M 0等效为一个反相器,类似上述C s 的缓冲级设计,计算出M 1的P 管和N 管的尺寸。

图3-8 输出缓冲级

计算类似于输入级:

5.7112142182280296)()(2≈?+??+?=++λ

λλλλ

λλλ逻辑=

L W L W L W L W N P L M P L

4.43≈≈N

28743694P 1P 1=?=?

??

????? ??=?=?

??

????? ??,逻辑,逻辑

==L W N L W L W N L W N N

3.2.6 输入保护电路设计

因为MOS 器件的栅极有极高的绝缘电阻,当栅极处于浮置状态时,由于某种原因(如触摸),感应的电荷无法很快地泄放掉。而MOS 器件的栅氧化层极薄,这些感应的电荷使得MOS 器件的栅与衬底之间产生非常高的电场。该电场强度如果超过栅氧化层的击穿极限,则将发生栅击穿,使MOS 器件失效,因此要设置保护电路。

可设计如图3-9所示的输入保护电路。保护电路中的电阻可以是扩散电阻、多晶硅电阻或其他合金薄膜电阻,其典型值为300~500Ω。二极管的有效面积可

取500μm2,或用Shockley 方程计算。

由于保护电路计算比较复杂,因此在版图设计中直接调用库中的标准pad ,因其包含保持电路,就不必另外的保护电路设计。

图3-9 保护电路

至此,完成了全部器件的参数计算,汇总列出各级N 管和P 管的尺寸如下: 输入级:

86=??? ??N L W 7=???

??P L W 1,=?

?? ??提拉管P L W λ172=N W λ14=P W λ6,=提拉管P W

内部反相器;

3=??? ??N L W 7=???

??P

L W λ6=N W λ14=P W

输入缓冲级:

9=??? ??N L W 21=???

??P

L W λ18=N W λ42=P W

内部逻辑门:

9=??? ??N L W 7=???

??P

L W λ18=N W λ14=P W

缓冲输出级:

36=??? ??N L W 28=???

??P

L W λ72=N W λ56=P W

输出级:

48=??? ??N L W 140=???

??P

L W λ96=N W λ280=P W

3.3 功耗与延迟估算 在估算延时、功耗时,从输入到输出选出一条级数最多的支路进行估算。74HC139电路从输入到输出的所有各支路中,只有Cs 端加入了缓冲级,因而增加了延时与功耗,因此在估算延时、功耗时,就以Cs 支路电路图(如下图所示)来简化估算。

图3-10 估算延时、功耗Cs 支路电路

3.3.1 模型简化

由于在实际工作中,四个三输入与非门中只有一个可被选通并工作,而另三个不工作,所以估算功耗时只估算上图所示的支路即可。

在Cs 端经三级反相器后,将不工作的三个三输入与非门等效为负载电容C L1,而将工作的一个三输入与非门的两个输入接高电平,只将Cs 端信号加在反相器上。在X 点之前的电路,由于A 0,A 1,Cs 均为输入级,虽然A 0、A 1比Cs 少一个反相器,作为工程估算,可以认为三个输入级是相同的,于是,估算功耗时对X 点这前的部分只要计算Cs 这一个支路,最后将结果乘以3倍就可以了。在X 点之后的电路功耗,则只计算一个支路。

3.3.2 功耗估算

CMOS 电路的功耗中一般包括静态功耗、瞬态功耗、交变功耗。由于CMOS 电路忽略漏电,静态功耗近似为0,工作频率不高时,也可忽略交变功耗,则估算时只计算瞬态功耗P T 即可。P T 是上述C s 支路各级器件功耗的总和(共有6级),即:

P T =C L 总V dd 2f max

其中:L L s g PN

L C C C C C

C ++++∑∑∑1=总

PN C 为本级漏极PN 结电容,按3.2.2①相关公式计算:

31058.31003.110294.115

99X ,??+?+?=---∑P N PN W W C

前

3

1058.3)2212727(1003.1)2923286(10294.11599??+?+?+??+?+?+??=---λλF 1310247.1-?=

31058.31003.110294.11599X ,??+?+?=---∑P N PN W W C

后

31058.3)14022827(1003.1)4823629(10294.11599??++?+??++?+??=---λλ F 1310574.1-?=

g C 为与本级漏极相连的下一级栅电容,按3.2.2②的g C 计算(这里忽略输入提拉管的电容做

近似计算):

F 15.423105.081314X ,--=??=∑前

g C F 15.423105.081314X ,--=??=∑后

g C

s C 为本级漏连接到下一级栅连线杂散电容,其值较小,可忽略不计。

1L C 为断开的三个三输入的非门栅电容,按3.2.2②的g C 计算(这里取其中一个门做近似)

: 1L C =F C g 141005.8-?=

L C 为最后一级(即输出级)的下一级栅电容,即负载电容15pF 。

X 前、X 后表示Cs 支路电路中X 点之前或X 点之后的所有器件。

12

1313141313101510415.210574.1)1005.8010415.210247.1(3------?+?+?+?++?+??=总L C F 11

10

67.1-?=

对于74HC139器件,整个芯片功耗为2P T :

mW mW P P T 15024)103051067.1(226

211<=????==-总

符合设计要求。 3.3.3 延迟估算

算出每一级等效反相器延迟时间,总的延迟时间为各级(共6级)延迟时间的总和。各级等效反相器延迟时间可用下式估算:

)2

2(21)

(2

1

f r pHL pLH pd t t

t t t +≈+=

∑==6

1

i pdi pd t t

各字母的意义如图3-11所示。

图3-11 延迟时间,上升与下降时间

由上面的计算可以看出,L C ,即最后一级(即输出级)的下一级栅电容比起其它电容

都大得多,在这里为了简化运算,用最后一级功耗乘以级数进行估算。

ns W L K C t n n L f 1.4481103074.11015)(

412=????==- ns W L K C t p p L r 1.4140

1

108644.31015)(412=????==-

所以有 ns ns t t t f r 253.12)2

1

.421.4(

216)22(216<=+??=+?= 符合设计要求。

4.电路模拟

电路模拟中为了减小工作量,使用上述功耗与延迟估算部分用过的Cs 支路电路图。为了计算出功耗,在两个电源支路分别加入一个零值电压源V I1和V I2,电压值为零(如下图3-12所示),在模拟时进行直流扫描分析,然后就可得出功耗。

图3-12 电路模拟用Cs 支路电路

把此电路图转化为SPICE 文件,加入电路特性分析指令和控制语句,即可进行电路模拟。

首先,宽长比采用计算的数据,进行一次仿真模拟,但是,从仿真模拟的结果并不理想,直流分析的转变电平没有达到1.4V ,瞬时分析的输出波形是一个三角波,达不到设计要求,故为了改变转变电平,对输入级管的宽长比进行修改。为了改变瞬时分析时输出的波形,对输出级管的宽长比也进行适当的修改,以符合设计的要求。通过修改的宽长比如下: 输入级:

86=??? ??N L W 14=???

??P

L W λ172=N W λ28=P W

输出级:

240=??? ??N L W 140=???

??P

L W λ480=N W λ280=P W

修改为以上数值后,进行下列各参数的模拟分析。 4.1直流分析

直流分析:当VCS 由0.4V 变化到2.4V 过程中,观察波形得到阈值电压(状态转变电平)V I *。V I *的值应为1.4V 。直流分析的电路图如图4-1所示,其对应的SPICE 文件如图4-2所示,直流分析的输入输出电压曲线如图4-3所示。

图4-1 直流分析电路图

图4-2 直流分析SPICE 设置

图4-3 直流分析输入输出电压关系

分析:从电压关系可以看出,转变电平大约在1.4V 左右,符合设计的要求。因此所画电路通过了直流分析测试。

4.2 瞬态分析

从波形中得到t pLH 、t pHL 、t r 和t f ,然后进行相关计算。瞬态分析的电路图见图4-4所示,其对应的瞬态分析的SPICE 文件设置见图4-5所示。对应的瞬态分析的结果见图4-6。

图4-4 瞬态分析电路图

图4-5 瞬时分析SPICE设置

图4-6 瞬态分析输入输出电压关系

由W-edit 可以得到其瞬态参数如下:

t r =1.93ns t f =2.45ns t pLH =2.60ns t pHL =3.29ns

则

ns t t t t t f

r pHL pLH pd

47.1)2

2(21)(2

1

≈+≈+=

满足电路设计要求。

4.3 功耗分析

对电压源V I1和V I2进行直流扫描分析:“.dc lin source VI1 0 5 0.1 sweep lin source VI2 0 5 0.1 ”,输出“.print dc p( VI1) p(VI2)”。功耗分析的电路原理图见图4-7,SPICE 文件设置见图4-8,功耗分析结果见图4-9。

这里的功耗分析采用的是静态功耗,所以这里没有加入脉冲源,只有直流电源。

图4-7 功耗分析电路原理图

图4-8 功耗分析SPICE设置

从波形中得出p( VI1 )max=-782.46pW p(VI2)max=-102.24nW,总功耗:

1.Give a formal or descriptive definition for each of the following terms. (1)、ITRS:International Technology Roadmap for Semiconductor. (2)、Gate-Equivalent:It’s used to measure the basic unit of the complexity of the digital circuit, and based on to complete a circuit function, the number of logic gates are independent of each other.A gate equivalent stands for a unit of measure which allows specifying manufacturing-technology-independent complexity of digital electronic circuit. (3)、Technology Nodes:A Technology Nodes is defined as the ground rules of a process governed by the smallest feature printed in a repetitive array. (4)、Feature size:A single graphic minimal size.The minimum scale in integrated circuit devices.roughly half the length of the smallest transistor. (5)、IC design complexity sources:It contains chip size, power dissipation, heterogeneity, variability and reliability. (6)、Behavioral representation:It represents a design as a black box and describes its outputs in terms of its inputs and times.It indicates no geometrical information or structural information and takes the forms of textual,mathematics,or algorithmic description. (7)、Abstraction hierarchy:Abstraction hierarchies are a human invention designed to assist people in engineering very complex systems by ignoring unnecessary details.A set of interrelated representation levels that allow a system to be represented in varying amounts of detail. (8)、IC design:A design is a set of transformations from one representation of a system to another until a representation that can be fabricated exists.Integrated circuit design involves the creation of electroniccomponents,such as transistors, resistors, capacitors and the metallic interconnect of these components onto a piece of semiconductor, typically silicon. (9)、Synthesis:The process of transforming one representation in the design abstraction hierarchy into another representation. (10)、Refinement:The process of transforming functional representation in the design abstraction hierarchy into geometrical representation.Refinement is a generic

附件3 2017年智能制造新模式应用项目 任务书 项目名称: 项目责任单位(盖章): 项目责任人(法人代表): 项目技术负责人: 项目年限:20 年月至20 年月填报日期: 20 年月日 中华人民共和国工业和信息化部制 二〇年月

编写说明 1.项目任务书必须依据工业和信息化部对项目的立项批复以及通过评审的项目申报书编制,不得随意变更内容。项目总经费按照立项批复的项目总投资填写。 2.每个项目必须具备项目责任人(单位法人代表)和技术负责人。 3.项目任务书编制流程: (1)任务书由项目责任单位编制,并报送所在地省级工业和信息化主管部门; (2)根据项目立项批复和项目申报书的内容填报项目任务书; (3)项目任务书一式四份,工业和信息化部、财政部各一份;项目责任单位一份;项目责任单位所在地省级工业和信息化主管部门一份。 4.填报格式说明:请用A4幅面编辑,正文字体为4号仿宋体,单倍行距。一级标题4号黑体,二级标题4号楷体。双面打印。

智能制造专项项目基本信息项目名称 预计完成时间 预期成果类型□标准□研究报告□试验验证平台□专利□软件□智能工厂□数字化车间□其他(请注明) 项目责任单位信息单位名称单位性质□国有□民营□三资通讯地址邮政编码 所在地区单位主管部门 联系电话 组织机构代码/ 统一社会信用代 码 传真号码单位成立时间 电子信箱 项目目标产品技术水平 (新模式应用类项目填写) □国际先进□国内领先□国内先进 □其他(请注明) 标准制定基 础 □牵头制定过行业标准/国家标准□所申报标准类项目已在国家 标准或国际标准立项 智能制造基 础 □工信部两化融合管理体系贯标企业□工信部智能制造试点示 范企业□国家级两化深度融合示范企业□其他(请注明) 2014年2015年2016年 总资产(万元)负债率 主营业务收入(万元)税金(万元)利润(万元) 项目技术负责人信息 姓名性别出生日期职称最高学位从事专业固定电话移动电话传真号码电子信箱证件类型证件号码 联合单位信息单位名称单位性质 组织机构代码/统一 社会信用代码

集成电路设计 实验报告 时间:2011年12月

实验一原理图设计 一、实验目的 1.学会使用Unix操作系统 2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件 二:实验内容 使用schematic软件,设计出D触发器,设置好参数。 二、实验步骤 1、在桌面上点击Xstart图标 2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入 用户密码,在protocol:中选择telnet类型 3、点击菜单上的Run!,即可进入该用户unix界面 4、系统中用户名为“test9”,密码为test123456 5、在命令行中(提示符后,如:test22>)键入以下命令 icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。 出现的主窗口所示: 6、建立库(library):窗口分Library和Technology File两部分。Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。 7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输 入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。当然在Tool工具中还有很多别的

课程设计 班级: 姓名: 学号: 成绩: 电子与信息工程学院 电子科学系

CMOS二输入与非门的设计 一、概要 随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。而对于现代信息产业和信息社会的基础来讲,集成电路是改造和提升传统产业的核心技术。随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。 集成电路有两种。一种是模拟集成电路。另一种是数字集成电路。本论文讲的是数字集成电路版图设计的基本知识。然而在数字集成电路中CMOS与非门的制作是非常重要的。 二、CMOS二输入与非门的设计准备工作 1.CMOS二输入与非门的基本构成电路 使用S-Edit绘制的CMOS与非门电路如图1。 图1 基本的CMOS二输入与非门电路

2.计算相关参数 所谓与非门的等效反相器设计,实际上就是根据晶体管的串并联关系,再根据等效反相器中的相应晶体管的尺寸,直接获得与非门中各晶体管的尺寸的设计方法。具体方法是:将与非门中的VT3和VT4的串联结构等效为反相器中的NMOS 晶体管,将并联的VT 1、VT 2等效PMOS 的宽长比(W/L)n 和(W/L)p 以后,考虑到VT3和VT4是串联结构,为保持下降时间不变,VT 3和VT 4的等线电阻必须减小为一半,即他们的宽长比必须为反相器中的NMOS 的宽长比增加一倍,由此得到(W/L)VT3,VT4=2(W/L)N 。 因为考虑到二输入与非门的输入端IN A 和IN B 只要有一个为低电平,与非门输出就为高电平的实际情况,为保证在这种情况下仍能获得所需的上升时间,要求VT 1和VT 2的宽长比与反相其中的PMOS 相同,即(W/L)VT1,VT2=(W/L)P 。至此,根据得到的等效反向器的晶体管尺寸,就可以直接获得与非门中各晶体管的尺寸。 如下图所示为t PHL 和t PLH ,分别为从高到低和从低到高的传输延时,通过反相器的输入和输出电压波形如图所示。给其一个阶跃输入,并在电压值50%这一点测量传输延迟时间,为了使延迟时间的计算简单,假设反相器可以等效成一个有效的导通电阻R eff ,所驱动的负载电容是C L 。 图2 反相器尺寸确定中的简单时序模型 对于上升和下降的情况,50%的电都发生在: L eff C R 69.0=τ 这两个Reff 的值分别定义成上拉和下拉情况的平均导通电阻。如果测量t PHL 和t PLH ,可以提取相等的导通电阻。 由于不知道确定的t PHL 和t PLH ,所以与非门中的NMOS 宽长比取L-Edit 软件中设计规则文件MOSIS/ORBIT 2.0U SCNA Design Rules 的最小宽长比及最小长度值。 3.分析电路性质 根据数字电路知识可得二输入与非门输出AB F =。使用W-Edit 对电路进行仿真后得到的结果如图4和图5所示。

1. Shown below are buffer-chain designs. (1) Calculate the minimum delay of a chain of inverters for the overall effective fan-out of 64/1. Solution : 由题可知:64=F 根据经验6.3=opt f 为最合适的值,所以6.364===N N F f ,所以24.3=N ,但是级数必须为整数所以取3=N ,又因为1=γ,所以:15)641(3,464303=+?===p p t t f ,所以时最合适4=f 。 (2) Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V power supply, design a circuit simulation scheme to verify them with their correspondent parameters of N, f, and t p . Solution: 根据(1)中计算知道三级最合适,所以验证如下: A )、一级无负载测本征延时代码如下: .title buffer-chain 1 .lib 'C:\synopsys\Hspice_D-2010.03-SP1\tsmc018\mm018.l' TT * set 0.18um library .opt scale=0.1u * set lambda

.options post=2 list .temp 27 .global vdd Vdd vdd gnd 1.8 vin vin 0 0.9 pulse 0 1.8 25n 5p 5p 49.99n 100n $频率为10Mhz Cl vout gnd 0f $Cg1=2.46fF,负载为CL=157.44fF .subckt inv in out wn=3.5 wp=10 t=7.5 mn out in gnd gnd NCH l=2 w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t' mp out in vdd vdd PCH l=2 w=wp ad='wp*t' pd='wp+2*t' as='wp*t' ps='wp+2*t' .ends X1 vin vout inv wn=3.5 wp=10 t=7.5 .op .tran 5p 5n .meas tran voutmax max v(vout) from=5p to=5n .meas tran voutmin min v(vout) from=5p to=5n $一级 .meas tran tphl1 +trig v(vin) +val=0.9 +rise=1

《集成电路设计》课程设计实验报告 (前端设计部分) 课程设计题目:数字频率计 所在专业班级:电子科 作者姓名: 作者学号: 指导老师:

目录 (一)概述 2 2 一、设计要求2 二、设计原理 3 三、参量说明3 四、设计思路3 五、主要模块的功能如下4 六、4 七、程序运行及仿真结果4 八、有关用GW48-PK2中的数码管显示数据的几点说明5(三)方案分析 7 10 11

(一)概述 在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得十分重要。测量频率的方法有多种,数字频率计是其中一种。数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,是一种用十进制数字显示被测信号频率的数字测量仪器。数字频率计基本功能是测量诸如方波等其它各种单位时间内变化的物理量。在进行模拟、数字电路的设计、安装、调试过程中,由于其使用十进制数显示,测量迅速,精确度高,显示直观,经常要用到频率计。 频率计的基本原理是应用一个频率稳定度高的时基脉冲,对比测量其它信号的频率。时基脉冲的周期越长,得到的频率值就越准确。通常情况下是计算每秒内待测信号的脉冲个数,此时我们称闸门时间是1秒。闸门时间也可以大于或小于1秒,闸门的时间越长,得到的频率值就越准确,但闸门的时间越长则每测一次频率的间隔就越长,闸门时间越短,测的频率值刷新就越快,但测得的频率精度就受影响。 本文内容粗略讲述了我们小组的整个设计过程及我在这个过程中的收获。讲述了数字频率计的工作原理以及各个组成部分,记述了在整个设计过程中对各个部分的设计思路、程序编写、以及对它们的调试、对调试结果的分析。 (二)设计方案 一、设计要求: ⑴设计一个数字频率计,对方波进行频率测量。 ⑵频率测量可以采用计算每秒内待测信号的脉冲个数的方法实现。

) 课程设计任务书 学生姓名:王伟专业班级:电子1001班 指导教师:刘金根工作单位:信息工程学院题目: 基于CMOS的二输入与门电路 初始条件: 计算机、Cadence软件、L-Edit软件 要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) & 1、课程设计工作量:2周 2、技术要求: (1)学习Cadence IC软件和L-Edit软件。 (2)设计一个基于CMOS的二输入的与门电路。 (3)利用Cadence和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 | 学习Cadence IC和L-Edit软件,查阅相关资料,复习所设计内容的基本理论知识。 对二输入与门电路进行设计仿真工作,完成课设报告的撰写。 提交课程设计报告,进行答辩。 指导教师签名:年月日系主任(或责任教师)签名:年月日

目录 # 摘要 (2) 绪论…....………………………………………….………………….. ..3 一、设计要求 (4) 二、设计原理 (4) 三、设计思路 (4) 3.1、非门电路 (4) 3.2、二输入与非门电路 (6) 、二输入与门电路 (8) } 四、二输入与门电路设计 (9) 4.1、原理图设计 (9) 4.2、仿真分析 (10) 4.3、生成网络表 (13) 五、版图设计........................ (20) 、PMOS管版图设计 (20) 、NMOS管版图设计 (22) 、与门版图设计 (23)

电子科学与技术系 课程设计 中文题目:CMOS二输入与非门的设计 英文题目: The design of CMOS two input NAND gate 姓名:张德龙 学号: 1207010128 专业名称:电子科学与技术 指导教师:宋明歆 2015年7月4日

CMOS二输入与非门的设计 张德龙哈尔滨理工大学电子科学与技术系 [内容摘要]随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。而对于现代信息产业和信息社会的基础来讲,集成电路是改造和提升传统产业的核心技术。随着全球信息化、网络化和知识经济浪潮的到来,集成电路产业的地位越来越重要,它已成为事关国民经济、国防建设、人民生活和信息安全的基础性、战略性产业。 集成电路有两种。一种是模拟集成电路。另一种是数字集成电路。本次课程设计将要运用S-Edit、L-edit、以及T-spice等工具设计出CMOS二输入与非门电路并生成spice文件再画出电路版图。 [关键词]CMOS二输入与非门电路设计仿真

目录 1.概述 (1) 2.CMOS二输入与非门的设计准备工作 (1) 2-1 .CMOS二输入与非门的基本构成电路 (1) 2-2.计算相关参数 (2) 2-3.电路spice文件 (3) 2-4.分析电路性质 (3) 3、使用L-Edit绘制基本CMOS二输入与非门版图 (4) 3-1.CMOS二输入与非门设计的规则与布局布线 (4) 3-2.CMOS二输入与非门的版图绘制与实现 (5) 4、总结 (6) 5、参考文献 (6)

1.概述 本次课程设计将使用S-Edit画出CMOS二输入与非门电路的电路图,并用T-spice生成电路文件,然后经过一系列添加操作进行仿真模拟,计算相关参数、分析电路性质,在W-edit中使电路仿真图像,最后将电路图绘制电路版图进行对比并且做出总结。 2.CMOS二输入与非门的设计准备工作 2-1 .CMOS二输入与非门的基本构成电路 使用S-Edit绘制的CMOS与非门电路如图1。 图1 基本的CMOS二输入与非门电路 1

青岛农业大学 理学与信息科学学院 电子设计自动化及专用集成电路 课程设计报告 设计题目一、设计一个二人抢答器二、密码锁 学生专业班级 学生姓名(学号) 指导教师 完成时间 实习(设计)地点信息楼121 年 11 月 1 日

一、课程设计目的和任务 课程设计目的:本次课程设计是在学生学习完数字电路、模拟电路、电子设计自动化的相关课程之后进行的。通过对数字集成电路或模拟集成电路的模拟与仿真等,熟练使用相关软件设计具有较强功能的电路,提高实际动手,为将来设计大规模集成电路打下基础。 课程设计任务: 一、设计一个二人抢答器。要求: (1)两人抢答,先抢有效,用发光二极管显示是否抢到答题权。 (2)每人两位计分显示,打错不加分,答对可加10、20、30分。 (3)每题结束后,裁判按复位,重新抢答。 (4)累积加分,裁判可随时清除。 二、密码锁 设计四位十进制密码锁,输入密码正确,绿灯亮,开锁;不正确,红灯亮,不能开锁。密码可由用户自行设置。 二、分析与设计 1、设计任务分析 (1)二人抢答器用Verilog硬件描述语言设计抢答器,实现: 1、二人通过按键抢答,最先按下按键的人抢答成功,此后其他人抢答无效。 2、每次只有一人可获得抢答资格,一次抢答完后主持人通过复位按键复位,选手再从新抢答。 3、有从新开始游戏按键,游戏从新开始时每位选手初始分为零分,答对可选择加10分、20分,30分,最高九十分。 4、选手抢答成功时其对应的分数显示。 (2)密码锁 1、第一个数字控制键用来进行密码的输入 2、第二个按键控制数字位数的移动及调用密码判断程序。当确认后如果显示数据与预置密码相同,则LED 亮;如不相等,则无反应。按下复位键,计数等均复位

北京邮电大学 实验报告 实验题目:cmos模拟集成电路实验 姓名:何明枢 班级:2013211207 班内序号:19 学号:2013211007 指导老师:韩可 日期:2016 年 1 月16 日星期六

目录 实验一:共源级放大器性能分析 (1) 一、实验目的 (1) 二、实验内容 (1) 三、实验结果 (1) 四、实验结果分析 (3) 实验二:差分放大器设计 (4) 一、实验目的 (4) 二、实验要求 (4) 三、实验原理 (4) 四、实验结果 (5) 五、思考题 (6) 实验三:电流源负载差分放大器设计 (7) 一、实验目的 (7) 二、实验内容 (7) 三、差分放大器的设计方法 (7) 四、实验原理 (7) 五、实验结果 (9) 六、实验分析 (10) 实验五:共源共栅电流镜设计 (11) 一、实验目的 (11) 二、实验题目及要求 (11) 三、实验内容 (11) 四、实验原理 (11) 五、实验结果 (14) 六、电路工作状态分析 (15) 实验六:两级运算放大器设计 (17) 一、实验目的 (17) 二、实验要求 (17) 三、实验内容 (17) 四、实验原理 (21) 五、实验结果 (23) 六、思考题 (24) 七、实验结果分析 (24) 实验总结与体会 (26) 一、实验中遇到的的问题 (26) 二、实验体会 (26) 三、对课程的一些建议 (27)

实验一:共源级放大器性能分析 一、实验目的 1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法; 2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真; 3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线; 4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响 二、实验内容 1、启动synopsys,建立库及Cellview文件。 2、输入共源级放大器电路图。 3、设置仿真环境。 4、仿真并查看仿真结果,绘制曲线。 三、实验结果 1、实验电路图

集成电路课程设计 范例 1

集成电路课程设计 1.目的与任务 本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。 2.设计题目与要求 2.1设计题目及其性能指标要求 器件名称:含两个2-4译码器的74HC139芯片 要求电路性能指标: (1)可驱动10个LSTTL电路(相当于15pF电容负载); (2)输出高电平时,|I OH|≤20μA,V OH,min=4.4V; (3)输出底电平时,|I OL|≤4mA,V OL,man=0.4V; (4)输出级充放电时间t r=t f,t pd<25ns; (5)工作电源5V,常温工作,工作频率f work=30MHz,总功耗P max=150mW。 2.2设计要求 1.独立完成设计74HC139芯片的全过程; 2.设计时使用的工艺及设计规则: MOSIS:mhp_n12;

3.根据所用的工艺,选取合理的模型库; 4.选用以lambda(λ)为单位的设计规则; 5.全手工、层次化设计版图; 6.达到指导书提出的设计指标要求。 3.设计方法与计算 3.174HC139芯片简介 74HC139是包含两个2线-4线译码器的高速CMOS数字电路集成芯片,能与TTL集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示: 图1 74HC139芯片管脚图 表1 74HC139真值表 片选输入数据输出 C s A1 A0 Y0 Y1Y2Y3 0 0 0 0 1 1 1 0 0 1 1 0 1 0 1 0 1 1 0 1

超大规模集成电路设计 随着半导体工业的发展和工艺的深入,VLSI(超大规模集成电路)设计正迅速地向着规模越来越大,工作频率越来越高方向发展。显而易见,规模的增大和频率的提高势必将产生更大芯片的功耗,这对芯片封装,冷却以及可靠性都将提出更高要求和挑战,增加更多的成本来维护这些由功耗所引起的问题。而在便携式设备领域,如智能手机、手提电脑等现在智能生活的必需品对芯片功耗的要求更为严格和迫切。 由于时钟树工作在高频状态,随着芯片规模增大,时钟树规模也迅速增大,通过集成clockgating电路降低时钟树功耗是目前时序数字电路系统设计时节省功耗最有效的处理方法。Clockgating的集成可以在RTL 设计阶段实现,也可以在综合阶段用工具进行自动插入。由于利用综合工具在RTL转换成门级网表时自动插入clockgating的方法简单高效,对RTL无需进行改动,是目前广为采用的clockgating集成方法。 综合工具如果使用clockgating技术,那么对应的RTL综合所得的门级网表电路将如图2所示。图中增加了由LATCH和AND所组成的clockgatingcell,LATCH的LD输入端为registerbank的使能信号,LG 端(即为LATCH的时钟电平端)为CLK的反,LATCH的输出ENL和CLK信号相与(ENCLK)作为registerbank的时钟信号。如果使能信号EN为高电平,当CLK为低时,LATCH将输出EN的高电平,并在CLK为高时,锁定高电平输出,得到ENCLK,显然ENCLK的togglerate要低于 CLK,registerbank只在ENCLK的上升沿进行新的数据输出,在其他时候保持原先的DATAOUT。从电路结构进行对比,对于一组registerbank(n 个registercell)而言只需增加一个clockgatingcell,可以减少n个二路选择器,节省了面积和功耗。从时序分析而言,插入clockgatingcell之后的registerbankENCLK的togglerate明显减少,同时LATCHcell的引入抑制了EN信号对registerbank的干扰,防止误触发。所以从面积/功耗/噪声干扰方面而言,clockgating技术都具有明显优势。

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么? 集成电路的发展过程: ?小规模集成电路(Small Scale IC,SSI) ?中规模集成电路(Medium Scale IC,MSI) ?大规模集成电路(Large Scale IC,LSI) ?超大规模集成电路(Very Large Scale IC,VLSI) ?特大规模集成电路(Ultra Large Scale IC,ULSI) ?巨大规模集成电路(Gigantic Scale IC,GSI) 划分集成电路规模的标准 2.超大规模集成电路有哪些优点? 1. 降低生产成本 VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少. 2.提高工作速度 VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得. 3. 降低功耗 芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降. 4. 简化逻辑电路 芯片内部电路受干扰小,电路可简化. 5.优越的可靠性 采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。 6.体积小重量轻 7.缩短电子产品的设计和组装周期 一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度. 3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。 1、形成N阱 2、形成P阱 3、推阱 4、形成场隔离区 5、形成多晶硅栅 6、形成硅化物 7、形成N管源漏区 8、形成P管源漏区 9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺 4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么? 互连线的要求 低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化) 与器件之间的接触电阻低 长期可靠工作 可能的互连线材料 金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)

集成电路课程设计报告 设计课题: 数字电子钟的设计 姓名: 专业: 电子信息工程 学号: 日期 20 年月日——20 年月日指导教师: 国立华侨大学信息科学与工程学院

目录 1.设计的任务与要求 (1) 2.方案论证与选择 (1) 3.单元电路的设计和元器件的选择 (5) 3.1 六进制电路的设计 (6) 3.2 十进制计数电路的设计 (6) 3.3 六十进制计数电路的设计 (6) 3.4双六十进制计数电路的设计 (7) 3.5时间计数电路的设计 (8) 3.6 校正电路的设计 (8) 3.7 时钟电路的设计 (8) 3.8 整点报时电路的设计 (9) 3.9 主要元器件的选择 (10) 4.系统电路总图及原理 (10) 5.经验体会 (10) 参考文献 (11) 附录A:系统电路原理图 (12)

数字电子钟的设计 1. 设计的任务与要求 数字钟是一种…。 此次设计数字钟就是为了了解数字钟的原理,从而学会制作数字钟。而且通过数字钟的制作进一步了解…。 1.1设计指标 1. 时间以12小时为一个周期; 2. 显示时、分、秒; 3. 具有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间; 4. 计时过程具有报时功能,当时间到达整点前10秒进行蜂鸣报时; 5. 为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号。1.2 设计要求 1. 画出电路原理图(或仿真电路图); 2. 元器件及参数选择(或开发板的考虑); 3. 编写设计报告,写出设计的全过程,附上有关资料和图纸(也可直接写在 相关章节中),有心得体会。 2. 方案论证与选择 2.1 数字钟的系统方案 数字钟实际上是…

集成电路设计综合实验 题目:集成电路设计综合实验 班级:微电子学1201 姓名: 学号:

集成电路设计综合实验报告 一、实验目的 1、培养从版图提取电路的能力 2、学习版图设计的方法和技巧 3、复习和巩固基本的数字单元电路设计 4、学习并掌握集成电路设计流程 二、实验内容 1. 反向提取给定电路模块(如下图1所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。 图1 1.1 查阅相关资料,反向提取给定电路模块,并且将其整理、合理布局。 1.2 建立自己的library和Schematic View(电路图如下图2所示)。 图2 1.3 进行仿真验证,并分析其所完成的逻辑功能(仿真波形如下图3所示)。

图3 由仿真波形分析其功能为D锁存器。 锁存器:对脉冲电平敏感,在时钟脉冲的电平作用下改变状态。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。其中使能端A 加入CP信号,C为数据信号。输出控制信号为0时,锁存器的数据通过三态门进行输出。所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。锁存,就是把信号暂存以维持某种电平状态。 1.4 生成Symbol测试电路如下(图4所示) 图4

广州创亚企业管理顾问有限公司 中国集成电路设备与半导体行业分析报告

目录Contents

?1.1集成电路设备的定义 集成电路的概述 ?1.2集成电路设备的发展历程 ?1.3我国集成电路的发展历程 ?2.1集成电路设备的总体规模集成电路设备的生产现状 ?2.2集成电路设备产能状况 ?3.1半导体集成电路设备的品牌发展现状半导体集成电路设备的发展现状 ?3.2半导体集成电路设备经典工艺与现状 ?3.3半导体集成电路设备的市场容量 ?4.1半导体集成电路设备模式分析 ?4.2半导体集成电路设备行业投资环境半导体集成电路设备的发展前景 ?4.3半导体集成电路设备投资机会 ?4.3半导体集成电路设备投资方向

集成电路的概述 1.1集成电路设备的定义 集成电路(integrated circuit)是一种微型电子器件或部件。采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构;其中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。它在电路中用字母“IC”表示。集成电路发明者为杰克·基尔比(基于锗(Ge)的集成电路)和罗伯特·诺伊思(基于硅(Si)的集成电路)。当今半导体工业大多数应用的是基于硅的集成电路。

1.2集成电路的发展大事件 1947年 ?贝尔实验室肖特莱等人发明了晶体管,这是微电子技术发展中第一个里程碑。 1958年 ?仙童公司Robert Noyce与德仪公司基尔比间隔数月分别发明了集成电路,开创了世界微电子学的历史。1960年 ?H H Loor和E Castellani发明了光刻工艺。 1963年 ?F.M.Wanlass和C.T.Sah首次提出CMOS技术,如今,95%以上的集成电路芯片都是基于CMOS工艺。 1966年?美国RCA公司研制出CMOS集成电路,并研制出第一块门阵列(50门),为现如今的大规模集成电路发展奠定了坚实基础,具有里程碑意义。 1971年?Intel推出1kb动态随机存储器(DRAM),标志着大规模集成电路出现。 ?全球第一个微处理器4004由Intel公司推出,采用的是MOS工艺,这是一个里程碑式的发明。 1978年?64kb动态随机存储器诞生,不足0.5平方厘米的硅片上集成了14万个晶体管,标志着超大规模集成电路(VLSI)时代的来临。

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图

集成电路课程设计报告 课题:二输入或非门电路与版图设计 专业 电子科学与技术 学生姓名 严 佳 班 级 B 电科121 学号 1210705128 指导教师 高 直 起止日期 2015.11.16-2015.11.29

摘要 集成电路是一种微型电子器件或部件。它是采用一定的工艺,把一个电路中所需的晶体管等有源器件和电阻、电容等无源器件及布线互连在一起,制作在一小块半导体晶片上,封装在一个管壳内,执行特定电路或系统功能的微型结构。在整个集成电路设计过程中,版图设计是其中重要的一环。它是把每个原件的电路表示转换成集合表示,同时,元件间连接的线也被转换成几何连线图形。对于复杂的版图设计,一般把版图设计划分成若干个子版图进行设计,对每个子版图进行合理的规划和布图,子版图之间进行优化连线、合理布局,使其大小和功能都符合要求。 越来越多的电子电路都在使用MOS管,特别是在音响领域更是如此。MOS 管与普通晶体管相比具有输入阻抗高、噪声系数小、热稳定性好、动态范围大等优点,且它是一种压控器件,有与电子管相似的传输特性,因而在集成电路中也得到了广泛的应用。 关键词:CMOS门电路或非门集成电路

绪论 目前,集成电路经历了小规模集成、中规模集成、大规模集成和超大规模集成。单个芯片上已经可以制作包含臣大数量晶体管的、完整的数字系统。在整个集成电路设计过程中,版图设计是其中重要的一环。它是把每个原件的电路表示转换成集合表示,同时,元件间连接的线也被转换成几何连线图形。对于复杂的版图设计,一般把版图设计划分成若干个子版图进行设计,对每个子版图进行合理的规划和布图,子版图之间进行优化连线、合理布局,使其大小和功能都符合要求。版图设计有特定的规则,这些规则是集成电路制造厂家根据自己的工艺特点而制定的。不同的工艺,有不同的设计规则。设计者只有得到了厂家提供的规则以后,才能开始设计。在版图设计过程中,要进行定期的检查,避免错误的积累而导致难以修改。 1.设计要求 (1)学习Multisim软件和L-Edit软件 (2)设计一个基于CMOS的二输入或非门电路。 (3)利用Multisim和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 2.设计目的 (1)熟悉Multisim软件的使用。 (2)L-Edit软件的使用。 (3)培养自己综合运用所学知识、独立分析和解决实际问题的能力,培养创新意识和创新能力,并获得科学研究的基础训练,加深对集成电路版图设计的了解。 3.设计原理 能够实现B =“或非”逻辑关系的电路均称为“或非门”。二输入或 A L+ 非门有两个输入端A和B以及一个输出端L,只有当A端和B端同时为高电平时输出才为低电平,否则输出都为高电平。在一个或门的输出端连接一个非门就构成了“或非门”,如图1.1所示,逻辑符号如图1.2所示,真值表如图1.3所示。

集成电路原理及应用课程设计报告 \\ 题目 DDS芯片AD9850原理及应用 授课教师 学生 学号 专业

教学单位 完成时间 2011年7月1日 摘要:介绍了美国A D公司采用先进的直接数字频率合成 ( DDS )技术推出的高集成度频率合成器 A D9 8 5 0的工作原理、主要特点及其与 MCS51单片机的接口,并给出了接口电路图和部分源程序。同时给出了以AD9850为频率合成器,以AT89S52单片机为进程控制和任务调度核心来设计一个信号频率和幅度都能预置且频率稳定度高的函数信号发生器的设计方法. 引言 随着“软件无线电”技术和数字技术的飞速发展,用数字控制方法从一个参考频率源产生多种频率的技术——直接数字合成器(Direct Digital Synthesizer。DDS)被广泛应用。具体体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。现已广泛应用于通讯、导航、雷达、遥控遥测、电子对抗以及现代化的仪器仪表工业等领域。美国AD公司推出的高集成度的采用先进的CMOS技术的直接频率合成器AD9850是DDS技术的典型产品之一。AD9850是高稳定度的直接数字频率合成器件,部数据输入寄存器、可编程DDS系统、高性能数/模转换器(DAC)及高速比较器,能实现全数字编程控制的频率合成器和时钟发生器,如接上精密时钟源,AD9850可产生一个频谱纯净、频率和相位都可编程控制的正弦信号。AD9850中包含高速比较器,正弦波也可直接用作频率信号源,也可通过比较器转换成方波,作为时钟输出。本文主要介绍了高集成度频率合成器 A D9 8 5 0的工作原理、主要特点及其与 MCS51单片机的接口及应用设计。 一.特性: 1)最高125MHz的时钟频率; 2)片集成高性能模数变换器(10位ADC)和高速比较器; 3)具有良好的动态性能:在40MHz输出时,DAC的抑制寄生动态围(SFDR)仍大于50dB; 4)供电模式可选:+5v或+3.3v单电源供电;