QFN封装设计

1. Introduction

立 理 , QFN/ DFN Package (Quad Flat No-lead, Dual Flat No-lead) 中央有一個大面積的散熱片 (SMD). QFN Package ( 面 )/ DFN Package (矩形 面 ) 良 導 功 性功能 量 , (Figure 1)

QFN的封装和CSP(Chip Scale Package) , QFN , 與PCB(Print Circuit Board)的電性和機械連接是通過QFN四周底部的焊盤(Pad)與PCB焊盤(Footprint or Land Pattern)上印刷錫膏、過IR回焊流来實現的, SMT(Surface Mount Technology)

有關於PCB Footprint 設計, 目前業界 參考IPC-SM-782, 但是QFN对PCB焊盤設計仍然是屬於較新的製程, 相關的QFN Footprint設計規格仍在發展中, 所以此份Application Note提供使用者有關於QFN General Guideline。 數, Guideline , 理,

Figure 1: QFN Section View

2. QFN/ DFN Outline Drawings

有關於RichTek QFN/ DFN Package Outline 請參考RichTek Data Sheet Outline Dimension, 亦可在RichTek

Web-site 4.1.2 Outline Dimension Package Outline Dimension.

3. SMT Process

SMT 數 良率, 數 SMT 參

Point

Factors Control

Solder Paste Shippment and Storeage Tempture, Paste Expiration Date, Viscosity and Texture, Dry out, Stencil Design

PCB Quality Clean, Flat, Residue, Wrapage…

Reflow Profile Profile Depended PCB Design, PCB Thickness, Compontent…

4. Stencil Design Guideline

4.1 度 Stencil Thickness Design

, 列 : 雷 , 金 . 度 , 略 Footprint , 1:1 Footprint. IPC-7525 . 130um~150um(5~6mils) , 150um 易 連 度 ( 更 不 ), 參數

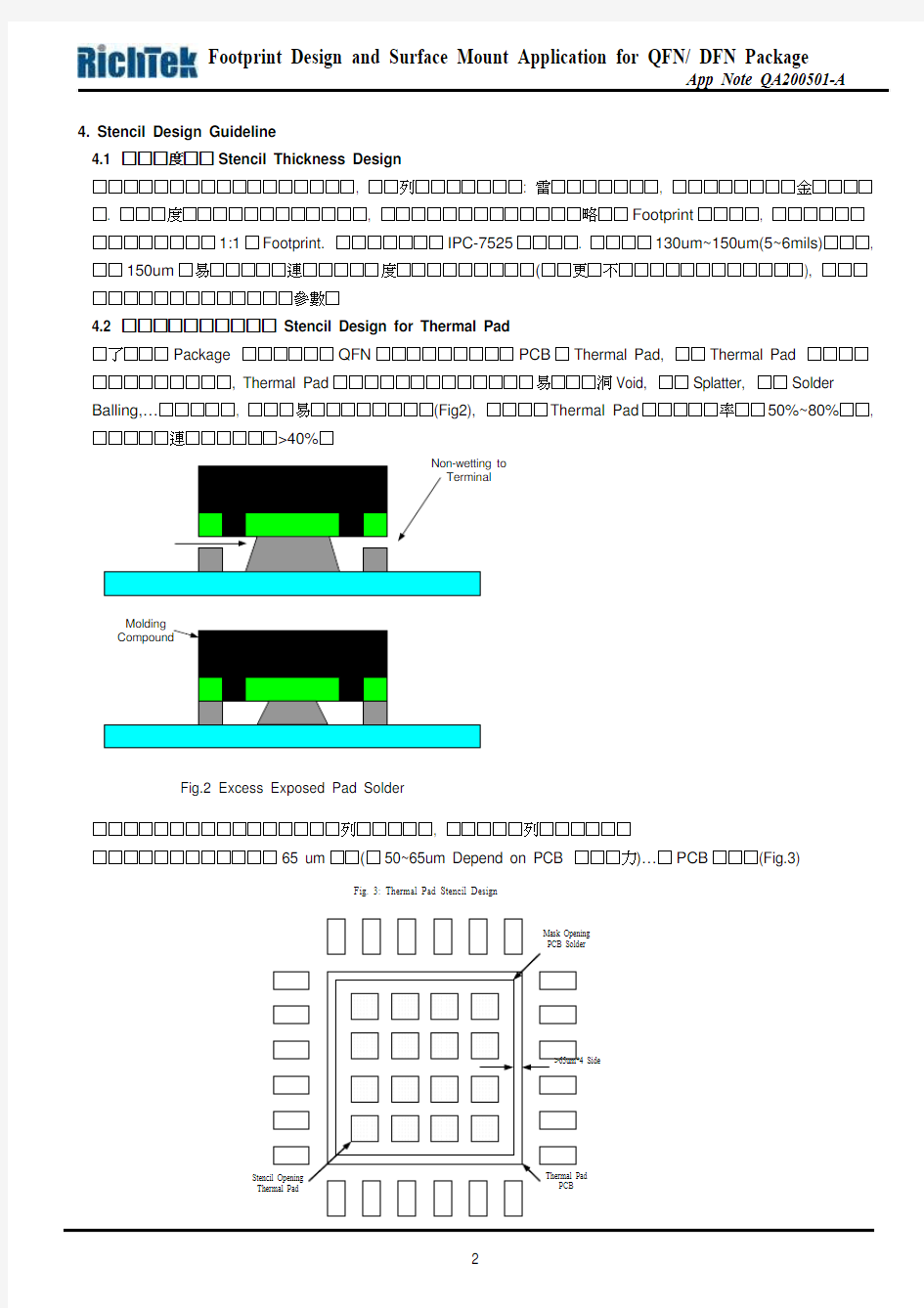

4.2 Stencil Design for Thermal Pad

了 Package QFN PCB Thermal Pad, Thermal Pad , Thermal Pad 易 洞Void, Splatter, Solder Balling,… , 易 (Fig2), Thermal Pad 率 50%~80% , 連 >40%

Fig.2 Excess Exposed Pad Solder

列 , 列

65 um ( 50~65um Depend on PCB 力)… PCB (Fig.3)

Fig. 3: Thermal Pad Stencil Design

4.3 Terminal Lead Stencil Design

Solder (Lead ) 50um~75um 立 度(Stand-off), 兩 :

Area Ratio: Area of Aperture open/ Aperture Wall Area=LW/2T(L+W) ? Area Ratio > 0.66 Aspect Ratio: Aperture With/ Stencil Thickness= W/T ? Aspect Ratio > 1.5 L: Aperture Length; W: Aperture Width; T: Stencil Thickness 5. PCB Footprint Guideline 5.1 Footprint Drawing

Table 1: Typical Footprint Dimension X: Pad Width+0.05mm; Y: Pad Length+0.20mm; ZD Max: D+ PKG Tolerance+2(0.2); GD Min: D-2(Lmax)-2(0.05); D2th: GDmin-2(CpL=0.2) & Thermal Pad Open, 兩 Package (mm)

PCB Footprint Dimension

Body Lead Pad Width Pad Length

Pitch

ZD Max GD Min ZE Max GE Min D2th E2th X Y

DFN 2*2 6 0.30 0.40 0.65 2.50 1.10 0.70 1.40 0.35

0.60 DFN 2*2 8 0.30 0.40 0.50 2.50 1.10 0.60 1.20 0.35 0.60 DFN 3*3 6 0.45 0.525 0.95 3.50 1.85 1.45 2.30 0.50 0.725 DFN 3*3 8 0.30 0.525 0.65 3.50 1.85

1.45

2.30 0.35 0.725 DFN 3*3 10 0.30 0.45 0.50

3.50 2.00 1.60 2.50 0.35 0.65 QFN 3*3 16 0.30 0.45 0.50 3.50 2.00 3.50 2.00 1.60 1.60 0.35 0.65 QFN 4*4 16 0.35 0.60 0.65

4.50 2.70 4.50 2.70 2.25 2.25 0.40 0.80 QFN 4*4 24 0.30 0.45 0.50 4.50 3.00 4.50 3.00 2.60 2.60 0.35 0.65 QFN 5*5 16 0.35 0.60 0.80

5.50 3.70 5.50 3.70 3.25 3.25 0.40 0.80 QFN 5*5 24 0.35 0.45 0.65 5.50 4.00 5.50 4.00 3.25 3.25 0.40 0.65 QFN 5*5 32 0.30 0.45 0.50 5.50 4.00 5.50 4.00 3.60 3.60 0.35 0.65 QFN 6*6 28 0.375 0.45 0.65

6.50 5.00 6.50 5.00 4.225 4.225 0.425 0.65 QFN 6*6 40 0.30 0.45 0.50

6.50

5.00

6.50 5.00 4.40 4.40 0.35 0.65

Fig. 4: Typical QFN/ DFN Footprint

Design with Package

Q FN P ad

5.2 Solder Mask Design

PCB 了 , PCB (Solder Mask), , 若 , , (Solder Mask Define: SMD). 若 , , (Non-solder Mask Defined)(Fig.5)

Lead Non-Solder Mask Defined, 來 Thermal Pad Solder Mask Defined, 來

5.3 Thermal Pad Via Design

了 PCB 金 , , Thermal Pad . 參 : 1.2mm Pitch with Via Diameter of 0.34mm( / 料 Solder Wicking, 0.25mm(0.010”) via , 例 0.34mm 1 略 0.25mm 洞)(Fig. 6)

Fig. 5 Comparison between Solder Mask Defined Pad and Non-solder Mask Defined Pad

Pad

Solder Mask Defined

Non-solder Mask Defined

5*5 Body

6*6 Body

0.34 mm Via Diameter

Fig. 6 Suggested Thermal Via Layout

SMT 連 洞 Via Solder Wicking, Thermal Pad 行類 塞 , 塞 :

PCB 爐 , 路 留

爐 , 路 防止表面錫膏流入孔內造成虛焊影響黏貼

列 塞 來 Solder Wicking: Capped Via (Copper Layer Cover Via & Plugged Material) Plugged Via (Solder Mask Cover Via & Plugged Material) Tented Via (Solder Mask Cover Via)

6. Re-flow Profile

All of RichTek’s products are requested to meet the standard of Reflow Profile in the

IPC/JEDEC J-STD-020C. (Fig.8)

Copper

Capped Via

Plugged Via

Tented Via Fig. 7 Via Type

7.0 Rework Process

PCB ? ? ? PCB ? ? IC ? IR Re-flow ?

Fig.8 IR-Re-flow Profile

元件封装库设计规范

文件编号:CHK—WI—JS-00 制订部门:技术中心 版本版次:A/0 生效日期:2012-11-22 受控印章:

文件修订记录

目录 一、库文件管理................................................................................................错误!未定义书签。 1、目得 ...........................................................................................................错误!未定义书签。 2.适用范围?错误!未定义书签。 3. 引用标准.......................................................................................................错误!未定义书签。 4。术语说明?错误!未定义书签。 5.库管理方式?错误!未定义书签。 6。库元件添加流程?错误!未定义书签。 二、原理图元件建库规范?错误!未定义书签。 1、原理图元件库分类及命名......................................................................错误!未定义书签。2、原理图图形要求......................................................................................错误!未定义书签。 3. 原理图中元件值标注规则...........................................................................错误!未定义书签。 三、PCB封装建库规范?错误!未定义书签。 1.PCB封装库分类及命名............................................................................错误!未定义书签。 2、PCB封装图形要求 (10) 四、PCB封装焊盘设计规范 .........................................................................错误!未定义书签。 1、通用要求?错误!未定义书签。 2。 AI元件得封装设计?错误!未定义书签。 3、DIP元件得封装设计...........................................................................错误!未定义书签。 4。SMT元件得封装设计?错误!未定义书签。 5。特殊元件得封装设计..............................................................................错误!未定义书签。

元件封装库设计规范初稿分析

文件编号:CHK-WI-JS-00 制订部门:技术中心 版本版次:A/0 生效日期:2012-11-22 受控印章:

文件修订记录

目录 一、库文件管理 (4) 1. 目的 (4) 2. 适用范围 (4) 3. 引用标准 (4) 4. 术语说明 (4) 5. 库管理方式 (5) 6. 库元件添加流程 (5) 二、原理图元件建库规范 (6) 1. 原理图元件库分类及命名 (6) 2. 原理图图形要求 (7) 3. 原理图中元件值标注规则 (8) 三、PCB封装建库规范 (8) 1. PCB封装库分类及命名 (9) 2. PCB封装图形要求 (11) 四、PCB封装焊盘设计规范 (11) 1.通用要求 (11) 2. AI元件的封装设计 (11) 3. DIP元件的封装设计 (12) 4. SMT元件的封装设计 (12) 5.特殊元件的封装设计 (13)

一、库文件管理 1. 目的 《元件器封装库设计规范》(以下简称《规范》)为电路元件库、封装库设计规范文档。本文档规定设计中需要注意的一些事项,目的是使设计规范化,并通过将经验固化为规范的方式,为企业内所有设计师提供完整、规范、统一的电子元器件图形符号和封装库,从而实现节省设计时间,缩短产品研发周期,降低设计差错率,提高电路设计水平的目的。 2. 适用范围 适用于公司内部研发、生产等各环节中绘制的电子电路原理图、电路板图。 3. 引用标准 3.1. 采用和遵循最新国际电气制图标准和国家军用规范 3.2. GB/T 4728-2007《电气简图用图形符号》 3.3. GB/T 7092-1993《半导体集成电路外形尺寸》 3.4. GB7581-1987《半导体分立器件外形尺寸》 3.5. GB/T 15138-1994《膜集成电路和混合集成电路外形尺寸》 3.6. GJB3243-1998《电子元器件表面安装要求》 3.7. JESD30-B-2006《半导体器件封装的描述性指定系统》 3.8. IPC-7351A-2005《表面安装设计和焊盘图形标准的通用要求》 4. 术语说明 4.1. Part Number 类型系统编号 4.2. Library Ref 原理图符号名称 4.3. Library Path 原理图库路径 4.4. description 简要描述 4.5. Component Tpye 器件类型 4.6. Footprint 真正库封装名称 4.7. SorM Footprint 标准或厂家用封装名称 4.8. Footprint path 封装库路径 4.9. Value 标注 4.10. PCB 3D 3D图形名称 4.11. PCB 3D path 3D库路径 4.12. Availability 库存量 4.13. LT 供货期 4.14. Supplier 生产商 4.1 5. Distributer 销售商 4.16. Order Information 订货号 4.17. ManufacturerP/N 物料编码 4.18. RoHS 是否无铅 4.19. UL 是否UL认证(尽量加入UL号) 4.20. Note 备注 4.21. SMD: Surface Mount Devices/表面贴装元件。 4.22. RA:Resistor Arrays/排阻。 4.23. MELF:Metal electrode face components/金属电极无引线端面元件. 4.24. SOT:Small outline transistor/小外形晶体管。 4.2 5. SOD:Small outline diode/小外形二极管。

QFN焊接方法

QFN焊接方法 QFN封装特点 QFN是一种无引脚封装,呈正方形或矩形,封装底部中央位置有一个大面积裸露焊盘用来导热,围绕大焊盘的封装外围四周有实现电气连结的导电焊盘。由于QFN封装不像传统的SOIC 与TSOP封装那样具有鸥翼状引线,内部引脚与焊盘之间的导电路径短,自感系数以及封装体内布线电阻很低,所以它能提供卓越的电性能。此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热通道,用于释放封装内的热量。通常将散热焊盘直接焊接在电路板上,并且PCB中的散热过孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。另外相对于BGA封装,QFN封装跟方便于布线,这使得QFN封装应用越来越广泛。 下图是MPU-6050封装图 工程师在开发调试阶段,总遇到需要手工焊接QFN的时候,然而头疼的是,每次都很难焊接好,本文分享一个焊接QFN芯片的方法,需要用到的工具有: 电烙铁(此处用的是刀头的,用尖头的更好)、热烘枪,焊锡丝,细金属丝,助焊剂,酒精棉签。

QFN封装焊接方法步骤: 1.芯片引脚处理,给引脚上锡,便于后期焊接 2.焊盘表面处理,让焊盘表面平整,然后涂上助焊剂 3.将芯片对准焊盘,用热风枪加热,将芯片焊接固定在电路板上 4.用烙铁处理下四周,和短接情况,让芯片更好的和焊盘焊接在一起 5.用酒精棉签清洗芯片四周的助焊剂残渣,发现有空焊和虚焊情况

6.给芯片四周再加上助焊剂 7.取一根飞线用的细金属丝,上锡(注:若用的尖头烙铁,可以省略此步骤,直接用尖头烙铁处理空焊虚焊情况) 8.然后再让金属丝贴于芯片四周用烙铁处理芯片四周的焊盘,处理空焊虚焊情况 9.再用酒精棉签擦干净,仔细检查,观察四周引脚焊接是否光亮饱满

[整理]PCB元器件封装建库规范.

XXXXXXXXXXXXX质量管理体系文件 编号:CZ-DP-7.3-03 PCB元器件封装建库规范 第 A 版 受控状态: 发放号: 2006-11-13发布 2006-11-13实施 XXXXXXXXXXX发布

1 编写目的 制定本规范的目的在于统一元器件PCB库的名称以及建库规则,以便于元器件库的维护与管理。 2 适用范围 本规范的适用条件是采用焊接方式固定在电路板上的优选元器件,以CADENCE ALLEGRO作为PCB建库平台。 3 专用元器件库 3.1 PCB工艺边导电条 3.2 单板贴片光学定位(Mark)点 3.3 单板安装定位孔

4 封装焊盘建库规范 4.1 焊盘命名规则 4.1.1器件表贴矩型焊盘: SMD[Length]_[Width],如下图所示。 通常用在SOP/SOJ/ QFP/ PLCC等表贴器件中。 如:SMD32_30 4.1.2器件表贴方型焊盘: SMD [Width]SQ,如下图所示。 如:SMD32SQ 4.1.3器件表贴圆型焊盘: ball[D],如下图所示。通常用在BGA封装中。 如:ball20

4.1.4器件圆形通孔方型焊盘: PAD[D_out]SQ[d_inn] D/U ; D代表金属化过孔, U 代表非金属化过孔。 如:PAD45SQ20D,指金属化过孔。PAD45SQ20U,指非金属化过孔。 4.1.5器件圆形通孔圆型焊盘: PAD[D_out]CIR[d_inn]D/U ; D代表非金属化过孔, U 代表非金属化过孔。 如:PAD45CIR20D,指金属化过孔。PAD45CIR20U,指非金属化过孔。 4.1.6散热焊盘 一般命名与PAD命名相同,以便查找。如PAD45CIR20D 4.1.7过孔: via[d_dirll]_[description],description可以是下述描述: GEN:普通过孔;命名规则:via*_bga 其中*代表过孔直径 Via05_BGA:0.5mm BGA的专用过孔; Via08_BGA:0.8mm BGA的专用过孔; Via10_BGA:1.0mm BGA的专用过孔; Via127_BGA:1.27 mm BGA的专用过孔;

元器件库设计规范

元器件库设计规范 受控印章位 注:本文件归本公司所有,未经批准任何人不得翻录 复制,纸介文件以盖红色“受控”印章为有效文件。 适用部门 □信息部□综合管理部□测试部■ID/MD设计部■研发部 □产品管理部□技术销售部□市场部□国内销售部□海外销售部□销售管理部□采购部□售后服务部□计划管理部□质量管理部□品质部□仓储物流部□人事行政部□生产技术部□生产部 □财务部□人力资源部□后勤保障部□□ □□□□□

1.目的 编写本文档的目的是为了元器件库的规范和统一。 2.适用范围 本标准规定了印制电路板(以下简称PCB)设计中所使用的焊盘、元器件封装库的命名、丝印、图形坐标原点等基本要求。 3.职责 EDA零件工程师负责元器件库的建立和维护。 4.名词解释 S:Surface Mount Devices/表面贴装元件 D: DIP/插件元件 SOT:Small outline transistor/小外形晶体管 SOD:Small outline diode/小外形二极管 SN:Resistor Arrays/排阻 SOP: Small Outline Package Integrated Circuits/小外形封装集成电路 SSOP: Shrink Small Outline Package Integrated Circuits/缩小外形封装集成电路TSOP: Thin Small Outline Package/薄小外形封装 TSSOP: Thin Shrink Small Outline Package/薄缩小外形封装 PQFP:Plastic Quad Flat Pack/塑料方形扁平封装 PLCC:Plastic leaded chip carriers/塑料封装有引线芯片载体 PBGA:Plastic Ball Grid Array /塑封球栅阵列器件 L:Inductance/电感 SW:Switch/开关 RJ45:RJ45/网口 SFP:fiber/光口 USB:usb接口 TF:transformer/变压器

元器件封装库设计规范

元器件封装库设计规范编号:TSH_HW_002_FootPrint_DESIGN

1 概述 ! 闪龙公司《元器件封装库设计规范》(以下简称《规范》)为电路元器件PCB封装库设计规范文档。本文档规定元器件封装库设计中需要注意的一些事项,目的是使设计规范化,并通过将经验固化为规范的方式,避免设计过程中错误的发生,最终提高产品质量。 本文中的所有信息归闪龙公司所有,未经允许,不得外传。 2 相关说明 本规范作为电路设计中的指导文档,并会由其中抽取相应要点形成“元器件封装检查规范”。 3 设计规范 通用规范 单位尺寸使用mil(千分之一英寸)和mm(毫米)两种,以取整为使用前提。比如:常用的100mil间距插座(2.54mm),50mil间距芯片引脚;一些特殊的2mm间距插座,1mm间距芯片引脚,0.8mm 间距BGA焊球。 因为单位换算有精度损失,在设计中不要随意切换单位! : 焊盘设计相关要求 焊盘的命名方法参见表1 注:PAD单位为mil。

】 焊盘类型 简称标准图示命名 表面贴装 矩形焊盘 SMD SMD + 宽(Y) x 长(X) 命名举例:SMD21X20,SMD32X30。 表面贴装圆焊盘SMDC SMDC + 焊盘直径(C) 命名举例:SMDC40 表面贴装手指焊盘SMDF SMDF + 宽(Y) x 长 (X) 命名举例:SMDF57X10 通孔圆焊 盘 THC THC + 焊盘外径(C)+ D +孔径(D) 命名举例:THC25D10 注:非金属化孔按通孔圆焊盘标注,焊 盘外径标为0。 通孔矩形焊盘THR( THR + 宽(Y) x 长(X)+ D + 孔 径 命名举例:THR80X37D37。

PCB封装设计规范V

P C B封装设计规范V Document serial number【NL89WT-NY98YT-NC8CB-NNUUT-NUT108】

PCB封装设计规范 文件编号: 受控标识: 版本状态: 发放序号: 编制:日期:审核:日期:批准:日期:

目录

1、目的 本规范是为电子元器件的表面属性提供模版信息,即为表面器件焊盘图形设计提供模版尺寸,外形以及公差,以便检查和测试,确保表面装配产品的可靠性,从而规范电子元器件的PCB 封装设计 2、适用范围 本规范适用于研发中心PCB部所有PCB封装的设计。 3、职责 PCB封装库评审由PCB部门经理与工艺部门经理共同评审完成,特殊封装除外。 PCB部门专职PCB封装设计人员负责PCB封装库的设计、评审和更新。 4、术语定义 PCB(Print circuit Board):印刷电路板 Footprint:封装 IC(integrated circuits):集成电路 SMC(Surface Mounted Components):表面组装元件 SMD(Surface Mounted Devices):表面组装器件 5、引用标准 下列标准包含的条文,通过在本规范中引用而构成本规范的条文。在规范归档时,所示版本均为有效。所有规范都会被修订,使用本规范的各方应探讨,使用下列标准最新版本的可能性。 IPC Batch Footprint Generator Reference IPC-7351 Generic Requirements for Surface Mount Design and Land Pattern Standard IPC-SM-782A Surface Mount Design and Land Pattern Standard 《表面组装技术基础与可制造性设计》 6、PCB封装设计过程框图

pcb封装设计规范v1.0

PCB封装设计规范 文件编号: 受控标识: 版本状态: 发放序号: 编制:日期:审核:日期:批准:日期:

1、目的 ...................................................................................................................... 错误!未定义书签。 2、适用范围................................................................................................................. 错误!未定义书签。 3、职责 ...................................................................................................................... 错误!未定义书签。 4、术语定义................................................................................................................. 错误!未定义书签。 5、引用标准................................................................................................................. 错误!未定义书签。 6、PCB封装设计过程框图 ......................................................................................... 错误!未定义书签。 7、SMC(表面组装元件)封装及命名简介 ............................................................. 错误!未定义书签。 8、SMD(表面组装器件)封装及命名简介 ............................................................. 错误!未定义书签。 9、设计规则................................................................................................................. 错误!未定义书签。 10、PCB封装设计命名方式 ....................................................................................... 错误!未定义书签。 11、PCB封装放置入库方式 ....................................................................................... 错误!未定义书签。 12、封装设计分类....................................................................................................... 错误!未定义书签。 、矩形元件(标准类)........................................................................................ 错误!未定义书签。 、圆形元件(标准类)........................................................................................ 错误!未定义书签。 、小外形晶体管(SOT)及二极管(SOD)(标准类)..................................... 错误!未定义书签。 、集成电路(IC)(标准类)............................................................................... 错误!未定义书签。 、微波器件(非标准类).................................................................................... 错误!未定义书签。 、接插件(非标准类)........................................................................................ 错误!未定义书签。 1、目的 本规范是为电子元器件的表面属性提供模版信息,即为表面器件焊盘图形设计提供模版尺寸,外形以及公差,

QFN封装芯片手工焊接方法

QF N封装芯片手工焊接方法 QFN四侧无引脚扁平封装,是一种相对比较新的IC 封装形式,QFN 外观呈正方形或矩形,大小接近于CSP,很薄很轻。元件底部具有与底面水平的焊端,在中央有一个大面积裸露焊端用来导热,围绕大面积裸露焊端的外围四周有实现电气连接的I/O 焊端,I/O 焊端有两种类型:一种只裸露出元件底部的一面,其它部分被封装在元件内;另一种焊端有裸露在元件侧面的部分。由于其尺寸小、体积小,电气性能优越,在我所得到了越来越广泛的应用。由于本人长期从事高密度印制板的组装及返修工作,对于QFN芯片的手工焊接及返修有一点实践经验,现与感兴趣的朋友分享一下。 一、焊接前准备 1、电烙铁 一般的QFN芯片都是静电敏感器件,对静电防护要求特别高,所以建议焊接前最好先对烙铁进行防静电测试,确认其符合静电防护要求。 2、加热台 我们经常用的是PACE的加热台,当然也要先确认其已经良好接地并且符合静电防护要求。 3、静电手腕 焊接前也需要用三用表确认其状态正常,并且良好接地。 4、其它常用工具 镊子、松香笔(或自制松香水)、放大镜 二、焊接步骤

1、打开电烙铁及加热台 以我常用的PACE烙铁为例,对焊端搪锡时,我一般把温度设置为260度左右,加热台视PCB材料及厚度选择合适的温度,一般为215度左右。 2、器件引脚与PCB焊盘搪锡 这一步非常重要,锡上的好不好直接关系到焊接的质量。上锡时,先要在QFN芯片的I/0焊端涂上一层助焊剂,然后将烙铁头擦拭干净,在烙铁头上沾少量锡(注意烙铁头上的锡一定不能太多,不然不同引脚间容易桥连),轻轻的沿着引脚排列方向拖一遍,这样在每一个引脚上就会形成一个漂亮的中间高四边略低的“枕形”焊点,然后对中央大面积裸露焊端搪锡,注意这里的锡不要搪的太多,不然容易因为中间锡的高度太高,使得I/O焊端焊不上,要尽量使得中央大面积裸露焊端与I/O焊端的搪锡高度大致一样。到这里对于那种只裸露出元件底部的一面,其它部分被封装在元件内的QFN 芯片来说,预加工已经完成,而对于另一种焊端有裸露在元件侧面的QFN 芯片来说还没有结束。还需要对裸露在元件侧面的引脚端面进行处理,要像给引脚搪锡一样对引脚端面进行处理,使其端面也搪上一层锡。然后用沾了酒精的擦拭纸对搪好锡的芯片进行清洗。 PCB焊盘搪锡和清洗与器件预加工方法相同。 3、器件对中 将清洗干净的芯片与PCB先各涂上一层助焊剂,然后再将芯片按资料所示方向放置在PCB上,调整芯片位置使两者精确对中。 4、焊接 用镊子轻轻的夹住己精确对中好芯片的PCB,放在温度已经升至设定温度的加热台上,用镊子轻轻的压住PCB,使其与加热台良好接触,然后注意

PCB封装设计规范 V0

PCB封装设计规范 文件编号: 受控标识: 版本状态: 发放序号: 编制:日期: 审核:日期: 批准:日期: 目录 1、目得....................................................................................................................... 错误!未定义书签。 2、适用范围................................................................................................................. 错误!未定义书签。 3、职责?错误!未定义书签。 4、术语定义?错误!未定义书签。 5、引用标准?错误!未定义书签。 6、PCB封装设计过程框图........................................................................................ 错误!未定义书签。 7、SMC(表面组装元件)封装及命名简介................................................................ 错误!未定义书签。 8、SMD(表面组装器件)封装及命名简介 ........................................................ 错误!未定义书签。 9、设计规则?错误!未定义书签。 10、PCB封装设计命名方式?错误!未定义书签。 11、PCB封装放置入库方式 .................................................................................. 错误!未定义书签。 12、封装设计分类?错误!未定义书签。 12、1、矩形元件(标准类)?错误!未定义书签。 12、2、圆形元件(标准类).............................................................................. 错误!未定义书签。 12、3、小外形晶体管(SOT)及二极管(SOD)(标准类)?错误!未定义书签。 12、4、集成电路(IC)(标准类)?错误!未定义书签。 12、5、微波器件(非标准类) .......................................................................... 错误!未定义书签。 12、6、接插件(非标准类)?错误!未定义书签。 1、目得 本规范就是为电子元器件得表面属性提供模版信息,即为表面器件焊盘图形设计提供模版尺寸,外形以及公

QFN封装IC 的管控资料

QFN封装 目录 概况 特点 周边引脚的焊盘设计 散热焊盘和散热过孔设计 阻焊层的考虑 1.网板设计 2.QFN焊点的检测与返修 概况 四侧无引脚扁平封装,表面贴装型封装之一。现在多称为LCC。QFN 是日本电子机械工业会规定的名称。封装四侧配置有电极触点,由于无引脚,贴装占有面积比QFP 小,高度比QFP 低。但是,当印刷基板与封装之间产生应力时,在电极接触处就不能得到缓解。因此电极触点难于作到QFP 的引脚那样多,一般从14 到100 左右。材料有陶瓷和塑料两种。当有LCC 标记时基本上都是陶瓷QFN。电极触点中心距 1.27mm。塑料QFN 是以玻璃环氧树脂印刷基板基材的一种低成本封装。电极触点中心距除1.27mm 外,还有0.65mm 和0.5mm 两种。这种封装也称为塑料LCC、PCLC、P-LCC 等。 特点 QFN是一种无引脚封装,呈正方形或矩形,封装底部中央位置有一个大面积裸露焊盘用来导热,围绕大焊盘的封装外围四周有实现电气连结的导电焊盘。由于QFN 封装不像传统的SOIC与TSOP封装那样具有鸥翼状引线,内部引脚与焊盘之间的导电

路径短,自感系数以及封装体内布线电阻很低,所以它能提供卓越的电性能。此外,它还通过外露的引线框架焊盘提供了出色的散热性能,该焊盘具有直接散热通道,用于释放封装内的热量。通常将散热焊盘直接焊接在电路板上,并且PCB中的散热过孔有助于将多余的功耗扩散到铜接地板中,从而吸收多余的热量。 图1显示了这种采用PCB焊接的外露散热焊盘的QFN封装。由于体积小、重量轻、加上杰出的电性能和热性能,这种封装特别适合任何一个对尺寸、重量和性能都有的要求的应用。我们以32引脚QFN与传统的28引脚PLCC封装相比较为例,面积(5mm×5mm)缩小了84%,厚度(0.9mm)降低了80%,重量(0.06g)减轻了95%,电子封装寄生效应也提升了50%,所以非常适合应用在手机、数码相机、PDA以及其他便携小型电子设备的高密度印刷电路板上。 图1 采用PCB焊接外露散热焊盘的QFN封装 标准或遵循工艺标准(如IPC-SM-782)来进行的。由于QFN是一个全新的封装类型,印制板焊盘设计的工业标准或指导书还没有制定出来,况且,焊盘设计完成后,还需要通过一些试验来验证。当然,在充分考虑元件底部的散热焊盘以及引脚和封装的公差等各种其他因素的情况下,仍然可以参考IPC的方法来制定设计原则。 QFN的焊盘设计主要有三个方面:①周边引脚的焊盘设计;②中间热焊盘及过孔的设计;③对PCB阻焊层结构的考虑。 周边引脚的焊盘设计 尽管在HECB设计中,引脚被拉回,对于这种封装,PCB的焊盘可采用与全引脚封装一样的设计,周边引脚的焊盘设计尺寸如图3。在图中,尺寸Zmax为焊盘引脚外侧最大尺寸,Gmin是焊盘引脚内侧最小尺寸。D2t为散热焊盘尺寸。X、Y是焊盘的宽度和长度。 图3 PCB焊盘设计尺寸

军工优质PCB工艺设计规范

军品PCB工艺设计规范 1. 目的 规范军品的PCB工艺设计,规定PCB工艺设计的相关参数,使得PCB的设计满足可生产性、可测试性、安规、EMC、EMI等的技术规范要求,在产品设计过程中构建产品的工艺、技术、质量、成本优势。 2. 适用范围 本规范适用于所有军品的PCB工艺设计,运用于但不限于PCB 的设计、PCB投板工艺审查、单板工艺审查等活动。本规范之前的相关标准、规范的内容如与本规范的规定相抵触的,以本规范为准。 3. 定义 导通孔(via):一种用于内层连接的金属化孔,但其中并不用于插入元件引线或其它增强材料。 盲孔(Blind via):从印制板内仅延展到一个表层的导通孔。 埋孔(Buried via):未延伸到印制板表面的一种导通孔。 过孔(Through via):从印制板的一个表层延展到另一个表层的导通孔。 元件孔(Component hole):用于元件端子固定于印制板及导电图形电气联接的孔。 孔化孔(Plated through Hole):经过金属化处理的孔,能导电。 非孔化孔(Nu-Plated through Hole):没有金属化理,不能导电,通常为装配孔。 装配孔:用于装配器件,或固定印制板的孔。 定位孔:指放置在板边缘上的用于电路板生产的非孔化孔。 光学定位点:为了满足电路板自动化生产需要,而在板上放置的用于元件贴装和板测试定位的特殊焊盘。 Stand off:表面贴器件的本体底部到引脚底部的垂直距离。 回流焊(Reflow Soldering):一种焊接工艺,既熔化已放在焊点上

的焊料,形成焊点。主要用于表面贴装元件的焊接。 波峰焊(Wave Solder):一种能焊接大量焊点的工艺,即在熔化焊料形成的波峰上,通过印制板,形成焊点。主要用于插脚元件的焊接。 PBA(Printed Board Assembly):指装配元器件后的电路板。 4. 引用/参考标准或资料 5. 规范内容 5.1 PCB板材要求 5.1.1确定 PCB使用板材以及 TG值 确定PCB所选用的板材,例如FR—4、铝基板、陶瓷基板、纸芯板等,若选用高TG值的板材,应在文件中注明厚度公差。 5.1.2确定 PCB的表面处理镀层 确定PCB铜箔的表面处理镀层,例如镀锡、镀镍金或OSP等,并在文件中注明。 5.2热设计要求 5.2.1 高热器件应考虑放于出风口或利于对流的位置 PCB 在布局中考虑将高热器件放于出风口或利于对流的位置。 5.2.2 较高的元件应考虑放于出风口,且不阻挡风路 5.2.3 散热器的放置应考虑利于对流 5.2.4 温度敏感器械件应考虑远离热源 对于自身温升高于30℃的热源,一般要求: a.在风冷条件下,电解电容等温度敏感器件离热源距离要求大于或等于2.5mm;

大公司PCB设计规范

XXXXXXX 电器股份有限公司 电子分公司 文件:印制PCB板工艺设计规范 版本: B 制定: 校核: 审核: 审批: 日期: 2008-1-30 1、目的 规范我司产品的PCB工艺设计,规定PCB设计的相关工艺参数,使得PCB的设计满足可生产性、可测试性、安规、EMC、EMI等的技术规范要求,在产品的设计过程中构建产品的工艺、技术、质量、成本的优势。

2、适用范围 适用于本司所有的PCB工艺设计,运用于但不限于PCB的工艺设计、PCB投板工艺审查,单板工艺审查等活动。 考虑到我司的实际情况,本设计规范的内容重点放在了低频、插件工艺的单面PCB上,对于高频、双面(包括多层)、SMT工艺的PCB方面的内容没有做具体的要求,以后随着发展的需要再考虑增加。3.职责 客户:负责 PCB板外形尺寸、主要元件的安装等要求的提供; 技术单位:负责PCB板的设计及样板确认; 品管单位:负责PCB板的试验和来料检验; 3、定义 1、电气间隙:两相邻导体或一个导体与相邻电机壳表面的沿空气测量的最短距离。 2、爬电距离:两相邻导体或一个导体与相邻电机壳表面的沿绝绝缘表面测量的最短距离 4、引用/参考标准或资料 1、《电子分公司标准元件库》 2、IEC60194 《印制板设计、制造与组装术语与定义》 3、TS—S0902010001 《信息技术设备PCB安规设计规范》 5、规范内容 5.1 PCB板材要求: 5.1.1确定PCB使用板材 5.1.1.1 根据设计的产品的实际需要,确定使用PCB板的板材,例如:KB-3151、KB-3150、ZD-90F、 FR-4等; 5.1.1.2 优先采用单面板,除非设计必须或客户要求尽量不采用双面板; 5.1.1.3 对于所选择的板材的阻燃等级要求:除非特别规定,否则本司所有设计的PCB板的板材的 阻燃等级全部按94-V0级标准执行; 5.1.2确定PCB板的表面处理工艺 根据设计产品的需要,确定PCB板铜箔表面的处理工艺,例如:光铜板、镀锡、镀镍、镀金等,应在打样及评估时注明; 5.1.2.1 对于PCB设计过程中涉及带金手指的产品,统一采用镀金工艺; 5.1.2.2 对于PCB设计过程中涉及IC邦定的产品(一般不推荐),优先采用镀金工艺; 5.2 热设计要求: 5.2.1 高热器件应考虑放在出风口或利于对流的位置 PCB在布局中应考虑将高热器件放在整机出风口或利于对流的位置。 5.2.2 较高的元件应考虑放于出风口,且不阻挡风路; 5.2.3 散热器的放置应考虑利于对流 5.2.4 温度敏感器件应考虑远离热源 对于自身温升高于30K的热源,一般要求: 在风冷条件下,电解电容等温度敏感元件离热源距离要求≥2.5mm; 在自然冷条件下,电解电容等温度敏感元件离热源距离要求≥4mm; 若因为空间的原因不能达到要求的距离,则应通过温度测试保证温度敏感元件的温升在将额 范围内。 5.2.5 大面积铜箔要求用隔热带与焊盘相连 为了保证透锡良好,在大面积铜箔上的元件的焊盘要求用隔热带与焊盘相连,对于需通过5A以上大电流的焊盘不能采用隔热焊盘,如图2-1所示: