An+overview+of+MWT+cells+and+evolution+to+the+ASPIRE+concept

当表面活性剂遇到大环分子

114Univ. Chem. 2023, 38 (12), 114–119收稿:2023-06-27;录用:2023-08-01;网络发表:2023-08-11*通讯作者,Email:*****************.cn基金资助:2021年基础学科拔尖学生培养计划2.0研究课题(20211014);天津市首批虚拟教研室试点建设项目(化学类交叉人才培养课程建设虚拟教研室)•专题• doi: 10.3866/PKU.DXHX202306051 当表面活性剂遇到大环分子阮文娟,李悦,耿文超,郭东升*南开大学化学学院,天津 300071摘要:近年来,表面和胶体化学与大环化学的结合引起了科学家的普遍关注。

将多样的大环结构引入表面活性剂分子,不仅极大地丰富了表面活性剂分子的种类,还可以赋予其大环的主客体识别功能。

由此所开发出的大环两亲和超两亲分子已在生物成像和药物递送中表现出很高的应用潜力。

从传统表面活性剂到大环两亲和超两亲分子的发展、应用表明,不同领域的交叉融合对科学研究的发展是非常重要的。

关键词:表面活性剂;胶束;大环结构;大环两亲分子;超两亲分子中图分类号:G64;O6Encountering of Surfactants with Macrocyclic MoleculesWen-Juan Ruan, Yue Li, Wen-Chao Geng, Dong-Sheng Guo *College of Chemistry, Nankai University, Tianjin 300071, China.Abstract: In recent years, the combination of surface and colloid chemistry with macrocyclic chemistry has garnered widespread attention among scientists. The integration of diverse macrocyclic structures into surfactant molecules not only greatly enriches the diversity of surfactants, but also imparts them with the host-guest recognition functionality of macrocycles. Macrocyclic amphiphiles and supra-amphiphiles, developed from this approach, have demonstrated high potential in applications such as bioimaging and drug delivery. The evolution from traditional surfactants to macrocyclic amphiphiles and supra-amphiphiles underscores the importance of interdisciplinary integration in advancing scientific research.Key Words: Surfactants; Micelles; Macrocycles; Macrocyclic amphiphiles; Supra-amphiphiles表面活性剂及其所构筑的胶束是表面和胶体化学中所涉及的一类非常重要的体系。

2018年生命科学导论03-细胞-文档资料

细胞生命活动:

•以物质代谢为基础; •以能量代谢(ATP)为 动力; •以信息调控为机制。

细胞是生殖和遗传的基础和桥梁,具有相同的遗 传语言

人与人之间的基因组差别只有千分之一

惟 妙 惟 肖 的 表 型 特 征

的

2 独立完整的蛋白质合成系 进

统,而且类似原核;

化

3 线粒体能以分裂发生繁殖 以及内外膜组成和结构差异

大;

步 骤 模 型

4 叶绿体可在异体细胞中生

存。

现代分子生物学的研究

16SrRNA测序,建立系统树,显示真核细胞与原核 细胞(包括古菌)是由共同的祖先平行进化而来。

真核细胞的性质

具有真正的细胞核,其遗传物质DNA包被在双层膜 的特殊结构中; 具有许多由膜包被的各式细胞器,即线粒体、叶 绿体、高尔基体和内质网等; 植物及真菌具有细胞壁,其成分分别是纤维素和 几丁质; DNA结构非常复杂,其中含有许多非编码区,而且 存在多种调控机制; 具有由特异的结构蛋白装配而成的细胞骨架 和细 胞质基质系统;

3.2 细胞的基本概念

从形态学的角度定义细胞:

细胞是由膜包围的 原生质团,通过质 膜与周围环境进行 物质和信息交流。

被质膜包裹在细胞 内的所有生活物质称为 原生质(protoplasm), 包括细胞核和细 胞 质 (cell plasma)。

细胞具有不同的形态和大小。

多种多样,细胞形态和大小的 差异,一般与其所执行的生理功 能以及所处的环境条件有关。

• 在多细胞生物中,具有不同形态和功能的 细胞都是由一个受精卵分裂和分化而来的。

所以,研究生物的生长发育必须以研究 细胞的增值、生长与分化为基础。

固定化菌藻微生物燃料电池

固定化菌藻微生物燃料电池英文回答:Microbial Fuel Cells with Immobilized Microalgae.Microalgae-based microbial fuel cells (MFCs) have gained considerable attention in recent years due to their potential for simultaneous wastewater treatment and bioelectricity generation. The integration of microalgae into MFCs offers several advantages, including enhanced substrate utilization, biomass recovery, and nutrient recycling. The immobilization of microalgae within the MFC system is a crucial aspect that influences the performance and stability of the device.Immobilization techniques aim to physically confine microalgae cells within the MFC, thereby preventing their washout from the system. This allows for extended contact between the microalgae and the anode, facilitatingefficient substrate utilization and electron transfer.Various immobilization methods have been employed in microalgae-based MFCs, each with its own advantages and disadvantages.One common approach involves the use of biofilms. Biofilms are naturally occurring communities of microorganisms that adhere to surfaces. Microalgae can be encouraged to form biofilms on the anode surface, creating a stable and electrochemically active layer. Biofilm formation enhances the adhesion of microalgae cells, promotes electron transfer, and protects the cells from shear forces and other environmental stresses.Another immobilization method utilizes microcarrier beads. These small, inert particles provide a solid support for microalgae growth. Microalgae cells are attached to the beads, which are then suspended in the MFC. The use of microcarrier beads allows for easy handling and scalability of the MFC system. Additionally, the beads can provide structural support for microalgae growth, improving their viability and performance.Other immobilization techniques include the use of hydrogels, scaffolds, and nanomaterials. Hydrogels are three-dimensional networks of hydrophilic polymers that can encapsulate microalgae cells. They provide a protective environment for the cells while allowing the exchange of nutrients and waste products. Scaffolds are typically porous structures that support microalgae growth and facilitate electron transfer. Nanomaterials, such as carbon nanotubes and graphene oxide, offer high surface areas for microalgae attachment and can enhance the electrical conductivity of the MFC system.The choice of immobilization method depends on factors such as the type of microalgae used, the desired MFC performance, and the scalability of the system. Effective immobilization techniques contribute to the stability, efficiency, and long-term viability of microalgae-based MFCs.中文回答:固定化菌藻微生物燃料电池。

NBTI degradation From physical mechanisms to modelling

Introductory Invited PaperNBTI degradation:From physical mechanisms to modellingV.Huarda,*,M.Denaisb,c,C.ParthasarathybaPhilips R&D Crolles,850rue Jean Monnet,38926Crolles,FrancebSTMicroelectronics,Central R&D Labs,850rue Jean Monnet,38926Crolles,France cLaboratoire Mate´riaux et Microe ´lectronique de Provence (L2MP –UMR CNRS 6137)–ISEM,Maison des Technologies,Place Georges Pompidou,83000Toulon,FranceReceived 18January 2005Available online 26April 2005AbstractAn overview of the evolution of transistor parameters under negative bias temperature instability stress conditions commonly observed in p-MOSFETs in recent technologies is presented.The physical mechanisms of the degradation as well as the different defects involved have been discussed according to a systematic set of experiments with different stress conditions.According to our findings,a physical model is proposed which could be used to more accurately pre-dict the transistor degradation.Finally,based on our new present understanding,a new characterization methodology is proposed,which would open the way to a more accurate determination of parameter shifts and thus allowing imple-menting the degradation into design rules.Ó2005Elsevier Ltd.All rights reserved.1.IntroductionBias temperature instability (BTI)is a degradation phenomenon occurring mainly in MOS Field Effect Transistors (MOSFETs),known since the late 1960s [1,2].Even though the exact root causes of the degrada-tion are not yet well understood,it is now commonly admitted that under a constant gate voltage and an ele-vated temperature a build up of positive charges occurs either at the interface Si/SiO 2or in the oxide layer lead-ing to the reduction of MOSFET performances.Never-theless,this degradation remained marginal for many years,especially when compared to hot carrier injection(HCI)degradation,thanks to the exclusive use of buried channel devices at this time.As a result of aggressive scaling of MOS transistors,the thickness of the gate oxide layer was decreased down to 1.4nm or even lower.In order to improve the transis-tors performances,nitrogen atoms were introduced into the oxide layer by different nitridation processes,but mostly by thermal annealing.This nitridation step is in-tended both to give a better control on the gate leakage current and to avoid the boron atoms,used to dope the polysilicon gate,to flow through the oxide into the sub-strate.Besides,the general trend was that most of the de-vices turned out to be surface-channel devices instead of buried-channel ones in recent technologies to counter the short-channel effects inherent of the downscaling process and to improve the performances.As a conse-quence of both the introduction of the nitridation pro-cess step and the use of surface-channel devices,many0026-2714/$-see front matter Ó2005Elsevier Ltd.All rights reserved.doi:10.1016/j.microrel.2005.02.001*Corresponding author.E-mail address:vincent.huard@ (V.Huard).Microelectronics Reliability 46(2006)1–23researchers ascribed an enhanced BTI-like degradation of p-MOSFETs under negative bias and elevated tem-peratures,the so-called NBTI effect[3–5].This work aims to investigate the evolution of tran-sistor parameters under NBTI stress conditions,leading to a general definition of the Negative Bias Temperature Instability in p-MOSFETs in recent technologies.Sys-tematic sets of experiments have been performed with different stress conditions to identify the physical mech-anisms lying behind the degradation.According to our findings,the interface traps creation is not the sole source of degradation but a major hole trapping effect also occurs.This trapping behaviour is at the origin of a strong recovery effect which makes an accurate mea-surement of the degradation difficult.We propose a new characterisation methodology which gives a more accurate view of the actual degradation.2.Device fabrication and experimental detailsThe devices used in this study were n-and p-MOS-FETs with dual gate process,i.e.n+and p+polysilicongate,respectively,with pure or nitrided(NO)gate oxide layers.Source and drain junctions were formed with ar-senic/phosphorous ion implantations for n-MOSFET and a boron-based implantation for p-MOSFET.Exper-iments were carried out on MOSFETs with oxide thick-ness ranging from 1.6nm to10nm.The MOSFETs have gate lengths ranging from0.1l m to10l m and typ-ically a width of10l m.NBTI stress was applied with the gate electrode held at a low constant negative bias(rang-ing fromÀ0.75V toÀ3.5V)under a temperature ranging from25°C to200°C while the source/drain and n-well electrodes were grounded.In order to characterize the NBTI effect,we primarily used a conventional methodol-ogy based on periodic stops during the stress to measure MOS parameters and/or the two-level charge pumping (CP)current as a measure of the interface traps density. The CP curves are measured with a frequency of105Hz and low gate bias V gl ranging fromÀ0.7V to0.3V and a voltage swing from1V to1.5V.A new characterization methodology will be introduced later in the paper,as it is based on recentfindings.Most of the experiments were carried out at125°C unless it is mentioned differently.2.1.Bias temperature instabilities2.1.1.Degradation of electrical parametersBy definition,bias temperature instabilities are ob-served when either a capacitor or a transistor is stressed at relatively high temperatures(typically ranging from 80°C to150°C)under a low and constant gate voltage while the source/drain and well electrodes are grounded. The symmetry of stress conditions along the channel proves that this degradation is not related to channel carrier transport.Fig.1shows the typical evolution of I dÀV g curves in linear regime for a p-MOSFET once degraded under NBTI stress conditions for10,000s. Generally,it is observed that after an NBTI stress,the saturated drain current value(I dsat)is reduced.The for-ward and reverse values of the saturated drain current both degrade identically,demonstrating the symmetry of the stress.By the same time,the threshold voltage (V th)is increased as well as the S/D series resistance.Fi-nally,the mobility,as described through the g mÀV g curve is also reduced(cf.Fig.1).Altogether,the degra-dation of these parameters demonstrates the build-up of positive charges close or at the interface of Si/SiO2and yields to a lower level of performance for the transistor. For short stress times,the off-leakage current is decreas-ing due to the shift of the I dÀV g curves linked to the threshold voltage shift.Nevertheless,in some cases,an increase of the GIDL observed at lowfields may over-come this decrease and limit the performances of the cir-cuit by an increased consumption.The instabilities exist in most of the configurations, for either p-MOSFETs or n-MOSFETs,and whatever a negative bias and/or a positive bias is applied,except for the n-MOSFET under positive bias,which does ex-hibit almost no degradation.Nevertheless,as shown in Fig.2,applying NBTI stress conditions(i.e.negative gate voltage)on p-MOSFETs represents the most degrading case.That is why the rest of this paper will mainly focus on the mechanisms of p-MOSFET degra-dation under NBTI conditions,but all the conclusions would also apply to the other configurations.2V.Huard et al./Microelectronics Reliability46(2006)1–232.2.Interface traps creation under NBTI stress conditionsSo far,the microscopic details of the NBTI degrada-tion are not clearly understood but there is a general agreement to say that there is generation of traps at the Si–SiO2interface during negative BT aging.2.3.Nature of interface trapsDue to the lattice mismatch between the bulk silicon and the silicon dioxide and considering the amorphous nature of the dielectrics,some Si atoms at the interface are left unbound when the great majority is bound to oxygen atoms(or nitrogen atoms for the case of nitrided oxides).This trivalent Si atom at the Si/SiO2interface has an unpaired valence electron in a dangling orbital (dangling bond),and is often called Pb centers[6].On (100)-oriented wafers,commonly used for ICs,two de-fects named Pb0and Pb1have been detected by electron spin resonance(ESR)methods,and showed to result from strain relaxation at the interface.These two types of defects have slightly different local atomic configura-tions and so are expected to have slightly different elec-trical behaviours.In both cases,these defects have an amphoteric nature.This means that the dangling orbital can be occupied by zero,one or two electrons,which would make the same defect positively charged(donor-like),neutral or negatively charged(acceptor-like), depending on the Fermi level at the interface[7,8].Dur-ing the consecutive process steps,these dangling bonds are generally annealed by hydrogen atoms,which create SiH bonds at the interface.Though considerably improving the initial parameters of the transistor,these bonds might be broken during the operating lifetime of the device,which in turn will lead to a degradation of its parameters.2.4.Role of charge transportIn most of wearout mechanisms,such as hot-carrier injection,oxide breakdown or electromigration,experi-ments pointed out that the charge transport activated directly or indirectly the degradation.Naturally, whether or not the charge transport is related to the NBTI degradation is a question,which has to be an-swered.It should be pointed out that the symmetrical nature of the stress with no drain-to-source potential drop implies that there is no charge transport along the channel.The only remaining displacement of chan-nel carriers is based on their thermal activity.Concern-ing the role of carriersflowing through the oxide layer by either direct tunnelling and/or Fowler–Nordheim mechanism,it is interesting to compare both ultra-thin oxides(about2nm-thick)and thicker oxides(about 6.5nm-thick)degradations.In the latter case,the NBTI degradation can be important for these oxides when stressed with a low oxidefield below the detection limit of Fowler–Nordheim current(cf.Fig.3).In that case, the tunnelling probability of carriers through the oxide layer is close to zero which is not the case for thinner oxides under similar oxidefield.Nevertheless,the NBTI degradation monitored in this case is rather similar in spite of the different conduction probabilities through the oxide layer.In agreement with many researchers, we have to conclude that the NBTI degradation isV.Huard et al./Microelectronics Reliability46(2006)1–233closely related to the presence of‘‘cold channel holes’’. This assumption is also supported by the small level of degradation for an n-MOSFET under PBTI conditions (cf.Fig.2),where only negligible hole densities can be found on both sides of the oxide layer.Nevertheless, the exact mechanism of degradation involving cold holes remains unknown at this point.2.5.Influence of channel hole populationIf the channel cold holes are responsible for the NBTI degradation,thefirst thing to check out is the ef-fect of varying the hole population by keeping the other stress conditions constant.This configuration can be ob-tained experimentally by two different ways.Thefirst one is to increase the initial threshold voltage V th0by adding an additional implant.For a similar gate voltage value V g,the oxidefield value would be similar(due to the channel potential grounded to zero)but the channel hole population(proportional to V gÀV th)would de-crease when the threshold voltage is increased.Another way is to change the initial threshold voltage value V th0 by applying a positive bulk bias.In this case,for an increasing positive bulk bias,the threshold voltage value is increased and so that the channel hole population is decreased.Fig.4shows that though V gÀV th is varying by about10%,no changes can be observed in the inter-face traps creation dynamics.In the latter case,some precautions are taken in order to avoid additional degra-dation due to hot holes injection resulting from impact ionisation phenomenon induced by electronsflowing through the oxide layer.Basically,for gate voltage up to2.5V,hot electrons coming from the gate demon-strated no impact on electrical parameters.Under hot carrier stress configuration,degradation rates have been found similar whatever the presence of electronsflowing through the gate.Fig.4shows that,over a relatively large range of channel hole population(large gate volt-ages range for varying bulk voltages),the electrical parameters shifts are similar and not impacted by vary-ing the hole population(i.e.the bulk voltage).As a con-clusion,if the channel holes are responsible for the observed degradation,their population is not a limiting factor.Ourfindings are in agreement with conclusionsof Mitani et al.[9].2.6.Gate voltage or oxidefield dependenceSymmetrically,for different bulk biases,the gate volt-age V g is changed in a way to keep V gÀV th constant and so that the channel hole population is made similar. In this case,only the oxidefield is modified.When the oxidefield is increased,the electrical parameters show a clear increase of their degradation(cf.Fig.5).These results demonstrate the importance of the oxidefield and/or the gate voltage in the degradation.The question of whether the oxidefield or the gate voltage is the driving factor of the degradation remains. Typically,gate voltage dependence is linked to a carrier-energy driven degradation similarly to the case of the gate oxide breakdown and the Channel Hot Carrier (CHC)-induced degradation[10,11].But,as discussed in Fig.3,NBTI degradation occurs also for thick oxides for oxidefields where the gate leakage current is below the detection limit.Therefore,it is difficult to assign the NBTI degradation to energetic carriersflowing through the oxide,either holes or electrons,such as pro-posed in[12].In order to investigate the oxidefield4V.Huard et al./Microelectronics Reliability46(2006)1–23dependence,the interface traps creation under NBTI degradation is investigated for different gate oxide thick-nesses,ranging from2.1nm to10nm-thick,considering both pure oxides and nitrided oxides with various nitrid-ation processes.Fig.6a shows that for pure oxides stressed with a similar gate voltage the interface traps creation is reduced when the oxide thickness is in-creased.Summarizing a set of pure oxides with four dif-ferent thicknesses stressed with various gate voltages for three different stress times,Fig.6b shows that for a given stress time the number of interface traps created are identical for similar oxidefields.These results clearly demonstrate that the oxidefield is the driving force of the interface traps creation during NBTI degradation for pure oxides[13,14].It is questionable if the incorporation of nitrogen atoms into the oxide network will modify this oxide-field dependence.As already discussed previously in the introduction,incorporation of nitrogen is known to en-hance the NBTI degradation.Following the approach that NBTI degradation is solely linked to the creation of interface traps,it means that the nitrogen atoms should modify the properties of the interface.Several possibilities have been already discussed in literature as the introduction of mechanical stresses in the atomic structure close to the SiO2/Si interface,a catalytic role [15],an increase of Pb1proportion with respect to the Pb0center[16],a reduction of the activation energy of SiH bond[17].Whatever the mechanism which might be involved here,the incorporation of nitrogen atoms should modify the interface degradation rate.To solveout that question,both n-MOSFETs and p-MOSFETS devices with either pure or nitrided oxides have been stressed under NBTI stress conditions with thicknesses ranging from 2nm to 10nm.Fig.7shows that the inter-face traps creation is identical for pure and nitrided oxi-des over a wide range of oxide thicknesses.It means that for interface traps creation the oxide field is the major driving force and not the nature of the oxide itself.A crucial point is raised here because the strong impact of the incorporation of nitrogen on the NBTI degrada-tion is well documented in the literature.But,the inter-face traps creation is not modified by the presence of nitrogen atoms.This contradiction shows that the inter-face traps cannot be the sole root cause of the device parameter shifts.This point will be discussed further in this paper.2.7.Temperature dependenceBesides the importance of the oxide field,the NBTI degradation is also activated with temperature.Fig.8shows the influence of the temperature on the interface traps creation for temperatures ranging from 50°C to 200°C under similar oxide field.The time dynamics present two main characteristics:power law behaviour at low stress times and saturation phenomenon for long stress times.Besides it should be noticed that for low stress times,the power law exponent increases with tem-perature.Fig.9shows that it increases linearly with tem-perature.The combination of these two factors implies that the apparent activation energy E a (as determined through degradation levels in an Arrhenius plot)at a given time is not a constant value.Fig.10shows that E a varies with the stress time,increasing for low stress times and finally decreasing for long stress times.As a consequence,the interface traps creation is a non-Arrhenius phenomenon [18],which requires a deeper analysis to understand both the temperature dependence and at the end the physical mechanisms lying behind.This analysis is required in order to be able to determine realistic extrapolation laws for various temperatures.2.8.Time dynamicsUnderstanding the physics that lies behind the NBTI degradation requires to understand not only the oxide field and temperature dependences of the interface traps creation but also the time dynamics.It is also a strong requirement in order to develop an accurateextrapola-6V.Huard et al./Microelectronics Reliability 46(2006)1–23tion model for device lifetime.A characteristic feature of the interface traps creation during NBTI degradation is its fractional power law time dependence(cf.Fig.11). As most of the published data,our experiments span a range from0.2to0.3for the power law exponent.Nev-ertheless,the fractional time dependence of NBTI degra-dation decreases at longer stress times and indicates a tendency towards saturation.Several phenomenological models have been pro-posed to explain the formation of interface traps associ-ated with NBTI degradation.Jeppson et al.[19] proposedfirst a diffusion-controlled mechanism to ex-plain the observed time dependence of interface trap generation.Other authors suggested a similar mecha-nism and examined the time dependence of different charged diffusing species[4,20].Their common assump-tion is that as reaction-limited time dependence obeys a linear relationship,the observed fractional time depen-dence has tofind its origin in a diffusion-limited mode. Diffusion of hydrogenated species away from the inter-face could possibly explain the power law dependence (t a)of the interface traps creation down to t1/2[4],and indeed,at the time,observed values of power law expo-nents ranged between0.75and0.5.However,in more re-cent years,time-dependencies below t1/2and saturation effects are common for sub-micron devices.Recent stud-ies proposed new evolutions of such approach to explain power law exponents ranging about0.25[21,22].In light of the analysis of such Reaction–Diffusion(RD)models, it is possible to distinctly observefive different regimes of evolution(cf.Fig.12from[21]).At short times(t<s reac) (regime1),the system is reaction limited with a charac-teristic slope of1,linked directly to the dissociation en-ergy of SiH bonds.In this approach,it is important to notice that all bonds are identical and the system can be described by a single dissociation energy E d.In re-gime2,the reaction is in equilibrium but theflux of hydrogen away from the interface is negligible.Regime 3is characterized by the hydrogen diffusion limited time dependence described by a power law exponent,which is independent of the oxidefield and/or the temperature but is only determined by the nature of the diffusing hydrogenated species.In regime4,the power law expo-nent increases up to0.5due to hydrogen diffusion into the gate which is supposed to occur with infinite diffu-sion velocity.Finally,in regime5,the generationslowsdown due to saturation of the process and the lack of new bonds to be broken.In order to check the validity of this approach to de-scribe the NBTI degradation,it is important to get some new insights into the interface traps creation during NBTI degradation.One way is to apply preliminary stresses(pre-stress)on the devices in order to break some SiH bonds present at the interface previous to the stress.By doing so,according to the RD model, the regime1should not be impacted since its slope and time constant are only defined by the dissociation energy E d of the bonds.But,a parallel shift downwards of the regime3power law part is expected due to the reduction of the maximum saturation level linked to the maximum number of SiH bonds present previously to the stress.Actually,Fig.13shows that pre-stressing a transistor modifies the reaction-limited part,with a decreasing linear slope(i.e.increasing associated dissoci-ation energy E d)when pre-stress lasts longer.It strictly means that SiH bonds can have various dissociation energies.Concerning the interface traps generation, many authors[23,24]have already reported that the de-fect activation energy of SiH bonds at the interface show a broadened Fermi derivative distribution g(E,r)(with r about0.1eV).In case of distributed dissociation ener-gies,for a given pre-stress time,the slope of the linear part is proportional to the number of SiH bonds for that particular dissociation energy over the characteristic time constant related to this dissociation energy.Our analysis led for two oxidefields on large number of pre-stress times shows that the dissociation energies can befitted by a broadened Fermi derivative distribu-tions with a spread r about0.1eV(cf.Fig.14),as found by other experimental approaches[23,24].In conclusion, we have presented in this section experimental proofs that the SiH bonds at the interface have dispersed disso-ciation energies according to a broadened Fermi deriva-tive distribution.This is an important statement,which will be driven the way we understand and model the interface traps creation.2.9.Model for interface traps creationBreaking a Si–H bond at the interface is often de-scribed by afirst-order reaction such asRðt;sÞ¼1ÀeÀt sÀÁð1Þwhere s represents the time constant of the reaction and is supposed to be directly related to the dissociation en-ergy of the bond E d.Dissociation energy is defined in8V.Huard et al./Microelectronics Reliability46(2006)1–23this case either as the energy to break the SiH bond or the migration barrier the H atoms have to pass over to be released.For degradation times shorter than the time constant(t<s),the degradation rate presents a linear behaviour with time and so a constant defect generation rate P gen=1/s.As shown previously,SiH bonds at the interface do not present a single dissociation energy E d but a contin-uum of energies which,in agreement with other authors [23,24],will be further described by a broadened Fermi derivative distribution g(E d,r)due to disorder-induced variationsgðE d;rÞ¼1re E dmÀE drÀÁ1þe E dmÀE drÀÁ2ð2Þwhere E dm is the median dissociation energy and r is the spread of the distribution with experimental values about0.1eV.In this approach,every single bond is broken accord-ing to afirst-order equation,but each of them with a specific time constant depending on their own dissocia-tion energy.In consequence,given a range of bond ener-gies,lower-energy bonds would be broken relatively quickly leaving higher-energy bonds to be broken more slowly.The degradation rate results from the combina-tion of every single defectfirst-order equation rate, which has been analytically derived as[25]D N it it max ðtÞ¼Z1gðE d;rÞRðt;sðE dÞÞd E d/11þtsÀÁÀað3Þassuming s¼s0expðE dðE oxÞÞand a¼kT for s min<t<s,T being the bond temperature and s min the time constant of the weakest defect.The resulting evolution of the interface traps genera-tion with stress time according to Eq.(3)is shown in Fig.15.For very short times(t<s min),the degradation is lin-ear,with a slope linked to the defect generation rate of the weakest bonds.For longer stress times,more and more different bonds participate to the degradation, yielding to power-law dependence such as described in Eq.(3)with afinal saturation when less and less bonds are left to be broken.Fig.16shows that experimentaldynamics for various temperatures can be well repro-duced by Eq.(3),even the saturation effect that is clearly visible at higher temperatures.An important point in describing the temperature behaviour of the interface traps creation is the capability of the model to predict the temperature dependence of the power law exponent.The linear temperature depen-dence of the power law exponent was already pointed out above in Fig.9.In Fig.17,according to Eq.(3), the spread of the distribution r is determined byfitting experimental power law exponentsÕevolution and is found to be about0.1eV,as previously deduced by non-related methodologies.Due to the various temperature measurements,not only the spread of the distribution is known but it is also possible to have a close idea of what is the saturation value N it max.For a given value of oxidefield and various temperatures,studying the evolution of the time con-stant s,it is possible to extract the constant s o for 2.1nm nitrided oxide.Its value was found to be 1.34·10À8s in this case(cf.Fig.18).This value was found to be identical for various oxidefields.Once thisV.Huard et al./Microelectronics Reliability46(2006)1–239constant is known,it is possible to study the variation of s with oxidefield.This study yields to the determination of the mean dissociation energy E dm,function of theoxidefield.Fig.19shows that the dissociation energy evolves almost linearly with the oxidefield with aflat band limit of about1.5eV,which spans in the range of theoretical values(1.5-1.8eV)proposed by Pantelides et al.[26]for the migration barrier;depending if the hydrogen species migrate away in the substrate or in the oxide.Fig.20shows that using this model allows a good evaluation of the evolution of the apparent activation energy of the interface traps creation.It has to be noted here that if the overall interface traps creation phenom-enon seems to have a non-Arrhenius behaviour,every single bonds considering its own dissociation energy follow an arrhenius behaviour.The deviation from the10V.Huard et al./Microelectronics Reliability46(2006)1–23Arrhenius behaviour only occurs through the existence of the distribution of dissociation energies of the SiH bonds.Besides,this set of parameters allows reproducing not only ultra-thin oxides but also thicker oxides as shown in Fig.21(Nit creation for pure thick oxides with various oxidefields).In conclusion,we have developed a consistent physi-cal-based model of the interface traps creation,which al-lows reproducing all features including oxidefield and temperature dependence over a large range of oxide thickness.3.Threshold voltage degradationSo far,we have made the assumption that the NBTI degradation is only related to the creation of interface traps.We have carefully studied how they are created and how it is influenced by the various stress parameters. But,to understand the impact of the NBTI degradation up to circuit level,it is important to make the link with device parameters such as threshold voltage.As NBTI degradation is mainly a build-up of charges at the inter-face in a symmetrical configuration along the channel, the threshold voltage parameter is more relevant to de-scribe the degradation than other parameters such as the saturated drain current.3.1.Methodology of measurementsFor the NBTI stress characterization,the devices are typically stressed under a constant gate voltage,gener-ally higher than V dd in order to benefit from an acceler-ated degradation,while the source,drain and bulk are grounded.But the stress is periodically interrupted on a linear or a logarithmic time scale,and device parame-ters(threshold voltage,drive current,etc.)are measured at nominal voltage to monitor the degradation.This ap-proach is based on the assumption that the degradation is permanently generated and cannot be removed once the stress is switched off.But,as already shown by Ershov et al[27],inserting a delay between stress inter-ruption and measurements yields to a recovery of at least a part of the degradation.Similar experiments were led measuring both the threshold voltage and the inter-face traps creation through CP measurement.As shown in Fig.22,artificially increased delay between stress interruption and measurements yields also in our case to a partial recovery of the threshold voltage shift.But it is important to notice that the number of interface traps created during the stress is similar.By the way,it is important here to consider the number of interface traps as determined through the integration of the bell-like CP curve and not to make a direct link with the maximum value of the CP current I cpmax.Actually,dur-ing the recovery phase,I cpmax is slightly reduced but the width of the bell-like CP curve is also changed.Leading the integration of this curve shows that the total number of interface traps created during the stress remains con-stant in spite of the reduction of I cpmax.The combination of the unchanged interface traps density,the partial recovery of threshold voltage and the modified edges of the bell-like CP curve with an increased delay points out the fact that the NBTI-induced threshold voltage degradation is not only related to the creation of inter-face traps but a second component has to be taken intoaccount.。

solarcell_technology

• Third Generation

– Nanocrystal solar cells – Photoelectrochemical (PEC) cells • Gräetzel cells – Polymer solar cells – Dye sensitized solar cell (DSSC)

SOLAR CELL TECHNOLOGY

Cho, Woo-Suhl Xufeng Wang James E Moore Tom Adams

Outlines

• What is a Solar Cell: Overview and Fundamentals • First Generation: Silicon Solar Cell • Second Generation: Thin Film Solar Cell • Beyond Solar Cell: Betavoltaic Cell Technology

– Only a fraction better efficiency than selenium cells – Less expensive Si basis: a step towards greater efficiency

– Diffused Si p-n junction: Experimenting with semiconductors, accidentally found that Si doped with certain impurities was very sensitive to light – Array of thin Si strips: 6% efficiency

4

Photovoltaic Effect

• Incident light causes an excitation of electrons from the valence band into the conduction band everywhere in the device

第一章细胞生物学绪论

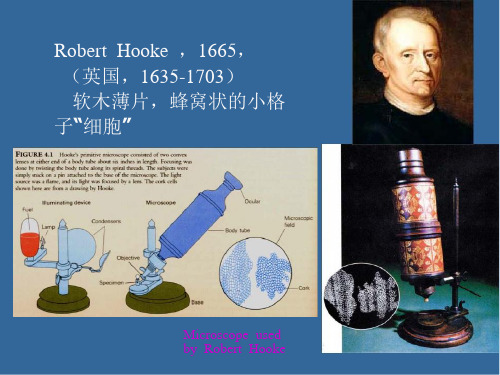

3.细胞学的经典时期 (1)原生质(protoplasm)理论的提出: 1840年,普金耶(J.E.Pukinje)和1846 年冯•莫尔 (Von Mohl)将动植物细胞“肉样质”内含物称为原生质 (protoplasm)。 1861年,Max Schultze提出了原生质理论:有机体的 组织单位是一小团原生质,这种物质在一般有机体中是相 似的。并把细胞明确地定义为: “细胞是具有细胞核和细 胞膜的活物质”。 1880年,Hanstein提出原生质体(‘protoplast)概 念:细胞是由细胞膜包围着的原生质,原生质分化为细胞 核和细胞膜。较cell(细胞,小室)更确切了。

细胞生理学(cytophysiology)的研究: 19世纪末叶,对活细胞的细胞质流动、肌肉收缩、变 性运动、纤毛与鞭毛运动,细胞膜通透性、细胞的应激性、 神经传导开展了大量研究。 Harrison与Carrel创立了组织培养(1909)。Carrel 研制成Carrel培养瓶,采用严格的组织培养技术,成功地培 养了鸡胚胎成纤维细胞持续了34年(1912-1946)。 Claude用高速离心机分离细胞核和各种细胞器的技术 (1943) 。

美国细胞学家威尔逊(E.B.Wilson,1856~1939): 1905年,他和斯特蒂文特(A.H.Sturtevant,1891~1971) 以细胞学的事实,确定了染色体同性别的关系,并提出XX 为雌性,XY为雄性。

细胞生物学在整个生命科学学科体系中的定位

化学生物学与合成生物学

电能

风能

化能自养

太阳能

光能自养 有氧代谢

新工生命体系

水能 核能

二氧化碳还原酶在电极上的定点偶联

利用电能进行淀粉生物合成

形成电能细胞,创新生物的能量来源,引领下一代生物技 术的发展,如生物计算机、生物传感器、分子马达等。

电子催化酶与电子传递通道设计

电能驱动

线粒体基因组人工合成与优化组装

Why designing artificial enzymes?

➢ Approaches to novel biocatalysts: Top down: reprogramming native enzymes Bottom up: design and engineering artificial biocatalysts

(cytochrome c oxidase hydrogenase)

(photosystem II)

Most important enzymes for sustainable energy are metalloenzymes. However, metalloenzymes are too expensive.

➢ Structural features (bond distance, angle and geometry) vary widely and ill-defined;

➢ Most metal ions have beautiful colors and strong magnetic properties, serving as in situ probe of the design process.

C. H. Kjaergaard, J. Rossmeisl, and J. K. Nørskov, Inorg. Chem. 49, 3567–3572 (2010).

ESmtg

THE EARTHSCOPE PROJECT

Seismic, GPS and MT components (+ drilling of San Andreas Fault) Data archived and freely available Further Information

A brief review of electrical conductivity and the MT method

Regional conductivity structure of NW USA from 3D inversion of EMScope MT data an overview

2 1000m

4 30m

“Transverse Magnetic” (TM) Mode: Electric currents flow across to the geologic strike—magnetic fields are parallel

Two-dimensional Earth—effect of shallow near-surface

a 1/ a

depth

GDE_060607

Impedance Tensor

For 2D case (preferred geologic strike) the tensor will have the special form

Ex 0 E Z y yx

Z xy Bx 0 By

When expressed in the proper coordinate system … problem decouples into two “modes” … TE and TM

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AN OVERVIEW OF MWT CELLS AND EVOLUTION TO THE ASPIRE CONCEPT:A NEW INTEGRATED MC-SI CELL AND MODULE DESIGN FOR HIGH-EFFICIENCIESI.G. Romijn, A.A. Mewe*, M.W.P.E. Lamers, E. Kossen, E.E. Bende, A.W. WeeberECN Solar Energy, P.O. Box 1, 1755 ZG Petten, The Netherlands*Corresponding author: Phone: +31 224 564323; Fax: +31 224 568214; email: mewe@ecn.nl ABSTRACT:At ECN, we are developing several different cell concepts to reduce the €/W p costs of crystalline silicon solar cells by increasing the efficiency on thin and large solar cells. Our metallization wrap through (MWT) concept PUM reduces the shading losses from the front side by 3%, which results in a gain in J sc. Furthermore, the cells are fully back contacted and easy to implement in a module. Another way to improve efficiencies, especially on thin wafers, is to replace the full aluminum BSF at the rear side by a more appropriate passivating layer like silicon nitride in combination with partial rear metallization. In this paper we present the development at ECN from standard H-patterned cell processing towards a combination of the two concepts mentioned above:our rear side passivated PUM cell, the ASPIRe cell. The proof of concept of the ASPIRe cell will be given. Compared to PUM reference cells, ASPIRe cells have reached higher J sc and V oc, although the FF still remained behind. The highest efficiency obtained so far for ASPIRe cells is 16.4%, and methods to improve the FF by changing the rear side Al pattern are shown.Keywords:multi crystalline, metal-wrap-through, back contact, bifacial1INTRODUCTIONTo remain competitive in the future, wafer-based solar cell manufacturers will have to reach high efficiencies on thin and large cells. These cells should be easy to implement into a module, or, ideally, an integrated cell and module concept should be developed. Back-contacted cells like Metallization-Wrap-Through (MWT) are easier to implement into a module than the conventional H-pattern cells with contacts on both sides since the contacting can be done completely at the rear side.However, processing of (very) thin and fragile MWT cells using a full area Al back surface field (BSF) will reduce the cell efficiency due to a non optimal passivation and optical confinement of the rear [1-7]. Furthermore, the use of such MWT cells will still cause problems for module assembly due to the increased bowing.To overcome this major drawback, we have introduced a new MWT concept ASPIRe: A ll S ides P assivated and I nterconnected at the Re ar. The ASPIRe cells are based on our existing MWT PUM cells [8-10]. The emitter metallization is led to the rear side via 16 holes in the wafer, while the front side metallization is changed into a symmetric pattern around these holes. A similar pattern is now also applied on the rear side.The rear side of this cell is passivated with a single silicon nitride layer (SiN x) and local metallization is applied. Better rear surface passivation and better optical confinement results in higher efficiencies. Furthermore, the cell warping is reduced to 0 and the lower Al consumption will reduce the cell manufacturing costs considerable.When local Al contacts are used at the rear side, a challenge is to obtain good fill factors while keeping optimal rear surface passivation. Less metallization at the rear, for instance by using narrower aluminum lines, will decrease the FF, but improve (lower) the rear surface recombination since the passivation by a silicon nitride layer is superior to that of the local fired through Al contacts. More metallization at the rear will have the opposite effect, higher FF but worse rear surface passivation. At ECN we have developed a 2D simulation program to optimize the rear side metallization pattern while keeping the metallization fraction constant, such that the rear surface passivation remains the same[11].As for the front side of PUM cells, the modular design on the rear side of the ASPIRe cells allows more freedom in the pattern design compared to the standard H-pattern design a better balance between the FF and rear side passivation can be achieved.2METALLIZATION WRAP THROUGH CONCEPTIn the past, several back contact solar cell concepts have been developed for multi or mono crystalline silicon solar cells. Most commonly known are the interdigitated back contacts (IBC), emitter wrap through (EWT) or metallization wrap through(MWT) cells [12-18].Compared to IBC or EWT, the processing of MWT cells is relatively simple, and can be applied on both low and high material quality.For IBC cells the emitter is only applied at the rear side. In this case the material quality should be high to prevent too much bulk recombination. For EWT cells the emitter is applied on the front side, and led to the rear via a large number of holes in the wafer. This means in principle lower material quality can be used compared to IBC cells. The metallization in both (IBC and EWT) cases is only applied at the rear side.For MWT cells the emitter is applied on the front side as well as in the holes, thus also lower material quality can be used. Compared to EWT, the conduction in the holes of MWT cells is high because of the application of metal inside the holes. This means a limited number of holes will be sufficient to enable a good FF for MWT cells, making the processing easier than for EWT.In the past, several institutes have worked on MWT cell concepts [8-10,14-18].Already 10 years ago, IMEC reported their MWT concept, using cells madeon 100 mm 2 wafers [12,13]. The front busbars were replaced by laser holes while the amount of front Ag fingers was kept intact. The cells could be contacted into a module in a conventional way: strings were made using tabbing material interconnecting the emitter and base busbars on the rear side.More recently, researchers from ISE reported on MWT cells made in a similar way on mc-Si material [15]. Forty eight laser-drilled holes replaced three busbars on the front side. Again, contacting into a module was done in a conventional way by soldering strings on the busbars on the rear side. An efficiency gain of 0.6% was reported for tabbed and laminated MWT cells compared to standard solar cells.At previous conferences, ECN introduced the MWT-PUM technology.Unlike the MWT concepts mentioned above, this is a completely integrated cell-and-module concept [8-10].The front side metallization pattern is shown in figure 1. This pattern is symmetric around 16 holes through which the emitter metallization is led to the rear side ofthe wafer.Figure 1: PUM front sideThe emitter and base contacts are no longer the usual busbars, but evenly spaced dots on the rear surface. This enables a more homogeneous layout of the front fingers resulting in lower shading losses and a higher FF when the cells are connected into a module. Interconnecting the cells into strings is no longer necessary. The cells are placed into a module by simply picking and placing them on a conducting foil where the emitter and base contacts are directly soldered or glued [8,19].With this MWT-PUM technology, an efficiency gain of 0.6-0.8% absolute has been demonstrated on full module size due to lower metallization coverage and less resistance losses after interconnection [9,10].Moreover, the modular metallization pattern around the holes makes it very easy to adapt the PUM concept to larger cell sizes without loosing in the FF. 3PROCESS DEVELOPMENTS TOWARDS ASPIRE3.1Different cell conceptsFigure 2 shows four different cell concepts that are currently under investigation at ECN.Integrated cell and module conceptRear side passivation Base: pn+by silicon nitride Open metallization1.The first one is the well known ‘standard’ H-patterned mc-Si solar cell with a full aluminum rear surface. This cell concept is used by almost all PV manufacturers since it is quite straightforward and enables reasonable cell efficiencies. The standard H-patterned concept relies on both front and rear contacting into strings for module manufacturing. When the wafers become too thin, the cells will start to bow after the high temperature ‘firing’ step due to differences in thermal expansion. This, especially in combination with the stringing of cells into modules, will increase the chance of breakage for thinner and larger wafers.2.To increase the current, and enable all rear sideinterconnection of the solar cells, the so-called ‘PUM’ MWT cells were developed at ECN [1,14]. The emitter contacts are led towards the rear through 16 holes (for 156x156 mm 2 sized cells). The front metallization is modular in design around the holes and there are no busbars necessary, reducing the metallization (shadowing) fraction by 2-3%. Furthermore, the complete rear side interconnection enables simple ‘picking and placing’ of the cells into a conducting foil [17], which reduces the chance of breakage considerably during module manufacturing.3.To reduce the bowing and increase the efficiency ofsolar cells, the full aluminum rear surface has to be replaced by a better passivating rear surface layer with open rear metallization. At ECN we successfully tested SiNx passivating layers on the rear side of standard H-patterned solar cells [1].A gain in J sc of ~ 3% relative has been realized for 125x125 mm 2 wafers showing the potential of this concept.bining the two new ECN cell concepts, wearrive at the ASPIRe cell concept: All Sides Passivated and Interconnected at the Rear (figure 3)In this cell, the advantages of all rear side interconnection and reduction of shadow losses are combined with those of a passivated rear surface with open Al metallization. This concept will enable both higher efficiencies and easier module manufacturing [1].Figure 3: ASPIRe front and rear sideIn the next paragraphs, the optimization of the PUM concept, and the development and optimization of the ASPIRe cell concept are described in more detail. The development towards the rear side passivated solar cells is already extensively discussed in previous publications [1].3.2H-pattern towards PUMThe processing of the PUM cells is very similar to the standard H-pattern processing, except for the laser drilling of the 16 MWT holes, the application of a different metallization pattern including printing Ag inside the holes, and hole isolation after the co-firing step. The flow charts of the two cell types are shown in figure 4, with the additional steps for PUM indicated in red italics.“Standard”industrial cellAl rear metallizationCo-firing Edge isolationAg front and rear metallizationFront side SiN xP-glass removal Emitter diffusion IsotextureHole lasering Isotexture Emitter diffusion P-glass removal Front SiN xAg front, hole , rear metallizationFlow chart PUM processingCo-firingAl rear metallizationHole and edge isolationFigure 4: flow charts of a ‘standard’ and a PUM cell The comparison between H-pattern cells and PUM cells is to be treated with delicacy. The only reliable comparison – especially with respect to the fill factor -can be achieved after interconnection or laminationof single or more cells. In previous publications, we have shown [9,10] that after interconnection and lamination PUM results in about 0.6-0.8% higher absolute efficiency than conventional H-pattern modules.In figure 5, modules of standard H-pattern cells and PUM cells are shown, together with the IV results.I SC (A)V OC (V)FF (%)P (W)H pattern 7.6622.3.72015.2123PUM 7.8622.3.73315.8128Figure 5: comparison of standard H-patterned and PUM cells on module levelRecently, PUM processing has been improved even further.The processing of the metallization inside the holes has been optimized, yielding a much more stable processing and fill factor.Instead of applying metallization only on the edges of the holes, a ‘plug’paste was used which completely fills the holes. The improved FF is shown in figure 6. The reference group has been processed in the ‘old’ way. The plug paste clearly improve both the absolute value (by 1.4% absolute) and the standard deviation of the FF. The J sc and V oc values for the PUM cells processed with the plug paste are similar to those of the reference group, which resulted in an improved efficiency of 0.2% absolute compared to the reference. The more stableProcessing our rear side passivated solar cells –either H-patterned or MWT ASPIRe– is again very similar to the standard mc-Si H-patterned or PUM cell processing. In figure 7 the flow diagrams for our H-patterned open rear side cells (PASHA) [1,21] and ASPIRe are shown.Flow chart PASHA cellAg front and rear metallizationAl rear metallizationCo-firingFront and rear SiNx P-glass removal and cleaningRear emitter removal & smoothing Emitter diffusionIsotextureflow chart ASPIRe cell P-glass removal and cleaningFront and rear SiNxAg front and rear/hole metallizationRear emitter removal/ structuring Emitter diffusionIsotexture Hole lasering Al rear metallizationCo-firingFigure 7: flow charts of the rear side passivated cell concepts PASHA and ASPIRe. Steps that differ from the standard H-pattern processing are indicated in red italics. Note that for neither concept laser isolation is needed after the co-firing step.After diffusion, the rear side emitter is removed and the rear surface is polished to enable better surface passivation by the silicon nitride. A single SiN x layer, which is optimized for maximal passivation is applied on the rear side, after which the ‘standard’ anti-reflection coating is applied on the front side. Metallization is applied on the front and the rear side, and inside the holes for ASPIRe, after which the contacts are formed in a single firing step. In the case of ASPIRe, special care has to be taken that the emitter contact inside the holes and on the rear surface do not cause any shunts.As can be seen from the flow diagrams, no additional laser processing is necessary for the isolation.4PROOF OF CONCEPT AND OPTIMIZATION OF ASPIRE4.1IV results of different cell conceptsAt the previous conference, we already presented 125x125 mm 2bifacial cells with an increase of almost 3% relative in J sc compared to full Al reference cells. The optimization towards larger (156x156 mm 2) Pasha cells is still ongoing [19].The first ASPIRe cells were processed in January 2007. At the Milan conference the first results were presented, with cell efficiencies up to 15.9% on 160 µm thin material. On thinner (130µm) material, unfortunately of lower quality, 15.5% efficiency has been reached.Recently several batches of wafers, all of 156x156 mm 2 and 180 µm thin neighboring material, were processed into ASPIRe cells.At this point, the rear side pattern of the ASPIRe cells is not optimized yet.Especially the series resistance in the aluminum linesresults in a lower FF. For the ASPIRe cells discussed in this paragraph and shown in table 1 and figure 8, we exclude the influence of the high series resistance by shorting the rear aluminum lines. In this way a better comparison can be made between the cell parameters of PUM and ASPIRe.Of course, a real comparison should be made on module level [10].The first two batches yield an average efficiency of 15.8% and 15.6%. PUM reference cells had a higher average efficiency of 16.0, mainly due to a higher FF (see table 1) even though the rear aluminum of the ASPIRe cells has been shorted. This indicates that also other aspects of the rear ASPIRe pattern like aluminum line distance and line width should be optimized further.By applying a better and more homogeneous texturization on the ASPIRe cells, average efficiencies of 16.1%, with a maximum of 16.4% were reached on a third neighboring batch. The results of the PUM and ASPIRe cells are summarized in table 1.Table 1: Average and maximum IV results for the ASPIRe and PUM solar cells. Average values were taken over 10 (ASPIRe 1) or 7 (ASPIRe 2 and ASPIRe 3) cells.4.2Discussion of IV resultsAs can be seen from table 1 and figure 8, the J sc and V oc considerably improved for the subsequent ASPIRe batches. This is partly due to a more controlled processing as we gained more experience with ASPIRe processing over time. For a larger part, this is due to a decreased line-width for the rear side Al pattern in batch 2 and 3 compared to batch 1. The total coverage of rear side Aluminum decreased from 17-20% in the first batch towards ~10-12% in the second and third batch. To enable this, both the line width in the printing screen was decreased and a better firing through aluminum paste was used. However, while the FFs for the first batch were reasonable good (although still lower than those of the PUM reference) for the second and third batch the values are lower. The decrease in line-width causes a higher R series on the rear side which is directly reflected into the FF.While the FF drops, J sc and V oc increase for narrower aluminum lines. This can be seen when ASPIRe batches 1 and 2 are compared. This is expected, since the passivation obtained with the silicon nitride coating is better than the passivation by the fired through local Al back surface field (BSF).For group 3, a better texturization was used on the front side. Besides yielding both a higher J sc and a higher V oc , also the FF improved probably due to a more homogeneous surface.Detailed analysis on the PUM and ASPIRe cells, such as IQE and PC1D analysis, should still be done.currently ongoing at ECN.To optimize the rear side metallization pattern,by using for instance shorter lines to the rear contact points while keeping the metallization fraction the same, a 2D cell simulation program is being developed at ECN.The first calculations resulted in 4 new rear side patterns for the ASPIRe cells. The reference pattern 1 has 15 base contact points, and around 13% metallization. Pattern 2 and 3 have 25 base contact points, with 15% and 23% metallization. Pattern 4 and 5 have 64 base contact points, again with 15 and 23% metallization. The V oc*J sc and FF results for ASPIRe cells using the different rear side aluminum patterns are shown in figure 9a and 9b. In this case, the IV and FF results are shown without rear side patterns. On the x-axis the number of base contact points and the metallization percentage are mentioned.Additional efficiency gain will be achieved by improving the formation of the local BSF below the aluminum lines. In that case, a higher metallization fraction (like pattern 3 or 5) could be allowed and still result in high V oc*J sc. Achieving a FF of 77% while keeping J sc and V oc the same, will result in efficiencies of 17 % for ASPIRe cells similar to those in batch 3.5MODULE MANUFACTURINGThe ASPIRe cells will be interconnected into either by soldering or by gluing the reara module using the new ECN pilot line for rearcells into modules [19]. Although theinterconnection of ASPIRe cells into agluing, the ASPIRe have been tested in our climate chambers. Thetested in our climateFigure 11: 2x2 laminate of 160 µm thin ASPIRe cells for climate testing6CONCLUSIONSIn this paper we presented the development at ECN from standard H-patterned cell processing towards our rear side passivated PUM cell, the ASPIRe cell. The ASPIRe cell combines the properties for enhancing efficiencies of the MWT PUM concept and the PASHA cell concept. Proof of concept for the ASPIRe cell concept has been given, and several batches of ASPIRe cells were processed. Efficiencies similar to the PUM cell were reached. The highest efficiency obtained so far for ASPIRe cells is 16.4%. A first optimization of the aluminum rear side pattern was performed for ASPIRe, yielding 3% absolute higher FF for the same J sc and V oc. In the future, this pattern will be further optimized towards values of 77%, and efficiencies of 17% for ASPIRe cells will be within reach.7ACKNOWLEDGEMENTSThis work was financially supported by the FP6 European Crystal Clear project (EC contract SES6-CT-2003-502583) [22] and by the Dutch Senter Novem project StarFire (EOS-ES program project IS063024) [23]. All project partners are gratefully acknowledged for their helpful discussions and fruitful collaboration. Solland Solar Energy BV is acknowledged for using the front side metallization pattern of the ASPIRe and PUM cells8REFERENCES[1] I. G. Romijn et al., proceedings 22nd EPVSEC, Milan, September 2007; proceedings 21st EPVSEC, Dresden, September 2006[2] C. J. J. Tool et al., Solar Energy Mat. and Solar Cells 90, 2006, 3165-3173[3] L. Janssen et al., Progress in Photovoltaics: Res and Appl 15, 2007, 469-475[4] M. Hofmann et al., Proceedings 21st EPVSEC, Dresden, September 2006[5] G. Agostinelli et al., Proceedings 21st EPVSEC, Dresden, September 2006[6] P. Choulat et al., Proceedings 22nd EPVSEC, Milan, September 2007[7] M. Kaes et al, Proceedings 22nd EPVSEC, Milan, September 2007[8] J. H. Bultman et al., Proceedings WCPEC-3, Osaka 2003[9] P.C. de Jong et al., Proceedings 19th EPVSEC, Paris, 2004, 2145[10] A. W. Weeber et al., Proceedings 21st EPVSEC, Dresden, September 2006, 605;IEEE WCPEC-4, Waikoloa, Hawaii, mei 2006[11] E. E. Bende et al., proceedings 33rd IEEE Spec. Conf., San Diego, USA, 2008[12][13][14] E. van Kerschaver, et al., Proceedins 2nd World Conference on PVEC, Vienna, 1998, 1479[15] E. Van Kerschaver, et al., Proceedings 29th IEEE PV Spec. Conf., New Orleans, USA, 2002, 78[16] H. Knauss et al, Proceedings 31st IEEE, Orlando, USA, 2005[17] F. Clement, et al., Proceedings 22nd EPVSEC, Milan, September 2007[18] www.photovoltech.be[19] M. Spath at al, Proceedings 33rd IEEE Spec. Conf, San Diego, USA, 2008; This conference[20] A. A. Mewe, this conference[21] I. Cesar, this conference[22] G. Beaucarne et al., this conference[23] M. N. van den Donker, this conference。