数字电路-与非门OC门三态门

实验二 三态门和OC门的研究

图输出高电平VOH的下限值; VOL(max) --门电路输出低电平VOL的上限值; IOH(max)--门电路带拉电流负载的能力,或称放电流能力; IOL(max)—门电路带灌电流负载的能力,或称吸电流能力; VIH(min)--为能保证电路处于导通状态的最小输入(高)电平; VIL(max) --为能保证电路处于截止状态的最大输入(低)电平。 IIH — 输入高电平时流入输入端的电流; IIL -- 输入低电平时流出输入端的电流。

图3_2_5 计算OC门外接电阻Rc的工作状态

m'(7)个输入端(a) 计算Rc最大值(b) 计算Rc最小值图3_2_5 计算OC门外接电阻Rc的 工作状态

其中 IcEO -- OC门输出三极管T5截止时的漏电流; Ec — 外接电源电压值; m -- TTL负载门个数; n — 输出短接的OC门个数; m’— 各负载门接到OC门输出端的输入端总和。 Rc值的大小会影响输出波形的边沿时间,在工作速度较高时,Rc的取值应接近

3完成第七项中的思考题1233281用三态门实现三路信号分时传送的总线结构

实验二 三态门和OC门的研究 一、实验目的

(1) 熟悉两种特殊的门电路:三态门和OC门; (2) 了解“总线”结构的工作原理。 二、实验原理

数字系统中,有时需把两个或两个以上集成逻辑门的输出端连接起来,完成一定的逻

辑功能。普通TTL门电路的输出端是不允许直接连接的。图2_1示出了两个TTL门输出短 接的情况,为简单起见,图中只画出了两个与非门的推拉式输出级。设门A处于截止状态, 若不短接,输出应为高电平;设门B处于导通状态,若不短接,输出应为低电平。在把门 A和门B的输出端作如图3_2_1所示连接后,从电源Vcc经门A中导通的T4、D3和门B中导 通的 T5到地,有了一条通路,其不良后果为:图3_2_1 不正常情况:普通TTL门电路输 出端短接

与或非门电路

4. 同或门

◆ 能够实现 A⊙B “同或”逻辑关系的 L A B A B 电路均称为“同或门”。由非门、与门和或门组合而成的同或门 及逻辑符号如下图所示。

同或门电路:

逻辑符号:

提 示

双输入端同或门波形图:

当输入端A、B 的电平 状态互为相反时,输出端L 一定为低电平;而当输入端 A、B 的电平状态相同时, 输出端 L 一定为高电平。

◆

L A B

◆

三态门真值表

◆

三态门应用举例 (a)门电路选择 (b)数据双向传输 (c)总线结构

作

P50

业

2.6 2.7 2.8

(5)TTL与非门74LS00集成电路示意图

◆ 4个双输入与非门, ◆ 此类电路多数采用双列直插式封装。

2.2.2 MOSHale Waihona Puke 列门电路◆ CMOS门电路举例

▲ CMOS非门电路 ▲ CMOS与非门

2-2

▲ CMOS或非门

工作原理 A为高电平,T1截 止T2导通,L为低电 平,符合非逻辑关 系。

工作原理 A、 B同为高电平 时T1 、T2截止, T3 、 T4导通,L为低电平, 符合与非逻辑关系。 反之亦然。

◆

OC门的逻辑符号

◆

OC门线与的应用

L A B CD A B CD

2. 三态门

◆ ◆

什么是三态门 三态门的特点

除0、1外还有第三种状态——高阻抗状态 高阻抗状态时的输出阻抗非常大,输入与 输出视为开路,对外电路不起任何作用 计算机接口电路中广泛应用

三态与非门的原 理示意图及其符号

2.3.2 产品分类电路

1

1 1 1 1 1 1 1 1 1 1 1 1 1

数字电路第2章 门电路

2)输入负载特性 (ui R )

R1 3k b1 A B C T1 R2 750 R4 100

+5V

c1

T3

T2

3k

T4

R5 T5

F

ui

V

R

R3

360

R较小时 设:T2、T5 截止

A B C

R1 3k b1

+5V

R4

R2

c1

T1

T2

R5

T3

T4 F T5

R

ui

R3

R (5 U ) 4.3R ui be1 R1 R 3 R

I BS vcc vCES 5 0.3 mA 0.094mA βRc 50 1

V CC = +5V Rc iC 1kΩ vo c R b 10kΩ b β = 40 iB e

②vi=0.3V时,iB=0,三极管 工作在截止状态,ic=0。因 为ic=0,所以输出电压: vo=VCC=5V

IB 0

IC 0

VCE VCC

7

三极管的开关特性

+UCC 3V 0V RB RC uO T

+UCC

RC 3V

饱和时, VCE ≈ 0,C、 E极间电阻 很小 0V 截止时, IC ≈ 0,C、 E极间电阻 很大

C E

uO 0

相当于 开关闭合

ui

饱和 截止

+UCC RC

C E

uO UCC

避免!

0V 0

VL(max)

低电平

分立元件门电路和集成门电路:

分立元件门电路:用分立的元件和导线连 接起来构成的门电路。简单、经济、功耗低, 负载差。 集成门电路:把构成门电路的元器件和连 线都制作在一块半导体芯片上,再封装起来, 便构成了集成门电路。现在使用最多的是CMOS 和TTL集成门电路。

三态与非门原理

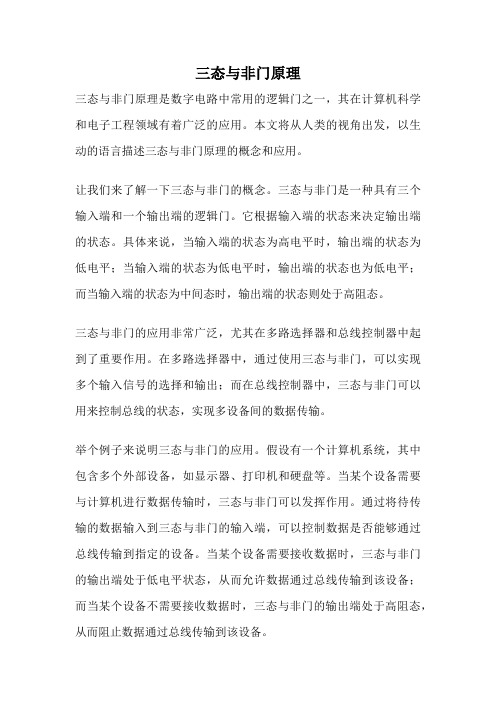

三态与非门原理三态与非门原理是数字电路中常用的逻辑门之一,其在计算机科学和电子工程领域有着广泛的应用。

本文将从人类的视角出发,以生动的语言描述三态与非门原理的概念和应用。

让我们来了解一下三态与非门的概念。

三态与非门是一种具有三个输入端和一个输出端的逻辑门。

它根据输入端的状态来决定输出端的状态。

具体来说,当输入端的状态为高电平时,输出端的状态为低电平;当输入端的状态为低电平时,输出端的状态也为低电平;而当输入端的状态为中间态时,输出端的状态则处于高阻态。

三态与非门的应用非常广泛,尤其在多路选择器和总线控制器中起到了重要作用。

在多路选择器中,通过使用三态与非门,可以实现多个输入信号的选择和输出;而在总线控制器中,三态与非门可以用来控制总线的状态,实现多设备间的数据传输。

举个例子来说明三态与非门的应用。

假设有一个计算机系统,其中包含多个外部设备,如显示器、打印机和硬盘等。

当某个设备需要与计算机进行数据传输时,三态与非门可以发挥作用。

通过将待传输的数据输入到三态与非门的输入端,可以控制数据是否能够通过总线传输到指定的设备。

当某个设备需要接收数据时,三态与非门的输出端处于低电平状态,从而允许数据通过总线传输到该设备;而当某个设备不需要接收数据时,三态与非门的输出端处于高阻态,从而阻止数据通过总线传输到该设备。

通过以上的描述,我们可以看出,三态与非门的原理和应用非常重要。

它在计算机系统的数据传输中起到了关键的作用,使得多个设备能够高效地进行数据交互。

同时,三态与非门的设计也是数字电路设计中的基本内容之一,对于理解和掌握数字电路的工作原理具有重要意义。

三态与非门是一种常用的逻辑门,通过控制输入端的状态来决定输出端的状态。

它在计算机科学和电子工程领域有着广泛的应用,尤其在多路选择器和总线控制器中发挥着重要作用。

通过对三态与非门的深入理解和应用,可以提高数字电路设计和计算机系统的性能和效率。

希望本文能够对读者对三态与非门有一个更加清晰的认识和理解。

(完整版)OC门及三态门解析

二、集成逻辑门电路的选用

若要求功耗低、抗干扰能力强,则应选用 工C根M作据O频S电率电路1路工M。作H其z要以中求下C和、M市驱O场S动4因0能0素0力等系要综列求合一不决般高定用的于 场合;HCMOS 常用于工作频率 20 MHz 以下、 要求较强驱动能力的场合。

若对功耗和抗干扰能力要求一般,可选用 TTL 电路。目前多用 74LS 系列,它的功 耗较小,工作频率一般可用至 20 MHz; 如工作频率较高,可选用 CT74ALS 系列, 其工作频率一般可至 50 MHz。

1. 电路、逻辑符号和工作原理 三态门的输出有0、1、高阻三种状态,故称三态门。

当出现高阻状态时,门电路的输出阻抗很大,使得输入 和输出之间呈现开路状态。

当 EN = 0 时,Y = AB, 三态门处于工作态;

当 EN = 1 时,三态门输出呈 EN 称使能信号或控制信号, 现高阻态,又称禁止态。 A、B 称数据信号。

注意:使用时, OC门公共输出端和电源 VCC 间接上拉电阻

三态门:输出0,输出1,输出高阻

注意:三态门输出端可并联使用,但同一时刻只能有一个 门工作,其他门输出处于高阻状态。

•TTL门电路的使用注意事项

EXIT

三、CMOS 数字集成电路应用要点

(一)CMOS 数字集成电路系列

CMOS4000 系列

EXIT

应用集成门电路时,应注意:

(1)电源电压的正确使用

TTL电路只能用+5 V(74系列允许误差±5%);CMOS 4000 系列可用 3 ~ 15 V;HCMOS系列可用 2 ~ 6 V; CTMOS 系列用 4.5 ~ 5.5 V。一般情况下,CMOS 门多 用 5 V,以便与 TTL 电路兼容。

数字电子技术 第2章 逻辑门

2

2.1

主要内容:

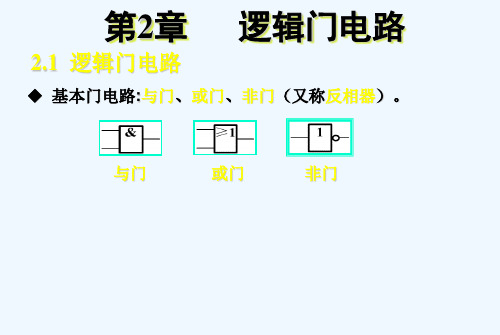

基本逻辑门

与、或、非三种基本逻辑运算

与、或、非三种基本逻辑门的逻辑功能

41

标准TTL门的输入 / 输出逻辑电平 :

42

CMOS门的输入 / 输出逻辑电平(+5V电源时) :

4.4V

0.33V

43

传输延迟时间tpd

t pd 1 (tPHL tPLH ) 2

tPHL和tPLH的定义(下图为非门的输入和输出波形) :

44

输入/输出电流 (1)“拉电流”工作状态 (2)“灌电流”工作状态

9

2.1.2 或门

实现“或”运算的电路称为或逻辑门,简称或门 。 逻辑或运算可用开关电路中两个开关相并联的例 子来说明

真 值 表

A 0 0 1 1

B 0 1 0 1

F A B

0 1 1 1

10

“或”运算的逻辑表达式为: F = A+B “或”逻辑的运算规律为:

一般形式

000 0 1 1 0 1 11 1

A

一般形式

A A A A 1 A A 0

14

非门的逻辑符号:

74LS04(六非门)

例2-5 : 向非门输入图示的波形,求其输出波形F。 解:

15

2.2 复合逻辑门

主要内容:

与非、或非、异或、同或的复合逻辑运算 与非门、或非门的逻辑功能 异或门、同或门的逻辑功能 各种复合逻辑门的真值表及输出波形

三态门和OC门的研究

要求

► 下载到FPGA目标板上,测试电路功能,写出

真值表。

负载电阻RL的选择

5V In

&

&

Y

&

&

&

&

&

&

要求

► a)用四个OC门线与,驱动四个与非门; ► b)计算负载电阻RL; ► c)在该阻值条件下,测量VH与VL。

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;

ENTITY tri_gate IS PORT ( din, en: IN STD_LOGIC; dout: OUT STD_LOGIC); END tri_gate;

B

1

EN

C

1

实体

F

1

A CB

ARCHITECTURE struct OF mux2_1 IS COMPONENT tri_gate PORT ( din, en: IN STD_LOGIC; dout: OUT STD_LOGIC); END COMPONENT;

EN

部件声明语句:部件调用前必须先声明

结构体

信号定义:内部节点必须定义为信号 SIGNAL CB: STD_LOGIC; BEGIN u1: tri_gate PORT MAP (B, C, F); 部件描述语句:节点必须按次序对应 u2: tri_gate PORT MAP (A, CB, F); CB <= not C; END struct;

74LS01 四2输入与非门(OC)

74LS01

四2输入与非门(OC)

输出显示

模式选为4

(自助实验区)

实验四 OC门与三态门

实验四 OC门和TS门

4. 实验内容及步骤

(1)用OC门实现“线与”

(a)四2输入与非门(oc)74LS03 电源电压VCC为+5V。

(b)六非门74LS04

负载电阻RL用100Ω 电阻和10K电位器串联代替, 用实验方法确定RLmax和RLmin的值, 并与理论计算值相比。

计算时取 VOH=2.8V, VOL=0.35V, n=4,VCC=+5V, IOH=0.05mA,ILM=20mA, IIL=1.6mA, IIH=0.05mA。

负载电阻的测定

RL RL(max)

理论值

实测值

RL(min) 验证:Y = A1 + A2 +A3+A4

OC“线与”实验电路

(2)用OC门实现电平转换 OC门实现TTL~CMOS接口电路

实验四 OC门和TS门

(4)三态(TS)门逻辑功能测试

四总线缓冲器74LSl25 (低电平使能有效)

电源电压为+5V

74LSl26(高电平使能有效)

实验四 OC门和TS门

Байду номын сангаас

测试TS门的总线功能

① 通过译码器 G 控制,使 Y0~Y3全部为“1”, 用万用表测量总线输出端 Y的电平,并观察LED状态。

RL(max)

VC' C nIOH

VOH mIIH

53

k 2.63k

20.2 9 0.04

RL(min)

VC'C VOL ILM mIIL

5 0.4 k 0.35k 16 31

选定的 RL值应在 2.63kΩ 与 0.35kΩ 之间,考虑标称值

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

“0” 1 “1”

1

IOH II H

+5V

+5V

TIO4H

Rb1 II H

“1”

T1

T5

负载能力的计算

II H

&

IOH

1

II H

“1”

&

II H

&

II H

&

IOH=NIIH N=IOH/IIH=400/40=10

II L

&

1

IOL

II L

“0”

&

II L

&

II L

&

IOL=NIIL N=IOL/IIL=16/1.6=10 N —扇出系数

外接Rc的最小值

m个

二、输出三态门 G为使门端 G

A

外设 B

1

R1 D R2

T3

T1

T2

R3 R5

+5V R4

T4 F

T5

主

1、工作原理

机

2 G=0时: F=AB

3

G=1时: T2、T5截止

D导通,T3、T4截止

总线

输出呈现高阻状态。

2、三态门符号

A

&

A

A

B

EN

FB

B

F

EN

EN

EN

EN=0时:F=AB EN=1时:F=Z Z为高阻

TP导通。输出VO≈VDD。

VI

VO

TN (2)当Vi =VDD时,TN导通,

TP截止,输出VO≈0V。

增强型场效应管

2.CMOS与非门和或非门电路

VDD

VDD

TP2

TP1

A

TP1

A

FB TN1

TP2 F

B

TN2

TN1

TN2

与非门

或非门

2. CMOS传输门

设MOS管的开启电压: TN管 2V TP管 -2V

直流参数

低电平输入电流 IIL≤1.6 mA 高电平输入电流 IIH ≤40 A 低电平输出电流 IOL≤16 mA 高电平输出电流 IOH ≤0.4 mA 低电平输出电压 VOL≤0.4V (10个负载) 高电平输出电压 VOH ≥2.4V (10个负载)

传输延迟时间

A

A1

F

F

50% 50%

实际波形

1

R 灌电流负载 (输出低电平有效)

“0” F

IOL—输出低电平电流(灌电流16mA)

3、输出特性 问题:输入电压和输出电压之间的关系

4、电压传输特性

+5V

1

RA

Vi

F

Vo

uo /V

UOH4 3

UOHmin 2

U0Lmax1 UOL0

1UffUon2

ui /V

Uff—关门电平 (输出高电平的最小值≥ 2.4V)

当EN=H时,传输门按下表工作

ui 0 1 2 3 4 TN √ √ √ √ TP √ √ √ √ uo 0 1 2 3 4

5 (V) 5 (V)

当EN=L时,两个MOS管 都截止,传输门不通,呈高阻。

CMOS逻辑门电路的系列

(1)基本的CMOS—— 4000系列。 (2)高速的CMOS——HC系列。 (3)与TTL兼容的高速CMOS——HCT系列。

tPd1

tPd2

A

tpd1—前沿传输延迟时间

F

tpd2—后沿传输延迟时间

理想波形

平均传输

tpd1+tpd2

延迟时间 tpd= 2

一、集电极开路(OC)与非门

为什么需要OCБайду номын сангаас? 普通与非门输出不能直接连在一起实现“线与”!

F=F1•F2

1 F1

“1”

F?

1 F2

“0”

+5V

I

T4 F1 T5

+5V

T4 F2 T5

课后作业: 2.1、2.3和2.10

三态门应用 双向总线驱动器,又称收发器

DI 1

EN

DO 1

EN

双向总线

DB

E

六、 TTL系列

系列

中速TTL(74) 高速TTL(74H) 肖特基(甚高速)TTL

(74S) 低功耗肖特基TTL

(74LS)

延迟功耗乘 积(微微焦耳)

100 132

57

传输延迟 /ns

OC门输出全为“1” 时: IOH —T5集电极漏电流

n个

VCC

RC

IRC

IOH

IIH

&

&

&

UOH &

UOH=VCC –IRCRC

+5V

=VCCR–1(nIOH+mRI2IH)RC

&

+VCC

&

RRCC UOH

A B

T1

T2

C

当UOH=UOHmin

时:

R3

F

RCTm5ax=

VCC–UOHmin nIOH+mIIH

10 6 3

19

9.5

功耗 /mW

10 22 19

2

实际的与非门器件

14

8

&

&

&

&

1

7

74LS00 2输入4与非门

14

8

&

1

7

74LS30 8输入与非门

2-5 CMOS逻辑门电路

1.CMOS非门

设VDD>(VTN+|VTP|), 且VTN=|VTP|

VDD (1)当Vi =0V时,TN截止,

TP

CMOS逻辑门电路主要参数的特点

(1)VOH(min)=VDD; VOL(max)=0。 所以CMOS门电路的逻辑摆幅(即高低电平之差)较大。

(2)阈值电压Vth约为VDD/2。 ViH(min)=VDD / 2

(3)其高、低电平噪声容限约 VDD / 2 。 (4)CMOS电路的功耗很小,一般小于1 mW/门;

T5饱和程度降低, 输出低电平抬高, 输出“不高不 F低”T。5电流过

大被烧毁。

OC门可以实现“线与”

VCC

A

RC

& F1

B

F

C & F2

D

F=F1•F2

OC门电路

A B C

+5V

+VCC

R1

R2

RC

T1

T2

R3

F T5

OC门必须外接电阻RC和电源VCC才能正常工作。

A

逻辑符号:

&

F

B

A B

F

RC的计算方法

A

&

B

A FB

A B

F

EN

EN

EN

EN

EN=1时:F=AB EN=0时:F=Z Z为高阻

3、三态门应用 多路开关

A1 A2

EN

1 G1 F

EN

1 G2

EN

1

当EN=0时,G1作为正常 与非门工作,G2的使门端 为1,G2输出端处于高阻 状态(相当于G2不起作用) F=A1

当EN=1时,G2使门端为0, G2作为正常与非门工作, G1的使门端为1,G1输出 端处于高阻状态(相当于 G1不起作用)F=A2

(5)因CMOS电路有极高的输入阻抗,故其扇出系数很大,达50

CMOS门电路功耗低,扇出数大,噪声容限大,开关速度与 TTL接近,易大规模集成,已成为数字集成电路的发展方向。

速度

TTL

快

CMOS 慢

功耗 大 小

噪声容限 扇出系数 集成度

小

小

低

大

大

高

1

F

ui Ri

+5V

Rb1

i

Ri

ui T1

TTL门电路输入端悬空时为“1”。

3、输出特性

问题:当输出端增加一个电阻时,如何保证输出端 是“1”或是“0”,或者是拉电流或灌电流

3、输出特性

“0”

“1”

1

R

拉电流负载

F

(输出高电平有效)

IOH

IOH —输出高电平电流(拉电流400A)

+5V

“1”

IOL

外接Rc的最大值

m个

VCC

RC的计算方法

RC

IRC

IOL

&

IIL

&

OC门输出中有 一个为“0”时: n个

“0”

&

UOL &

“1”

UOL=VCC-(IOL-mIIL)RC+5V

&

+V“1CC”

&

R1

R2

RC RCIOL UOL

A B C

T1

T2

当UOL=UOLmax 时:

R3

F

RCTm5in=

VCC–UOLmax IOL-mIIL

Uon—开门电平 (输出低电平的最大值≤ 0.4V )

理想化

UOH uo

UT —阈值电压(门槛电平)

UOL

UT ui

UT=1.4V

三、门电路级联: 前一个器件的输出就是后一个 器件的输入,后一个是前一个的负 载,两者要相互影响。

“1” 1 “0” IOL

+5V

T4“0” T5 IOL

1

II L

+5V Rb1