MAX293CWE中文资料

MAX2990中文资料

传感器控制和数据采集 电力线传输语音设备

Key Specifications: Powerline Networking Devices

Part Features

Number

Security Features

Smalles

t

Budgetary

Availabl Oper. Interf EV Package e Pckg. Temp.

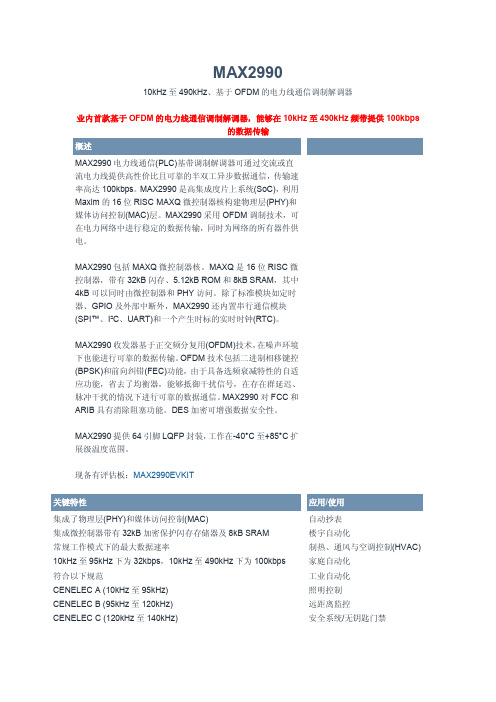

MAX2990

10kHz 至 490kHz、基于 OFDM 的电力线通信调制解调器

业内首款基于 OFDM 的电力线通信调制解调器,能够在 10kHz 至 490kHz 频带提供 100kbps 的数据传输

概述

MAX2990 电力线通信(PLC)基带调制解调器可通过交流或直 流电力线提供高性价比且可靠的半双工异步数据通信,传输速 率高达 100kbps。MAX2990 是高集成度片上系统(SoC),利用 Maxim 的 16 位 RISC MAXQ 微控制器核构建物理层(PHY)和 媒体访问控制(MAC)层。MAX2990 采用 OFDM 调制技术,可 在电力网络中进行稳定的数据传输,同时为网络的所有器件供 电。

Yes LQFP/64

Compliant to

Serial

Managemen

FCC,

UART

t

CENELEC,

148.8

-40 to $8.50 @1k

+85

ARIB

Data Rate Up

to 100Kbps

OFDM-Based

PHY

查看所有 Powerline Networking Devices (5)

Pricing Notes:

This pricing is BUDGETARY, for comparing similar parts. Prices are in U.S. dollars and subject to change. Quantity pricing may vary substantially and international prices may differ due to local duties, taxes, fees, and exchange rates. For volume-specific prices and delivery, please see the price and availability page or contact an authorized distributor.

MAX213CAI-T中文资料

General DescriptionThe MAX200–MAX211/MAX213 transceivers are designed for RS-232 and V.28 communication inter-faces where ±12V supplies are not available. On-board charge pumps convert the +5V input to the ±10V need-ed for RS-232 output levels. The MAX201 and MAX209operate from +5V and +12V, and contain a +12V to -12V charge-pump voltage converter.The MAX200–MAX211/MAX213 drivers and receivers meet all EIA/TIA-232E and CCITT V.28 specifications at a data rate of 20kbps. The drivers maintain the ±5V EIA/TIA-232E output signal levels at data rates in excess of 120kbps when loaded in accordance with the EIA/TIA-232E specification.The 5µW shutdown mode of the MAX200, MAX205,MAX206, and MAX211 conserves energy in battery-powered systems. The MAX213 has an active-low shut-down and an active-high receiver enable control. Two receivers of the MAX213 are active, allowing ring indica-tor (RI) to be monitored easily using only 75µW power.The MAX211 and MAX213 are available in a 28-pin wide small-outline (SO) package and a 28-pin shrink small-outline (SSOP) package, which occupies only 40% of the area of the SO. The MAX207 is now avail-able in a 24-pin SO package and a 24-pin SSOP. The MAX203 and MAX205 use no external components,and are recommended for applications with limited circuit board space.ApplicationsComputersLaptops, Palmtops, Notebooks Battery-Powered Equipment Hand-Held Equipment Next-Generation Device Features ♦For Low-Cost Applications:MAX221E: ±15kV ESD-Protected, +5V, 1µA, Single RS-232 Transceiver with AutoShutdown™♦For Low-Voltage and Space-Constrained Applications:MAX3222E/MAX3232E/MAX3237E/MAX3241E/MAX3246E: ±15kV ESD-Protected, Down to 10nA,+3.0V to +5.5V, Up to 1Mbps, True RS-232Transceivers (MAX3246E Available in UCSP™Package)♦For Space-Constrained Applications:MAX3228E/MAX3229E: ±15kV ESD-Protected,+2.5V to +5.5V, RS-232 Transceivers in UCSP ♦For Low-Voltage or Data Cable Applications:MAX3380E/MAX3381E: +2.35V TO +5.5V, 1µA,2Tx/2Rx RS-232 Transceivers with ±15kV ESD-Protected I/O and Logic Pins ♦For Low-Power Applications:MAX3224E–MAX3227E/MAX3244E/MAX3245E:±15kV ESD-Protected, 1µA, 1Mbps, +3.0V to+5.5V, RS-232 Transceivers with AutoShutdown Plus™MAX200–MAX211/MAX213+5V , RS-232 Transceivers with 0.1µF External Capacitors ________________________________________________________________Maxim Integrated Products 119-0065; Rev 6; 10/03For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Ordering Information appears at end of data sheetAutoShutdown, AutoShutdown Plus, and UCSP are trademarks of Maxim Integrated Products, Inc.MAX200–MAX211/MAX213+5V , RS-232 Transceiverswith 0.1µF External Capacitors______________________________________________________________________________________19Ordering Information*Contact factory for dice specifications.M A X 200–M A X 211/M A X 213+5V , RS-232 Transceiverswith 0.1µF External Capacitors Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.20____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2003 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

MAX232中文资料,MAX232CPE,MAX232EPE,MAX232ECPE,规格书,MAXIM代理商,datasheet,PDF

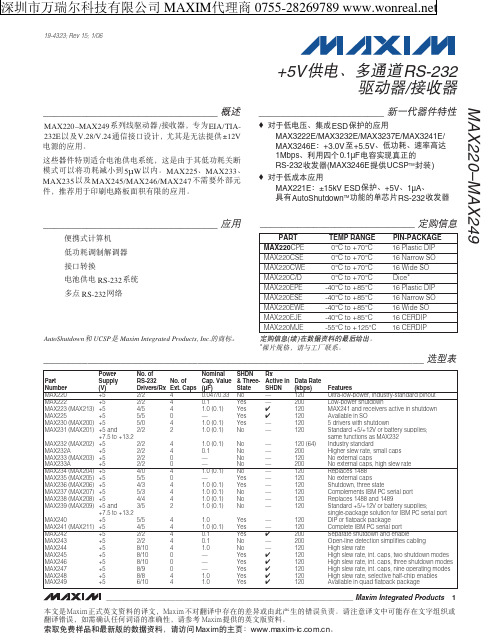

19-4323; Rev 15; 13;5V ޥ٫Ăۂ لRS-232 ഝڑಹ/ेฏಹ

________________________________ ݣะ

MAX220–MAX249࿅઼ഝڑಹ /ेฏಹLjከཛྷEIA/TIA232EჾࣆV.28/V.24ဳेਊහࣜLjᅐದกྐۨ໗ ޥ±12V ٫ᆚوᄮᅋă

ሦဗಹऔ໎Ӽคࠩ٫֠ޥ٫࿅༇Ljሦกᅑᅢದّڱߔࠞޢ ன৹ჾटࠞޢऋဏ ف5μW ჾăMAX225ĂMAX233Ă MAX235 ჾࣆ MAX245/MAX246/MAX247 ԥၖე༶ԩᆐ औLj༚ऌᅋᅢᄩฺ٫ଁғஎࢵᅘوᄮᅋă

1.0 (0.1) 0.1 — — 1.0 (0.1) — 1.0 (0.1) 1.0 (0.1) 1.0 (0.1) 1.0 (0.1)

1.0 1.0 (0.1) 0.1 0.1 1.0 — — — 1.0 1.0

SHDN & ThreeState No Yes Yes Yes Yes No

No No No No No Yes Yes No No No

_____________________________________________________________________ ၭျӹ

Part Number MAX220 MAX222 MAX223 (MAX213) MAX225 MAX230 (MAX200) MAX231 (MAX201)

MAX232 (MAX202) MAX232A MAX233 (MAX203) MAX233A MAX234 (MAX204) MAX235 (MAX205) MAX236 (MAX206) MAX237 (MAX207) MAX238 (MAX208) MAX239 (MAX209)

MAX1239MEEE中文资料

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

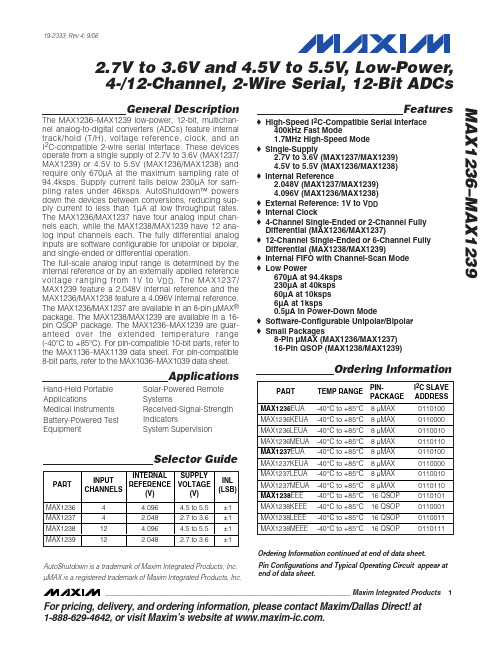

MAX1236–MAX1239

♦ ♦

Applications

Hand-Held Portable Applications Medical Instruments Battery-Powered Test Equipment Solar-Powered Remote Systems Received-Signal-Strength Indicators System Supervision

________________________________________________________________ Maxim Integrated Products

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim’s website at .

MAX195中文资料

MAX195BCWE MAX195ACDE MAX195BC/D MAX195BEPE MAX195BEWE MAX195AEDE MAX195AMDE MAX195BMDE

* Dice are specified at TA = +25°C, DC parameters only. ** Contact factory for availability and processing to MIL-STD-883.

Σ

CALIBRATION DACs SAR 2 CLK SCLK CONV BP/UP/SHDN CS RESET 3 9 1 8 10 CONTROL LOGIC

COMPARATOR

4 6 11 16 14 15

VDDD DGND VSSD VDDA AGND VSSA

MAX195

13 AIN 12 REF 11 VSSD 10 RESET 9 CONV

DYNAMIC PERFORMANCE (fs = 85kHz, bipolar range AIN = -5V to +5V, 1kHz) (Note 1) Signal-to-Noise plus Distortion Ratio (Note 2) Total Harmonic Distortion (up to the 5th harmonic) (Note 2) Peak Spurious Noise (Note 2) Conversion Time Clock Frequency (Notes 3, 4) Serial Clock Frequency tCONV fCLK fSCLK SINAD THD TA = +25°C TA = +25°C TA = +25°C 16 (tCLK) 9.4 1.7 5 87 90 -97 -90 -90 dB dB dB µs MHz MHz

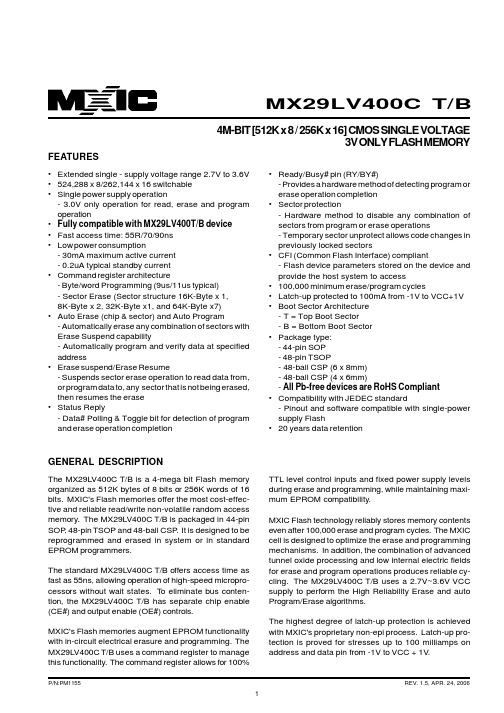

MX29LV400CTXEI-55R中文资料

MX29LV400C T/B4M-BIT [512K x 8 / 256K x 16] CMOS SINGLE VOLTAGE3V ONLY FLASH MEMORY•Ready/Busy# pin (RY/BY#)- Provides a hardware method of detecting program or erase operation completion •Sector protection- Hardware method to disable any combination of sectors from program or erase operations- Temporary sector unprotect allows code changes in previously locked sectors•CFI (Common Flash Interface) compliant- Flash device parameters stored on the device and provide the host system to access•100,000 minimum erase/program cycles•Latch-up protected to 100mA from -1V to VCC+1V •Boot Sector Architecture - T = Top Boot Sector - B = Bottom Boot Sector •Package type:- 44-pin SOP - 48-pin TSOP- 48-ball CSP (6 x 8mm)- 48-ball CSP (4 x 6mm)- All Pb-free devices are RoHS Compliant •Compatibility with JEDEC standard- Pinout and software compatible with single-power supply Flash•20 years data retentionFEATURES•Extended single - supply voltage range 2.7V to 3.6V •524,288 x 8/262,144 x 16 switchable •Single power supply operation- 3.0V only operation for read, erase and program operation•Fully compatible with MX29LV400T/B device •Fast access time: 55R/70/90ns •Low power consumption- 30mA maximum active current - 0.2uA typical standby current •Command register architecture- Byte/word Programming (9us/11us typical)- Sector Erase (Sector structure 16K-Byte x 1,8K-Byte x 2, 32K-Byte x1, and 64K-Byte x7)•Auto Erase (chip & sector) and Auto Program- Automatically erase any combination of sectors with Erase Suspend capability- Automatically program and verify data at specified address•Erase suspend/Erase Resume- Suspends sector erase operation to read data from,or program data to, any sector that is not being erased,then resumes the erase •Status Reply- Data# Polling & Toggle bit for detection of program and erase operation completionGENERAL DESCRIPTIONThe MX29LV400C T/B is a 4-mega bit Flash memory organized as 512K bytes of 8 bits or 256K words of 16bits. MXIC's Flash memories offer the most cost-effec-tive and reliable read/write non-volatile random access memory. The MX29LV400C T/B is packaged in 44-pin SOP , 48-pin TSOP and 48-ball CSP . It is designed to be reprogrammed and erased in system or in standard EPROM programmers.The standard MX29LV400C T/B offers access time as fast as 55ns, allowing operation of high-speed micropro-cessors without wait states. To eliminate bus conten-tion, the MX29LV400C T/B has separate chip enable (CE#) and output enable (OE#) controls.MXIC's Flash memories augment EPROM functionality with in-circuit electrical erasure and programming. The MX29LV400C T/B uses a command register to manage this functionality. The command register allows for 100%TTL level control inputs and fixed power supply levels during erase and programming, while maintaining maxi-mum EPROM compatibility.MXIC Flash technology reliably stores memory contents even after 100,000 erase and program cycles. The MXIC cell is designed to optimize the erase and programming mechanisms. In addition, the combination of advanced tunnel oxide processing and low internal electric fields for erase and program operations produces reliable cy-cling. The MX29LV400C T/B uses a 2.7V~3.6V VCC supply to perform the High Reliability Erase and auto Program/Erase algorithms.The highest degree of latch-up protection is achieved with MXIC's proprietary non-epi process. Latch-up pro-tection is proved for stresses up to 100 milliamps on address and data pin from -1V to VCC + 1V .MX29LV400C T/BPIN CONFIGURATIONS 44 SOP(500 mil)PIN DESCRIPTIONSYMBOL PIN NAMEA0~A17Address InputQ0~Q14Data Input/OutputQ15/A-1Q15 (Word mode)/LSB addr(Byte mode) CE#Chip Enable InputWE#Write Enable InputBYTE#Word/Byte Selection inputRESET#Hardware Reset Pin/Sector ProtectUnlockOE#Output Enable InputRY/BY#Ready/Busy OutputVCC Power Supply Pin (2.7V~3.6V)GND Ground PinNC Pin Not Connected Internally48 TSOP (Standard Type) (12mm x 20mm)A15A14A13A12A11A10A9A8NCNCWE# RESET#NCNC RY/BY#NCA17A7A6A5A4A3A2A1123456789101112131415161718192021222324A16BYTE#GNDQ15/A-1Q7Q14Q6Q13Q5Q12Q4VCCQ11Q3Q10Q2Q9Q1Q8Q0OE#GNDCE#A0484746454443424140393837363534333231302928272625MX29LV400C T/B2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 2244 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23NC RY/BY#A17A7A6A5A4A3A2A1A0CE#GNDOE#Q0Q8Q1Q9Q2Q10Q3Q11RESET#WE#A8A9A10A11A12A13A14A15A16BYTE#GNDQ15/A-1Q7Q14Q6Q13Q5Q12Q4VCCMX29LV4CT/BMX29LV400C T/BMX29LV400C T/BBLOCK STRUCTURETable 1: MX29LV400CT SECTOR ARCHITECTURE Note: Byte mode:address range A17:A-1, word mode:address range A17:A0.Sector Sector SizeAddress range Sector AddressByte Mode Word ModeByte Mode (x8)Word Mode (x16)A17A16A15A14A13A12SA064Kbytes 32Kwords 00000-0FFFF 00000-07FFF 000X X X SA164Kbytes 32Kwords 10000-1FFFF 08000-0FFFF 001X X X SA264Kbytes 32Kwords 20000-2FFFF 10000-17FFF 010X X X SA364Kbytes 32Kwords 30000-3FFFF 18000-1FFFF 011X X X SA464Kbytes 32Kwords 40000-4FFFF 20000-27FFF 100X X X SA564Kbytes 32Kwords 50000-5FFFF 28000-2FFFF 101X X X SA664Kbytes 32Kwords 60000-6FFFF 30000-37FFF 110X X X SA732Kbytes 16Kwords 70000-77FFF 38000-3BFFF 1110X X SA88Kbytes 4Kwords 78000-79FFF 3C000-3CFFF 111100SA98Kbytes 4Kwords 7A000-7BFFF 3D000-3DFFF 111101SA1016Kbytes8Kwords7C000-7FFFF3E000-3FFFF11111XSector Sector SizeAddress range Sector AddressByte Mode Word ModeByte Mode (x8)Word Mode (x16)A17A16A15A14A13A12SA016Kbytes 8Kwords 00000-03FFF 00000-01FFF 00000X SA18Kbytes 4Kwords 04000-05FFF 02000-02FFF 000010SA28Kbytes 4Kwords 06000-07FFF 03000-03FFF 000011SA332Kbytes 16Kwords 08000-0FFFF 04000-07FFF 0001X X SA464Kbytes 32Kwords 10000-1FFFF 08000-0FFFF 001X X X SA564Kbytes 32Kwords 20000-2FFFF 10000-17FFF 010X X X SA664Kbytes 32Kwords 30000-3FFFF 18000-1FFFF 011X X X SA764Kbytes 32Kwords 40000-4FFFF 20000-27FFF 100X X X SA864Kbytes 32Kwords 50000-5FFFF 28000-2FFFF 101X X X SA964Kbytes 32Kwords 60000-6FFFF 30000-37FFF 110X X X SA1064Kbytes32Kwords70000-7FFFF38000-3FFFF111XXXTable 2: MX29LV400CB SECTOR ARCHITECTURE Note: Byte mode:address range A17:A-1, word mode:address range A17:A0.MX29LV400C T/BBLOCK DIAGRAMCONTROL INPUT LOGICPROGRAM/ERASE HIGH VOLTAGEWRITE STATE MACHINE (WSM)STATE REGISTERFLASH ARRAYX-DECODERADDRESS LATCHAND BUFFERY -PASS GATEY -DECODERARRAY SOURCE HVCOMMAND DATADECODERCOMMAND DATA LATCHI/O BUFFERPGM DATA HVPROGRAM DATA LATCHSENSE AMPLIFIERQ0-Q15/A-1A0-A17CE#OE#WE#RESET#MX29LV400C T/BAUTOMATIC PROGRAMMINGThe MX29L V400C T/B is byte programmable using the Automatic Programming algorithm. The Automatic Pro-gramming algorithm makes the external system do not need to have time out sequence nor to verify the data programmed. The typical chip programming time at room temperature of the MX29LV400C T/B is less than 10 seconds.AUTOMATIC CHIP ERASEThe entire chip is bulk erased using 10 ms erase pulses according to MXIC's Automatic Chip Erase algorithm. T ypical erasure at room temperature is accomplished in less than 4 second. The Automatic Erase algorithm au-tomatically programs the entire array prior to electrical erase. The timing and verification of electrical erase are controlled internally within the device.AUTOMATIC SECTOR ERASEThe MX29L V400C T/B is sector(s) erasable using MXIC's Auto Sector Erase algorithm. The Automatic Sector Erase algorithm automatically programs the specified sector(s) prior to electrical erase. The timing and verifi-cation of electrical erase are controlled internally within the device. An erase operation can erase one sector, multiple sectors, or the entire device.AUTOMATIC PROGRAMMING ALGORITHMMXIC's Automatic Programming algorithm requires the user to only write program set-up commands (including 2 unlock write cycle and A0H) and a program command (program data and address). The device automatically times the programming pulse width, provides the pro-gram verification, and counts the number of sequences.A status bit similar to Data# Polling and a status bit toggling between consecutive read cycles, provide feed-back to the user as to the status of the programming operation. Refer to write operation status, table7, for more information on these status bits.AUTOMATIC ERASE ALGORITHMMXIC's Automatic Erase algorithm requires the user to write commands to the command register using stan-dard microprocessor write timings. The device will auto-matically pre-program and verify the entire array. Then the device automatically times the erase pulse width, provides the erase verification, and counts the number of sequences. A status bit toggling between consecutive read cycles provides feedback to the user as to the sta-tus of the erasing operation.Register contents serve as inputs to an internal state-machine which controls the erase and programming cir-cuitry. During write cycles, the command register inter-nally latches address and data needed for the program-ming and erase operations. During a system write cycle, addresses are latched on the falling edge, and data are latched on the rising edge of WE# or CE#, whichever happens first.MXIC's Flash technology combines years of EPROM experience to produce the highest levels of quality, reli-ability, and cost effectiveness. The MX29LV400C T/B electrically erases all bits simultaneously using Fowler-Nordheim tunneling. The bytes are programmed by us-ing the EPROM programming mechanism of hot elec-tron injection.During a program cycle, the state-machine will control the program sequences and command register will not respond to any command set. During a Sector Erase cycle, the command register will only respond to Erase Suspend command. After Erase Suspend is completed, the device stays in read mode. After the state machine has completed its task, it will allow the command regis-ter to respond to its full command set.AUTOMATIC SELECTThe automatic select mode provides manufacturer and device identification, and sector protection verification, through identifier codes output on Q7~Q0. This mode is mainly adapted for programming equipment on the de-vice to be programmed with its programming algorithm. When programming by high voltage method, automatic select mode requires VID (11.5V to 12.5V) on address pin A9 and other address pin A6, A1 as referring to T able 3. In addition, to access the automatic select codes in-system, the host can issue the automatic select com-mand through the command register without requiring VID, as shown in table4.To verify whether or not sector being protected, the sec-tor address must appear on the appropriate highest orderMX29LV400C T/BTABLE 3. MX29LV400C T/B AUTO SELECT MODE OPERATIONNOTE:SA=Sector Address, X=Don't Care, L=Logic Low, H=Logic HighA17A11A8A5DescriptionMode CE#OE#WE#RE- | |A9 |A6 |A1A0Q15~Q0SET#A12A10A7A2Manufacture LLHHXX VID XLXLLC2HCodeRead Device ID Word L L H H X X VID X L X L H 22B9H Silicon (T op Boot Block)Byte L L H H X X VID X L X L H XXB9H IDDevice ID (Bottom Word L L H H X X VID X L X L H 22BAH Boot Block)ByteL L H H X X VID X L X L H XXBAH XX01H Sector Protection LLHHSAX VID XLXHL(protected)VerificationXX00H (unprotected)address bit (see T able 1 and T able 2). The rest of address bits, as shown in table3, are don't care. Once all neces-sary bits have been set as required, the programming equipment may read the corresponding identifier code on Q7~Q0.MX29LV400C T/BTABLE 4. MX29LV400C T/B COMMAND DEFINITIONSFirst Bus Second Bus Third Bus Fourth Bus Fifth Bus Sixth Bus Command Bus Cycle Cycle Cycle Cycle Cycle CycleCycle Addr Data Addr Data Addr Data Addr Data Addr Data Addr Data Reset 1XXXH F0HRead1RA RDRead Silicon ID Word4555H AAH2AAH55H555H90H ADI DDIByte4AAAH AAH555H55H AAAH90H ADI DDISector Protect Word4555H AAH2AAH55H555H90H(SA)XX00HVerify x02H XX01HByte4AAAH AAH555H55H AAAH90H(SA)00Hx04H01HProgram Word4555H AAH2AAH55H555H A0H PA PDByte4AAAH AAH555H55H AAAH A0H PA PDChip Erase Word6555H AAH2AAH55H555H80H555H AAH2AAH55H555H10H Byte6AAAH AAH555H55H AAAH80H AAAH AAH555H55H AAAH10H Sector Erase Word6555H AAH2AAH55H555H80H555H AAH2AAH55H SA30H Byte6AAAH AAH555H55H AAAH80H AAAH AAH555H55H SA30H Sector Erase Suspend1XXXH B0HSector Erase Resume1XXXH30HCFI Query Word155H98Byte1AAH98Note:1.ADI = Address of Device identifier; A1=0, A0 = 0 for manufacturer code,A1=0, A0 = 1 for device code. A2-A17=do not care.(Refer to table 3)DDI = Data of Device identifier : C2H for manufacture code, B9H/BAH (x8) and 22B9H/22BAH (x16) for device code.X = X can be VIL or VIHRA=Address of memory location to be read.RD=Data to be read at location RA.2.P A = Address of memory location to be programmed.PD = Data to be programmed at location P A.SA = Address of the sector to be erased.3.The system should generate the following address patterns: 555H or 2AAH to Address A10~A0 in word mode/AAAH or555H to Address A10~A-1 in byte mode.Address bit A11~A17=X=Don't care for all address commands except for Program Address (PA) and SectorAddress (SA). Write Sequence may be initiated with A11~A17 in either state.4.For Sector Protect Verify operation: If read out data is 01H, it means the sector has been protected. If read out data is 00H, itmeans the sector is still not being protected.5.Any number of CFI data read cycle are permitted.MX29LV400C T/BADDRESSQ8~Q15DESCRIPTIONCE#OE#WE#RE- A17A10A9A8A6A5A1A0Q0~Q7BYTE BYTE SET#A11A7A2=VIH=VILReadLLHHAINDoutDout Q8~Q14=High ZQ15=A-1Write L H L H AIN DIN(3)DIN Q8~Q14=High ZQ15=A-1ResetX X X L X High Z High Z High Z Temporary sector unlock X X X VID AIN DIN DIN High Z Output Disable L H H H X High Z High Z High Z StandbyVcc ±XXVcc ±XHigh ZHigh ZHigh Z0.3V0.3VSector Protect L H L VID SA X X X L X H L DIN X X Chip Unprotect L H L VID X XXXH X H L DIN X X Sector Protection VerifyLLHHSAX VID XLXHLCODE(5)XXTABLE 5. MX29L V400C T/B BUS OPERATIONNOTES:1. Manufacturer and device codes may also be accessed via a command register write sequence. Refer to T able 4.2. VID is the Silicon-ID-Read high voltage, 11.5V to 12.5V .3. Refer to T able 4 for valid Data-In during a write operation.4. X can be VIL or VIH.5. Code=00H/XX00H means unprotected.Code=01H/XX01H means protected.6.A17~A12=Sector address for sector protect.7.The sector protect and chip unprotect functions may also be implemented via programming equipment.sequences. Note that the Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Sector Erase operation is in progress.COMMAND DEFINITIONSDevice operations are selected by writing specific ad-dress and data sequences into the command register.Writing incorrect address and data values or writing them in the improper sequence will reset the device to the read mode. Table 4 defines the valid register commandMX29LV400C T/BREQUIREMENTS FOR READING ARRAY DATATo read array data from the outputs, the system must drive the CE# and OE# pins to VIL. CE# is the power control and selects the device. OE# is the output control and gates array data to the output pins. WE# should re-main at VIH.The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory con-tent occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid address on the device address inputs produce valid data on the de-vice data outputs. The device remains enabled for read access until the command register contents are altered. WRITE COMMANDS/COMMAND SEQUENCEST o program data to the device or erase sectors of memory , the system must drive WE# and CE# to VIL, and OE# to VIH.An erase operation can erase one sector, multiple sec-tors , or the entire device. Table indicates the address space that each sector occupies. A "sector address" consists of the address bits required to uniquely select a sector. The "Writing specific address and data commands or sequences into the command register initiates device operations. Table 1 defines the valid register command sequences. Writing incorrect address and data values or writing them in the improper sequence resets the device to reading array data. Section has details on erasing a sector or the entire chip, or suspending/resuming the erase operation.After the system writes the autoselect command se-quence, the device enters the autoselect mode. The sys-tem can then read autoselect codes from the internal reg-ister (which is separate from the memory array) on Q7-Q0. Standard read cycle timings apply in this mode. Re-fer to the Autoselect Mode and Autoselect Command Sequence section for more information.ICC2 in the DC Characteristics table represents the ac-tive current specification for the write mode. The "AC Characteristics" section contains timing specification table and timing diagrams for write operations.STANDBY MODEWhen using both pins of CE# and RESET#, the device enter CMOS Standby with both pins held at Vcc ± 0.3V. If CE# and RESET# are held at VIH, but not within the range of VCC ± 0.3V, the device will still be in the standby mode, but the standby current will be larger. During Auto Algorithm operation, Vcc active current (Icc2) is required even CE# = "H" until the operation is completed. The device can be read with standard access time (tCE) from either of these standby modes, before it is ready to read data.OUTPUT DISABLEWith the OE# input at a logic high level (VIH), output from the devices are disabled. This will cause the output pins to be in a high impedance state.RESET# OPERATIONThe RESET# pin provides a hardware method of reset-ting the device to reading array data. When the RESET# pin is driven low for at least a period of tRP, the device immediately terminates any operation in progress, tristates all output pins, and ignores all read/write com-mands for the duration of the RESET# pulse. The device also resets the internal state machine to reading array data. The operation that was interrupted should be reinitiated once the device is ready to accept another command sequence, to ensure data integrityCurrent is reduced for the duration of the RESET# pulse. When RESET# is held at VSS±0.3V, the device draws CMOS standby current (ICC4). If RESET# is held at VIL but not within VSS±0.3V, the standby current will be greater.The RESET# pin may be tied to system reset circuitry.A system reset would that also reset the Flash memory, enabling the system to read the boot-up firm-ware from the Flash memory.If RESET# is asserted during a program or erase opera-tion, the RY/BY# pin remains a "0" (busy) until the inter-nal reset operation is complete, which requires a time of tREADY (during Embedded Algorithms). The system can thus monitor RY/BY# to determine whether the reset op-eration is complete. If RESET# is asserted when a pro-MX29LV400C T/Bgram or erase operation is completed within a time of tREADY (not during Embedded Algorithms). The system can read data tRH after the RESET# pin returns to VIH. Refer to the AC Characteristics tables for RESET# pa-rameters and to Figure 24 for the timing diagram.READ/RESET COMMANDThe read or reset operation is initiated by writing the read/ reset command sequence into the command register. Microprocessor read cycles retrieve array data. The de-vice remains enabled for reads until the command regis-ter contents are altered.If program-fail or erase-fail happen, the write of F0H will reset the device to abort the operation. A valid com-mand must then be written to place the device in the desired state.SILICON-ID READ COMMANDFlash memories are intended for use in applications where the local CPU alters memory contents. As such, manu-facturer and device codes must be accessible while the device resides in the target system. PROM program-mers typically access signature codes by raising A9 to a high voltage (VID). However, multiplexing high voltage onto address lines is not generally desired system de-sign practice.The MX29LV400C T/B contains a Silicon-ID-Read op-eration to supple traditional PROM programming meth-odology. The operation is initiated by writing the read silicon ID command sequence into the command regis-ter. Following the command write, a read cycle with A1=VIL, A0=VIL retrieves the manufacturer code of C2H/ 00C2H. A read cycle with A1=VIL, A0=VIH returns the device code of B9H/22B9H for MX29LV400CT, BAH/ 22BAH for MX29LV400CB.SET-UP AUTOMATIC CHIP/SECTOR ERASE COM-MANDSChip erase is a six-bus cycle operation. There are two "unlock" write cycles. These are followed by writing the "set-up" command 80H. T wo more "unlock" write cycles are then followed by the chip erase command 10H or sector erase command 30H.The Automatic Chip Erase does not require the device to be entirely pre-programmed prior to executing the Auto-matic Chip Erase. Upon executing the Automatic Chip Erase, the device will automatically program and verify the entire memory for an all-zero data pattern. When the device is automatically verified to contain an all-zero pat-tern, a self-timed chip erase and verify begin. The erase and verify operations are completed when the data on Q7 is "1" at which time the device returns to the Read mode. The system is not required to provide any control or timing during these operations.When using the Automatic Chip Erase algorithm, note that the erase automatically terminates when adequate erase margin has been achieved for the memory array (no erase verification command is required).If the Erase operation was unsuccessful, the data on Q5 is "1"(see Table 7), indicating the erase operation ex-ceed internal timing limit.The automatic erase begins on the rising edge of the last WE# or CE# pulse, whichever happens first in the com-mand sequence and terminates when the data on Q7 is "1" at which time the device returns to the Read mode, or the data on Q6 stops toggling for two consecutive read cycles at which time the device returns to the Read mode.MX29LV400C T/BPins A0A1Q15~Q8Q7Q6Q5Q4Q3Q2Q1Q0Code(Hex)Manufacture code Word VIL VIL00H1100001000C2HByte VIL VIL X11000010C2H Device code Word VIH VIL22H1011100122B9Hfor MX29LV400CT Byte VIH VIL X10111001B9HDevice code Word VIH VIL22H1011101022BAHfor MX29LV400CB Byte VIH VIL X10111010BAHSector Protection X VIH X0000000101H (Protected) Verification X VIH X0000000000H (Unprotected) TABLE 6. EXPANDED SILICON ID CODEREADING ARRA Y DATAThe device is automatically set to reading array data after device power-up. No commands are required to re-trieve data. The device is also ready to read array data after completing an Automatic Program or Automatic Erase algorithm.After the device accepts an Erase Suspend command, the device enters the Erase Suspend mode. The sys-tem can read array data using the standard read tim-ings, except that if it reads at an address within erase-suspended sectors, the device outputs status data. Af-ter completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exception. See "Erase Suspend/Erase Resume Commands" for more infor-mation on this mode. The system must issue the reset command to re-en-able the device for reading array data if Q5 goes high, or while in the autoselect mode. See the "Reset Command" section, next.RESET COMMANDWriting the reset command to the device resets the de-vice to reading array data. Address bits are don't care for this command.The reset command may be written between the se-quence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ignores reset commands until the operation is complete.The reset command may be written between the se-quence cycles in a program command sequence be-fore programming begins. This resets the device to reading array data (also applies to programming in Erase Sus-pend mode). Once programming begins, however, the device ignores reset commands until the operation is complete.The reset command may be written between the se-quence cycles in an SILICON ID READ command se-quence. Once in the SILICON ID READ mode, the reset command must be written to return to reading array data (also applies to SILICON ID READ during Erase Sus-pend).If Q5 goes high during a program or erase operation, writ-ing the reset command returns the device to read-ing array data (also applies during Erase Suspend).MX29LV400C T/Berase margin has been achieved for the memory array (no erase verification command is required). Sector erase is a six-bus cycle operation. There are two "un-lock" write cycles. These are followed by writing the set-up command 80H. Two more "unlock" write cycles are then followed by the sector erase command 30H. The sector address is latched on the falling edge of WE# or CE#, whichever happens later, while the command (data)is latched on the rising edge of WE# or CE#, whichever happens first. Sector addresses selected are loaded into internal register on the sixth falling edge of WE# or CE#, whichever happens later. Each successive sector load cycle started by the falling edge of WE# or CE#,whichever happens later must begin within 50us from the rising edge of the preceding WE# or CE#, whichever happens first. Otherwise, the loading period ends and internal auto sector erase cycle starts. (Monitor Q3 to determine if the sector erase timer window is still open,see section Q3, Sector Erase Timer.) Any command other than Sector Erase(30H) or Erase Suspend(B0H) during the time-out period resets the device to read mode.SECTOR ERASE COMMANDSThe Automatic Sector Erase does not require the de-vice to be entirely pre-programmed prior to executing the Automatic Sector Erase Set-up command and Au-tomatic Sector Erase command. Upon executing the Automatic Sector Erase command, the device will auto-matically program and verify the sector(s) memory for an all-zero data pattern. The system is not required to provide any control or timing during these operations.When the sector(s) is automatically verified to contain an all-zero pattern, a self-timed sector erase and verify begin. The erase and verify operations are complete when either the data on Q7 is "1" at which time the de-vice returns to the Read mode, or the data on Q6 stops toggling for two consecutive read cycles at which time the device returns to the Read mode. The system is not required to provide any control or timing during these operations.When using the Automatic sector Erase algorithm, note that the erase automatically terminates when adequateStatusQ7Q6Q5Q3Q2RY/(Note1)(Note2)BY#Byte Program in Auto Program Algorithm Q7#Toggle 0N/A No 0Toggle Auto Erase Algorithm0Toggle 01Toggle0Erase Suspend Read1No 0N/A Toggle1(Erase Suspended Sector)Toggle In ProgressErase Suspended ModeErase Suspend ReadData Data Data Data Data 1(Non-Erase Suspended Sector)Erase Suspend ProgramQ7#Toggle 0N/A N/A 0Byte Program in Auto Program AlgorithmQ7#Toggle 1N/A No 0Toggle ExceededTime Limits Auto Erase Algorithm0Toggle 11Toggle 0Erase Suspend ProgramQ7#Toggle1N/AN/ATable 7. Write Operation StatusNote:1.Q7 and Q2 require a valid address when reading status information. Refer to the appropriate subsection for further details.2.Q5 switches to '1' when an Auto Program or Auto Erase operation has exceeded the maximum timing limits.See "Q5:Exceeded Timing Limits " for more information.。

MAX629ESA中文资料

1

For free samples & the latest literature: , or phone 1-800-998-8800

元器件交易网

28V, Low-Power, High-Voltage, Boost or Inverting DC-DC Converter MAX629

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

元器件交易网

19-1219; Rev 1; 6/97

ANUAL N KIT M IO T A U EVAL BLE AVAILA

28V, Low-Power, High-Voltage, Boost or Inverting DC-DC Converter

____________________________Features

___________________________________________________Typical Operating Circuit

MAX3232中文资料zhuanzai

MAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容________________________________________________________________Maxim Integrated Products119-0273; Rev 7; 1/07MegaBaud和UCSP是Maxim Integrated Products, Inc.的商标。

本页已使用福昕阅读器进行编辑。

M A X 3222/M A X 3232/M A X 3237/M A X 32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Note 1:V+ and V- can have a maximum magnitude of 7V, but their absolute difference cannot exceed 13V.V CC ...........................................................................-0.3V to +6V V+ (Note 1)...............................................................-0.3V to +7V V- (Note 1)................................................................+0.3V to -7V V+ + V- (Note 1)...................................................................+13V Input VoltagesT_IN, SHDN , EN ...................................................-0.3V to +6V MBAUD...................................................-0.3V to (V CC + 0.3V)R_IN.................................................................................±25V Output VoltagesT_OUT...........................................................................±13.2V R_OUT....................................................-0.3V to (V CC + 0.3V)Short-Circuit DurationT_OUT....................................................................ContinuousContinuous Power Dissipation (T A = +70°C)16-Pin TSSOP (derate 6.7mW/°C above +70°C).............533mW 16-Pin Narrow SO (derate 8.70mW/°C above +70°C)....696mW 16-Pin Wide SO (derate 9.52mW/°C above +70°C)........762mW 16-Pin Plastic DIP (derate 10.53mW/°C above +70°C)...842mW 18-Pin SO (derate 9.52mW/°C above +70°C)..............762mW 18-Pin Plastic DIP (derate 11.11mW/°C above +70°C)..889mW 20-Pin SSOP (derate 7.00mW/°C above +70°C).........559mW 20-Pin TSSOP (derate 8.0mW/°C above +70°C).............640mW 28-Pin TSSOP (derate 8.7mW/°C above +70°C).............696mW 28-Pin SSOP (derate 9.52mW/°C above +70°C).........762mW 28-Pin SO (derate 12.50mW/°C above +70°C).....................1W Operating Temperature RangesMAX32_ _C_ _.....................................................0°C to +70°C MAX32_ _E_ _ .................................................-40°C to +85°C Storage Temperature Range.............................-65°C to +150°C Lead Temperature (soldering, 10s).................................+300°CMAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容_______________________________________________________________________________________3TIMING CHARACTERISTICS—MAX3222/MAX3232/MAX3241(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)ELECTRICAL CHARACTERISTICS (continued)(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)M A X 3222/M A X 3232/M A X 3237/M A X 32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容4________________________________________________________________________________________________________________________________________________________________典型工作特性(V CC = +3.3V, 235kbps data rate, 0.1µF capacitors, all transmitters loaded with 3k Ω, T A = +25°C, unless otherwise noted.)-6-5-4-3-2-101234560MAX3222/MAX3232TRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )20003000100040005000246810121416182022150MAX3222/MAX3232SLEW RATEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E (V /µs )20003000100040005000510152025303540MAX3222/MAX3232SUPPLY CURRENT vs. LOAD CAPACITANCEWHEN TRANSMITTING DATALOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )20003000100040005000TIMING CHARACTERISTICS—MAX3237(V CC = +3.0V to +5.5V, C1–C4 = 0.1µF (Note 2), T A = T MIN to T MAX , unless otherwise noted. Typical values are at T A = +25°C.)Note 2:MAX3222/MAX3232/MAX3241: C1–C4 = 0.1µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.MAX3237: C1–C4 = 0.1µF tested at 3.3V ±5%; C1–C4 = 0.22µF tested at 3.3V ±10%; C1 = 0.047µF, C2–C4 = 0.33µF tested at 5.0V ±10%.Note 3:Transmitter input hysteresis is typically 250mV.MAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容_______________________________________________________________________________________5-7.5-5.0-2.502.55.07.50MAX3241TRANSMITTER OUTPUT VOLTAGEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )2000300010004000500046810121416182022240MAX3241SLEW RATEvs. LOAD CAPACITANCELOAD CAPACITANCE (pF)S L E W R A T E (V /µs )20003000100040005000510152025303545400MAX3241SUPPLY CURRENT vs. LOADCAPACITANCE WHEN TRANSMITTING DATALOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )20003000100040005000-7.5-5.0-2.502.55.07.50MAX3237TRANSMITTER OUTPUT VOLTAGE vs. LOAD CAPACITANCE (MBAUD = GND)LOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )200030001000400050000102030504060700MAX3237SLEW RATE vs. LOAD CAPACITANCE(MBAUD = V CC )LOAD CAPACITANCE (pF)S L E W R A T E (V /µs )500100015002000-7.5-5.0-2.502.55.07.50MAX3237TRANSMITTER OUTPUT VOLTAGE vs. LOAD CAPACITANCE (MBAUD = V CC )LOAD CAPACITANCE (pF)T R A N S M I T T E R O U T P U T V O L T A G E (V )5001000150020001020304050600MAX3237SUPPLY CURRENT vs.LOAD CAPACITANCE (MBAUD = GND)LOAD CAPACITANCE (pF)S U P P L Y C U R R E N T (m A )200030001000400050000246810120MAX3237SLEW RATE vs. LOAD CAPACITANCE(MBAUD = GND)LOAD CAPACITANCE (pF)S L E W R A T E (V /µs )2000300010004000500010302040506070MAX3237SKEW vs. LOAD CAPACITANCE(t PLH - t PHL )LOAD CAPACITANCE (pF)1000150050020002500____________________________________________________________________典型工作特性(续)(V CC = +3.3V, 235kbps data rate, 0.1µF capacitors, all transmitters loaded with 3k Ω, T A = +25°C, unless otherwise noted.)M A X 3222/M A X 3232/M A X 3237/M A X 32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容6_________________________________________________________________________________________________________________________________________________________________引脚说明MAX3222/MAX3232/MAX3237/MAX32413.0V至5.5V、低功耗、1Mbps、真RS-232收发器,使用四只0.1µF外部电容_______________________________________________________________________________________7_______________________________详细说明双电荷泵电压转换器MAX3222/MAX3232/MAX3237/MAX3241的内部电源由两路稳压型电荷泵组成,只要输入电压(V CC )在3.0V至5.5V范围以内,即可提供+5.5V (倍压电荷泵)和-5.5V (反相电荷泵)输出电压。