DSP串行通信系统设计与实现

dsp课件

DSP的特点

DSP具有高效性

由于DSP采用数字信号处理器 进行信号处理,因此其处理效 率高,能够实现高速实时信号

处理。

DSP具有高精度

数字信号处理器可以实现对信 号的高精度处理,避免了模拟 信号处理中可能出现的误差和 失真。

快速傅里叶变换(FFT)

01

FFT是一种高效计算离散傅里叶变换(DFT)及其逆变换的算法

。

数字滤波器设计

02

数字滤波器是一种用于信号处理的算法,可以实现对信号的滤

波、去噪等功能。

数字信号处理(DSP)算法

03

DSP算法包括多种数字信号处理方法,如频域分析、时域分析

、功率谱分析等。

CHAPTER 04

DSP课件

目 录

• DSP概述 • DSP硬件平台 • DSP软件编程 • DSP在信号处理中的应用 • DSP的优化与扩展 • DSP的发展趋势与未来展望

CHAPTER 01

DSP概述

DSP的定义

数字信号处理(DSP)是一门涉及信号处理、算法设计、系统实现等领域的学科 。它主要研究如何利用数字信号处理器(DSP)对数字信号进行采集、变换、滤 波、估值、压缩等处理,以满足人们在不同领域的需求。

DSP扩展板

内存扩展板

用于扩展DSP的内存容量,提高数据处理能力。

数字IO扩展板

用于扩展DSP的数字输入输出接口,实现与外部设备的通信。

音频视频接口扩展板

用于扩展DSP的音频视频接口,实现音频视频数据的采集和输出。

DSP与其他设备的连接

DSP的串行通信及在数字电压调节器的应用

器业 内最受欢迎 的处理器。其 工作原理 为 : g  ̄ D S P # 1 部 程序设 计处理后 。 又 以数 字信号 转为模拟 信号控 制外

围 电路 的 过 程 。

【 关键词】 D S P ; 电压调 节器 ; P I D; 电机

【 中图分类号】F 4 0 7 . 6

【 文献标识码】 A

理论前 沿 2 0 1 3 年 第3 期

D S P 的串行通信及在数字 电压调节器 的应用

高 飞

( 绥化学院 电气工 程学 院 , 黑龙江 绥化 1 5 2 0 6 1 )

【 摘

要】 D S P 是个数 字信号处理 器, 其作 用是在 日常 生活 中处理各种 图像 、 各 种音频 的处理 器 , 是数 字处理

( 一) D S P 实现 的 内部 算法 比较 这 些算法 的工作原 理如 下图所示 。其 工作原 理

电平 。

主要 特点 :单5 V电源 工作 ; L i n B i C MO S T M工艺 为 当输 入值 与设 定值产 生偏 差后 。再经过 比例调 节

技术 ;  ̄ 3 0 V 输 入电平 ;低 电源 电流 :典 型值 是8 mA 器 、微分 调节 器和 积分调节 器调 节后去驱 动被控 器

( 二) M A X简介

MA X 是连 接D S P 和电脑工作 的轿梁 , D S P 输 出信 号 电压 为3 — 5 伏, 电脑 周边 工 作 电压 为 1 5 V, 因此 要

图2 一 l 系统 框 图

想 它 们正 常 通信 , 就 得做 电压 转 换 , 接 一个 MA X .

该器 件 符合T I A / E I A 一 2 3 2 一 F 标准 ,每一个 接 收器 将 T I A / E I A 一 2 3 2 一 F 电平 转换成5 一 V T I I / C MO S 电平 。每

F2812DSP的最小系统设计

} 3.3 异步串行通信测试程序 void scib_init(void) { ScibRegs.SCIFFTX.all=0xE040;//允许接收,使 //能FIFO,没有FIFO中断,清除TXFIFINT ScibRegs.SCIFFRX.all=0x2021;//使能FIFO接 //收,清除RXFFIN ScibRegs.SCIFFCT.all=0x0000;//禁止波特率校 //验 ScibRegs.SCICCR.all=0x0007;//1个停止位,无 //校验,禁止自测试,空闲地址模式,字长8位 ScibRegs.SCICTL1.all=0x0003; //复位 ScibRegs.SCICTL2.all=0x0003; ScibRegs.SCIHBAUD=0x0001; //设定波特率 ScibRegs.SCILBAUD=0x00E7; //为 9600bps ScibRegs.SCICTL1.all=0x0023; //退出RESET } interrupt void scibRxFifoIsr(void) { recveddata=ScibRegs.SCIRXBUF.all;//从缓冲区 //接收数据 recveddata&=0xFF; //接收数据高8位清零 if(recveddata=='a') //如果接收到的数据为‘a’ { Light=0xFFFE; StartCpuTimer0();//开定时器,流水灯工作 } ScibRegs.SCIFFRX.bit.RXFFOVRCLR=1; ScibRegs.SCIFFRX.bit.RXFFINTCLR=

《 DSP及其在控制中的应用》课程 报告

题目: F2812DSP的最小系统设计

院 系: 航天学院 学 科: 控制科学与工程

基于DSP的PC104总线多功能串行通信卡设计

s f r n amut fn t n lsr l oot e o l . ci a e a mmu iainc r a e n dgtls n lpo e sr( P).T ee p r n wa iu o i c nct ad b sd o ii i a rc so DS o a g h x e me t i

基础软件 的设计与调试. 实验证明 , 采用 T 3 0 2 1 S MS2 F8 2D P能够实现异步串行 通信 、 同步串行通信、 A C N通信 3 种不 同协议 的串行数据接收与发送 . 通过 P 14总线驱动双 口 R M方式 可以方便地嵌入 P 1 总线计算机 , C0 A C0 4 实现多形式 串行通信 功能的扩展.

s o d t a h y t m a c o l h s ra o td t e evn n r n miso c odig t h e r tc lmo e . h we h tt e s se c n a c mp i e ilp r a ar c ii g a d ta s s in a c r n o t r ep oo o d s s

关键词 : 数字信号处理器 ; 串行通信 ;C 0 P 14总线 ; 口 R M 双 A

中图分类号 :K 6 T 23 文献标 识码 : A 文章编 号:0 9— 7 X(00 0 —0 3 0 10 6 1 2 1 ) 2 0 4— 4

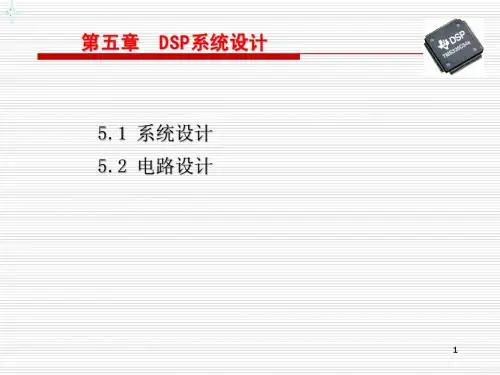

第五章 DSP系统设计

随着大规模集成芯片和可编程逻辑芯片的发展,使硬

件原理设计的难度得以降低,但它依然是DSP系统集成 中关键的一步。原理图设计的成功与否是DSP系统能否

正常工作的最重要的一个因素。

16/39

第五章

DSP系统设计

5.1 系统设计— DSP系统硬件设计

第四步:PCB设计

PCB图的设计要求DSP系统的设计人员既要熟悉系

流之间留有一定余量,因为峰值电流会更大,余量至少

是20%。 现有的电源模块分AC/DC型和DC/DC型。DSP设计中常用 DC/DC型。 DC/DC型中又分开关型和线性低压降型(LDO)。开关型效

率高,但体积大、纹波大。线性LDO型体积小巧,但效率

低,其效率相当于输出电压和输入电压之比,例如5V转 1.8V的效率仅32%,只适用于电流较小的场合。

的电流消耗。 以AD6P21060/ADSP 21062为例,其进行FFT运算时,需 要的电源电流最大,这一峰值电流约是700 mA,但这是 在最“坏”情况下,真正的电流消耗比这小很多。

19/39

第五章

DSP系统设计

5.2 电路设计— 电源设计

因此在设计电源时,必须考虑在电源电流和实际需用电

出现问题时,一般采用修改软件的方法,如果软件修改

无法解决问题,则必须调整硬件,这时问题就严重了。

18/39

第五章

DSP系统设计

5.2 电路设计— 电源设计

DSP使用的电源是数字电源,这些电源必须满足一定要 求,一般要求纹波不超过10%;还应准确估算出DSP及

其外围器件的功耗。DSP数据手册给出了各种情况下DSP

电路设计时有必要采用多层印刷板,一般建议其中 一层是地层。优点:减少干扰;布线时省去了大量 器件管脚接地的工作量。注意:现在DSP等元件广泛 采用表贴封装,在器件布线时,将尽可能多的网络

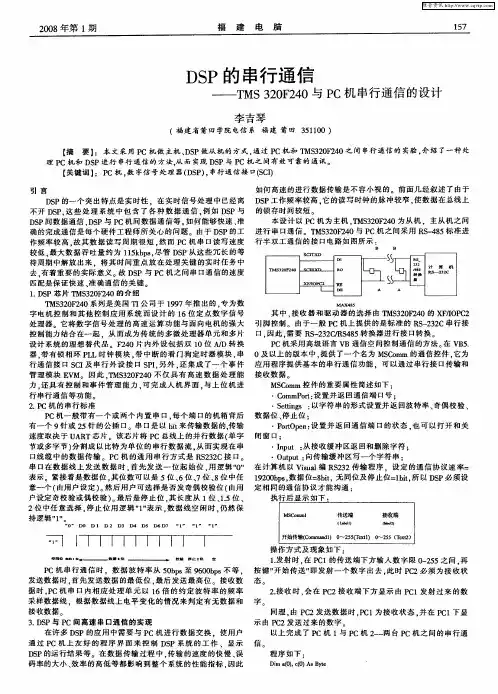

DSP的串行通信——TMS 320F240与PC机串行通信的设计

行 半 双 工 通 信 的 接 口电 路如 图所 示 :

T 3 0 2 0系列 是 美 国 1 公 司 于 1 9 MS 2 F 4 1 9 7年 推 出 的 . 为 数 专 字 电机 控 制 和 其 他 控 制 应 用 系 统 而 设 计 的 1 6位 定 点 数 字 信 号

维普资讯

20 0 8年第 1 期

福

建 电

脑

17 5

D P的 串行通 信 S

T 2 F 4 MS3 0 2 0与 P C机 串行通信 的设计

李吉琴

(福 建 省 莆 田 学 院 电信 系 福 建 莆 田 3 10 ) 5 10

【 摘 要 】 本 文 采 用 P 机 做 主 机 、 S : C D P做 从 机 的 方 式 , 过 P 通 C机 和 T 3 0 2 0之 间 串行 通 信 的 实 验 , 绍 了一 种 处 MS 2 F 4 介 理P C机 和 D P进 行 串行 通 信 的 方 法. 而 实现 D P与 P S 从 S C机 之 间有 效 可靠 的 通 讯 。

【 关键词】 C机 , 字信号 处理器( S ) 串行通信接 口(C ) :P 数 DP , SI

Байду номын сангаас引 言

D P的一 个 突 出 特 点 是 实 时 性 .在 实 时 信 号 处 理 中 已经 离 S 不 开 D P 这 些 处 理 系 统 中包 含 了 各 种 数 据 通 信 , 如 D P与 S. 例 S D P问 数 据通 信 . S S D P与 P C机 问 数 据 通 信 等 。 何 能 够 快 速 、 如 准 确 的完 成 通 信 是 每个 硬件 工程 师 所 关 心 的 问题 。 由于 D P的 工 S 作频 率 较 高 。 其 数 据 读 写 周 期 很 短 。 而 P 故 然 C机 串 E读 写 速 度 l 较低 . 大 数 据 吞 吐 量 约 为 15 b s尽 管 D P从 这些 冗 长 的 等 最 1k p , S 待周 期 中 解 放 出来 .将 其 时 间重 点 放 在 处 理 关 键 的实 时 任 务 中 去. 有着 重 要 的实 际 意 义 。 D P与 P 故 S C机 之 间 串 E通 信 的速 度 l 匹配 是 保 证 快 速 、 确 通 信 的 关 键 。 准

基于DSP的串行通信接口设计

测 试 测 量 技 术

基 于 DS 的 串行 通 信 接 口设 计 P

D esgn i o ̄Se i l C ortnuni aton nt f ce B a e On SP ra rr c i I er a s d D

郑 争 兵 ( 西 理 工 学 院 电信 工 程 系 , 西 汉 中 7 3 0 陕 陕 2 0 3)

61 是 T 46 I公

司 C 00系列 60 中推 出的一 款

高 速 定 点 DS P

O X 1 O

X O

禁 止 时 钟 停 止 模 式 。 时 钟 使 能 为 非 SP 模 式 I 无 延 迟 的 低 电 平 无 效 状 态 。 Mc BSP在 CL X 的 上 升 沿 发 送 数 据 . CL K 在 KX 的 下 降 沿 接 收 数 据

Ar c e I 1 03 U l D:O -01 ( 0 8) -0 3 3 07 2 0 07 01 -0

1引言

TM ¥3 0C 2

钟信 号 C IK的极 2具体的控制寄存器 的配置和相应 的工 LC I 1  ̄[ , 作方 式如表 1 所示 。

CL TP CL KS KXP 时 钟配 置

Abs r c : e pa rito c d de o t a t Th pe r du e SPI n mo f McB as n TIs co an MS3 0 4 6 An h n t e h r wa e it r e ci ut SP b ed o ’ mp y T 2 C6 1 d t e h a d r n ef ac r i c bewe n T t e MS3 0C6 6 n 2 41 a d MAX 1 esgn d 311 E i d i e W i h s t t e DSP BI h / OS a wo k p ovd y CCS. h e l a in o e ilG m ̄ u f me r r i ed b r t e r a i t fs r O z o a —

基于DSP+FPGA的UART设计与实现

基于DSP+FPGA的UART设计与实现摘要:UART作为RS232协议的控制接口得到广泛的应用,将UART功能集成在DSP和FPGA芯片组成的系统中,可使整个系统更为灵活、紧凑,减小电路体积,提高系统的可靠性和稳定性。

本文提出了一种基于DSP和FPGA 系统的UART 实现方法。

关键词:通用异步收发器;DSP;FPGA1 引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,通常称作UART)是一种串行异步收发协议,应用十分广泛。

UART可以和各种标准串行接口,如RS232、RS485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART 由专用芯片来实现,但专用芯片引脚较多,内含许多辅助功能,在实际使用时往往只需要用到UART 的基本功能,使用专用芯片会造成资源浪费和成本提高[1]。

在DSP和FPGA组成的系统中,利用DSP芯片完成UART数据收发控制,FPGA完成UART数据具体的收发时序,二者利用EMIF接口配合,即可实现UART通信功能。

这样设计可以大大减少电路体积、简化电路,也提高了系统的灵活性,使整个系统更加紧凑、稳定且可靠。

2 UART原理UART是一种串行数据总线,用于全双工异步通信。

工作原理是将数据的二进制位按位进行传输。

基本的UART 只需要两条信号线(收、发)和一条地线就可以完成数据的互通,接收和发送互不干扰。

在UART通信协议中,信号线上的状态位高电平代表“1”,低电平代表“0”。

图1 UART数据传输格式UART 数据传输格式如图1所示,一个字符由起始位、数据位、校验位和停止位组成(其中校验位可选)。

其中各位的含义如下:起始位:一位逻辑“0”信号,表示字符数据传输的开始;数据位:5~8位可选的逻辑“0”或“1”。

数据位的发送顺序为:先发送数据的最低位,最后发送最高位;校验位:包括奇校验或偶校验两种方式,即数据位加上这一位后,使得“1”的位数应为偶数(偶校验)或奇数(奇校验)。

基于DSP实验系统的串口通信

课程设计报告( 2014 -- 2015年度第二学期)课程名称:DSP课程设计题目:基于DSP实验系统的串口通信院系:电子与通信工程系班级:电子学号:学生姓名:指导教师:设计周数: 2成绩:日期:2015 年7月16日一、课程设计的目的与要求1.设计方案:通过TMS320C5509A的串口与电脑进行通信,利用串口调试助手发送数据,由DSP接收到,DSP读到收到数据进行下一步的让四位LED灯亮,实现数据的通信,并在lcd12864上显示发送的数据,还有显示拨码开关的数值。

2.设计指标:电脑只能发送0~15,因为读出数据的时候比较方便解码,比如发送4就可以直接给LED直接赋值,让第三个灯亮,也就是一般的二进制转换。

二、设计正文1.设计思路(系统组成介绍)串口模块:TL16C550 是一个标准的串口接口芯片,它的控制寄存器基地址为0x400200,寄存器占用TMS320VC5509 的8 个地址单元。

串口中断与TMS320VC5509 的INT0 连接。

用户可以使用TMS320VC5509 的中断0 响应串口中断。

TL16C550 有11 个寄存器,这11 个寄存器是通过TMS320VC5509 的3 个地址线(A3~A1)和线路控制寄存器中的DLAB 位对它们进行寻址的。

板上加上16C550、Max232 和驱动电路。

驱动电路主要完成将输出的0-3.3V 电平转换成异步串口的工作电平,转换电平的工作由MAX232 芯片完成,但由于它是5V 器件,所以它同DSP 间的信号线必须有电平转换,此板采用的是74LVC245。

实验箱上的液晶模块采用的型号是TJDM12864MTJDM12864M 是一款带中文字库的图形点阵模块,由动态驱动方式驱动128×64 点阵显示。

低功耗,供应电电压范围宽。

内含多功能的指令集,操作简易。

采用COB 工艺制作,结构稳固,使用寿命长。

特性:1.提供 8 位,4 位及串行接口可选2.64×16 位字符显示 RAM(DDRAM 最多 16 字符×4 行,LCD 显示范围 16×2 行)3.2M 位中文字型 ROM(CGROM),总共提供 8192 个中文字型(16×16 点阵)4.16K 位半宽字型 ROM(HCGROM),总共提供 126 个西文字型(16×8 点阵)5.64×16 位字符产生 RAM(CGRAM)6.15×16 位总共 240 点的 ICON RAM(ICONRAM)7.自动复位(RESET)功能8.绘图及文字画面混合显示功能9.提供多功能指令:——画面清除(display clear)——游标归位(return home)——显示开/关(display on/off)——游标显示/隐藏(cursor on/off)——字符闪烁(display character blink)——游标移位(cursor shift)——显示移位(display shift)——垂直画面旋转(vertical line scoll)——反白显示(By-line reverse display)——睡眠模式(sleep mode)DSP与LCD的连接:3.软件设计流程:4.在试验箱上模拟实现用随实验箱附带的串口线(两端均为9 孔“D”形插头)连接计算机com1 或com2 插座和ICETEK–VC5509-A 板上标准RS-232 插座,编译、下载、运行。

DSP原理及应用TMS320C54x片内外设及应用实例

应用领域拓展

随着数字信号处理技术的不断发展,DSP的应用领 域也在不断拓展,需要不断探索新的应用场景和市 场需求。

人才培养和生态系统建设

为了推动DSP技术的发展和应用,需要加强 人才培养和生态系统建设,建立完善的开发 环境和工具链。

06

参考文献

参考文献

1

[1] 张雄伟, 杨吉斌. 数字信号处理——原理、算 法与实现[M]. 北京: 清华大学出版社, 2011.

应用场景

在音频处理、信号测量、控制系统 等领域广泛应用。

存储器和I/O引脚

存储器和I/O引脚功能

01

TMS320C54x芯片具有外部存储器和多个I/O引脚,用于扩展外

部存储空间和连接外设。

工作原理

02

通过读写外部存储器实现数据存储,I/O引脚用于输入输出电平

信号。

应用场景

03

在数据存储、外设控制、信号采集等方面具有广泛应用。

FFT在TMS320C54x上的实现

TMS320C54x的硬件结构支持FFT运算,其乘法器和累加器运算单元可以高效地完成 FFT计算。在实现FFT时,需要注意数据的位序和存储方式。

FFT应用实例

通过FFT算法,可以分析语音、图像、雷达等信号的频谱成分,从而实现信号的频域分 析、滤波、调制解调等功能。

TMS320C54x的优势与局限性

• 丰富的外设接口:TMS320C54x系列DSP具有多种外设接口, 如串行通信接口、并行输入输出接口等,方便与外部设备进行 数据交换。

TMS320C54x的优势与局限性

价格较高

由于TMS320C54x系列DSP采用高性能的制程技术和复杂的内 部结构,导致其价格较高,增加了应用成本。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

不高的系统, SP I总线的使用可以简化电路设计、省

掉了很多常规电路中的接口器件、提高了设计的可

靠 性。 该 系 统 利 用 SP I 外 接 数 码 管 驱 动 芯 片

MAX7219, MAX7219芯片的特点是可以利用一个芯

片完成 8位字数据和线数据的驱动, 使得电路紧凑。 该芯片与数码管相连时无需限流电阻, 8位显示的

ZHANG Kun- chan, YANG Jian- hua, DU X in- hu

( College of A utomation, N or thw estern Po ly technical University, X i an 710072, China)

A bstract: A TMS320LF2407A - based serial comm unication system was deve loped to rea lize communications betw een digita l signal processo r ( DSP ) and other contro llers. T his system em ployed an Un iversa l Asynchronous R eceiver T ransm itter ( UART ) m odule and a Seria l P eripheral Interface ( SP I) m odule to connect the DSP to a host PC and a client d isp lay peripheral respectively. Deta iled principle and m ethod for hardw are design w ere introduced; comm un ication program s and relative so ftw are structure w ere g iven. Communication experim ents show ed that the system w as sim ple in c ircu it design and stable and accurate in data transm ission. It has reference value and pract ical benefit to explo it comm un ications of DSP system.

电流可以通过一个外部电阻进行调节, 显示亮度也

可通过程序进行控制。片内具有 BCD 码译码选择,

可以对输入的数据先进行译码再驱动输出, 也可以 将输入的数据直接驱动。

MAX7219内部有 16位移位 寄存器, 所 存储的

数据为 D0~ D15。 D8- D11为寄存器地址, D0~ D7

为数据, D12 ~ D15为不关心位, 片内有 14 个寄存

器, 其中 8个数据寄存器, 寄存与 DIG0- D IG7对应 的显示数据, 地址依次为 1H - 8H, 还有 6 个控制寄

存器, 依次为译码控制寄存器 ( Decode M ode)、显示

亮度寄存器 ( Intensity) 、扫描频率限制寄存器 ( Scan

L im it) 、消隐控制寄存器 ( Shutdown) 、显示测试寄存 器 ( D isp lay T est) 及无操作寄 存器 ( No - Op) , 其地

关键词: 数字信号处理; 串行通信; 外设接口 DO I编码: 10. 3969 / .j issn. 1002- 2279. 2010. 06. 009 中图分类号: TN 911. 72 文献标识码: B 文章编号: 1002- 2279( 2010) 06- 0023- 04

Design and Imp lementation of Serial Communication Based on DSP

CPLD

LA OD D IN SCLK

数码管

图 1 UART 硬件连接框图

2. 2 SP I串行外设接口 SP I( 串行外设接口 ) 是一个高速同步串行 I/O

口, 允许长度可编程的串行位流 ( 1~ 16位 ) 以可编 程的位传输速度移入或移出器件。对于实时性要求

图 2 SP I硬件连接框图

电路 UART 和 SP I中都使用了 CPLD, 一方面可 以对 DSP 的控制信 号、地址和数据线灵活配置, 另 一方面也可以灵活生成 UART 的复位、选通、读写信 号以及 SP I的片选、时钟和数据信号, 从而增强系统

综合上述, 详细介绍了 DSP 与 PC 机如何通过 外接异步收发芯片 TL16C752B 实现 RS232通信和 DSP 如 何 实 现 SP I 通 信。 T I 公 司 的 TM S320LF2407A 型 DSP 微控制器可外接异步收发 芯片 TL16C752B, 通过 RS232接口可以方便地进行 DSP之间或与 PC 机之间的异步通信, 而串行外设 接口 ( SP I) 是 TM S320LF 2407A 自带的一个 高速同 步串行输入 /输出 ( I/O) 端口, 常用于 DSP 控制器和 其它 SP I控制器件的通讯 [ 1] 。

具有 SP I接口的器件, MAX7219具有 SP I接口, 并且

只需 要 3 位 数 据 线 和 控 制 线 来 连 接。 DSP 的 CLOCKOUT / IOPE0、 SP ISIMO / IOPC2 和 SP ICLK /

IOPC4引脚分别通过 CPLD 与 MAX7219的 LOAD、

D IN 和 SCLK 引脚相连接, MAX7219的 DIG0- DIG7

初始化主 要包括系统初始化和串口通信初始 化。其软件主要设计步骤如图 3所示。

开始

禁止所有中断

设置状态寄存器 ST0和 ST1

设置系统控制和 状态寄存器 SCSR 1和 SC SR 2

SP I初始化

U ART 初始化

开中断

图 3 初始化子程序流程图

系统初始化使系统正常进入工作状态, 主要包 括对 TM S320LF2407A 寄存器的初始化, 配置相对应 的 I/O 口为具有 SP I、UART 和外部中断 的特殊功 能, 时钟模式的选择, 波特率的设定, 传输数据长度 的设置等。首先通过初始化 I/O复用控制寄存器配 置 SP ISOM I、SP ICLK 引 脚 为特 殊 功 能 方 式, 设 置 SP ICCR (串行外设接口配置控制寄存器 ) 输出数据 长度为 8 位, 在 SP ICLK 的 下 降 沿 接 收 数 据, 与 MAX7219在上升沿接 收数据相 配合, 通过 SP ICTL (串 行 外 设 接 口 操 作 控 制 寄 存 器 ) 设 置 TM S320LF2407A为主动模式, 通过 SP IBRR( 串行外 设接口操作控制寄存器 )设置 SP I的波特率; 通过系 统初始化配置 X INT 1引脚为特殊功能方式, 设置外 部中断使能。

为了实现 TM S320LF 2407A 与 PC 机的 异步通 信, 该 系 统 采 用 T I 公 司 的 异 步 收 发 芯 片 TL16C752B。该芯片采用 8 位异 步并 行存储 器接 口, 具有 64字节发送 /接收 F IFO, 波特率可编程, 最 高工作波特率可以达到 1. 5M bps( 使用 24MH z晶体 时 ) 或 3M bps( 使用 48MH z振荡 器或 时钟 源时 ) 。 TL16C752B提供 A、B 两个通道, 可独立工作, 由片 选信号选通, 同时还提供两个中断请求信号 INTA、 INTB, 分别用于 A、B 通道向 D SP 申请 中断 [ 3] 。芯 片的每个通道包含 18个寄存器, 通过地址 A0~ A2 及寄存器位对它们寻址。

2 硬件设计

该系统中 DSP 利用异步收发芯片 TL16C752B

作者简介: 张焜鋋 ( 1982- ) , 男, 陕西高陵人, 硕士研究生, 主研方向: 现代检测理论与传感器。 收稿日期: 2010- 01- 14

24

微处理机

2 010 年

接收来自 PC机的数据, 然后通过 SP I口传给数码显 示电路, 以便实时监视数据的可靠性。 2. 1 异步串行接口 ( UART )

第 6期 2010年 12月

微机网络与通 信

微处理机 M ICROPRO CE SSOR S

N o. 6 D ec. , 2010

DSP串行通信系统设计与实现

张焜鋋, 杨建华, 杜新虎

(西北工业大学自动化学院, 西安 710072)

摘 要: 针 对 数 字 信 号 处 理 器 ( DSP ) 与 其 它 控 制 器 的 通 信 需 要, 设 计 了 一 种 基 于 TM S320LF2407A 的串行通信系统。该系统通过串行外设接口 ( SP I) 和通用异步收发器 ( URAT ) 两 个通信模块实现 DSP 与 PC主机和数显外设的串行通信。详细介绍了 DSP 串行通信系统的硬件设 计原理和方法, 给出了系统运行流程和相关的软件构架。通信实验表明, 该系统电路设计简单, 传 输数据稳定准确, 对 DSP系统在通信方面的开发具有一定的参考价值和实际意义。

该模块的硬件框图如图 1所示。图中, 地址线 A0~ A2、数 据线 D0~ D7 分别和 DSP 的 地址总线 A0~ A 2、外部数据线 D0~ D7直接相连, 而选通信 号 CSA /CSB、读写信号 IOR / IOW、复位信号 RESET 以及中断信号 INTA /B 则接入 CPLD 并由 CPLD 处 理。同时 DSP 端的 PS、DS、IS、STRB、R /W 也同时 接入 CPLD 以用于生成控制信号。由于 PC 端串口 采用 RS232 电平 标准, 因 此 UART 之 后需要 连接 MAX3160以完成电平转 换。 TL 16C752B 的数据发 送引脚和数据接收引脚分别与 MAX3160的数据输 入引 脚和 数 据输 出 引 脚连 接。这 里只 使 用 一套 UART 来完成 TL16C752B 和 PC 的通信。数据收、 发采用 中 断 方 式, TL16C752B 的 INTA 引 脚通 过 CPLD 和 TM S320LF2407A 的 外部 中 断 INT 1 相连 接 [ 3] 。