基于FPGA的QPSK调制解调电路设计与实现

基于FPGA的QPSK OFDM调制解调器设计与实现

基于FPGA的QPSK OFDM调制解调器设计与实现OFDM(正交频分多路复用)是一种高效的调制解调技术,常用于无线通信系统中。

本文将介绍基于FPGA的QPSK(四相移键控)OFDM调制解调器的设计与实现。

一、引言OFDM技术在无线通信领域有着广泛的应用,其通过将高速数据流分成多个低速子载波进行传输,有效提高了系统的传输效率和频谱利用率。

而QPSK调制方式在OFDM系统中常被使用,能够传输两个比特的信息。

二、系统设计1. 系统框架基于FPGA的QPSK OFDM调制解调器主要包括信号生成、调制、多载波复用、通道传输、接收、解调等模块。

其中,信号生成模块负责产生待发送的信息信号;调制模块将信息信号进行QPSK调制;多载波复用模块将调制后的信号进行串行-并行转换;通道传输模块将并行数据通过多个子载波进行传输;接收模块接收并处理接收到的信号;解调模块将接收到的信号进行QPSK解调,得到原始信息信号。

2. 信号生成在信号生成模块中,我们可以使用伪随机序列发生器生成随机的数字信号作为待发送的信息源。

这里我们选择使用16位的二进制数字信号。

3. QPSK调制QPSK调制模块将二进制信号映射到复平面上的四个相位,即正弦信号与余弦信号共同构成的星座图。

通过将两个比特的输入分别映射到正弦信号与余弦信号的相位上,得到QPSK调制信号。

4. 多载波复用多载波复用模块将QPSK调制信号进行串行-并行转换,将多个并行的调制信号通过并行数据总线发送到通道传输模块。

5. 通道传输通道传输模块将并行的调制信号通过多个子载波进行传输。

在传输过程中,可能会出现信道衰落、噪声等问题,需要引入信道估计和均衡技术进行处理。

6. 接收与解调接收模块接收到经过信道传输后的信号,并进行信道估计和均衡处理,将接收到的信号进行QPSK解调,得到原始的二进制信息。

三、系统实现本文使用基于FPGA的开发板进行系统的实现。

通过使用硬件描述语言进行电路的设计,将各个模块进行逻辑连接,实现QPSK OFDM 调制解调器的功能。

如何实现一种基于FPGA全数字高码率QPSK调制设计?

如何实现一种基于FPGA全数字高码率QPSK调制设计?1 ** 全数字高码率QPSK调制解调软件设计**1.1 QPSK调制1.1.1 QPSK调制原理1.1.2 QPSK并行调制实现调制(信号)的符号速率达到500Mbps,根据奈奎斯特采样定理,DA的采样频率采用2Gbps。

由于数据速率比较的高,对(FPGA)运算要求太高,因此在设计过程中,采用并行处理的方式,来减轻对FPGA运算的压力。

图1-1为高码率500M QPSK调制实现框图。

其实现的原理为将二进制数据流经过QPSK映射后形成I、Q两路基带信号,在经过8倍成型(滤波器)后,分别与两路正交的数字本振混频后相加输出至(DAC)即可。

图1-1 并行QPSK调制实现框图1.1.2.1 QPSK符号映射QPSK信号的每个码元包含两个比特(信息),可用ab表示。

ab 序列有四种排列,即00,01,10,11。

每种排列对应4种不同的调制相位。

通常各种排列的相位关系按照格雷码进行编码,其符号映射关系如图1-2所示。

图1-2 QPSK映射星座图在实现过程中,将每个符号所包含的两比特二进制信息,分别对应为I、Q两路,先到的信息比特映射为I路,后到的信息比特映射为Q路。

其中二进制0对应正值(逻辑高+1),二进制1对应负值(逻辑低-1)。

图1-3为500Mbps QPSK调制(MATLAB)(仿真)映射星座图,从图中可以看出基带数据严格聚集在[-1,-1],[-1,1],[1,-1],[1,1]四个相位点上。

图1-3 500MbpsQPSK调制MATLAB仿真映射星座图1.1.2.2数字基带成型滤波由于现代无线电(通信)及卫星通信中,频带和功率一般均受限。

一方面,为了有效利用信道,节约频谱资源,需要对发射信号进行带限;另一方面,当矩形脉冲通过带限信道时,脉冲会在时间上扩展,每个符号的脉冲将扩展到相邻符号的码元内,这会造成码间串扰(ISI),并导致接收机在(检测)码元时发生错误的概率增大。

基于FPGA的QPSK解调技术的设计与实现的开题报告

基于FPGA的QPSK解调技术的设计与实现的开题报告一、选题背景及意义随着现代通信技术的发展,频谱资源越来越紧张,为提高频谱利用效率,射频通信系统中使用数字调制技术是一种可有效降低带宽能量占用和提高信道容量的方式。

其中一种常用的数字调制技术是QPSK调制,它可以将两路单极性NRZ数据分别调制在正弦波和余弦波载波上,实现带宽利用率的提高。

在接收端,解调器需要对QPSK调制信号进行还原,提取出原始的信息数据。

因此,本课题选取了基于FPGA的QPSK解调技术的设计与实现作为研究方向,旨在探索一种高效实现数字信号解调的方法,为提高现代通信技术的发展水平做出贡献。

二、研究内容1. 系统总体设计本课题设计的QPSK解调系统包括射频前端的载频同步、时序同步、均衡、解调等模块,还包括数字信号处理相关的滤波器、采样率变换等模块。

通过这些模块的协同作用,将接收到的QPSK调制信号解调还原成原始的数字信号数据流。

2. 载频同步模块该模块负责完成载频的同步,用于去除接收端的时移影响和相位偏差。

常用的载频同步算法有Costas算法、DDS算法、ZT算法等。

3. 时序同步模块该模块用于解决接收数据中时序抖动的问题,采用软判决算法实现。

4. 均衡模块该模块用于抑制信道传输时产生的干扰,提高系统的抗干扰性能。

常用的均衡算法有线性均衡算法、决策反馈均衡算法等。

5. 解调模块该模块用于将QPSK调制信号还原成原始数字信号。

该模块通常包括滤波器、采样率变换器等子模块。

三、研究计划第一年:我们将完成系统的总体设计,并完成载频同步模块和时序同步模块的算法研究和验证。

同时进行硬件平台的搭建和仿真测试。

第二年:我们计划完成均衡模块和解调模块的算法研究和验证,并将这些模块集成到硬件平台上。

在验证完成后,完善系统的功能和性能,并进行实际场景测试。

第三年:在系统的测试和实际应用中不断完善和优化,提高系统的性能和稳定性,并探索将该技术应用到更广泛领域的可能性,为现代通信技术的发展做出更大的贡献。

基于FPGA的QPSK高速数字调制系统的研究与实现

基于FPGA的QPSK高速数字调制系统的研究与实现摘要:介绍了一种基于FPGA的QPSK的高速数字调制系统的实现方案。

先从调制系统的基本框图入手,简要介绍其实现原理及流程;然后着重介绍FPGA功能模块的软件编程、优化及整个系统的性能。

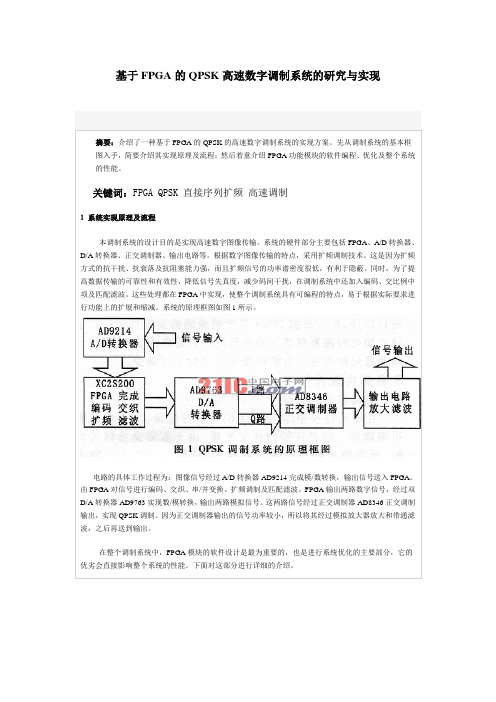

关键词:FPGA QPSK 直接序列扩频高速调制1 系统实现原理及流程本调制系统的设计目的是实现高速数字图像传输。

系统的硬件部分主要包括FPGA、A/D转换器、D/A转换器、正交调制器、输出电路等。

根据数字图像传输的特点,采用扩频调制技术。

这是因为扩频方式的抗干扰、抗衰落及抗阻塞能力强,而且扩频信号的功率谱密度很低,有利于隐蔽。

同时,为了提高数据传输的可靠性和有效性,降低信号失真度,减少码间干扰,在调制系统中还加入编码、交比例中项及匹配滤波。

这些处理都在FPGA中实现,使整个调制系统具有可编程的特点,易于根据实际要求进行功能上的扩展和缩减。

系统的原理框图如图1所示。

电路的具体工作过程为:图像信号经过A/D转换器AD9214完成模/数转换,输出信号送入FPGA。

由FPGA对信号进行编码、交织、串/并变换、扩频调制及匹配滤波。

FPGA输出两路数字信号,经过双D/A转换器AD9763实现数/模转换,输出两路模拟信号。

这两路信号经过正交调制器AD8346正交调制输出,实现QPSK调制。

因为正交调制器输出的信号功率较小,所以将其经过模拟放大器放大和带通滤波,之后再送到输出。

在整个调制系统中,FPGA模块的软件设计是最为重要的,也是进行系统优化的主要部分,它的优劣会直接影响整个系统的性能。

下面对这部分进行详细的介绍。

2 软件部分实现原理FPGA模块的软件设计部分包括以下几个方面:编码、交织、串并变换、扩频、匹配滤波以及复位和时钟。

2.1 编码和交织数字通信中经常使用信道编码加交织模块来提高数据传输的可靠性和有效性。

为了达到一定的增益要求,选择卷积码中纯编码增益为3.01的(1,1,6)码(在大信噪比下),并对其进行增信删余。

QPSK调制解调技术的设计与仿真

摘要本文主要阐述的是QPSK调制与解调电路的设计。

数字调制解调技术在数字通信中占有非常重要的地位。

为了使数字信号在带通信道中传输,必须用数字信号对载波进行调制。

根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制)。

多进制数字调制与二进制相比,其频谱利用率更高,在有限的信道频带内,能够传输高速数据。

数字通信技术与FPGA的结合是现代通信系统发展的一个必然趋势。

多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。

文中介绍了QPSK调制解调的原理,并基于FPGA实现了QPSK调制解调电路。

MUXPLUSⅡ环境下进行编译、综合仿真,验证了设计的正确性。

此外,本方案采用了相位选择法,与常用的调相解调法相比,设计更简单,更适合于FPGA实现,系统的可靠性也更高。

通过对仿真波形的分析可知,该方案很好的实现了QPSK调制与解调功能。

关键词:PSK FPGA QPSK调制解调AbstractThis article mainly deals with the design of QPSK modulation and demodulation circuit. Technology of digital modulation and demodulation plays an important role in digital communication system.In order to transmit digital signal in band-pass channel,digital signal must be used on the carrier modulation..According to the different bands of digital signal that is handled,there are binary and multi-band pared with binary modulation ,multi-band modulation has higher specrum utilization rate,and it could transmit high-speed data in limited-band channel.The combination of digital communication technology and FPGA is a certainly trend of the development of modern communication system.The combination of multi-band modulation and FPGA makes the performance of communication system a rapid increase.The paper introduces the principle of QPSK modulation and demodulation, the circuits are also be realized based on FPGA. The complier and simulation under MAX+PLUSII environment provides the correction of the design..In addition, this design employs phase selection ,compared with the PM demodulation method,phase selection is simpler,more suitable for FPGA implementation,the reliability of the system is higher.The analysis of simulation waveform indicates that the programme achieves QPSK modulation and demodulation functions well.Keywords:PSK FPGA QPSK modulation demodulation目录摘要 (I)ABSTRACT.................................................... I I 前言 (1)1.绪论 (2)1.1QPSK的简介 (2)1.2FPGA和CPLD简介 (2)1.3VHDL简介 (3)1.4MAX+PLUS II简介 (3)2.调制与解调电路的基本设计原理 (4)2.1QPSK调制的电路原理图 (5)2.2QPSK解调的电路原理图 (5)3.QPSK调制与解调电路的设计 (6)3.1调制电路的设计 (6)3.1.1 设计思路 (6)3.1.2 调制电路的程序 (7)3.1.3 调制电路仿真结果 (8)3.2解调电路的设计 (9)3.2.1 设计思路 (9)3.2.2 解调电路的程序 (10)3.2.3 解调电路的仿真结果 (10)3.3仿真分析 (11)3.3.1 BPSK调制解调的实现及其仿真波形 (11)3.3.2 BPSK和QPSK的区别 (16)3.3.3 QPSK仿真波形的分析 (18)4.总结 (20)参考文献 (21)附录 (22)前言现代通信系统要求通信距离远、通信容量大、传输质量好。

毕业设计(论文)-qpsk的fpga实现[管理资料]

![毕业设计(论文)-qpsk的fpga实现[管理资料]](https://img.taocdn.com/s3/m/39dd34b0be1e650e53ea99ca.png)

QPSK的FPGA实现摘要数字调制解调技术在数字通信中占有非常重要的地位, 数字通信技术与FPGA 的结合是现代通信系统发展的一个必然趋势。

QPSK数字调制技术,具有频谱利用率高、频谱特性好、抗干扰性能强、传输速率快等突出特点,在移动通信、卫星通信中具有广泛应用价值,但是基于FPGA的全数字QPSK 调制解调仍在进一步研究发展中。

本文首先叙述了QPSK调制解调技术的工作原理和数字式调制与解调的特点。

其次对QPSK的调制和解调设计展开讨论。

设计包括QPSK的调制、解调两部分,基于对整个设计的要求进行分析及对QPSK实现FPGA进行功能的分解,以此划分成比较小的模块,自下而上设计系统;根据QPSK的原理分别画出QPSK调制、解调的实现框图。

设计中设定每个比特对应特定的载波,并以载波作为比较,实现最后的对应的输出结果。

最后基于VHDL 语言分别完成QPSK的调制与解调,完成系统的设计方案,在MAX+PLUSII 环境下对模块逻辑、时序进行仿真调试的仿真结果表明了该设计的正确性,并综合得出RTL的结构图。

关键词:QPSK,FPGA,调制,解调FPGA IMPLEMENTATION OF QPSKABSTRACTTechnology of digital modulation and demodulation plays an important role in digital communication system and the combination of digital communication technology and FPGA is certainly a digital modulation technique has features of high-spectrum utilization ratio,better spectrum specification, stronger anti-interference performance and faster baud rate and has been applied widely in mobile communication system and satellite communication system.But all-digital QPSK modulation and demodulation based on FPGA is still towards further research and development.At first, this paper describes the principle of QPSK modulation and demodulation technology as well as the characteristics of digital modulation and demodulation. In the following words we mainly provide the discussion combined with the research and design of the QPSK modulation and demodulation .This design has two parts, which are QPSK modulation and demodulation .The analysis on the whole design requirement and the decomposition of QPSK function in FPGA lay the basis for the smaller divided modules. Then we can start up the bottom-up design .Respectively, we draw QPSK modulation and demodulation diagram on the basis of the principle of QPSK. The design supposes each bit corresponds to a specific carrier .To achieve the final result of the corresponding output, we should take carrier as a comparison. In the end, we use VHDL to achieve the QPSK modulation and demodulation. After completing the whole system design, it goes on with simulation on module logic, timing in the MAX+PLUSII environment. The simulation results indicate that the design is correct and comprehensively deduce the RTL's chart.KEY WORDS:QPSK, FPGA, Modulation, Demodulation目录前言 (1)第1章绪论 (1)§设计的依据与意义 (2)§同类产品的概况 (2)第2章数字通信系统 (4)§通信系统的数字化 (4)§数字通信与模拟通信的性能比较 (5)§数字通信系统的基本组成部分 (5)§数字调制技术 (8)§数字调制的方法 (8)§PSK--又称相移键控法 (9)§FSK--又称频移键控法 (9)§ASK--又称幅移键控法 (10)§MASK--又称多进制数字调制法 (10)§QAM--又称正交幅度调制法 (10)§MSK--又称最小移频键控法 (11)§GMSK--又称高斯滤波最小移频键控法 (11)第3章FPGA与VHDL语言介绍 (12)§FPGA介绍 (12)§FPGA的发展历史 (12)§FPGA的基本特点 (13)§FPGA的优点 (14)§VHDL语言介绍 (14)§VHDL语言发展回顾 (14)§VHDL系统设计的特点 (15)§VHDL系统优势 (16)第4章四相移相键控(QPSK) (18)§QPSK概述 (18)§QPSK的特点 (18)§QPSK的原理 (18)§QPSK的调制和解调 (20)§调制 (20)§解调 (22)§QPSK应用 (23)第5章QPSK的FPGA实现 (23)§引言 (23)§QPSK调制电路FPGA实现及仿真: (23)§QPSK解调电路FPGA实现及仿真 (26)结论 (29)参考文献 (30)致谢 (31)附录 (33)前言QPSK是在无线通信中应用比较广泛的一种调制方式,它具有较高的频谱利用率、较强的抗干扰性。

基于fpga的qpsk调制解调的仿真及相关软件设计毕业设计

1.1研究背景

自1897年意大利科学家G.Marconi首次使用无线电波进行信息传输并获得成功后,在一个多世纪的时间中,在飞速发展的计算机和半导体技术的推动下,无线通信的理论和技术不断取得进步,今天,无线移动通信已经发展到大规模商用并逐渐成为人们日常生活不可缺少的重要通信方式之一。

随着数字技术的飞速发展与应用数字信号处理在通信系统中的应用越来越重要。数字信号传输系统分为基带传输系统和频带传输系统。频带传输系统也叫数字调制系统,该系统对基带信号进行调制,使其频谱搬移到适合信道传输的频带上数字调制信号有称为键控信号。在调制的过程中可用键控[1]的方法由基带信号对载频信号的振幅,频率及相位进行调制最基本的方法有三种:正交幅度调制(QAM)、频移键控(FSK)和相移键控(PSK)。

1.2.2FPGA的发展概况

FPGA/CPLD、DSP和CPU被称为未来数字电路系统的3块基石,也是目前硬件设计研究的热点[11]。过去的数字信号处理实现中,大多采用ASIC和DSP,但这类器件都有一定的缺陷。ASIC处理速度快,但开发成本高,而且内部功能不可改变,这样系统的可重构性差;DSP可以通过更改软件来改变其功能,其重构性好,但它的处理速度慢,逐渐跟不上越来越高的信号处理速度的要求字调制解调技术的发展现状

数字信号调制是用基带数字信号控制高频载波,把基带数字信号变换为频带数字信号的过程,数字信号的调制设备包括数字信号处理(编码)单元和调制单元。

图1.1 数字通信调制系统框图

首先将模拟信号数字化,然而数字信号序列进行编码码流是不能或不适合直

作为数字通信技术中重要组成部分的调制解调技术一直是通信领域的热点课题。随着当代通信的飞速发展,通信体制的变化也日新月异,新的数字调制方式不断涌现并且得到实际应用[2]。目前的模拟调制方式有很多种,主要有AM、FM、SSB、DSB、CW等,而数字调制方式的种类更加繁多,如ASK、FSK、MSK、GMSK、PSK、DPSK、QPSK、QAM等。如果产生每一种信号需要一个硬件电路甚至一个模块,那么能产生几种、十几种通信信号的通信机的电路将相当复杂,体积重量将会很大,而且要增加新的调制方式也是十分困难的。在众多调制方式中,四相相移键控(Quadrature Phase Shift Keying,QPSK)信号由于抗干扰能力强而得到了广泛的应用[3],[4],具有较高的频谱利用率和较好的误码性能,并且实现复杂度小,解调理论成熟,广泛应用于数字微波、卫星数字通信系统、有线电视的上行传输、宽带接入与移动通信等领域中[5],并已成为新一代无线接入网物理层和B3G通信中使用的基本调制方式[6]。现场可编程门阵列(Field Programmable Gate Array,FPGA)是20世纪9年代发展起来的大规模可编程逻辑器件,随着电子设计自动化(ElectronDesign Automation EDA)技术和微电子技术的进步,FPGA的时钟延迟可达到ns级,结合其并行工作方式,在超高速、实时测控方面都有着非常广阔的应用前景[7]。FPGA具有高集成度、高可靠性等特点,在电子产品设计中也将得到广泛的应用。FPGA器件的另一特点是可用硬件描述语言VHDL对其进行灵活编程[8],可利用FPGA厂商提供的软件仿真硬件的功能,使硬件设计如同软件设计一样灵活方便,缩短了系统研发周期。基于上述优点,用FPGA实现调制解调电路,不仅降低了产品成本,减小了设备体积,满足了系统的需要,而且比专用芯片具有更大的灵活性和可控性。在资源允许下,还可以实现多路调制。

基于FPGA的QPSK调制器的设计与实现

20 0 8年 l 2月

湖南 冶金 职 业技 术 学院 学 报

Ju a fHu a tl ria rfsin l e h oo yC U g o r lo n nMeal gc l oe s a c n lg o ee n u P o T

V0. No4 1 8 .

率 、 强 的抗干 扰性 、 电路 上 实现也 较 为简单 , 较 在 本 文研 究 了基 于 F G P A的 Q S P K调制 电路 的实现

【a)^万 i相 系统 c

图 1QP SK信 号Q atsI 境 下 的仿 真 结 ur l环 u

内部 的 P L直 接产 生 Ck L l0和 Ck ll两 路 频 率 相

l F G 0 l / : PA I -l 2 3 xl

一 | 4 "/ r4 r

种 : 幅 键 控 (S ) 频 移 键 控 (s )相 移 键 控 振 A K、 FK、 (S ) P K 。根据 所处 理 的基 带信 号 的进 制不 同 , 它们

可 分 为二进 制 和多进 制 调制( 进制 ) M 。多进制 数

O

1

一r 12 /

中图 分 类号 : M7 文 献标 识 码 : 文章 编号 :62 7 1 ( 0)4 0 9 0 T 6 A 17 — 422 8 — 9— 3 0 0

0 引 言

于a b通常是按格 雷码 的规 则排 列的 , 它与 载波 故 相位的对应关 系如表 1 示 ,相 应的 向量关 系如 所

种不 同相位的载波 。按串饼 变换 器的双 比特码元 的不 同 , 逻辑选相 电路输 出相 应相位 的载波 , 虚线

11 四相 绝对移 相键控 ( P K . QS )

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的QPSK调制解调电路设计与实现数字调制信号又称为键控信号,调制过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制,最基本的方法有3种:正交幅度调制(QAM)、频移键控(FSK)、相移键控(PSK).根据所处理的基带信号的进制不同分为二进制和多进制调制(M进制).多进制数字调制与二进制相比,其频谱利用率更高.其中QPSK(即4PSK)是MPSK(多进制相移键控)中应用最广泛的一种调制方式。

1 QPSK简介QPSK信号有00、01、10、11四种状态。

所以,对输入的二进制序列,首先必须分组,每两位码元一组。

然后根据组合情况,用载波的四种相位表征它们。

QPSK信号实际上是两路正交双边带信号, 可由图1所示方法产生。

QPSK信号是两个正交的2PSK信号的合成,所以可仿照2PSK信号的相平解调法,用两个正交的相干载波分别检测A和B两个分量,然后还原成串行二进制数字信号,即可完成QPSK信号的解调,解调过程如图2所示。

图1 QPSK 信号调制原理图图2 QPSK 信号解调原理图2 QPSK 调制电路的FPGA 实现及仿真 2.1基于FPGA 的QPSK 调制电路方框图基带信号通过串/并转换器得到2位并行信号,,四选一开关根据该数据,选择载波对应的相位进行输出,即得到调制信号,调制框图如图3所示。

基带信号clkstart串/并转换四选一开关分 频0°90°180°270°调制信号FPGA图3 QPSK 调制电路框图系统顶层框图如下图中输入信号clk为调制模块时钟,start为调制模块的使能信号,x为基带信号,y是qpsk调制信号的输出端,carrier【3..0】为4种不同相位的载波,其相位非别为0、90、180、270度,锁相环模块用来进行相位调节,用来模拟通信系统中发送时钟与接收时钟的不同步start1为解调模块的使能信号。

y2为解调信号的输出端。

2.2调制电路VHDL程序程序说明信号yy 载波相位载波波形载波符号“00”0°f3“01”90°f2“10”180°f1“11”270°f0library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity PL_MPSK isport(clk :in std_logic; --系统时钟start :in std_logic; --开始调制信号x :in std_logic; --基带信号y :out std_logic;carrier :out std_logic_vector(3 downto 0);xxx :out std_logic_vector(1 downto 0)); --调制信号end PL_MPSK;architecture behav of PL_MPSK issignal q:integer range 0 to 7; --计数器signal ss:std_logic_vector(1 downto 0); --中间寄存器signal yy:std_logic_vector(1 downto 0); --2位并行码寄存器signal xx:std_logic_vector(1 downto 0);signal f:std_logic_vector(3 downto 0); --载波fbeginprocess(clk) --通过对clk分频,得到4种相位;并完成基带信号的串并转换beginif clk'event and clk='1' thenif start='0' thenq<=0;elsif q=0 thenq<=1;f(3)<='1'; f(1)<='0'; xx(1)<=x;yy<=xx;elsif q=2 thenq<=3;f(2)<='0'; f(0)<='1';elsif q=4 thenq<=5;f(3)<='0'; f(1)<='1'; xx(0)<=x;elsif q=6 thenq<=7;f(2)<='1'; f(0)<='0';else q<=q+1;end if;end if;--ss<=yy;xxx<=yy;end process;y<=f(0) when yy="11" elsef(1) when yy="10" elsef(2) when yy="01" elsef(3) when yy="00"; --根据yy寄存器数据,输出对应的载波carrier<=f;end behav;在quartus ii下的仿真结果总体结果如下图所示局部放大图如下3 QPSK解调电路的FPGA实现及仿真3.1 QPSK解调电路方框图当调制为低电平时,译码器1根据记数器输出值,送入加法器相应的数据。

加法器把运算结果送到寄存器,译码器2根据寄存器数据通过译码,输出两位并行信号,该信号再通过并/串转换即可得到解调后的基带信号,调制框图如图4所示。

图4 QPSK解调电路框图3.2解调电路VHDL程序library ieee;use ieee.std_logic_arith.all;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity PL_MPSK2 isport(clk :in std_logic; --系统时钟start :in std_logic; --同步信号x :in std_logic; --调制信号y :out std_logic); --基带信号end PL_MPSK2;architecture behav of PL_MPSK2 issignal q:integer range 0 to 7; --计数器signal xx:std_logic_vector(2 downto 0); --加法器signal yyy:std_logic_vector(1 downto 0); --2位并行基代信号寄存器signal yy:std_logic_vector(2 downto 0); --寄存xx数据beginprocess(clk)beginif clk'event and clk='1' thenif start='0' then q<=0;elsif q=0 thenq<=1;yy<=xx; y<=yyy(0); --把加法计数器的数据送入yy寄存器if x='0' thenxx<="001"; --调制信号x为低电平时,送入加法器的数据“001”elsexx<="000";end if;elsif q=2 then q<=3;if x='0' thenxx<=xx+"001"; --调制信号x为低电平时,送入加法器的数据“001”end if;elsif q=4 then q<=5; y<=yyy(1);if x='0' thenxx<=xx+"010"; --调制信号x为低电平时,送入加法器的数据“010”end if;elsif q=6 then q<=7;if x='0' thenxx<=xx+"011"; --调制信号x为低电平时,送入加法器的数据“011”end if;else q<=q+1;end if;end if;end process;process(yy) --此进程根据yy寄存器里的数据进行译码beginif clk='1' and clk'event thenif yy="101" then yyy<="00"; --yy寄存器“101”对应基带码“00”elsif yy="011" then yyy<="01"; --yy寄存器“011”对应基带码“01”elsif yy="010" then yyy<="10"; --yy寄存器“010”对应基带码“10”elsif yy="100" then yyy<="11"; --yy寄存器“100”对应基带码“11”else yyy<="00";end if;end if;end process;end behav;使用FPGA实现QPSK调制解调电路,多进制数字调制技术与FPGA的结合使得通信系统的性能得到了迅速的提高。

系统联调的全局仿真图如下局部放大图如下所示从仿真图中可以看到基带信号x与解调出的信号y2一致,说明解调成功。