数字逻辑chapter6.1

数字逻辑第六章课件

2. 应用举例

A3 =0时,片Ⅰ工作,片Ⅱ禁止

(1)功能扩展(利用使能端实现)

仿真 扩展位 控制 图3-9 用两片74LS138译码器构成4线—16线译码器 A3 =1时,片Ⅰ禁止,片Ⅱ工作 使能端

(2) 实现组合逻辑函数F(A,B,C)

F ( A, B, C ) mi (i 0 ~ 7)

Ai 0 0 0 0 1 1 1 1 Bi 0 0 1 1 0 0 1 1 Ci-1 0 1 0 1 0 1 0 1 Si 0 1 1 0 1 0 0 1 Ci 0 0 0 1 0 1 1 1

Si Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai ( Bi Ci 1 Bi Ci 1 ) Ai ( Bi Ci 1 Bi Ci 1 ) Ai ( Bi Ci 1 ) Ai ( Bi Ci 1 ) Ai Bi Ci 1

试将8421BCD码转换成余3BCD码 (1)真值表 (2)卡诺图

0 1 2 3 4 5 6 7 8 9 10 8421码 余3码 B3 B2 B1 B0 E3 E2 E 1 E0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 0 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 0 0 1 1 0 1 0 0 1 0 1 1 1 1 0 1 0 1 0 0 0 1 0 1 1 1 0 0 1 1 1 0 0 1 0 1 0

Yi S mi mi ( S 1, i 0,1,2,7)

比较以上两式可知,把3线—8线译码器 74LS138地址输入端(A2A1A0)作为逻辑函数的输 入变量(ABC),译码器的每个输出端Yi都与某一 个最小项mi相对应,加上适当的门电路,就可以利 用译码器实现组合逻辑函数。

数字逻辑知识点报告总结

数字逻辑知识点报告总结1. 数字逻辑的定义数字逻辑是一种以数字为基础的逻辑学科,它研究数字之间的关系和数字系统的运算规律。

在数字逻辑中,数字通常表示为0和1,这两个数字是数字逻辑中的基本元素。

数字逻辑研究的范围包括数制、逻辑运算、逻辑代数、逻辑函数、数字逻辑电路等。

2. 基本概念在数字逻辑中,有几个基本概念是必须要了解的,包括数制、位权、数字编码、二进制加法和减法、二进制码等。

其中,数制是指用来表示数字的一组符号和表示方法,位权是指数字中各个位上的数值和位置的关系,数字编码是把数字用一定的代码表示出来,二进制加法和减法是对二进制数字进行加减运算。

3. 逻辑门逻辑门是数字逻辑的基本构件,它用来实现逻辑运算功能。

常见的逻辑门包括与门、或门、非门、异或门和与非门等。

这些逻辑门可以根据输入信号的不同,输出不同的逻辑运算结果。

逻辑门是数字逻辑电路的核心部件,它可以实现各种逻辑功能。

4. 布尔代数布尔代数是逻辑代数的一种,它是一种用来表示逻辑运算的代数系统。

在布尔代数中,逻辑运算可以用加法、乘法和求反运算来表示,这些运算具有一些特定的性质,比如交换律、结合律、分配律等。

布尔代数是数字逻辑的数学基础,它可以用来描述和分析各种逻辑函数和逻辑运算。

5. 逻辑功能在数字逻辑中,逻辑功能是指逻辑门实现的具体功能。

常见的逻辑功能包括与运算、或运算、非运算、异或运算等。

这些逻辑功能可以根据实际需求进行组合和变换,从而实现复杂的逻辑运算。

6. 数字逻辑电路数字逻辑电路是数字逻辑的物理实现,它由逻辑门和其他逻辑功能部件组成。

数字逻辑电路可以用来实现各种逻辑运算、逻辑函数和逻辑功能,它是数字系统中的核心部件。

7. 存储器存储器是一种用来存储信息的设备,它可以用来保存数字信息、程序信息和数据信息等。

在数字逻辑中,存储器通常是由触发器组成的,它可以存储和传输数字信号。

8. 计数器和触发器计数器是一种用来计数和累加的设备,它可以用来实现各种计数功能和定时功能。

《数字逻辑基础》课件

使用逻辑代数公式对逻辑函数进行化简,通过消去多余的项和简化 表达式来得到最简结果。

卡诺图化简法

使用卡诺图对逻辑函数进行化简,通过填1、圈1、划圈和填0的方 法来得到最简结果。

03

组合逻辑电路

组合逻辑电路的分析

组合逻辑电路的输入和输出

分析组合逻辑电路的输入和输出信号,了解它们之间的关系。

交通信号灯控制系统的设计与实现

交通信号灯简介

交通信号灯是一种用于控制交通流量的电子设备,通常设置在路口或 交叉口处。

设计原理

交通信号灯控制系统的设计基于数字逻辑电路和计算机技术,通过检 测交通流量和车流方向来实现信号灯的自动控制。

实现步骤

首先确定系统架构和功能需求,然后选择合适的元件和芯片,接着进 行电路设计和搭建,最后进行测试和调整。

真值表

通过列出输入和输出信号的所有可能组合,构建组合逻辑电路的真值表,以确定输出信 号与输入信号的逻辑关系。

逻辑表达式

根据真值表,推导出组合逻辑电路的逻辑表达式,表示输入和输出信号之间的逻辑关系 。

组合逻辑电路的设计

确定逻辑功能

根据实际需求,确定所需的逻辑功能,如与、或、非等。

设计逻辑表达式

根据确定的逻辑功能,设计相应的逻辑表达式,用于描述输入和 输出信号之间的逻辑关系。

实现电路

根据逻辑表达式,选择合适的门电路实现组合逻辑电路,并完成 电路的物理设计。

常用组合逻辑电路

01

02

03

04

编码器

将输入信号转换为二进制码的 电路,用于信息处理和控制系

统。

译码器

将二进制码转换为输出信号的 电路,用于数据分配和显示系

统。

多路选择器

数字逻辑第6章1

学习要求:

✓ 掌握门集成电路、器件、电路电气方面的基础知识,以便构建出符合 实际要求的电路和系统。

✓ 掌握门电路延时、触发器定时、时序电路原理 ✓ 掌握PLD方面的原理

2020/7/29

1

第6章 背景知识专题(续)

思考与报告6.1

请查资料,半导体硅材料在性能上遇到了什么瓶颈? 石墨烯材料有何优点? 想想看,你还有什么办法来提高集成电路的集成度? 集成电路中的导电连线是铝线好还是铜线好? 有人说,电路的延时是电路的固有属性,对不对?逻 辑函数有时延吗?

小规模集成电路(SSI) 中规模集成电路(MSI) 大规模集成电路(LSI) 超大规模集成电路(VLSI)

2020/7/29

5

6.1 设计空间(续)

半导体材料

常用的半导体材料的特性参数有:禁带 宽度、电阻率、载流子迁移率(载流子即 半导体中参加导电的电子和空穴)、非平 衡载流子寿命、位错密度。 禁带宽度由半导体的电子态、原子组态 决定,反映组成这种材料的原子中价电 子从束缚状态激发到自由状态所需的能 量。 电阻率、载流子迁移率反映材料的导电 能力。

非反相门

逻辑上的求反是“免费”获得的,而且用少于反相门所需的晶体 管数目来设计非反相门电路是不可能的。

CMOS非反相缓冲器、与门和或门都可由反相器与相应的反相门 连接组成。

2020/7/29

17

6.1 设计空间(续)

CMOS电路的稳态电气特性

根据右图,可定义 小于2.4伏的电压为 CMOS低输入电平,而 大于2.6伏的电压为高 输入电平。

2020/7/29

2

第6章 背景知识专题(续)

思考与报告6.2

2012年诺贝尔物理学奖

数字逻辑第六章

LDB ( Q2 Q1 ) T2

ADD Q2Q1 (电平信号控制)

CLR Q2 Q1 (电平信号控制)

1

2

P172 例6 举例

T 1 T1 T2

T1

2

3

4

5

6

7

8

T2

CLR

LDA LDB ADD

P172 例6 举例

例2

已知ASM图如下,用PLA阵列和一定数量的D触发器实现。

3个状态-----需要2个触发器

S0 S1 S2 S3

函数发生器

4

Ai i = 0,1,2,3

4

Bi

子系统ALU

74LS181功能表

演示_74LS181功能

74LS181

● 二、寄存器堆

寄存器

通用寄存器: 暂存参与ALU运算的数据和结果。4、8、16、32位

专用寄存器: 状态寄存器、指令寄存器、程序计数器

ALU A E A0~3 B E B0~3 双端口寄存器组

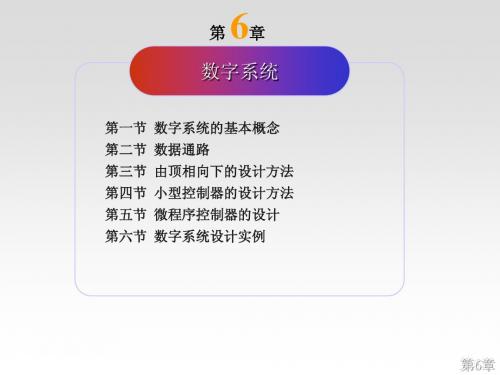

数字系统

要求

最上层系 统设计

划分

若干子系统

划分

若干功能块

From top to down 自上而下

设计控制器 简单的模块

时序机

数字系统的设计方法

概念设计 系统验证 系统设计和描述

系统划分 设计者

功能验证

子系统功能描述

综合 电子系统设计自动化 EDA Electronic Design Automation 芯片 数字系统的设计流程

0

1

X

S2

S3

1 0 P169 例4演示 ASM图举例

1

X

Z=1

例3 同步时序状态机如图所示,其中X1、X2是两个外部输入信号,Z是 输出信号。将时序状态机转换为ASM图。

数字逻辑知识点总结

数字逻辑知识点总结数字逻辑有着相当丰富的知识点,包括逻辑门的基本原理、布尔代数、数字信号的传输与处理、数字电路的设计原理等。

在这篇文章中,我将对数字逻辑的一些重要知识点进行总结,希望能够为初学者提供一些帮助。

1. 逻辑门逻辑门是数字电路中的基本单元,它可以完成各种逻辑运算,并将输入信号转换为输出信号。

常见的逻辑门包括与门、或门、非门、与非门、或非门、异或门等。

每种逻辑门都有其特定的逻辑功能,通过不同的组合可以完成各种逻辑运算。

在数字电路设计中,逻辑门是构建各种复杂逻辑电路的基础。

2. 布尔代数布尔代数是表示逻辑运算的一种代数系统,它将逻辑运算符号化,并进行了各项逻辑规则的代数化处理。

布尔代数是数字逻辑的基础,通过布尔代数可以很方便地表达和推导各种逻辑运算,对于理解数字电路的工作原理非常有帮助。

3. 二进制与十进制的转换在数字逻辑中,我们经常需要进行二进制与十进制的转换。

二进制是计算机中常用的数字表示方法,而十进制则是我们日常生活中常用的数字表示方法。

通过掌握二进制与十进制之间的转换规则,可以方便我们在数字逻辑中进行各种数字运算。

4. 组合逻辑与时序逻辑数字电路可以分为组合逻辑电路与时序逻辑电路。

组合逻辑电路的输出只取决于输入信号的瞬时状态,而时序逻辑电路的输出还受到时钟信号的控制。

理解组合逻辑与时序逻辑的差异对于理解数字电路的工作原理至关重要。

5. 有限状态机有限状态机是数字逻辑中一个重要的概念,它是一种认知和控制系统,具有有限的状态和能够在不同状态之间转移的能力。

有限状态机在数字系统中有着广泛的应用,可以用来设计各种具有状态转移行为的电路或系统。

6. 计数器与寄存器计数器与寄存器是数字逻辑中常用的两种逻辑电路。

计数器用于对计数进行处理,而寄存器则用于存储数据。

理解计数器与寄存器的工作原理和使用方法,对于数字系统的设计和应用具有非常重要的意义。

7. 逻辑电路的设计与分析数字逻辑的一大重点是逻辑电路的设计与分析。

数字逻辑资料

数字逻辑数字逻辑是一种数学分支,关注的是数字之间的逻辑关系及其应用。

在现代科技发展中,数字逻辑在电子电路、计算机科学、通信技术等领域都有着重要的应用。

数字逻辑在数学推理和逻辑运算方面有着广泛的应用,同时也是计算机系统设计的基础。

本文将重点介绍数字逻辑的概念、基本原理和应用。

1. 数字逻辑的基本概念数字逻辑主要研究数字之间的关系和运算规律。

在数字逻辑中,数字可以用二进制、十进制或其他进制表示。

数字逻辑中的基本元素包括逻辑门、布尔代数、真值表等。

逻辑门是数字逻辑中的基本构建块,它们可以实现各种逻辑运算,比如与、或、非等。

布尔代数是数字逻辑的数学基础,通过布尔代数可以描述逻辑运算的规则和性质。

真值表则是描述逻辑门的输入和输出之间关系的表格。

2. 数字逻辑的基本原理数字逻辑的基本原理包括逻辑门的工作原理、布尔代数规则以及逻辑运算的实现方法等。

逻辑门是数字逻辑中的基本组件,常见的逻辑门包括与门、或门、非门等。

这些逻辑门通过组合可以实现更复杂的逻辑功能。

布尔代数提供了逻辑运算的规则,包括与运算、或运算、非运算等。

数字逻辑中的运算实现通常通过逻辑门的组合来实现,不同的逻辑门组合可以实现不同的逻辑功能。

3. 数字逻辑的应用数字逻辑在电子电路、计算机系统、通信技术等领域有着广泛的应用。

在电子电路设计中,数字逻辑可以实现各种逻辑功能,比如加法器、减法器、寄存器、计数器等。

在计算机系统中,数字逻辑用于实现CPU内部的运算逻辑、控制逻辑等。

在通信技术中,数字逻辑用于编码解码、信号处理等方面。

数字逻辑的应用使得现代科技得以发展,推动了信息技术的进步。

4. 结语数字逻辑作为数学和工程领域的交叉学科,对现代科技发展具有重要意义。

通过数字逻辑的研究和应用,可以实现复杂的运算和控制功能,推动科技的发展。

数字逻辑的基本原理和应用广泛存在于我们日常生活和工作中,深入理解数字逻辑将有助于我们更好地理解现代科技并发挥其作用。

以上就是关于数字逻辑的基本概念、基本原理和应用的介绍,希望对读者理解数字逻辑有所帮助。

数字逻辑 知识点总结大全

数字逻辑知识点总结大全数字逻辑是一门研究数字信号在计算机中传输和处理的学科,它涉及到数字电路和逻辑电路的设计、分析和应用。

数字逻辑在计算机科学、电子工程、通信工程等领域都有着广泛的应用。

下面将对数字逻辑的知识点进行详细的总结,包括数字系统、布尔代数、逻辑门、时序逻辑和组合逻辑等内容。

数字系统数字系统是由有限个数的符号和数字组成的一种系统。

在计算机中,使用的数字系统一般为二进制,即由0和1组成。

除了二进制,还有十进制、八进制和十六进制等其他进制系统。

其中,二进制是计算机内部使用的基本进制。

数字系统中的基本概念包括位、字节、字和字长。

位是数字系统中的最小单位,它只有两种状态:0和1。

字节是8位的二进制数,用来表示一个字符或一个字母。

字是由多个字节组成的一个固定长度的数据单元。

而字长是一个数字系统中的字的长度,它决定了一个数字系统中能够表示的最大的数值范围。

布尔代数布尔代数是一种逻辑代数,它用来描述逻辑语句的真假情况。

在布尔代数中,所有逻辑变量的取值只有两种情况:真和假。

布尔代数中的基本运算包括与运算、或运算和非运算。

与运算表示两个逻辑变量同时为真时结果为真,否则为假;或运算表示两个逻辑变量中任意一个为真时结果为真,否则为假;非运算表示逻辑变量的取值取反。

布尔代数中的定理包括分配律、结合律、德摩根定律、消去律等。

这些定理是布尔代数中的基本规则,用于简化布尔表达式,并帮助我们理解逻辑电路的设计和分析。

逻辑门逻辑门是数字电路中的基本组成部分,它用来实现布尔代数中的逻辑运算。

逻辑门一般包括与门、或门、非门、异或门、与非门、或非门等类型。

这些门都有着特定的逻辑功能和真值表。

与门表示与运算,或门表示或运算,非门表示非运算,异或门表示异或运算,与非门表示与非运算,或非门表示或非运算。

这些逻辑门可以组成各种复杂的逻辑电路,包括加法器、减法器、多路选择器、触发器、寄存器等。

时序逻辑时序逻辑是数字逻辑中的一个重要分支,它涉及到数字电路中的时序关系和时序控制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

State Table

A A A B B B B C C C C D D D D

Transition Table

FA FB 0 1 0 1 State A B C D

Each state is assigned a unique code.

0 0 1 1

Transition Table for state machine M1

S-R flip-flop used to realize circuit

Transition Table for state machine M1

S-R flip-flop excitation table Qt 0 0 1 1 Qt+1 0 1 0 1 S 0 1 0 d R d 0 1 0

state machine M1 excitation table using S-R flip-flops

Excitation Table and Equations

SA K-Map

RA K-Map

SB K-Map

RB K-Map

SA=f(FA,FB,x,y)=Σ(5,7) +Σd(9,10,13,15) =FBy RA=f(FA,FB,x,y)=Σ(8,11,12,14) +Σd(0,1,2,3,4,6) =FB’xy+x’y’+FBy’ SB=f(FA,FB,x,y)=Σ(2,3) +Σd(4,5,6,7,14,15) =FA’x RB=f(FA,FB,x,y)=Σ(12,13) +Σd(0,1,8,9,10,11) =FAx’

X

State Diagram of Mealy model

0/0 00 0/1 1/0 I/O

01 1/0 11

S1

S2

0/1

0/1 1/0

Reads as: When at state s1 and apply input I, we get output O and proceed to state s2.

TA K-Map

TB K-Map

TA=f(FA,FB,x,y)=Σ(5,7,8,11,12,14)=FAFB’xy+FAx’y’+FAFBy’+FA’FBy

TB=f(FA,FB,x,y)=Σ(2,3,12,13)=FA’FB’x+FAFBx’

Excitation Table and Equations

Excitation Table and Equations

JA K-Map

KA K-Map

JB K-Map

KB K-Map

JA=f(FA,FB,x,y)=Σ(5,7) +Σd(8,9,10,11,12,13,14,15) =FBy KA=f(FA,FB,x,y)=Σ(8,11,12,14) +Σd(0,1,2,3,4,6,7) =FB’xy+x’y’+FBy’ JB=f(FA,FB,x,y)=Σ(2,3) +Σd(4,5,6,7,12,13,14,15) =FA’x KB=f(FA,FB,x,y)=Σ(12,13) +Σd(0,1,2,3,8,9,10,11) =FAx’

D flip-flop excitation table Qt 0 0 1 1 Qt+1 0 1 0 1 D 0 1 0 1

state machine M1 excitation table using D flip-flops

Excitation Table and Equations

DA K-Map

10

1/0

State Diagram of Moore model

I

S1/O1 S2/O2

0/0

00,11 01,10 01,10

1/1

00,11

Reads as: When at state s1 with output O1 and apply input I, we proceed to state s2 with Output O2.

State Table

Transition Table for Table machine M1 State state

Present State FA 0 FB 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Input X 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Y 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Next State FA 0 0 0 0 0 1 0 1 0 1 1 0 0 1 0 1 FB 0 0 1 1 1 1 1 1 0 0 0 0 0 0 1 1 Output Z 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

DB K-Map

Z K-Map

DA=f(FA,FB,x,y)=Σ(5,7,10,13,15)=FAFB’xy’+FAx’y+FBy DB=f(FA,FB,x,y)=Σ(2,3,4,5,6,7,14,15)=FA’FB+FA’x+FBx Z= f(FA,FB,x,y)=Σ(11)=FAFB’xy

Excitation Table and Equations

T flip-flop used to realize circuit

Transition Table for state machine M1

T flip-flop excitation table Qt 0 0 1 1 Qt+1 0 1 0 1 T 0 1 1 0

Excitation Table and Equations

Excitation Realization Cost

JA=FBy KA=FB’xy+x’y’+FBy’ JB=FA’x KB=FAx’

Excitation Realization Cost

SA=FBy

RA=FB’xy+x’y’+FBy’

SB=FA’x RB=FAx’

Excitation Realization Cost

2x=y

State variables states

State Diagram

Graphical representation of a state table. Graph node with label s denotes state s

S

Graph edge with label X denotes transition between two states when input X is applied

CHAPTER 6 Sequential Circuits’ Analysis

Sichuan University Software College

Mealy Vs Moore machines

Mealy model:

Both outputs and next state depend both on primary inputs AND present state. Only next state depends directly on primary inputs AND present state. Outputs depend only on present state.

OUTPUT VARIABLES (O)

Mealy sequential circuit model

INPUT VARIABLES (t) EXCITATION IMPUT LOGIC (f) STATE VARIABLES (E) MEMORY CLK (S) OUTPUT LOGIC (g)

OUTPUT VARIABLES (O)

Moore model:

Mealy Vs Moore machines

Moore sequential circuit model

INPUT VARIABLES (t) EXCITATION IMPUT LOGIC (f) STATE VARIABLES (E) MEMORY CLK (S) OUTPUT LOGIC (g)

State Diagram

State Table

Enumerates the relationship between inputs, outputs, and states of the sequential circuit.

State Table

State Table

State Table

Input Present State A X 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Y 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Next State A A B B B D B D A C C A A C B D Output Z 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

Transition Table for state machine M1

0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

Excitation Table and Equations

D flip-flop used to realize circuit

Transition Table for state machine M1

State Machine Notation

Impute variable Output variable State variable Excitation variable State State variables and states are related by the expression: